# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                   |

|---------------------------------|--------------------------------------------------------------------------|

| Core Processor                  | ARM® Cortex®-A9                                                          |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                                           |

| Speed                           | 852MHz                                                                   |

| Co-Processors/DSP               | Multimedia; NEON™ SIMD                                                   |

| RAM Controllers                 | LPDDR2, DDR3L, DDR3                                                      |

| Graphics Acceleration           | Yes                                                                      |

| Display & Interface Controllers | HDMI, Keypad, LCD, LVDS, MIPI/DSI, Parallel                              |

| Ethernet                        | 10/100/1000Mbps (1)                                                      |

| SATA                            | SATA 3Gbps (1)                                                           |

| USB                             | USB 2.0 + PHY (3), USB 2.0 OTG + PHY (1)                                 |

| Voltage - I/O                   | 1.8V, 2.5V, 2.8V, 3.3V                                                   |

| Operating Temperature           | -40°C ~ 125°C (TJ)                                                       |

| Security Features               | ARM TZ, A-HAB, CAAM, CSU, SJC, SNVS                                      |

| Package / Case                  | 624-FBGA, FCBGA                                                          |

| Supplier Device Package         | 624-FCBGA (21x21)                                                        |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6dp6avt8aar |

|                                 |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Block<br>Mnemonic                         | Block Name                           | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------|--------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSI                                       | MIPI CSI-2 Interface                 | Multimedia<br>Peripherals        | The CSI IP provides MIPI CSI-2 standard camera interface port. The CSI-2 interface supports up to 1 Gbps for up to 3 data lanes and up to 800 Mbps for 4 data lanes.                                                                                                                                                                                                                                                             |

| CSU                                       | Central Security Unit                | Security                         | The Central Security Unit (CSU) is responsible for setting comprehensive security policy within the i.MX 6DualPlus/6QuadPlus platform. The Security Control Registers (SCR) of the CSU are set during boot time by the HAB and are locked to prevent further writing.                                                                                                                                                            |

| CTI-0<br>CTI-1<br>CTI-2<br>CTI-3<br>CTI-4 | Cross Trigger<br>Interfaces          | Debug / Trace                    | Cross Trigger Interfaces allows cross-triggering based on inputs from masters attached to CTIs. The CTI module is internal to the Cortex-A9 Core Platform.                                                                                                                                                                                                                                                                       |

| СТМ                                       | Cross Trigger Matrix                 | Debug / Trace                    | Cross Trigger Matrix IP is used to route triggering events between CTIs.<br>The CTM module is internal to the Cortex-A9 Core Platform.                                                                                                                                                                                                                                                                                           |

| DAP                                       | Debug Access Port                    | System<br>Control<br>Peripherals | <ul> <li>The DAP provides real-time access for the debugger without halting the core to:</li> <li>System memory and peripheral registers</li> <li>All debug configuration registers</li> <li>The DAP also provides debugger access to JTAG scan chains. The DAP module is internal to the Cortex-A9 Core Platform.</li> </ul>                                                                                                    |

| DCIC-0<br>DCIC-1                          | Display Content<br>Integrity Checker | Automotive IP                    | The DCIC provides integrity check on portion(s) of the display. Each i.MX 6DualPlus/6QuadPlus processor has two such modules, one for each IPU.                                                                                                                                                                                                                                                                                  |

| DSI                                       | MIPI DSI interface                   | Multimedia<br>Peripherals        | The MIPI DSI IP provides DSI standard display port interface. The DSI interface support 80 Mbps to 1 Gbps speed per data lane.                                                                                                                                                                                                                                                                                                   |

| eCSPI1-5                                  | Configurable SPI                     | Connectivity<br>Peripherals      | Full-duplex enhanced Synchronous Serial Interface. It is configurable to support Master/Slave modes, four chip selects to support multiple peripherals.                                                                                                                                                                                                                                                                          |

| ENET                                      | Ethernet Controller                  | Connectivity<br>Peripherals      | The Ethernet Media Access Controller (MAC) is designed to support 10/100/1000 Mbps Ethernet/IEEE 802.3 networks. An external transceiver interface and transceiver function are required to complete the interface to the media. The i.MX 6DualPlus/6QuadPlus processors also consist of hardware assist for IEEE 1588 standard. For details, see the ENET chapter of the i.MX 6DualPlus/6QuadPlus reference manual (IMX6DQPRM). |

|                                           |                                      |                                  | <b>Note:</b> The theoretical maximum performance of 1 Gbps ENET is limited to 470 Mbps (total for Tx and Rx) due to internal bus throughput limitations. The actual measured performance in optimized environment is up to 400 Mbps. For details, see the ERR004512 erratum in the i.MX 6Dual/6Quad errata document (IMX6DQCE).                                                                                                  |

| EPIT-1<br>EPIT-2                          | Enhanced Periodic<br>Interrupt Timer | Timer<br>Peripherals             | Each EPIT is a 32-bit "set and forget" timer that starts counting after the EPIT is enabled by software. It is capable of providing precise interrupts at regular intervals with minimal processor intervention. It has a 12-bit prescaler for division of input clock frequency to get the required time setting for the interrupts to occur, and counter value can be programmed on the fly.                                   |

| Block<br>Mnemonic                | Block Name                    | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------|-------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRE1<br>PRE2<br>PRE3<br>PRE4     | Prefetch/Resolve<br>Engine    | Multimedia<br>Peripherals     | <ul> <li>The PRE includes the Resolve engine, Prefetch engine, and Store engine 3 blocks. The PRE key features are:</li> <li>The Resolve engine supports: <ul> <li>GPU 32bpp 4x4 standard tile, 4x4 split tile, 4x4 super tile, 4x4 super split tile format.</li> <li>GPU 16bpp 8x4 standard tile, 8x4 split tile, 8x4 super tile, 8x4 super split format.</li> <li>32/16x4 block mode and scan mode.</li> </ul> </li> <li>The prefetch engine supports: <ul> <li>Transfer of non-interleaved YUV422(NI422), non-interleaved YUV420(NI420), partial interleaved YUV422(PI422), and partial interleaved YUV420(PI420), inputs to interleaved YUV422.</li> <li>Vertical flip function both in block mode and scan mode. In block mode, vertical flip function should complete with TPR module enable.</li> <li>8bpp, 16bpp, 32bpp and 64bpp data format as generic data.</li> <li>Transfer of non-interleaved YUV444(NI444), input to interleaved YUV444 output.</li> </ul> </li> <li>The store Engine supports: 4/8/16 lines handshake modes with PRG.</li> </ul> |

| PRG1<br>PRG2                     | Prefetch/Resolve<br>Gasket    | Multimedia<br>Peripherals     | The PRG is a digital core function which works as a gasket interface<br>between the fabric and the IPU system. The primary function is to re-map<br>the ARADDR from a frame-based address to a band-based address<br>depending on the different ARIDs. The PRG also implements the<br>handshake logic with the Prefetch Resolve Engine (PRE).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PMU                              | Power-Management<br>Functions | Data Path                     | Integrated power management unit. Used to provide power to various SoC domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PWM-1<br>PWM-2<br>PWM-3<br>PWM-4 | Pulse Width<br>Modulation     | Connectivity<br>Peripherals   | The pulse-width modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images and it can also generate tones. It uses 16-bit resolution and a $4x16$ data FIFO to generate sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RAM<br>16 KB                     | Secure/non-secure<br>RAM      | Secured<br>Internal<br>Memory | Secure/non-secure Internal RAM, interfaced through the CAAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RAM<br>512 KB                    | Internal RAM                  | Internal<br>Memory            | Internal RAM, which is accessed through OCRAM memory controllers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ROM<br>96 KB                     | Boot ROM                      | Internal<br>Memory            | Supports secure and regular Boot Modes. Includes read protection on 4K region for content protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SATA                             | Serial ATA                    | Connectivity<br>Peripherals   | The SATA controller and PHY is a complete mixed-signal IP solution designed to implement SATA II, 3.0 Gbps HDD connectivity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### **Modules List**

| Block<br>Mnemonic       | Block Name                     | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-------------------------|--------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SDMA                    | Smart Direct Memory<br>Access  | System<br>Control<br>Peripherals | <ul> <li>The SDMA is multi-channel flexible DMA engine. It helps in maximizing system performance by off-loading the various cores in dynamic data routing. It has the following features:</li> <li>Powered by a 16-bit Instruction-Set micro-RISC engine</li> <li>Multi-channel DMA supporting up to 32 time-division multiplexed DMA channels</li> <li>48 events with total flexibility to trigger any combination of channels</li> <li>Memory accesses including linear, FIFO, and 2D addressing</li> <li>Shared peripherals between ARM and SDMA</li> <li>Very fast context-switching with 2-level priority based preemptive multi-tasking</li> <li>DMA units with auto-flush and prefetch capability</li> <li>Flexible address management for DMA transfers (increment, decrement, and no address changes on source and destination address)</li> <li>DMA ports can handle unit-directional and bi-directional flows (copy mode)</li> <li>Up to 8-word buffer for configurable burst transfers</li> <li>Support of byte-swapping and CRC calculations</li> <li>Library of Scripts and API is available</li> </ul> |  |  |  |

| SJC                     | System JTAG<br>Controller      | System<br>Control<br>Peripherals | The SJC provides JTAG interface, which complies with JTAG TAP standards, to internal logic. The i.MX 6DualPlus/6QuadPlus processors use JTAG port for production, testing, and system debugging. In addition, the SJC provides BSR (Boundary Scan Register) standard support, which complies with IEEE1149.1 and IEEE1149.6 standards. The JTAG port must be accessible during platform initial laboratory bring-up, for manufacturing tests and troubleshooting, as well as for software debugging by authorized entities. The i.MX 6DualPlus/6QuadPlus SJC incorporates three security modes for protecting against unauthorized accesses. Modes are selected through eFUSE configuration.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| SNVS                    | Secure Non-Volatile<br>Storage | Security                         | Secure Non-Volatile Storage, including Secure Real Time Clock, Security State Machine, Master Key Control, and Violation/Tamper Detection and reporting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| SPDIF                   | , , ,                          | Multimedia<br>Peripherals        | A standard audio file transfer format, developed jointly by the Sony and Phillips corporations. It supports Transmitter and Receiver functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| SSI-1<br>SSI-2<br>SSI-3 | I2S/SSI/AC97<br>Interface      | Connectivity<br>Peripherals      | The SSI is a full-duplex synchronous interface, which is used on the processor to provide connectivity with off-chip audio peripherals. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock / frame sync options. The SSI has two pairs of 8x24 FIFOs and hardware support for an external DMA controller to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream that reduces CPU overhead in use cases where two time slots are being used simultaneously.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

### Table 2. i.MX 6DualPlus/6QuadPlus Modules List (continued)

# 4.1.2 Thermal Resistance

### NOTE

Per JEDEC JESD51-2, the intent of thermal resistance measurements is solely for a thermal performance comparison of one package to another in a standardized environment. This methodology is not meant to and will not predict the performance of a package in an application-specific environment.

### 4.1.2.1 FCPBGA Package Thermal Resistance

Table 5 provides the FCPBGA package thermal resistance data for the *lidded* package type.

| Thermal Parameter                     | Test Conditions                                           | Symbol                | Value | Unit |

|---------------------------------------|-----------------------------------------------------------|-----------------------|-------|------|

| Junction to Ambient <sup>1</sup>      | Single-layer board (1s); natural convection <sup>2</sup>  | R <sub>θJA</sub>      | 24    | °C/W |

|                                       | Four-layer board (2s2p); natural convection <sup>2</sup>  | $R_{	extsf{	heta}JA}$ | 15    | °C/W |

| Junction to Ambient <sup>1</sup>      | Single-layer board (1s); air flow 200 ft/min <sup>3</sup> | R <sub>θJMA</sub>     | 17    | °C/W |

|                                       | Four-layer board (2s2p); air flow 200 ft/min <sup>4</sup> | $R_{\thetaJMA}$       | 12    | °C/W |

| Junction to Board <sup>1,4</sup>      | -                                                         | R <sub>θJB</sub>      | 5     | °C/W |

| Junction to Case (top) <sup>1,5</sup> | -                                                         | R <sub>0JCtop</sub>   | 1     | °C/W |

Table 5. FCPBGA Package Thermal Resistance Data (Lidded)

<sup>1</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Per JEDEC JESD51-3 with the single layer board horizontal. Thermal test board meets JEDEC specification for the specified package.

- <sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

- <sup>4</sup> Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>5</sup> Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1). The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

| Table 8. Maximum Supply Currents ( | (continued) |

|------------------------------------|-------------|

|------------------------------------|-------------|

| Power Supply | Conditions | Maximum C                                                                                                                                          | Unit     |      |  |  |

|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|--|--|

|              | Conditions | Power Virus                                                                                                                                        | CoreMark | onit |  |  |

| NVCC_LVDS2P5 | _          | NVCC_LVDS2P5 is connected to<br>VDD_HIGH_CAP at the board<br>level. VDD_HIGH_CAP is capable<br>of handing the current required by<br>NVCC_LVDS2P5. |          |      |  |  |

| MISC         |            |                                                                                                                                                    |          |      |  |  |

| DRAM_VREF    | _          | 1                                                                                                                                                  | mA       |      |  |  |

<sup>1</sup> i.MX 6DualPlus numbers assume VDD\_ARM23\_IN and VDD\_ARM23\_CAP are connected to ground.

<sup>2</sup> The actual maximum current drawn from VDD\_HIGH\_IN will be as shown plus any additional current drawn from the VDD\_HIGH\_CAP outputs, depending upon actual application configuration (for example, NVCC\_LVDS\_2P5, NVCC\_MIPI, or HDMI, PCIe, and SATA VPH supplies).

- <sup>3</sup> Under normal operating conditions, the maximum current on VDD\_SNVS\_IN is shown Table 8. The maximum VDD\_SNVS\_IN current may be higher depending on specific operating configurations, such as BOOT\_MODE[1:0] not equal to 00, or use of the Tamper feature. During initial power on, VDD\_SNVS\_IN can draw up to 1 mA if the supply is capable of sourcing that current. If less than 1 mA is available, the VDD\_SNVS\_CAP charge time will increase.

- <sup>4</sup> This is the maximum current per active USB physical interface.

- <sup>5</sup> The DRAM power consumption is dependent on several factors such as external signal termination. DRAM power calculators are typically available from memory vendors which take into account factors such as signal termination. See the *i.MX 6Dual/6Quad Power Consumption Measurement Application Note* (AN4509) for examples of DRAM power consumption during specific use case scenarios.

- <sup>6</sup> General equation for estimated, maximum power consumption of an IO power supply: Imax = N x C x V x (0.5 x F)

- Where:

N—Number of IO pins supplied by the power line

- C—Equivalent external capacitive load

- V—IO voltage

(0.5 xF)—Data change rate. Up to 0.5 of the clock rate (F)

In this equation, Imax is in Amps, C in Farads, V in Volts, and F in Hertz.

# 4.1.6 Low Power Mode Supply Currents

Table 9 shows the current core consumption (not including I/O) of the i.MX 6DualPlus/6QuadPlus processors in selected low power modes.

| Mode | Test Conditions                                                                                                                                                                                                                                    | Supply              | Typical <sup>1</sup> | Unit |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|------|

| WAIT | <ul> <li>WAIT</li> <li>ARM, SoC, and PU LDOs are set to 1.225 V</li> <li>HIGH LDO set to 2.5 V</li> <li>Clocks are gated</li> <li>DDR is in self refresh</li> <li>PLLs are active in bypass (24 MHz)</li> <li>Supply voltages remain ON</li> </ul> | VDD_ARM_IN (1.4 V)  | 6                    | mA   |

|      |                                                                                                                                                                                                                                                    | VDD_SOC_IN (1.4 V)  | 23                   | mA   |

|      |                                                                                                                                                                                                                                                    | VDD_HIGH_IN (3.0 V) | 3.7                  | mA   |

|      |                                                                                                                                                                                                                                                    | Total               | 52                   | mW   |

#### Table 9. Stop Mode Current and Power Consumption

| Mode                             | Test Conditions    | Supply   | Typical Current | Unit |

|----------------------------------|--------------------|----------|-----------------|------|

| P1: Transmitter idle, Rx powered | Single Transceiver | SATA_VP  | 0.67            | mA   |

| down, LOS disabled               | -                  | SATA_VPH | 0.23            |      |

|                                  | Clock Module       | SATA_VP  | 6.9             |      |

|                                  | -                  | SATA_VPH | 6.2             |      |

| P2: Powered-down state, only     | Single Transceiver | SATA_VP  | 0.53            | mA   |

| LOS and POR enabled              |                    | SATA_VPH | 0.11            |      |

|                                  | Clock Module       | SATA_VP  | 0.036           |      |

|                                  | -                  | SATA_VPH | 0.12            |      |

| PDDQ mode <sup>3</sup>           | Single Transceiver | SATA_VP  | 0.13            | mA   |

|                                  | -                  | SATA_VPH | 0.012           |      |

|                                  | Clock Module       | SATA_VP  | 0.008           | 1    |

|                                  | -                  | SATA_VPH | 0.004           | 1    |

#### Table 11. SATA PHY Current Drain (continued)

<sup>1</sup> Programmed for 1.0 V peak-to-peak Tx level.

<sup>2</sup> Programmed for 0.9 V peak-to-peak Tx level with no boost or attenuation.

<sup>3</sup> LOW power non-functional.

# 4.1.9 PCIe 2.0 Maximum Power Consumption

Table 12 provides PCIe PHY currents for certain operating modes.

Table 12. PCIe PHY Current Drain

| Mode                        | Test Conditions | Supply            | Max Current | Unit |

|-----------------------------|-----------------|-------------------|-------------|------|

| P0: Normal Operation        | 5G Operations   | PCIE_VP (1.1 V)   | 40          | mA   |

|                             |                 | PCIE_VPTX (1.1 V) | 20          |      |

|                             |                 | PCIE_VPH (2.5 V)  | 21          |      |

|                             | 2.5G Operations | PCIE_VP (1.1 V)   | 27          |      |

|                             |                 | PCIE_VPTX (1.1 V) | 20          |      |

|                             |                 | PCIE_VPH (2.5 V)  | 20          | 1    |

| P0s: Low Recovery Time      | 5G Operations   | PCIE_VP (1.1 V)   | 30          | mA   |

| Latency, Power Saving State |                 | PCIE_VPTX (1.1 V) | 2.4         | 1    |

|                             |                 | PCIE_VPH (2.5 V)  | 18          |      |

|                             | 2.5G Operations | PCIE_VP (1.1 V)   | 20          |      |

|                             |                 | PCIE_VPTX (1.1 V) | 2.4         |      |

|                             |                 | PCIE_VPH (2.5 V)  | 18          | 1    |

system to determine when the load capability of the regulator is being exceeded to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature.

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6DualPlus/6QuadPlus reference manual (IMX6DQPRM).

# 4.3.2.2 LDO\_2P5 / VDDHIGH\_CAP

The LDO\_2P5 module implements a programmable linear-regulator function from VDD\_HIGH\_IN (see Table 6 for min and max input requirements). Typical Programming Operating Range is 2.25 V to 2.75 V with the nominal default setting as 2.5 V. The LDO\_2P5 supplies the eFuses, PLLs, and USB PHY. Optionally it can be used to supply the HDMI, LVDS, MIPI, PCIe, and SATA PHY's through external connections. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature. An alternate self-biased low-precision weak-regulator is included that can be enabled for applications needing to keep the output voltage alive during low-power modes where the main regulator driver and its associated global bandgap reference module are disabled. The output of the weak-regulator is not programmable and is a function of the input supply as well as the load current. Typically, with a 3 V input supply the weak-regulator output is 2.525 V and its output impedance is approximately  $40 \,\Omega$ .

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6DualPlus/6QuadPlus reference manual (IMX6DQPRM).

# 4.3.2.3 LDO\_USB / VDD\_VBUS\_CAP

The LDO\_USB module implements a programmable linear-regulator function from the USB\_OTG\_VBUS and USB\_H1\_VBUS voltages (4.4 V–5.25 V) to produce a nominal 3.0 V output voltage. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. This regulator has a built in power-mux that allows the user to select to run the regulator from either VBUS supply, when both are present. If only one of the VBUS voltages is present, then the regulator automatically selects this supply. Current limit is also included to help the system meet in-rush current targets. If no VBUS voltage is present, then the VBUSVALID threshold setting will prevent the regulator from being enabled.

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6DualPlus/6QuadPlus reference manual (IMX6DQPRM).

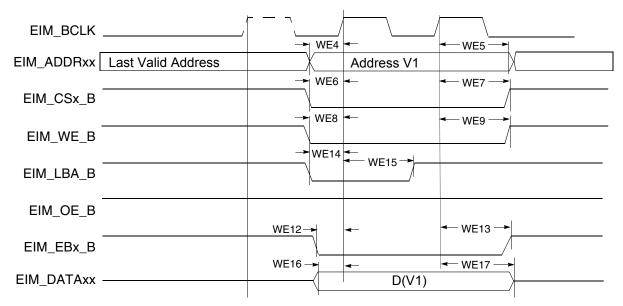

Figure 14 to Figure 17 provide few examples of basic EIM accesses to external memory devices with the timing parameters mentioned previously for specific control parameters settings.

Figure 14. Synchronous Memory Read Access, WSC=1

Figure 15. Synchronous Memory, Write Access, WSC=1, WBEA=0 and WADVN=0

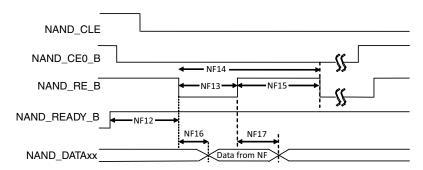

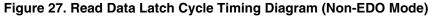

Figure 28. Read Data Latch Cycle Timing Diagram (EDO Mode)

| ID   | Parameter                | Symbol           | Timing<br>T = GPMI Clock Cycle                    |                              | Unit |

|------|--------------------------|------------------|---------------------------------------------------|------------------------------|------|

|      |                          |                  | Min                                               | Мах                          |      |

| NF1  | NAND_CLE setup time      | tCLS             | $(AS + DS) \times T$                              | - 0.12 [see <sup>2,3</sup> ] | ns   |

| NF2  | NAND_CLE hold time       | tCLH             | DH × T - 0.                                       | .72 [see <sup>2</sup> ]      | ns   |

| NF3  | NAND_CEx_B setup time    | tCS              | (AS + DS + 1)                                     | ) × T [see <sup>3,2</sup> ]  | ns   |

| NF4  | NAND_CEx_B hold time     | tCH              | (DH+1)×T                                          | - 1 [see <sup>2</sup> ]      | ns   |

| NF5  | NAND_WE_B pulse width    | tWP              | DS × T                                            | [see <sup>2</sup> ]          | ns   |

| NF6  | NAND_ALE setup time      | tALS             | $(AS + DS) \times T - 0.49$ [see <sup>3,2</sup> ] |                              | ns   |

| NF7  | NAND_ALE hold time       | tALH             | (DH × T - 0                                       | .42 [see <sup>2</sup> ]      | ns   |

| NF8  | Data setup time          | tDS              | DS × T - 0.                                       | .26 [see <sup>2</sup> ]      | ns   |

| NF9  | Data hold time           | tDH              | DH×T-1.                                           | .37 [see <sup>2</sup> ]      | ns   |

| NF10 | Write cycle time         | tWC              | (DS + DH)                                         | × T [see <sup>2</sup> ]      | ns   |

| NF11 | NAND_WE_B hold time      | tWH              | DH×T                                              | [see <sup>2</sup> ]          | ns   |

| NF12 | Ready to NAND_RE_B low   | tRR <sup>4</sup> | (AS + 2) × T [see <sup>3,2</sup> ] —              |                              | ns   |

| NF13 | NAND_RE_B pulse width    | tRP              | $DS \times T$ [see <sup>2</sup> ]                 |                              | ns   |

| NF14 | READ cycle time          | tRC              | $(DS + DH) \times T [see ^2]$                     |                              | ns   |

| NF15 | NAND_RE_B high hold time | tREH             | DH×T                                              | [see <sup>2</sup> ]          | ns   |

| Table 44. A | synchronous | Mode | Timing | Parameters <sup>1</sup> |  |

|-------------|-------------|------|--------|-------------------------|--|

|-------------|-------------|------|--------|-------------------------|--|

| Table 44. Asynchronous Mode | Timing Parameters <sup>1</sup> | (continued) |

|-----------------------------|--------------------------------|-------------|

|-----------------------------|--------------------------------|-------------|

| ID   | Parameter          | Symbol | Timing<br>T = GPMI Clock Cycle   |                                               | Unit |

|------|--------------------|--------|----------------------------------|-----------------------------------------------|------|

|      |                    |        | Min                              | Мах                                           |      |

| NF16 | Data setup on read | tDSR   | _                                | (DS $\times$ T $$ -0.67)/18.38 [see $^{5,6}]$ | ns   |

| NF17 | Data hold on read  | tDHR   | 0.82/11.83 [see <sup>5,6</sup> ] | _                                             | ns   |

<sup>1</sup> The GPMI asynchronous mode output timing can be controlled by the module's internal registers HW\_GPMI\_TIMING0\_ADDRESS\_SETUP, HW\_GPMI\_TIMING0\_DATA\_SETUP, and HW\_GPMI\_TIMING0\_DATA\_HOLD. This AC timing depends on these registers settings. In the table, AS/DS/DH represents each of these settings.

<sup>2</sup> AS minimum value can be 0, while DS/DH minimum value is 1.

<sup>3</sup> T = GPMI clock period -0.075ns (half of maximum p-p jitter).

<sup>4</sup> NF12 is met automatically by the design.

<sup>5</sup> Non-EDO mode.

<sup>6</sup> EDO mode, GPMI clock ≈ 100 MHz (AS=DS=DH=1, GPMI\_CTL1 [RDN\_DELAY] = 8, GPMI\_CTL1 [HALF\_PERIOD] = 0).

In EDO mode (Figure 28), NF16/NF17 are different from the definition in non-EDO mode (Figure 27). They are called tREA/tRHOH (NAND\_RE\_B access time/NAND\_RE\_B HIGH to output hold). The typical value for them are 16 ns (max for tREA)/15 ns (min for tRHOH) at 50 MB/s EDO mode. In EDO mode, GPMI will sample NAND\_DATAxx at rising edge of delayed NAND\_RE\_B provided by an internal DPLL. The delay value can be controlled by GPMI\_CTRL1.RDN\_DELAY (see the GPMI chapter of the i.MX 6DualPlus/6QuadPlus reference manual (IMX6DQPRM)). The typical value of this control register is 0x8 at 50 MT/s EDO mode. However, if the board delay is large enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

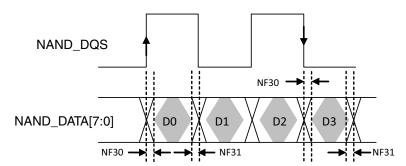

Figure 32. NAND\_DQS/NAND\_DQ Read Valid Window

| ID   | Parameter                                      | Symbol | Timin<br>T = GPMI Clo                     | Unit                     |    |

|------|------------------------------------------------|--------|-------------------------------------------|--------------------------|----|

|      |                                                |        | Min                                       | Max                      |    |

| NF18 | NAND_CEx_B access time                         | tCE    | $CE\_DELAY \times T \text{ -}$            | 0.79 [see <sup>2</sup> ] | ns |

| NF19 | NAND_CEx_B hold time                           | tCH    | 0.5 × tCK - 0.6                           | 3 [see <sup>2</sup> ]    | ns |

| NF20 | Command/address NAND_DATAxx setup time         | tCAS   | 0.5 	imes tCK ·                           | 0.05                     | ns |

| NF21 | Command/address NAND_DATAxx hold time          | tCAH   | 0.5 × tCK - 1.23                          |                          | ns |

| NF22 | clock period                                   | tCK    |                                           |                          | ns |

| NF23 | preamble delay                                 | tPRE   | PRE_DELAY × T - 0.29 [see <sup>2</sup> ]  |                          | ns |

| NF24 | postamble delay                                | tPOST  | POST_DELAY × T - 0.78 [see <sup>2</sup> ] |                          | ns |

| NF25 | NAND_CLE and NAND_ALE setup time               | tCALS  | 0.5 	imes tCK ·                           | 0.86                     | ns |

| NF26 | NAND_CLE and NAND_ALE hold time                | tCALH  | 0.5 	imes tCK ·                           | 0.37                     | ns |

| NF27 | NAND_CLK to first NAND_DQS latching transition | tDQSS  | T - 0.41 [s                               | ee <sup>2</sup> ]        | ns |

| NF28 | Data write setup                               | tDS    | 0.25 × tCK - 0.35                         |                          | —  |

| NF29 | Data write hold                                | tDH    | 0.25 × tCK - 0.85                         |                          | —  |

| NF30 | NAND_DQS/NAND_DQ read setup skew               | tDQSQ  | — 2.06                                    |                          | —  |

| NF31 | NAND_DQS/NAND_DQ read hold skew                | tQHS   | _                                         | 1.95                     | —  |

Table 45. Source Synchronous Mode Timing Parameters<sup>1</sup>

<sup>1</sup> The GPMI source synchronous mode output timing can be controlled by the module's internal registers GPMI\_TIMING2\_CE\_DELAY, GPMI\_TIMING\_PREAMBLE\_DELAY, GPMI\_TIMING2\_POST\_DELAY. This AC timing depends on these registers settings. In the table, CE\_DELAY/PRE\_DELAY/POST\_DELAY represents each of these settings.

<sup>2</sup> T = tCK (GPMI clock period) -0.075ns (half of maximum p-p jitter).

Figure 32 shows the timing diagram of NAND\_DQS/NAND\_DATAxx read valid window. For Source Synchronous mode, the typical value of tDQSQ is 0.85 ns (max) and 1 ns (max) for tQHS at 200MB/s. GPMI will sample NAND\_DATA[7:0] at both rising and falling edge of a delayed NAND\_DQS signal, which can be provided by an internal DPLL. The delay value can be controlled by GPMI register GPMI\_READ\_DDR\_DLL\_CTRL.SLV\_DLY\_TARGET (see the GPMI chapter of the i.MX 6DualPlus/6QuadPlus reference manual (IMX6DQPRM)). Generally, the typical delay value of this register is equal to 0x7 which means 1/4 clock cycle delay expected. However, if the board delay is large enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

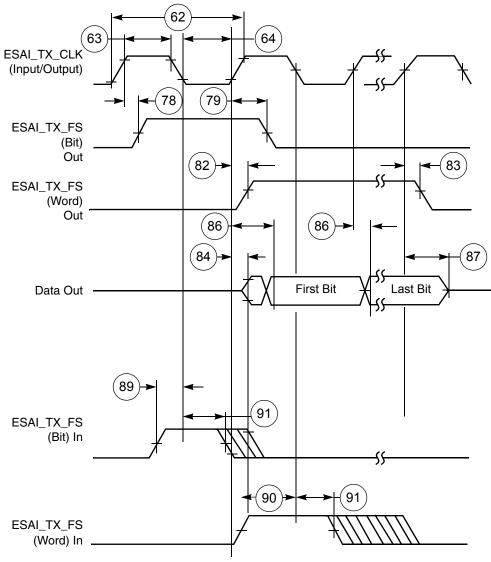

Figure 37. ESAI Transmitter Timing

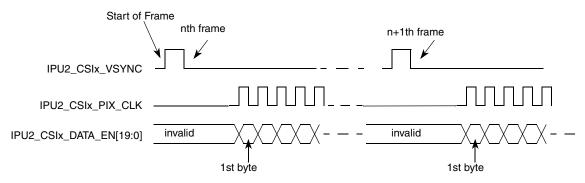

stops receiving data from the stream. For the next line, the IPU2\_CSIx\_HSYNC timing repeats. For the next frame, the IPU2\_CSIx\_VSYNC timing repeats.

### 4.12.10.2.3 Non-Gated Clock Mode

The timing is the same as the gated-clock mode (described in Section 4.12.10.2.2, "Gated Clock Mode,") except for the IPU2\_CSIx\_HSYNC signal, which is not used (see Figure 60). All incoming pixel clocks are valid and cause data to be latched into the input FIFO. The IPU2\_CSIx\_PIX\_CLK signal is inactive (states low) until valid data is going to be transmitted over the bus.

Figure 60. Non-Gated Clock Mode Timing Diagram

The timing described in Figure 60 is that of a typical sensor. Some other sensors may have a slightly different timing. The CSI can be programmed to support rising/falling-edge triggered IPU2\_CSIx\_VSYNC; active-high/low IPU2\_CSIx\_HSYNC; and rising/falling-edge triggered IPU2\_CSIx\_PIX\_CLK.

| i.MX<br>6DualPlus/6QuadPlus |                             |               |               | LCD           |                             |                 |                                  |                        |

|-----------------------------|-----------------------------|---------------|---------------|---------------|-----------------------------|-----------------|----------------------------------|------------------------|

|                             | RGB,                        | R             | GB/TV         | Signal A      | Allocation                  | (Examp          | ole)                             | Comment <sup>1,2</sup> |

| Port Name<br>(x = 0, 1)     | Signal<br>Name<br>(General) | 16-bit<br>RGB | 18-bit<br>RGB | 24 Bit<br>RGB | 8-bit<br>YCrCb <sup>3</sup> | 16-bit<br>YCrCb | 20-bit<br>YCrCb                  |                        |

| IPUx_DISPx_DAT05            | DAT[5]                      | G[0]          | B[5]          | B[5]          | Y/C[5]                      | C[5]            | C[5]                             | —                      |

| IPUx_DISPx_DAT06            | DAT[6]                      | G[1]          | G[0]          | B[6]          | Y/C[6]                      | C[6]            | C[6]                             | _                      |

| IPUx_DISPx_DAT07            | DAT[7]                      | G[2]          | G[1]          | B[7]          | Y/C[7]                      | C[7]            | C[7]                             | _                      |

| IPUx_DISPx_DAT08            | DAT[8]                      | G[3]          | G[2]          | G[0]          | _                           | Y[0]            | C[8]                             | _                      |

| IPUx_DISPx_DAT09            | DAT[9]                      | G[4]          | G[3]          | G[1]          | _                           | Y[1]            | C[9]                             | _                      |

| IPUx_DISPx_DAT10            | DAT[10]                     | G[5]          | G[4]          | G[2]          | _                           | Y[2]            | Y[0]                             | _                      |

| IPUx_DISPx_DAT11            | DAT[11]                     | R[0]          | G[5]          | G[3]          | _                           | Y[3]            | Y[1]                             | _                      |

| IPUx_DISPx_DAT12            | DAT[12]                     | R[1]          | R[0]          | G[4]          | _                           | Y[4]            | Y[2]                             | _                      |

| IPUx_DISPx_DAT13            | DAT[13]                     | R[2]          | R[1]          | G[5]          | _                           | Y[5]            | Y[3]                             | _                      |

| IPUx_DISPx_DAT14            | DAT[14]                     | R[3]          | R[2]          | G[6]          | _                           | Y[6]            | Y[4]                             | _                      |

| IPUx_DISPx_DAT15            | DAT[15]                     | R[4]          | R[3]          | G[7]          |                             | Y[7]            | Y[5]                             | _                      |

| IPUx_DISPx_DAT16            | DAT[16]                     | _             | R[4]          | R[0]          |                             |                 | Y[6]                             | _                      |

| IPUx_DISPx_DAT17            | DAT[17]                     | _             | R[5]          | R[1]          | _                           | —               | Y[7]                             | _                      |

| IPUx_DISPx_DAT18            | DAT[18]                     | _             |               | R[2]          |                             |                 | Y[8]                             | _                      |

| IPUx_DISPx_DAT19            | DAT[19]                     | _             |               | R[3]          |                             |                 | Y[9]                             | _                      |

| IPUx_DISPx_DAT20            | DAT[20]                     | _             |               | R[4]          |                             | —               | —                                | _                      |

| IPUx_DISPx_DAT21            | DAT[21]                     | _             | —             | R[5]          |                             | —               | —                                | _                      |

| IPUx_DISPx_DAT22            | DAT[22]                     | _             | —             | R[6]          | _                           | —               | —                                | _                      |

| IPUx_DISPx_DAT23            | DAT[23]                     | _             | —             | R[7]          |                             |                 | —                                | _                      |

| IPUx_DIx_DISP_CLK           |                             |               | <u> </u>      | PixCLK        | l                           | 1               | I                                | -                      |

| IPUx_DIx_PIN01              |                             |               |               |               |                             |                 | May be required for anti-tearing |                        |

| IPUx_DIx_PIN02              |                             | HSYNC         |               |               |                             |                 | _                                |                        |

| IPUx_DIx_PIN03              |                             | VSYNC         |               |               |                             |                 |                                  | VSYNC out              |

### Table 64. Video Signal Cross-Reference (continued)

| Symbol                                     | Parameters                | Test Conditions | Min | Тур | Max | Unit |  |  |  |

|--------------------------------------------|---------------------------|-----------------|-----|-----|-----|------|--|--|--|

| LP Line Receiver DC Specifications         |                           |                 |     |     |     |      |  |  |  |

| V <sub>IL</sub>                            | Input low voltage         | _               | —   | —   | 550 | mV   |  |  |  |

| V <sub>IH</sub>                            | Input high voltage        | _               | 920 | _   | _   | mV   |  |  |  |

| V <sub>HYST</sub>                          | Input hysteresis          | _               | 25  | _   | _   | mV   |  |  |  |

| Contention Line Receiver DC Specifications |                           |                 |     |     |     |      |  |  |  |

| V <sub>ILF</sub>                           | Input low fault threshold | _               | 200 | _   | 450 | mV   |  |  |  |

#### Table 68. Electrical and Timing Information (continued)

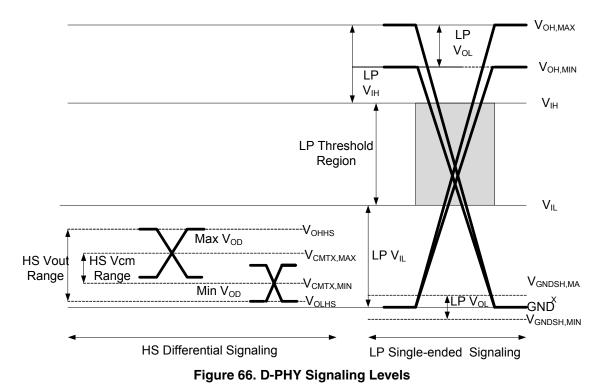

### 4.12.12.2 D-PHY Signaling Levels

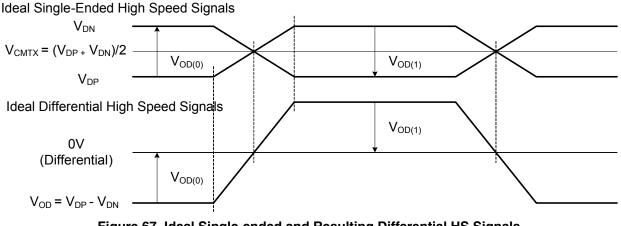

The signal levels are different for differential HS mode and single-ended LP mode. Figure 66 shows both the HS and LP signal levels on the left and right sides, respectively. The HS signalling levels are below the LP low-level input threshold such that LP receiver always detects low on HS signals.

# 4.12.12.3 HS Line Driver Characteristics

Figure 67. Ideal Single-ended and Resulting Differential HS Signals

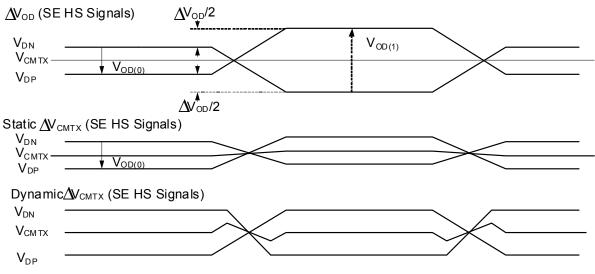

## 4.12.12.4 Possible $\triangle$ VCMTX and $\triangle$ VOD Distortions of the Single-ended HS Signals

Figure 68. Possible  $\triangle$ VCMTX and  $\triangle$ VOD Distortions of the Single-ended HS Signals

## 4.12.12.5 D-PHY Switching Characteristics

| Table 69. Electr | ical and Timing | Information |

|------------------|-----------------|-------------|

|------------------|-----------------|-------------|

| Symbol                            | Parameters                                   | Test Conditions                                          | Min | Тур | Мах  | Unit |  |  |  |

|-----------------------------------|----------------------------------------------|----------------------------------------------------------|-----|-----|------|------|--|--|--|

| HS Line Drivers AC Specifications |                                              |                                                          |     |     |      |      |  |  |  |

| _                                 | Maximum serial data rate (forward direction) | On DATAP/N outputs.<br>80 $\Omega$ <= RL <= 125 $\Omega$ | 80  | _   | 1000 | Mbps |  |  |  |

| F <sub>DDRCLK</sub>               | DDR CLK frequency                            | On DATAP/N outputs.                                      | 40  | _   | 500  | MHz  |  |  |  |

| P <sub>DDRCLK</sub>               | DDR CLK period                               | 80 Ω <= RL< = 125 Ω                                      | 2   |     | 25   | ns   |  |  |  |

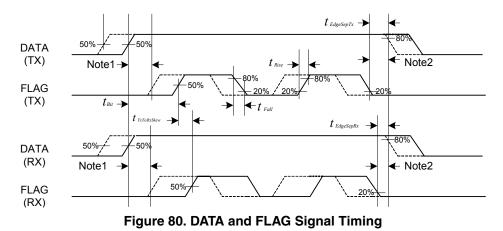

# 4.12.13.9 DATA and FLAG Signal Timing

# 4.12.14 MediaLB (MLB) Characteristics

### 4.12.14.1 MediaLB (MLB) DC Characteristics

Table 71 lists the MediaLB 3-pin interface electrical characteristics.

| Parameter                   | Symbol          | Test Conditions         | Min | Max | Unit |

|-----------------------------|-----------------|-------------------------|-----|-----|------|

| Maximum input voltage       | —               | —                       | —   | 3.6 | V    |

| Low level input threshold   | V <sub>IL</sub> | _                       | —   | 0.7 | V    |

| High level input threshold  | V <sub>IH</sub> | See Note <sup>1</sup>   | 1.8 | —   | V    |

| Low level output threshold  | V <sub>OL</sub> | I <sub>OL</sub> = 6 mA  | _   | 0.4 | V    |

| High level output threshold | V <sub>OH</sub> | I <sub>OH</sub> = –6 mA | 2.0 | —   | V    |

| Input leakage current       | ار              | $0 < V_{in} < VDD$      | —   | ±10 | μA   |

<sup>1</sup> Higher V<sub>IH</sub> thresholds can be used; however, the risks associated with less noise margin in the system must be evaluated and assumed by the customer.

Table 72 lists the MediaLB 6-pin interface electrical characteristics.

Table 72. MediaLB 6-Pin Interface Electrical DC Specifications

| Parameter                                                                                                                          | Symbol           | Test Conditions       | Min | Max | Unit |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-----|-----|------|--|--|--|--|

| Driver Characteristics                                                                                                             |                  |                       |     |     |      |  |  |  |  |

| Differential output voltage (steady-state): I $V_{O_{+}}$ - $V_{O_{-}}$ I                                                          | V <sub>OD</sub>  | See Note <sup>1</sup> | 300 | 500 | mV   |  |  |  |  |

| Difference in differential output voltage<br>between (high/low) steady-states:<br>I V <sub>OD, high</sub> - V <sub>OD, low</sub> I | ΔV <sub>OD</sub> | _                     | -50 | 50  | mV   |  |  |  |  |

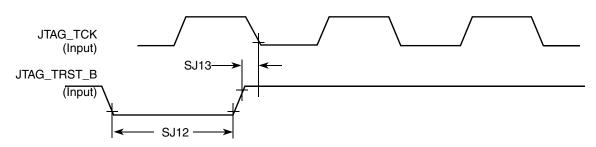

Figure 87. JTAG\_TRST\_B Timing Diagram

| ID   | Parameter <sup>1,2</sup>                                            | All Freq | All Frequencies |        |  |  |  |  |

|------|---------------------------------------------------------------------|----------|-----------------|--------|--|--|--|--|

|      |                                                                     | Min      | Max             | – Unit |  |  |  |  |

| SJ0  | JTAG_TCK frequency of operation 1/(3xT <sub>DC</sub> ) <sup>1</sup> | 0.001    | 22              | MHz    |  |  |  |  |

| SJ1  | JTAG_TCK cycle time in crystal mode                                 | 45       |                 | ns     |  |  |  |  |

| SJ2  | JTAG_TCK clock pulse width measured at $V_M^2$                      | 22.5     | _               | ns     |  |  |  |  |

| SJ3  | JTAG_TCK rise and fall times                                        | —        | 3               | ns     |  |  |  |  |

| SJ4  | Boundary scan input data set-up time                                | 5        | _               | ns     |  |  |  |  |

| SJ5  | Boundary scan input data hold time                                  | 24       | _               | ns     |  |  |  |  |

| SJ6  | JTAG_TCK low to output data valid                                   | —        | 40              | ns     |  |  |  |  |

| SJ7  | JTAG_TCK low to output high impedance                               | —        | 40              | ns     |  |  |  |  |

| SJ8  | JTAG_TMS, JTAG_TDI data set-up time                                 | 5        | _               | ns     |  |  |  |  |

| SJ9  | JTAG_TMS, JTAG_TDI data hold time                                   | 25       | _               | ns     |  |  |  |  |

| SJ10 | JTAG_TCK low to JTAG_TDO data valid                                 | —        | 44              | ns     |  |  |  |  |

| SJ11 | JTAG_TCK low to JTAG_TDO high impedance                             | —        | 44              | ns     |  |  |  |  |

| SJ12 | JTAG_TRST_B assert time                                             | 100      | —               | ns     |  |  |  |  |

| SJ13 | JTAG_TRST_B set-up time to JTAG_TCK low                             | 40       | —               | ns     |  |  |  |  |

| Tahlo | 79  | JTAG | Timing |

|-------|-----|------|--------|

| lable | 13. | JIAG | rinnig |

<sup>1</sup>  $T_{DC}$  = target frequency of SJC

<sup>2</sup>  $V_{M}$  = mid-point voltage

# 4.12.19 SPDIF Timing Parameters

The Sony/Philips Digital Interconnect Format (SPDIF) data is sent using the bi-phase marking code. When encoding, the SPDIF data signal is modulated by a clock that is twice the bit rate of the data signal.

Table 80 and Figure 88 and Figure 89 show SPDIF timing parameters for the Sony/Philips Digital Interconnect Format (SPDIF), including the timing of the modulating Rx clock (SPDIF\_SR\_CLK) for SPDIF in Rx mode and the timing of the modulating Tx clock (SPDIF\_ST\_CLK) for SPDIF in Tx mode.

NOTES:

1. ALL DIMENSIONS IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

3. MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

4. DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

<u>/5.</u>

PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

6. 21.2MM MAXIMUM PACKAGE ASSEMBLY (LID + LAMINATE) X AND Y.

| ©      | NXP SEMICONDUCTORS N.V.<br>ALL RIGHTS RESERVED | MECHANICAL OU       | TLINE                           | PRINT VERSION NOT | TO SCALE   |  |  |  |  |

|--------|------------------------------------------------|---------------------|---------------------------------|-------------------|------------|--|--|--|--|

| TITLE: | 624 I/O FC PB                                  | GA                  | DOCUMENT NO: 98ASA00330D REV: E |                   |            |  |  |  |  |

|        | 21 X 21 X 2 Pł                                 | STANDARD: NON-JEDEC |                                 |                   |            |  |  |  |  |

|        | 0.8 MM PITCH, STAM                             | PED LID             | SOT1643                         | -1 0              | 7 JAN 2016 |  |  |  |  |

Figure 101. 21 x 21 mm Lidded Package Top, Bottom, and Side Views (Sheet 2 of 2)

# 6.2.5 21 x 21 mm, 0.8 mm Pitch Ball Map

Table 98 shows the FCPBGA 21 x 21 mm, 0.8 mm pitch ball map.

|    | F        | 2          | З         | 4         | 5        | 9          | 7        | 8             | 6            | 10          | 11            | 12         | 13       | 14        | 15         | 16        | 17        | 18         | 19       | 20        | 21        | 22           | 23           | 24        | 25        |

|----|----------|------------|-----------|-----------|----------|------------|----------|---------------|--------------|-------------|---------------|------------|----------|-----------|------------|-----------|-----------|------------|----------|-----------|-----------|--------------|--------------|-----------|-----------|

| A  |          | PCIE_REXT  | PCIE_TXM  | GND       | FA_ANA   | USB_OTG_DP | XTALI    | GND           | MLB_SN       | MLB_DP      | MLB_CN        | SATA_TXP   | GND      | SATA_RXM  | SD3_DAT2   | NANDF_ALE | NANDF_CS2 | NANDF_D0   | NANDF_D4 | SD4_DAT3  | SD1_DAT0  | SD2_DAT0     | SD2_DAT2     | RGMII_TD3 | GND       |

| В  | PCIE_RXM | PCIE_RXP   | PCIE_TXP  | GND       | VDD_FA   | USB_OTG_DN | XTALO    | USB_OTG_CHD_B | MLB_SP       | MLB_DN      | MLB_CP        | SATA_TXM   | SD3_CMD  | SATA_RXP  | SD3_DAT3   | NANDF_RB0 | SD4_CMD   | NANDF_D5   | SD4_DAT1 | SD4_DAT6  | SD1_CMD   | SD2_DAT3     | RGMII_RD1    | RGMII_RD2 | RGMII_RXC |

| с  | GND      | JTAG_TRSTB | JTAG_TMS  | GND       | CLK2_N   | GND        | CLK1_N   | GPANAIO       | RTC_XTALO    | GND         | POR_B         | BOOT_MODE0 | SD3_DAT5 | SATA_REXT | NANDF_CLE  | NANDF_CS1 | NANDF_D1  | NANDF_D7   | SD4_DAT5 | SD1_DAT1  | SD2_CLK   | RGMII_TD0    | RGMII_TX_CTL | RGMII_RD0 | EIM_D16   |

| Q  | CSI_D1M  | CSI_D1P    | GND       | CSI_REXT  | CLK2_P   | GND        | CLK1_P   | GND           | RTC_XTALI    | USB_H1_VBUS | PMIC_ON_REQ   | ONOFF      | SD3_DAT4 | SD3_CLK   | SD3_RST    | NANDF_CS3 | NANDF_D3  | SD4_DAT0   | SD4_DAT7 | SD1_CLK   | RGMII_TXC | RGMII_RX_CTL | RGMII_RD3    | EIM_D18   | EIM_D23   |

| ш  | CSI_D2M  | CSI_D2P    | CSI_D0P   | CSI_DOM   | GND      | GND        | GND      | NVCC_PLL_OUT  | USB_OTG_VBUS | USB_H1_DP   | TAMPER        | TEST_MODE  | SD3_DAT6 | SD3_DAT0  | NANDF_WP_B | SD4_CLK   | NANDF_D6  | SD4_DAT4   | SD1_DAT2 | SD2_DAT1  | RGMII_TD2 | EIM_EB2      | EIM_D22      | EIM_D26   | EIM_D27   |

| L  | CSI_D3P  | CSI_D3M    | CSI_CLK0P | CSI_CLK0M | GND      | GND        | GND      | GND           | VDDUSB_CAP   | USB_H1_DN   | PMIC_STBY_REQ | BOOT_MODE1 | SD3_DAT7 | SD3_DAT1  | NANDF_CS0  | NANDF_D2  | SD4_DAT2  | SD1_DAT3   | SD2_CMD  | RGMII_TD1 | EIM_D17   | EIM_D24      | EIM_EB3      | EIM_A22   | EIM_A24   |

| IJ | DSI_D0P  | DSI_DOM    | GND       | DSI_REXT  | JTAG_TDI | JTAG_TDO   | PCIE_VPH | PCIE_VPTX     | VDD_SNVS_CAP | GND         | VDD_SNVS_DD   | SATA_VPH   | SATA_VP  | NVCC_SD3  | NVCC_NANDF | NVCC_SD1  | NVCC_SD2  | NVCC_RGMII | GND      | EIM_D20   | EIM_D19   | EIM_D25      | EIM_D28      | EIM_A17   | EIM_A19   |