Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                        |

|----------------------------|--------------------------------------------------------|

| Product Status             | Obsolete                                               |

| Core Processor             | 8051                                                   |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 12MHz                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                  |

| Number of I/O              | 14                                                     |

| Program Memory Size        | 8KB (8K x 8)                                           |

| Program Memory Type        | FLASH                                                  |

| EEPROM Size                | 512 x 8                                                |

| RAM Size                   | 256 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                            |

| Data Converters            | A/D 8x12b                                              |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                      |

| Mounting Type              | Surface Mount                                          |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                        |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z51f0811rfx |

|                            |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Z51F0811 Product Specification Zilog

- NAME

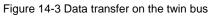

Figure 3-3 Z51F0811 20 TSSOP Pin assignment

# 7.11 DC Characteristics

Table 7-11 DC Characteristics

| Parameter                     | Symbol | Condition                                   | MIN    | TYP  | MAX              | Unit |

|-------------------------------|--------|---------------------------------------------|--------|------|------------------|------|

| Lowest Loves Malka and        | VIL1   | P2[2]                                       | -0.5   | -    | 0.2VDD           | V    |

| Input Low Voltage             | VIL2   | All others PAD                              | -0.5   | -    | 0.2VDD           | V    |

| Innut I ligh Voltage          | VIH1   | P2[2]                                       | 0.8VDD | -    | VDD              | V    |

| Input High Voltage            | VIH2   | All others PAD                              | 0.7VDD | -    | VDD              | V    |

| Output Low Voltage            | VOL1   | ALL I/O (IOL=20mA, VDD=4.5V)                | -      | -    | 1                | V    |

| Output High Voltage           | VOH1   | ALL I/O (IOH=-8.57mA, VDD=4.5V)             | 3.5    | -    | -                | V    |

| Input High Leakage<br>Current | ШΗ     | ALL PAD                                     | -      | -    | 1                | uA   |

| Input Low Leakage<br>Current  | IIL    | ALL PAD                                     | -1     | -    | -                | uA   |

| Pull-Up Resister              | RPU    | ALL PAD                                     | 20     | -    | 50               | kΩ   |

|                               | IDD1   | Run Mode, fXIN=12MHz @5V                    | -      | *2.6 | 10               | mA   |

|                               | IDD2   | Sleep Mode, fXIN=12MHz @5V                  | -      | *1.5 | 5                | mA   |

|                               | IDD3   | Sub Active Mode, fSUBXIN=32.768KHz @5V      | -      | *71  | 500              | uA   |

|                               | IDD4   | STOP1 Mode, WDT Active @5V (BOD enable)     | -      | *45  | 200              | uA   |

| Power Supply Current          | IDD5   | STOP1 Mode, WDT Active @5V (BOD disable)    | -      | *20  | 100              | uA   |

|                               | IDD6   | STOP2 Mode, WDT Disable @5V (BOD<br>enable) | -      | *27  | 100              | uA   |

|                               | IDD7   | STOP2 Mode, WDT Disable @5V (BOD disable)   | -      | *1   | 7 (room<br>temp) | uA   |

(VDD =2.7~5.5V, VSS =0V, fXIN=10.0MHz, TA=-40~+85℃)

Note) - STOP1: WDT running, STOP2: WDT disable.

- (\*) typical test condition : VDD=5V, Internal RC-OSC=8MHz, ROOM TEMP, all PORT output LOW, Timer0 Active, 1PORT toggling.

Z51F0811 Product Specification

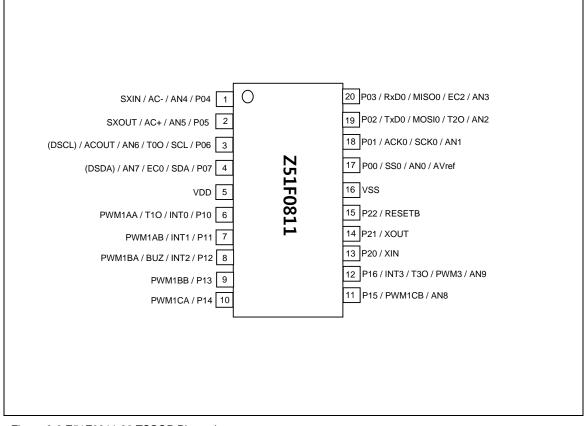

Figure 8-1 Program memory

- User Function Mode: 8KBytes Included Interrupt Vector Region

- Non-volatile and reprogramming memory: Flash memory based on EEPROM cell

Z51F0811 Product Specification

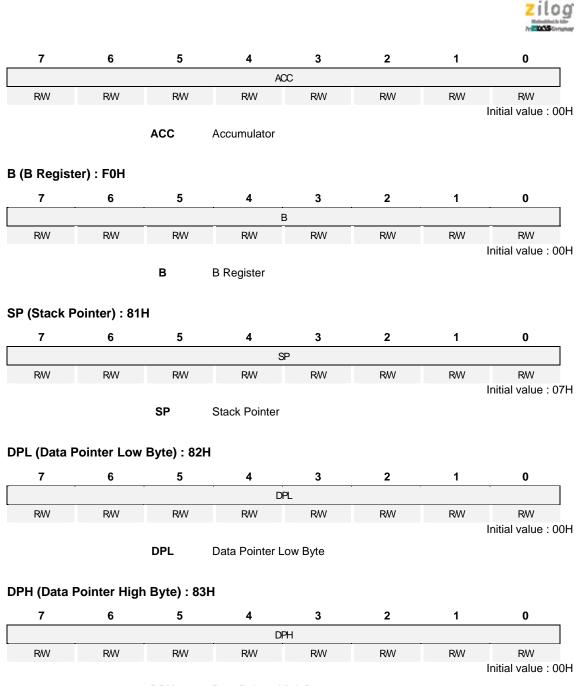

DPH Data Pointer High Byte

Z51F0811 Product Specification

zilog

| RW                 |

|----|----|----|----|----|----|----|--------------------|

|    |    |    |    |    |    |    | nitial value : 00H |

Px[7:0] I/O Data

### PxIO (Px Direction Register) : 89H, 91H, 99H, A1H

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0                | _  |

|-------|-------|-------|-------|-------|-------|-------|------------------|----|

| Px710 | Px6lO | Px5IO | Px4IO | Px3IO | Px210 | Px1IO | Px0IO            |    |

| RW               |    |

|       |       |       |       |       |       | I     | nitial value : 0 | ΟH |

PxIO[7:0] Px data I/O direction.

0 Input

1 Output

### PxPU (Px Pull-up Resistor Selection Register) : 2F00H ~ 2F03H

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0                |    |

|-------|-------|-------|-------|-------|-------|-------|------------------|----|

| Px7PU | Px6PU | Px5PU | Px4PU | Px3PU | Px2PU | Px1PU | Px0PU            | ĺ  |

| RW               |    |

|       |       |       |       |       |       | I     | nitial value : 0 | OН |

PxPU[7:0] Configure pull-up resistor of Px port

0 Disable

1 Enable

### PxOD (Px Open-drain Selection Register) : 2F0CH ~ 2F0FH

| 7     | 6     | 5        | 4             | 3              | 2     | 1     | 0                  |

|-------|-------|----------|---------------|----------------|-------|-------|--------------------|

| Px70D | Px6OD | Px5OD    | Px4OD         | Px3OD          | Px2OD | Px10D | Px0OD              |

| RW    | RW    | RW       | RW            | RW             | RW    | RW    | RW                 |

|       |       |          |               |                |       | I     | nitial value : 00H |

|       | P     | xOD[7:0] | Configure ope | en-drain of Px | port  |       |                    |

|       |       |          | 0 Disat       | ble            |       |       |                    |

|       |       |          | 1 Enab        | le             |       |       |                    |

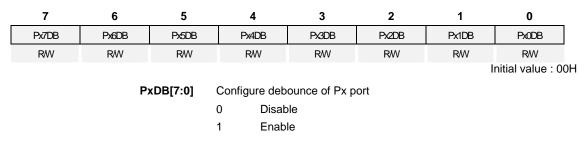

#### PxDB (Px Debounce Enable Register) : 2F18H ~ 2F1BH

### PCI0 (P0 Pin Change Interrupt Enable Register) : AEH

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PC107 | PC106 | PC105 | PC104 | PC103 | PCI02 | PC101 | PCI00 |

| RW    |

Initial value : 00H

#### 10.12.8 Register Map

| Name   | Address | Dir | Default | Description                                  |

|--------|---------|-----|---------|----------------------------------------------|

| IE     | A8H     | R/W | 00H     | Interrupt Enable Register                    |

| IE1    | A9H     | R/W | 00H     | Interrupt Enable Register 1                  |

| IE2    | ААН     | R/W | 00H     | Interrupt Enable Register 2                  |

| IE3    | ABH     | R/W | 00H     | Interrupt Enable Register 3                  |

| IE4    | ACH     | R/W | 00H     | Interrupt Enable Register 4                  |

| IE5    | ADH     | R/W | 00H     | Interrupt Enable Register 5                  |

| IP     | B8H     | R/W | 00H     | Interrupt Priority Register                  |

| IP1    | F8H     | R/W | 00H     | Interrupt Priority Register 1                |

| EIENAB | A3H     | R/W | 00H     | External Interrupt Enable Register           |

| EIFLAG | A4H     | R/W | 00H     | External Interrupt Flag Register             |

| EIEDGE | A5H     | R/W | 00H     | External Interrupt Edge Register             |

| EIPOLA | A6H     | R/W | 00H     | External Interrupt Polarity Register         |

| EIBOTH | A7H     | R/W | 00H     | External Interrupt Both Edge Enable Register |

Table 10-3 Register Map

# **10.13 Interrupt Register Description**

The Interrupt Register is used for controlling interrupt functions. Also it has External interrupt control registers. The interrupt register consists of Interrupt Enable Register (IE), Interrupt Enable Register 1 (IE1), Interrupt Enable Register 2 (IE2), Interrupt Enable Register 3 (IE3), Interrupt Enable Register 4 (IE4) and Interrupt Enable Register 5 (IE5). For external interrupt, it consists of External Interrupt Flag Register (EIFLAG), External Interrupt Edge Register (EIEDGE), External Interrupt Polarity Register (EIPOLA), External Interrupt Enable Register (EIENAB) and External Interrupt Both Edge Enable Register(EIBOTH).

#### 10.13.1 Register description for Interrupt

| 7          | 6   | 5     | 4              | 3                | 2              | 1        | 0                 |

|------------|-----|-------|----------------|------------------|----------------|----------|-------------------|

| EA         | -   | INT5E | INT4E          | INT3E            | INT2E          | INT1E    | INTOE             |

| RW         | -   | RW    | RW             | RW               | RW             | RW       | RW                |

|            |     |       |                |                  |                |          | nitial value : 00 |

|            |     | EA    | Enable or disa | ble all interrup | ot bits        |          |                   |

|            |     |       | 0 All In       | terrupt disable  | •              |          |                   |

|            |     |       | 1 All In       | terrupt enable   |                |          |                   |

|            |     | INT5E | Reserved       |                  |                |          |                   |

|            |     |       | 0 Disat        | ole              |                |          |                   |

|            |     |       | 1 Enab         | le               |                |          |                   |

|            |     | INT4E | Enable or disa | ble Pin Chang    | ge Interrupt 0 | (Port 0) |                   |

|            |     |       | 0 Disat        | ole              |                |          |                   |

|            |     |       | 1 Enab         | le               |                |          |                   |

|            |     | INT3E | Enable or disa | ble External I   | nterrupt 3     |          |                   |

|            |     |       | 0 Disat        | ole              |                |          |                   |

| PS020602-0 | 212 |       | PRELI          | MINARY           |                |          | E                 |

### IE (Interrupt Enable Register) : A8H

Level case:

- 0 When High level, Interrupt occurred (default)

- 1 When Low level, Interrupt occurred Edge case:

- 0 When Rising edge, Interrupt occurred (default)

- 1 When Falling edge, Interrupt occurred

#### EIENAB (External Interrupt Enable Register) : A3H

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|-------|-------|-------|-------|-------|-------|-------|-------|--|

| ENAB7 | ENAB6 | ENAB5 | ENAB4 | ENAB3 | ENAB2 | ENAB1 | ENAB0 |  |

| RW    |  |

Initial value : 00H

ENAB[7:0] Control External Interrupt

0 Disable (default)

1 Enable

#### EIBOTH (External Interrupt Both Edge Enable Register) : A7H

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0                |    |

|-------|-------|-------|-------|-------|-------|-------|------------------|----|

| BOTH7 | BOTH6 | BOTH5 | BOTH4 | BOTH3 | BOTH2 | BOTH1 | BOTH0            |    |

| RW               | -  |

|       |       |       |       |       |       | I     | nitial value : 0 | OH |

**BOTH[7:0]** Determines which type of interrupt may occur, EIBOTH or EIEDGE+EIPOLA. if EIBOTH is enable, EIEDGE and EIPOLA register value don't matter.

0 Disable (default)

1 Enable

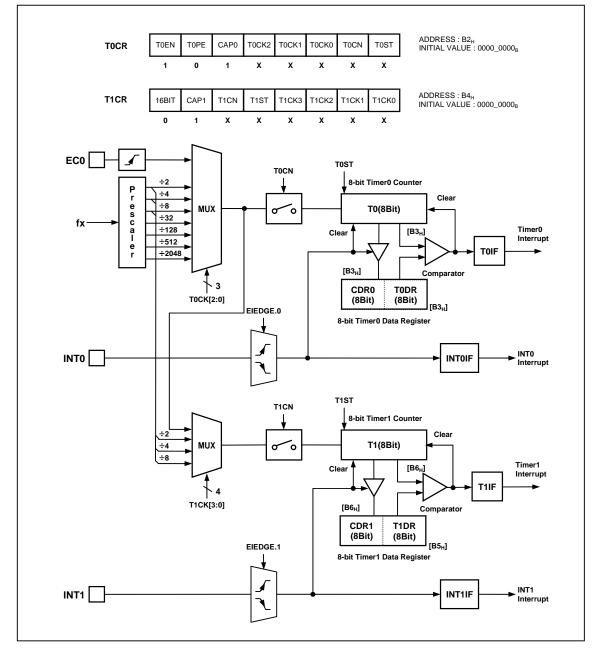

### 11.5 Timer/PWM

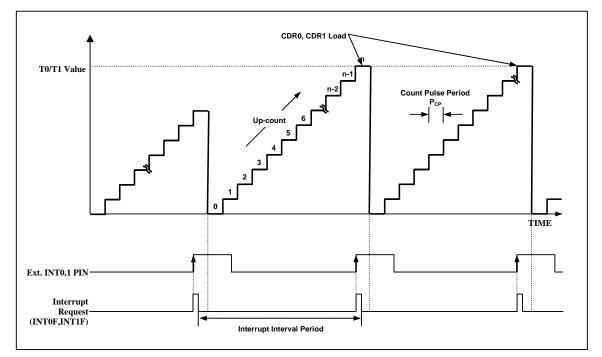

### 11.5.1 8-bit Timer/Event Counter 0, 1

### 11.5.1.1 Overview

Timer 0 and timer 1 can be used either two 8-bit timer/counter or one 16-bit timer/counter with combine them. Each 8-bit timer/event counter module has multiplexer, 8-bit timer data register, 8-bit counter register, mode register, input capture register, comparator. For PWM, it has PWM register (T1PPR, T1ADR, T1BDR, T1CDR, T1PCR, T1PCR2, T1PCR3, T1PHR, T1DLYA, T1DLYB, T1DLYC, T1ISR, T1IMSK).

It has seven operating modes:

- 8-bit timer/counter mode

- 8-bit capture mode

- 8-bit compare output mode

- 16-bit timer/counter mode

- 16-bit capture mode

- 16-bit compare output mode

- PWM mode

Note> TxDR must be set to higher than 0x03 for guaranteeing operation.

The timer/counter can be clocked by an internal or an external clock source (external EC0). The clock source is selected by clock select logic which is controlled by the clock select (T0CK[2:0], T1CK[3:0]). Also the timer/PWM/event counter 1 can use more clock sources than timer/event counter 0.

- TIMER0 clock source: fX/2, 4, 8, 32, 128, 512, 2048, EC0

- TIMER1 clock source: fX/1, 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024, 2048, 4096, 8192, 16384, T0CK

In the capture mode, by INT0, INT1, the data is captured into Input Capture Register. The timer 0 outputs the compare result to T0 port in 8/16-bit mode. Also the timer 1 outputs the result to T1 port in the timer mode and the PWM wave form to PWMA, PWMAB(bar), PWMB, PWMBB, PWMC, PWMCB Port(6-channel) in the PWM mode.

| 16 Bit | CAP0 | CAP1 | PWM1E | T0CK[2:0] | T1CK[3:0] | T0/1_PE | Timer 0             | Timer 1              |

|--------|------|------|-------|-----------|-----------|---------|---------------------|----------------------|

| 0      | 0    | 0    | 0     | XXX       | XXXX      | 00      | 8 Bit Timer         | 8 Bit Timer          |

| 0      | 0    | 1    | 0     | 111       | XXXX      | 00      | 8 Bit Event Counter | 8 Bit Capture        |

| 0      | 1    | 0    | 0     | XXX       | XXXX      | 01      | 8 Bit Capture       | 8 Bit Compare Output |

| 0      | 0    | 0    | 1     | XXX       | XXXX      | 11      | 8 Bit Timer/Counter | 10 Bit PWM           |

| 1      | 0    | 0    | 0     | XXX       | 1111      | 00      | 16 B                | it Timer             |

| 1      | 0    | 0    | 0     | 111       | 1111      | 00      | 16 Bit Ev           | ent Counter          |

| 1      | 1    | 1    | 0     | XXX       | 1111      | 00      | 16 Bit Capture      |                      |

| 1      | 0    | 0    | 0     | XXX       | 1111      | 01      | 16 Bit Con          | npare Output         |

Table 11-5 Timer 0,1 operating modes

Z51F0811 Product Specification Zilog

- WWW

Figure 11-10 8-bit Capture Mode for Timer 0, 1

# Z51F0811 **Product Specification** zilog

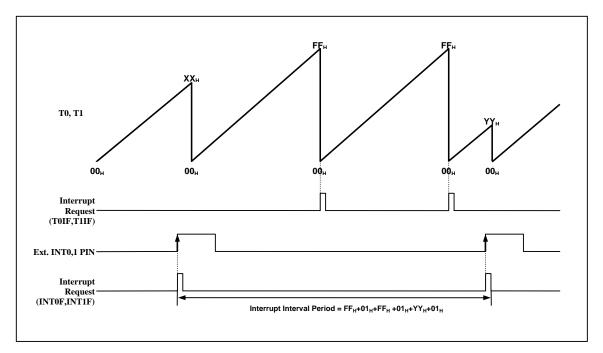

Figure 11-11 Input Capture Mode Operation of Timer 0, 1

Figure 11-12 Express Timer Overflow in Capture Mode

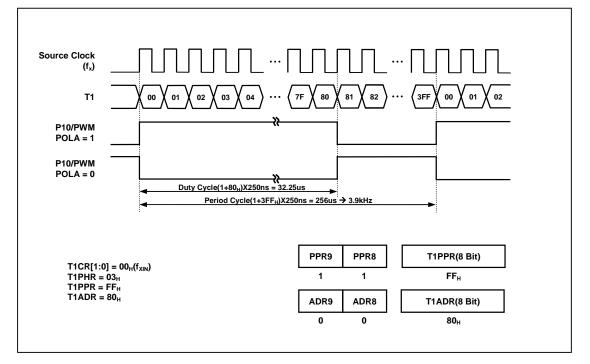

Figure 11-16 Example of PWM at 4MHz

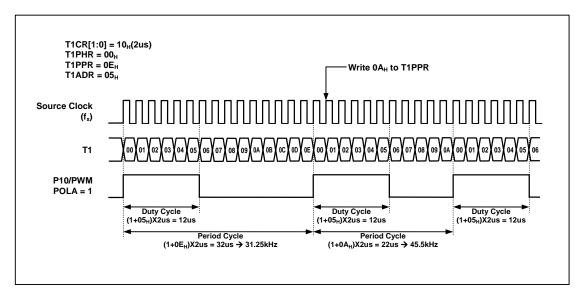

### Update period & duty register value at once

The period and duty of PWM comes to move from temporary registers to PPR (PWM Period Register) and PDR (PWM Duty Register) when always period match occurs. If you want that the period and duty is immediately changed, the UPDT bit in the T1PCR register must set to '1'. It should be noted that it needs the 3 cycle of timer clock for data transfer in the internal clock synchronization circuit. So the update data is written before 3 cycle of timer clock to get the right output waveform.

### Phase correction & Frequency correction

#### T0DR (Timer 0 Data Register: Write Case) : B3H

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0                 |

|------|------|------|------|------|------|------|-------------------|

| T0D7 | T0D6 | T0D5 | T0D4 | T0D3 | T0D2 | T0D1 | TODO              |

| W    | W    | W    | W    | W    | W    | W    | W                 |

|      |      |      |      |      |      | l    | nitial value : FF |

T0D[7:0] T0 Compare

# CDR0 (Capture 0 Data Register: Read Case, Capture mode only) : B3H

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0                 |    |

|-------|-------|-------|-------|-------|-------|-------|-------------------|----|

| CDR07 | CDR06 | CDR05 | CDR04 | CDR03 | CDR02 | CDR01 | CDR00             |    |

| R     | R     | R     | R     | R     | R     | R     | R                 |    |

|       |       |       |       |       |       | I     | nitial value : 00 | ЭН |

CDR0[7:0] T0 Capture

# T1CR (Timer 1 Mode Count Register) : B4H

| 7     | 6    | 5    | 4                                                        | 3                                                                      | 2         | 1               | 0                 |

|-------|------|------|----------------------------------------------------------|------------------------------------------------------------------------|-----------|-----------------|-------------------|

| 16BIT | CAP1 | T1CN | T1ST                                                     | T1CK3                                                                  | T1CK2     | T1CK1           | T1CK0             |

| RW    | RW   | RW   | RW                                                       | RW                                                                     | RW        | RW              | RW                |

|       |      | CAP1 | Select Timer 1<br>0 8 Bit<br>1 16 Bit<br>Control Timer 2 | operation mo                                                           |           |                 | Initial value : ( |

|       |      | T1CN | 1 Captur<br>Control Timer 7<br>0 Tempo                   | Counter mode<br>e mode<br>I Count pause<br>prary count sto<br>ue count | /continue |                 |                   |

|       | Ŧ    |      | Control Timer 7<br>0 Counte                              | l start/stop<br>er stop<br>counter and st                              |           | stom algely fro |                   |

|       |      |      |                                                          | CIOCK SOURCE.                                                          | -         | description     |                   |

|       |      |      | 0 0                                                      | 0                                                                      | 0         | fx              |                   |

|       |      |      | 0 0                                                      | 0                                                                      | 1         | fx/2            |                   |

|       |      |      | 0 0                                                      | 1                                                                      | 0         | fx/4            |                   |

|       |      |      | 0 0                                                      | 1                                                                      | 1         | fx/8            |                   |

|       |      |      | 0 1                                                      | 0                                                                      | 0         | fx/16           |                   |

|       |      |      | 0 1                                                      | 0                                                                      | 1         | fx/32           |                   |

|       |      |      | 0 1                                                      | 1                                                                      | 0         | fx/64           |                   |

|       |      |      | 0 1                                                      | 1                                                                      | 1         | fx/128          |                   |

|       |      |      | 1 0                                                      | 0                                                                      | 0         | fx/256          |                   |

|       |      |      | 1 0                                                      | 0                                                                      | 1         | fx/512          |                   |

|       |      |      | 1 0                                                      | 1                                                                      | 0         | fx/1024         |                   |

|       |      |      | 1 0                                                      | 1                                                                      | 1         | fx/2048         |                   |

|       |      |      | 1 1                                                      | 0                                                                      | 0         | fx/4096         |                   |

history and the second

### T1BDR (Timer 1 PWM 1B Duty Register) : BAH

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| PBD7 | PBD6 | PBD5 | PBD4 | PBD3 | PBD2 | PBD1 | PBD0 |

| RW   |

Initial value : 7FH

T1BDR[7:0] PWM 1B ch Duty Note) only write, when PWM1E '1'

T1CDR (Timer 1 PWM 1C Duty Register) : BBH

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0                  |

|------|------|------|------|------|------|------|--------------------|

| PCD7 | PCD6 | PCD5 | PCD4 | PCD3 | PCD2 | PCD1 | PCD0               |

| RW                 |

|      |      |      |      |      |      |      | nitial value : 7FI |

T1CDR[7:0] PWM 1C ch Duty

Note) only write, when PWM1E '1'

### T1PHR (Timer 1 PWM High Register) : BCH

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| ADR9 | ADR8 | BDR9 | BDR8 | CDR9 | CDR8 | PPR9 | PPR8 |

| RW   |

Initial value : 00H

:01

:0]

:0]

':01

| ADR[9:8] | F | PWM 1A Hig | gh (Bit [9:8] | ]) |         |

|----------|---|------------|---------------|----|---------|

| BDR[9:8] | F | PWM 1B Hig | gh (Bit [9:8] | ]) |         |

| CDR[9:8] | F | WM 1C Hig  | gh (Bit [9:8  | ]) |         |

| PPR[9:8] | F | PERIOD Hig | gh (Bit [9:8] | )  |         |

| PERIOD:  |   | PPR9       | PPR8          |    | T1PPR[7 |

| DUTY A:  |   | ADR9       | ADR8          |    | P1ADR[7 |

| DUTY B:  |   | BDR9       | BDR8          |    | P1BDR[7 |

| DUTY C:  |   | CDR9       | CDR8          |    | P1CDR[7 |

|          |   |            |               |    |         |

### T1PCR2 (Timer 1 PWM Control Register 2) : BDH

| 7     | 6     | 5    | 4     | 3    | 2     | 1    | 0                 |

|-------|-------|------|-------|------|-------|------|-------------------|

| FORCA | FORC6 | PAOE | PABOE | PBOE | PBBOE | PCOE | PCBOE             |

| RW    | RW    | RW   | RW    | RW   | RW    | RW   | RW                |

|       |       |      |       |      |       | I    | nitial value : 00 |

|       | -     |      |       |      | - I   |      |                   |

| FORCA | Contro | ol Force Drive A Channel mode                                             |

|-------|--------|---------------------------------------------------------------------------|

|       | 0      | Force Drive A Channel mode disable                                        |

|       | 1      | Force Drive A Channel mode enable                                         |

| FORC6 |        | ol Force 6 Channel mode<br>PAOE~PCBOE is effective when FORC6 sets to '1' |

|       | 0      | Force 6 Channel mode disable                                              |

|       | 1      | Force 6 Channel mode enable                                               |

| PAOE/ | Select | t Channel A/AB operation                                                  |

| PABOE | 0      | P1A (or P1AB) output disable                                              |

|       | 1      | P1A (or P1AB) output enable                                               |

| PBOE/ | Select | t Channel B/BB operation                                                  |

| PBBOE | 0      | P1B (or P1BB) output disable                                              |

|       | 1      | P1B (or P1BB) output enable                                               |

|       |        |                                                                           |

PRELIMINARY

Industrial to the

### T2DR (Timer 2 Data Register: Write Case) : C7H

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0                 |    |

|------|------|------|------|------|------|------|-------------------|----|

| T2D7 | T2D6 | T2D5 | T2D4 | T2D3 | T2D2 | T2D1 | T2D0              |    |

| W    | W    | W    | W    | W    | W    | W    | W                 |    |

|      |      |      |      |      |      | li   | nitial value : FF | ۶H |

T2D[7:0] T2 Compare data

### CDR2 (Capture 2 Data Register: Read Case) : C7H

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0                |    |

|-------|-------|-------|-------|-------|-------|-------|------------------|----|

| CDR27 | CDR26 | CDR25 | CDR24 | CDR23 | CDR22 | CDR21 | CDR20            |    |

| R     | R     | R     | R     | R     | R     | R     | R                |    |

|       |       |       |       |       |       | I     | nitial value : 0 | юн |

CDR2[7:0] T2 Capture data

### T3CR (Timer 3 Mode Count Register) : CAH

| 7   | 6     | 5         | 4                                                                   | 3               | 2                  | 1             | 0                 |  |  |

|-----|-------|-----------|---------------------------------------------------------------------|-----------------|--------------------|---------------|-------------------|--|--|

| POL | 16BIT | PWM3E     | CAF                                                                 | 3 T3Ck          | 1 T3CK0            | T3CN          | T3ST              |  |  |

| RW  | RW    | RW        | RW                                                                  | / RW            | RW                 | RW            | RW                |  |  |

|     |       |           |                                                                     |                 |                    |               | Initial value : 0 |  |  |

|     |       | POL       | Configure                                                           | PWM polarity    |                    |               |                   |  |  |

|     |       |           | 0 N                                                                 | legative (Duty  | Match: Clear)      |               |                   |  |  |

|     |       |           | 1 F                                                                 | ositive (Duty N | /latch: Set)       |               |                   |  |  |

|     |       | 16BIT     | Select Tir                                                          | ner 1 8/16Bit   |                    |               |                   |  |  |

|     |       |           | 0 8                                                                 | Bit             |                    |               |                   |  |  |

|     |       |           | 1 1                                                                 | 6 Bit           |                    |               |                   |  |  |

|     |       | PWM3E     | Control P                                                           | WM enable       |                    |               |                   |  |  |

|     |       |           | 0 F                                                                 | WM disable      |                    |               |                   |  |  |

|     |       |           | 1 F                                                                 | WM enable       |                    |               |                   |  |  |

|     |       | CAP3      |                                                                     | mer 3 mode      |                    |               |                   |  |  |

|     |       |           | 0 Т                                                                 | imer/Counter    | mode               |               |                   |  |  |

|     |       |           |                                                                     | apture mode     |                    |               |                   |  |  |

|     | 1     | T3CK[1:0] | Select clock source of Timer 3. Fx is the frequency of main system. |                 |                    |               |                   |  |  |

|     |       |           | T3CK1                                                               | T3CK0           | Description        |               |                   |  |  |

|     |       |           | 0                                                                   | 0               | fx                 |               |                   |  |  |

|     |       |           | 0                                                                   | 1               | fx/2               |               |                   |  |  |

|     |       |           | 1                                                                   | 0               | fx/16              |               |                   |  |  |

|     |       |           | 1                                                                   | 1               | Use Timer 2 Clo    |               |                   |  |  |

|     | Not   |           |                                                                     | -               | lock", you can set | T2EN bit in T | 2CR               |  |  |

|     |       | T3CN      |                                                                     | -               | ause/continue      |               |                   |  |  |

|     |       |           |                                                                     | emporary cou    | •                  |               |                   |  |  |

|     |       | TOOT      |                                                                     | Continue count  |                    |               |                   |  |  |

|     |       | T3ST      |                                                                     | mer 3 start/sto | q                  |               |                   |  |  |

|     |       |           |                                                                     | counter stop    |                    |               |                   |  |  |

|     |       |           | 1 C                                                                 | lear counter a  | nd start           |               |                   |  |  |

### T3DR (Timer 3 Data Register: Write Case) : CBH

#### 11.5.3.3 Register Map

| Name  | Address | Dir | Default | Description                   |

|-------|---------|-----|---------|-------------------------------|

| T4CR  | 0xCE    | R/W | 00H     | Timer 4 Mode Control Register |

| T4L   | 0xCF    | R   | 00H     | Timer 4 Low Register          |

| T4LDR | 0xCF    | W   | FFH     | Timer 4 Low Data Register     |

| LCDR4 | 0xCF    | R   | 00H     | Low Capture 4 Data Register   |

| T4H   | 0xD5    | R   | 00H     | Timer 4 High Register         |

| T4HDR | 0xD5    | R/W | 00H     | Timer 4 High Data Register    |

| HCDR4 | 0xD5    | R   | 00H     | High Capture 4 Data Register  |

Table 11-11 Register Map

# 11.5.3.4 Timer 4 Register description

The timer 4 register consists of Timer 4 Mode Control Register (T4CR), Timer 4 Low Register (T4L), Timer 4 Low Data Register (T4LDR), Low Capture 4 Data Register (LCDR4), Timer 4 High Register (T4H), Timer 4 High Data Register (T4HDR), High Capture 4 Data Register (HCDR4).

### 11.5.3.5 Register description for Timer 4

### T4CR (Timer 4 Mode Control Register) : CEH

| 7    | 6 | 5         |                                      | 4           | 3           | 2               | 1             | 0                  |  |  |

|------|---|-----------|--------------------------------------|-------------|-------------|-----------------|---------------|--------------------|--|--|

| T4EN | - | CAP4      | Ţ                                    | 4CK2        | T4CK1       | T4CK0           | T4CN          | T4ST               |  |  |

| RW   | - | RW        | 1                                    | RW          | RW          | RW              | RW            | RW                 |  |  |

|      |   |           |                                      |             |             |                 |               | Initial value : 00 |  |  |

|      |   | T4EN      | Control Timer 4 operation            |             |             |                 |               |                    |  |  |

|      |   |           | 0                                    | Timer 4 di  |             |                 |               |                    |  |  |

|      |   |           | 1 Timer 4 enable                     |             |             |                 |               |                    |  |  |

|      |   | CAP4      | Contro                               | Timer 4 m   | ode         |                 |               |                    |  |  |

|      |   |           | 0                                    | Timer/Cou   | unter mode  |                 |               |                    |  |  |

|      |   |           | 1                                    | Capture n   | node        |                 |               |                    |  |  |

|      |   | T4CK[2:0] | Select                               | Timer 4 clo | ck source.  | fx is main syst | em clock fred | quency             |  |  |

|      |   |           |                                      | T4CK1       | T4CK0       | Description     |               |                    |  |  |

|      |   |           | 0                                    | 0           | 0           | fx/2            |               |                    |  |  |

|      |   |           | 0                                    | 0           | 1           | fx/4            |               |                    |  |  |

|      |   |           | 0                                    | 1           | 0           | fx/8            |               |                    |  |  |

|      |   |           |                                      | 1           | 1           | fx/16           |               |                    |  |  |

|      |   |           | 1                                    | 0           | 0           | fx/64           |               |                    |  |  |

|      |   |           | 1                                    | 0           | 1           | fx/256          |               |                    |  |  |

|      |   |           | 1                                    | 1           | 0           | fx/1024         |               |                    |  |  |

|      |   |           | 1                                    | 1           | 1           | fx/2048         |               |                    |  |  |

|      |   | T4CN      | Control Timer 4 Count pause/continue |             |             |                 |               |                    |  |  |

|      |   |           | 0                                    |             | y count sto |                 |               |                    |  |  |

|      |   |           | 1                                    | Continue    | count       |                 |               |                    |  |  |

|      |   | T4ST      | Contro                               | Timer 4 sta | art/stop    |                 |               |                    |  |  |

|      | ~ |           |                                      |             |             |                 |               | 4.4                |  |  |

#### SPIDR (SPI Data Register) : D3H

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0                 |    |

|--------|--------|--------|--------|--------|--------|--------|-------------------|----|

| SPIDR7 | SPIDR6 | SPIDR5 | SPIDR4 | SPIDR3 | SPIDR2 | SPIDR1 | SPIDR0            |    |

| RW                |    |

|        |        |        |        |        |        | I      | nitial value : 00 | ЭН |

SPIDR [7:0]

SPI data register.

Although you only use reception, user must write any data in here to start the SPI operation.

#### SPISR (SPI Status Register) : D4H

| 7    | 6    | 5       | 4 | 3      | 2     | 1     | 0     |

|------|------|---------|---|--------|-------|-------|-------|

| TCIR | WCOL | SS_HIGH | - | TWOPIN | SSENA | TXENA | RXENA |

| R    | R    | RW      | - | RW     | RW    | RW    | RW    |

Initial value : 00H

| TCIR    | When a serial data transmission is complete, the TCIR bit is set. If the SPI interrupt is enabled, an interrupt is requested. And TCIR bit is cleared by hardware when executing the corresponding interrupt. If SPI interrupt is disable, TCIR bit is cleared when user read the status register SPISR, and then access (read/write) the data register SPIDR. |                                                                                                                                                                                        |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         | 0                                                                                                                                                                                                                                                                                                                                                              | Interrupt cleared                                                                                                                                                                      |  |  |  |

|         | 1                                                                                                                                                                                                                                                                                                                                                              | Transmission Complete and Interrupt Requested                                                                                                                                          |  |  |  |

| WCOL    | This b                                                                                                                                                                                                                                                                                                                                                         | it is set if the data register SPIDR is written during a data transfer.<br>it is cleared when user read the status register SPISR, and then<br>s (read/write) the data register SPIDR. |  |  |  |

|         | 0                                                                                                                                                                                                                                                                                                                                                              | No collision                                                                                                                                                                           |  |  |  |

|         | 1                                                                                                                                                                                                                                                                                                                                                              | Write Collision                                                                                                                                                                        |  |  |  |

| SS_HIGH | When SS pin is configured as input(master or slave), if 'HIGH'<br>come into SS pin, this flag bit will be set at the SS rising time. An<br>can clear it by writing '0'.<br>You can write only zero.                                                                                                                                                            |                                                                                                                                                                                        |  |  |  |

|         | 0                                                                                                                                                                                                                                                                                                                                                              | Flag is cleared                                                                                                                                                                        |  |  |  |

|         | 1                                                                                                                                                                                                                                                                                                                                                              | Flag is set                                                                                                                                                                            |  |  |  |

| TWOPIN  | This bi                                                                                                                                                                                                                                                                                                                                                        | it controls the 2 pin operation.                                                                                                                                                       |  |  |  |

|         | In mas                                                                                                                                                                                                                                                                                                                                                         | ster mode,                                                                                                                                                                             |  |  |  |

|         | 0                                                                                                                                                                                                                                                                                                                                                              | Disable                                                                                                                                                                                |  |  |  |

|         | 1                                                                                                                                                                                                                                                                                                                                                              | Enable                                                                                                                                                                                 |  |  |  |

| SSENA   | This bi                                                                                                                                                                                                                                                                                                                                                        | it controls the SS pin operation                                                                                                                                                       |  |  |  |

|         | 0                                                                                                                                                                                                                                                                                                                                                              | Disable                                                                                                                                                                                |  |  |  |

|         | 1                                                                                                                                                                                                                                                                                                                                                              | Enable                                                                                                                                                                                 |  |  |  |

| TXENA   | This bi                                                                                                                                                                                                                                                                                                                                                        | it controls a data transfer operation                                                                                                                                                  |  |  |  |

|         | 0                                                                                                                                                                                                                                                                                                                                                              | Disable                                                                                                                                                                                |  |  |  |

|         | 1                                                                                                                                                                                                                                                                                                                                                              | Enable                                                                                                                                                                                 |  |  |  |

| RXENA   | This bi                                                                                                                                                                                                                                                                                                                                                        | it controls a data reception operation                                                                                                                                                 |  |  |  |

|         | 0                                                                                                                                                                                                                                                                                                                                                              | Disable                                                                                                                                                                                |  |  |  |

|         | 1                                                                                                                                                                                                                                                                                                                                                              | Enable                                                                                                                                                                                 |  |  |  |

Note that if the MS is set to '0', when TWOPIN is set to '0', port 03 is set to MISO and if the MS is set to '0', when TWOPIN is set to '1', port 02 is set to MOSI. But if the MS is set to '1', when TWOPIN is set to '0', port 03 is set to MOSI and if the MS is set to '1', when TWOPIN is set to '1', port 02 is set to MISO.

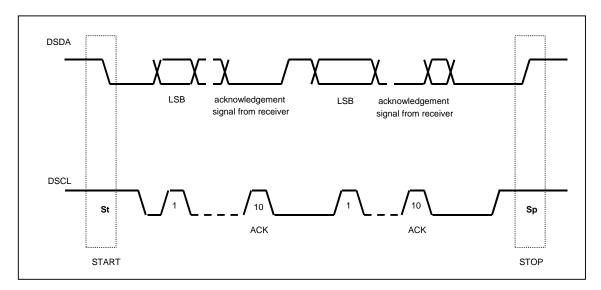

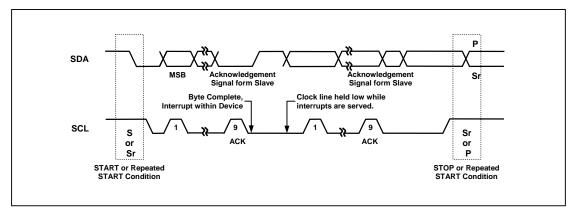

the most significant bit (MSB) first. If a slave can't receive or transmit another complete byte of data until it has performed some other function, it can hold the clock line SCL LOW to force the master into a wait state. Data transfer then continues when the slave is ready for another byte of data and releases clock line SCL.

Figure 11-54 STOP or Repeated START Condition

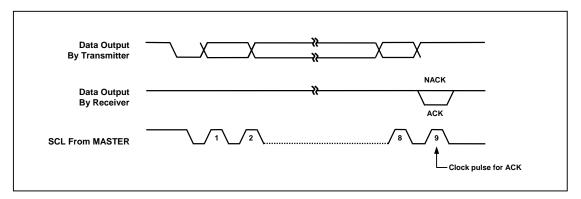

### 11.9.6 Acknowledge

The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse. When a slave is addressed by a master (Address Packet), and if it is unable to receive or transmit because it's performing some real time function, the data line must be left HIGH by the slave. And also, when a slave addressed by a master is unable to receive more data bits, the slave receiver must release the SDA line (Data Packet). The master can then generate either a STOP condition to abort the transfer, or a repeated START condition to start a new transfer.

If a master receiver is involved in a transfer, it must signal the end of data to the slave transmitter by not generating an acknowledge on the last byte that was clocked out of the slave. The slave transmitter must release the data line to allow the master to generate a STOP or repeated START condition.

Figure 11-55 Acknowledge on the I<sup>2</sup>C-Bus

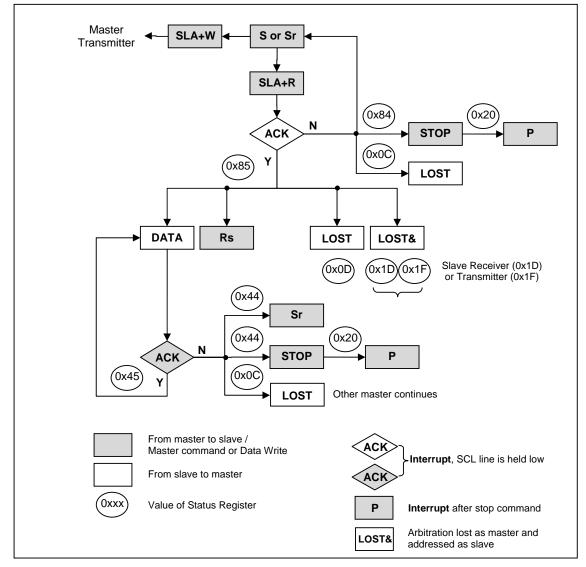

load SLA+R/W into the I2CDR and set the START bit in I2CMR.

After doing one of the actions above, write arbitrary value to I2CSR to release SCL line. In case of 1) and 2), move to step 7. In case of 3), move to step 9 to handle STOP interrupt. In case of 4), move to step 6 after transmitting the data in I2CDR, and if transfer direction bit is '0' go to master transmitter section.

This is the final step for master receiver function of I<sup>2</sup>C, handling STOP interrupt. The STOP bit indicates that data transfer between master and slave is over. To clear I2CSR, write arbitrary value to I2CSR. After this, I<sup>2</sup>C enters idle state.

The processes described above for master receiver operation of I<sup>2</sup>C can be depicted as the following figure.

Figure 11-59 Formats and States in the Master Receiver Mode

|            | 0                                                                                            | No detection |             |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------|--------------|-------------|--|--|--|--|

|            | 1                                                                                            | Detection    |             |  |  |  |  |

| EXTRF      | External Reset flag bit. The bit is reset by writing '0' to this bit or b ON reset.          |              |             |  |  |  |  |

|            | 0                                                                                            | No detection |             |  |  |  |  |

|            | 1                                                                                            | Detection    |             |  |  |  |  |

| WDTRF      | Watch Dog Reset flag bit. The bit is reset by writing '0' to this bit or Power ON reset.     |              |             |  |  |  |  |

|            | 0                                                                                            | No detection |             |  |  |  |  |

|            | 1                                                                                            | Detection    |             |  |  |  |  |

| OCDRF      | On-Chip Debug Reset flag bit. The bit is reset by writing '0' to this bit on Power ON reset. |              |             |  |  |  |  |

|            | 0                                                                                            | No detection |             |  |  |  |  |

|            | 1                                                                                            | Detection    |             |  |  |  |  |

| BODRF      | Brown-Out Reset flag bit. The bit is reset by writing '0' to this bit of Power ON reset.     |              |             |  |  |  |  |

|            | 0                                                                                            | No detection |             |  |  |  |  |

|            | 1                                                                                            | Detection    |             |  |  |  |  |

| BODLS[1:0] | BOD I                                                                                        | evel Voltage |             |  |  |  |  |

|            | BODL                                                                                         | S1 BODLS0    | Description |  |  |  |  |

|            | 0                                                                                            | 0            | 1.6V        |  |  |  |  |

|            | 0                                                                                            | 1            | 2.5V        |  |  |  |  |

|            | 1                                                                                            | 0            | 3.6V        |  |  |  |  |

|            | 1                                                                                            | 1            | 4.2V        |  |  |  |  |

| BODEN      | BOD op                                                                                       | peration     |             |  |  |  |  |

|            | 0                                                                                            | BOD disable  |             |  |  |  |  |

|            | 1                                                                                            | BOD enable   |             |  |  |  |  |

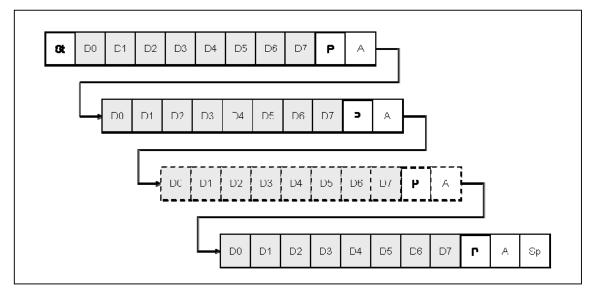

Figure 14-2 10-bit transmission packet

### 14.2.2 Packet transmission timing

### 14.2.2.1 Data transfer