# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 120MHz                                                                    |

| Connectivity               | CANbus, Ethernet, IrDA, MMC/SD, SPI, UART/USART, USB                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 79                                                                        |

| Program Memory Size        | 1MB (1M × 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-LQFP                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4e16cb-anr |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 21.3.3 Entering Parallel Programming Mode

The following algorithm puts the device in Parallel Programming mode:

- 1. Apply the supplies as described in Table 21-1.

- 2. If an external clock is available, apply it to XIN within the VDDCORE POR reset time-out period, as defined in the section "Electrical Characteristics".

- 3. Wait for the end of this reset period.

- 4. Start a read or write handshaking.

### 21.3.4 Programmer Handshaking

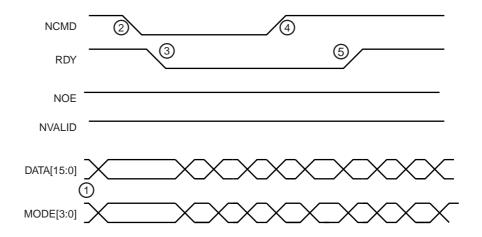

A handshake is defined for read and write operations. When the device is ready to start a new operation (RDY signal set), the programmer starts the handshake by clearing the NCMD signal. The handshaking is completed once the NCMD signal is high and RDY is high.

#### 21.3.4.1 Write Handshaking

For details on the write handshaking sequence, refer to Figure 21-2 and Table 21-4.

#### Figure 21-2. Parallel Programming Timing, Write Sequence

#### Table 21-4. Write Handshake

| Step | Programmer Action              | Device Action                        | Data I/O |

|------|--------------------------------|--------------------------------------|----------|

| 1    | Sets MODE and DATA signals     | Waits for NCMD low                   | Input    |

| 2    | Clears NCMD signal             | Latches MODE and DATA                | Input    |

| 3    | Waits for RDY low              | Clears RDY signal                    | Input    |

| 4    | Releases MODE and DATA signals | Executes command and polls NCMD high | Input    |

| 5    | Sets NCMD signal               | Executes command and polls NCMD high | Input    |

| 6    | Waits for RDY high             | Sets RDY                             | Input    |

#### 21.3.4.2 Read Handshaking

For details on the read handshaking sequence, refer to Figure 21-3 and Table 21-5.

| 24.12.4  | Bus Matrix Master Remap Control Register |            |      |      |      |      |      |  |  |  |

|----------|------------------------------------------|------------|------|------|------|------|------|--|--|--|

| Name:    | MATRIX_MRCR                              |            |      |      |      |      |      |  |  |  |

| Address: | 0x400E0300                               | 0x400E0300 |      |      |      |      |      |  |  |  |

| Access:  | Read-write                               |            |      |      |      |      |      |  |  |  |

| 31       | 30                                       | 29         | 28   | 27   | 26   | 25   | 24   |  |  |  |

| _        | -                                        | -          | -    | -    | -    | -    | -    |  |  |  |

| 23       | 22                                       | 21         | 20   | 19   | 18   | 17   | 16   |  |  |  |

| -        | -                                        | -          | -    | -    | -    | -    | -    |  |  |  |

| 15       | 14                                       | 13         | 12   | 11   | 10   | 9    | 8    |  |  |  |

| -        | -                                        | -          | -    | -    | -    | -    | -    |  |  |  |

| 7        | 6                                        | 5          | 4    | 3    | 2    | 1    | 0    |  |  |  |

| -        | RCB6                                     | RCB5       | RCB4 | RCB3 | RCB2 | RCB1 | RCB0 |  |  |  |

This register can only be written if the WPEN bit is cleared in the "Write Protect Mode Register" .

# RCBx: Remap Command Bit for Master x

0: Disable remapped address decoding for the selected Master

1: Enable remapped address decoding for the selected Master

# 25.8.8 DMAC Error, Buffer Transfer and Chained Buffer Transfer Interrupt Mask Register

| Name:    | DMAC_EBCIMR |    |    |       |       |       |       |  |

|----------|-------------|----|----|-------|-------|-------|-------|--|

| Address: | 0x400C0020  |    |    |       |       |       |       |  |

| Access:  | Read-only   |    |    |       |       |       |       |  |

| 31       | 30          | 29 | 28 | 27    | 26    | 25    | 24    |  |

| _        | -           | -  | _  | -     | -     | -     | -     |  |

|          |             | -  | -  |       |       |       | -     |  |

| 23       | 22          | 21 | 20 | 19    | 18    | 17    | 16    |  |

| _        | -           | -  | -  | ERR3  | ERR2  | ERR1  | ERR0  |  |

|          |             | -  | -  |       |       |       | -     |  |

| 15       | 14          | 13 | 12 | 11    | 10    | 9     | 8     |  |

| -        | -           | —  | -  | CBTC3 | CBTC2 | CBTC1 | CBTC0 |  |

|          |             |    |    |       |       |       |       |  |

| 7        | 6           | 5  | 4  | 3     | 2     | 1     | 0     |  |

| -        | —           | _  | _  | BTC3  | BTC2  | BTC1  | BTC0  |  |

# • BTCx: Buffer Transfer Completed [3:0]

0: Buffer Transfer Completed Interrupt is disabled for channel i.

1: Buffer Transfer Completed Interrupt is enabled for channel i.

### • CBTCx: Chained Buffer Transfer Completed [3:0]

- 0: Chained Buffer Transfer interrupt is disabled for channel i.

- 1: Chained Buffer Transfer interrupt is enabled for channel i.

# • ERRx: Access Error [3:0]

- 0: Transfer Error Interrupt is disabled for channel i.

- 1: Transfer Error Interrupt is enabled for channel i.

# 31.9.1 CAN Mode Register

Name: CAN\_MR

Address: 0x40010000 (0), 0x40014000 (1)

Access: Read/Write

| 31   | 30     | 29  | 28   | 27  | 26  | 25  | 24    |

|------|--------|-----|------|-----|-----|-----|-------|

| -    | -      | -   | -    | -   | -   | -   | -     |

| 23   | 22     | 21  | 20   | 19  | 18  | 17  | 16    |

| -    | -      | _   | -    | -   | -   | -   | -     |

| 15   | 14     | 13  | 12   | 11  | 10  | 9   | 8     |

| -    | —      | -   | -    | —   | —   | -   | -     |

| 7    | 6      | 5   | 4    | 3   | 2   | 1   | 0     |

| DRPT | TIMFRZ | TTM | TEOF | OVL | ABM | LPM | CANEN |

This register can only be written if the WPEN bit is cleared in the CAN Write Protection Mode Register.

# CANEN: CAN Controller Enable

0: The CAN Controller is disabled.

1: The CAN Controller is enabled.

# • LPM: Disable/Enable Low-power Mode

0: Disable Low-power mode.

1: Enable Low-power mode.

CAN controller enters Low-power mode once all pending messages have been transmitted.

# • ABM: Disable/Enable Autobaud/Listen mode

0: Disable Autobaud/listen mode.

1: Enable Autobaud/listen mode.

# • OVL: Disable/Enable Overload Frame

0: No overload frame is generated.

1: An overload frame is generated after each successful reception for mailboxes configured in Receive with/without overwrite Mode, Producer and Consumer.

# • TEOF: Timestamp messages at each end of Frame

0: The value of CAN\_TIM is captured in the CAN\_TIMESTP register at each Start Of Frame.

1: The value of CAN\_TIM is captured in the CAN\_TIMESTP register at each End Of Frame.

# • TTM: Disable/Enable Time Triggered Mode

0: Time Triggered Mode is disabled.

1: Time Triggered Mode is enabled.

# • TIMFRZ: Enable Timer Freeze

0: The internal timer continues to be incremented after it reached 0xFFFF.

1: The internal timer stops incrementing after reaching 0xFFFF. It is restarted after a timer reset. See "Freezing the Internal Timer Counter" on page 667.

# 33.6.36 PIO Additional Interrupt Modes Enable Register

# Name: PIO\_AIMER

Address:

0x400E0EB0 (PIOA), 0x400E10B0 (PIOB), 0x400E12B0 (PIOC), 0x400E14B0 (PIOD), 0x400E16B0 (PIOE)

Access:

Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

# • P0–P31: Additional Interrupt Modes Enable

0: No effect.

1: The interrupt source is the event described in PIO\_ELSR and PIO\_FRLHSR.

# 33.6.45 PIO Lock Status Register

# Name: PIO\_LOCKSR

Address:

0x400E0EE0 (PIOA), 0x400E10E0 (PIOB), 0x400E12E0 (PIOC), 0x400E14E0 (PIOD), 0x400E16E0 (PIOE)

Access:

Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

# • P0–P31: Lock Status

0: The I/O line is not locked.

1: The I/O line is locked.

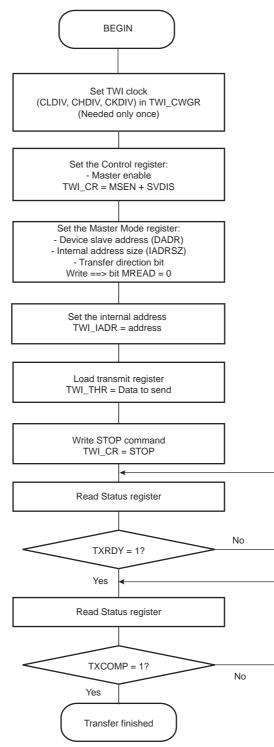

Figure 35-15. TWI Write Operation with Single Data Byte and Internal Address

Atmel

| 35.8.11  | TWI Transmit Holding Register |              |     |     |    |    |    |  |  |

|----------|-------------------------------|--------------|-----|-----|----|----|----|--|--|

| Name:    | TWI_THR                       | TWI_THR      |     |     |    |    |    |  |  |

| Address: | 0x400A8034 (0)                | , 0x400AC034 | (1) |     |    |    |    |  |  |

| Access:  | Write-only                    |              |     |     |    |    |    |  |  |

| 31       | 30                            | 29           | 28  | 27  | 26 | 25 | 24 |  |  |

| -        | -                             | -            | -   | -   | -  | -  | -  |  |  |

| 23       | 22                            | 21           | 20  | 19  | 18 | 17 | 16 |  |  |

| _        | -                             | _            | _   | _   | _  | _  | -  |  |  |

| 15       | 14                            | 13           | 12  | 11  | 10 | 9  | 8  |  |  |

| -        | -                             | -            | —   | _   | -  | _  | -  |  |  |

| 7        | 6                             | 5            | 4   | 3   | 2  | 1  | 0  |  |  |

|          |                               |              | TXD | AIA |    |    |    |  |  |

• TXDATA: Master or Slave Transmit Holding Data

# 38.6.19 Register Write Protection

To prevent any single software error from corrupting TC behavior, certain registers in the address space can be write-protected by setting the WPEN bit in the TC Write Protection Mode Register (TC\_WPMR).

The Timer Counter clock of the first channel must be enabled to access TC\_WPMR. The following registers can be write-protected:

- TC Block Mode Register

- TC Channel Mode Register: Capture Mode

- TC Channel Mode Register: Waveform Mode

- TC Fault Mode Register

- TC Stepper Motor Mode Register

- TC Register A

- TC Register B

- TC Register C

- TC Extended Mode Register

# 38.7 Timer Counter (TC) User Interface

#### Offset<sup>(1)</sup> Register Name Access Reset 0x00 + channel \* 0x40 + 0x00 **Channel Control Register** TC\_CCR Write-only \_ 0x00 + channel \* 0x40 + 0x04 **Channel Mode Register** TC\_CMR Read/Write 0 0 0x00 + channel \* 0x40 + 0x08 Stepper Motor Mode Register TC\_SMMR Read/Write 0x00 + channel \* 0x40 + 0x0C Register AB TC\_RAB Read-only 0 **Counter Value** 0 0x00 + channel \* 0x40 + 0x10 TC\_CV Read-only Read/Write<sup>(2)</sup> 0 0x00 + channel \* 0x40 + 0x14 Register A TC\_RA Read/Write<sup>(2)</sup> 0x00 + channel \* 0x40 + 0x18 Register B TC\_RB 0 Read/Write 0 0x00 + channel \* 0x40 + 0x1C Register C TC\_RC 0x00 + channel \* 0x40 + 0x20 Status Register TC SR Read-only 0 0x00 + channel \* 0x40 + 0x24 Interrupt Enable Register TC\_IER Write-only \_ 0x00 + channel \* 0x40 + 0x28 Interrupt Disable Register TC\_IDR Write-only \_ 0x00 + channel \* 0x40 + 0x2C Interrupt Mask Register TC\_IMR Read-only 0 0x00 + channel \* 0x40 + 0x30 TC\_EMR Read/Write 0 Extended Mode Register 0xC0 **Block Control Register** TC\_BCR Write-only \_ 0xC4 TC\_BMR Read/Write 0 Block Mode Register 0xC8 **QDEC Interrupt Enable Register** TC\_QIER Write-only \_ 0xCC **QDEC** Interrupt Disable Register TC\_QIDR Write-only \_ 0xD0 **QDEC Interrupt Mask Register** TC\_QIMR Read-only 0 0xD4 TC\_QISR 0 QDEC Interrupt Status Register Read-only 0xD8 Fault Mode Register TC\_FMR Read/Write 0 0xE4 Write Protection Mode Register TC\_WPMR Read/Write 0 0xE8-0xFC Reserved \_

\_

\_

Reserved for PDC Registers

#### Table 38-6.Register Mapping

Notes: 1. Channel index ranges from 0 to 2.

0x100-0x1A4

2. Read-only if TC\_CMRx.WAVE = 0

# • ETRGS: External Trigger

0: The External Trigger Interrupt is disabled.

1: The External Trigger Interrupt is enabled.

# • ENDRX: End of Receiver Transfer

0: The PDC Receive End of Transfer Interrupt is disabled.

1: The PDC Receive End of Transfer Interrupt is enabled.

# • RXBUFF: Reception Buffer Full

0: The PDC Receive Buffer Full Interrupt is disabled.

1: The PDC Receive Buffer Full Interrupt is enabled.

|         | 0       |                             |

|---------|---------|-----------------------------|

| FPZH/Lx | FPVH/Lx | Forcing Value of PWMH/Lx    |

| 0       | 0       | 0                           |

| 0       | 1       | 1                           |

| 1       | _       | High impedance state (Hi-Z) |

#### Table 39-3. Forcing Values of PWM Outputs by Fault Protection

#### CAUTION:

- To prevent any unexpected activation of the status flag FSy in PWM\_FSR, the FMODy bit can be set to '1' only if the FPOLy bit has been previously configured to its final value.

- To prevent any unexpected activation of the Fault Protection on the channel x, the bit FPEx[y] can be set to '1' only if the FPOLy bit has been previously configured to its final value.

If a comparison unit is enabled (see Section 39.6.3 "PWM Comparison Units") and if a fault is triggered in the channel 0, then the comparison cannot match.

As soon as the fault protection is triggered on a channel, an interrupt (different from the interrupt generated at the end of the PWM period) can be generated but only if it is enabled and not masked. The interrupt is reset by reading the interrupt status register, even if the fault which has caused the trigger of the fault protection is kept active.

#### 39.6.2.8 Spread Spectrum Counter

The PWM macrocell includes a spread spectrum counter allowing the generation of a constantly varying duty cycle on the output PWM waveform (only for the channel 0). This feature may be useful to minimize electromagnetic interference or to reduce the acoustic noise of a PWM driven motor.

This is achieved by varying the effective period in a range defined by a spread spectrum value which is programmed by the field SPRD in the PWM Spread Spectrum Register (PWM\_SSPR). The effective period of the output waveform is the value of the spread spectrum counter added to the programmed waveform period CPRD in the PWM Channel Period Register (PWM\_CPRD0).

It will cause the effective period to vary from CPRD-SPRD to CPRD+SPRD. This leads to a constantly varying duty cycle on the PWM output waveform because the duty cycle value programmed is unchanged.

The value of the spread spectrum counter can change in two ways depending on the bit SPRDM in PWM\_SSPR.

If SPRDM = 0, the Triangular mode is selected. The spread spectrum counter starts to count from -SPRD when the channel 0 is enabled or after reset and counts upwards at each period of the channel counter. When it reaches SPRD, it restarts to count from -SPRD again.

If SPRDM = 1, the Random mode is selected. A new random value is assigned to the spread spectrum counter at each period of the channel counter. This random value is between -SPRD and +SPRD and is uniformly distributed.

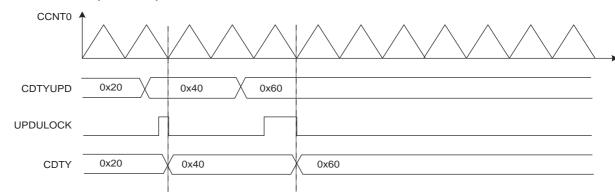

- 3. Enable the synchronous channels by writing CHID0 in the PWM\_ENA register.

- 4. If an update of the period value and/or the duty-cycle values and/or the dead-time values is required, write registers that need to be updated (PWM\_CPRDUPDx, PWM\_CDTYUPDx and PWM\_DTUPDx).

- 5. Set UPDULOCK to '1' in PWM\_SCUC.

- 6. The update of the registers will occur at the beginning of the next PWM period. When the UPDULOCK bit is reset, go to Step 4. for new values.

### Figure 39-13. Method 1 (UPDM = 0)

### Method 2: Manual write of duty-cycle values and automatic trigger of the update

In this mode, the update of the period value, the duty-cycle values, the dead-time values and the update period value must be done by writing in their respective update registers with the processor (respectively PWM\_CPRDUPDx, PWM\_CDTYUPDx, PWM\_DTUPDx and PWM\_SCUPUPD).

To trigger the update of the period value and the dead-time values, the user must use the bit UPDULOCK in the PWM\_SCUC register, which updates synchronously (at the same PWM period) the synchronous channels:

- If the bit UPDULOCK is set to '1', the update is done at the next PWM period of the synchronous channels.

- If the UPDULOCK bit is not set to '1', the update is locked and cannot be performed.

After writing the UPDULOCK bit to '1', it is held at this value until the update occurs, then it is read 0.

The update of the duty-cycle values and the update period is triggered automatically after an update period.

To configure the automatic update, the user must define a value for the update period by the UPR field in the PWM\_SCUP register. The PWM controller waits UPR+1 period of synchronous channels before updating automatically the duty values and the update period value.

The status of the duty-cycle value write is reported in the PWM Interrupt Status Register 2 (PWM\_ISR2) by the following flags:

• WRDY: this flag is set to '1' when the PWM Controller is ready to receive new duty-cycle values and a new update period value. It is reset to '0' when the PWM\_ISR2 register is read.

Depending on the interrupt mask in the PWM Interrupt Mask Register 2 (PWM\_IMR2), an interrupt can be generated by these flags.

Sequence for Method 2:

- 1. Select the manual write of duty-cycle values and the automatic update by setting the field UPDM to '1' in the PWM\_SCM register

- 2. Define the synchronous channels by the bits SYNCx in the PWM\_SCM register.

- 3. Define the update period by the field UPR in the PWM\_SCUP register.

- 4. Enable the synchronous channels by writing CHID0 in the PWM\_ENA register.

- 5. If an update of the period value and/or of the dead-time values is required, write registers that need to be updated (PWM\_CPRDUPDx, PWM\_DTUPDx), else go to Step 8.

| 39.7.18 | PWM Output Override Value Register |    |    |       |       |       |       |  |

|---------|------------------------------------|----|----|-------|-------|-------|-------|--|

| Name:   | PWM_OOV                            |    |    |       |       |       |       |  |

| Access: | Read/Write                         |    |    |       |       |       |       |  |

| 31      | 30                                 | 29 | 28 | 27    | 26    | 25    | 24    |  |

| -       | -                                  | -  | -  | -     | -     | -     | -     |  |

| 23      | 22                                 | 21 | 20 | 19    | 18    | 17    | 16    |  |

| -       | -                                  | _  | _  | OOVL3 | OOVL2 | OOVL1 | OOVL0 |  |

| 15      | 14                                 | 13 | 12 | 11    | 10    | 9     | 8     |  |

| -       | -                                  | —  | —  | —     | -     | -     | -     |  |

| 7       | 6                                  | 5  | 4  | 3     | 2     | 1     | 0     |  |

| -       | -                                  | -  | -  | OOVH3 | OOVH2 | OOVH1 | OOVH0 |  |

# • OOVHx: Output Override Value for PWMH output of the channel x

0: Override value is 0 for PWMH output of channel x.

1: Override value is 1 for PWMH output of channel x.

# • OOVLx: Output Override Value for PWML output of the channel x

0: Override value is 0 for PWML output of channel x.

1: Override value is 1 for PWML output of channel x.

| 40.14.9  | HSMCI Response Register |    |    |    |    |    |    |  |

|----------|-------------------------|----|----|----|----|----|----|--|

| Name:    | HSMCI_RSPR              |    |    |    |    |    |    |  |

| Address: | 0x40080020              |    |    |    |    |    |    |  |

| Access:  | Read-only               |    |    |    |    |    |    |  |

| 31       | 30                      | 29 | 28 | 27 | 26 | 25 | 24 |  |

|          |                         |    | R  | SP |    |    |    |  |

| 23       | 22                      | 21 | 20 | 19 | 18 | 17 | 16 |  |

|          |                         |    | R  | SP |    |    |    |  |

| 15       | 14                      | 13 | 12 | 11 | 10 | 9  | 8  |  |

|          |                         |    | R  | SP |    |    |    |  |

| 7        | 7 6 5 4 3 2 1 0         |    |    |    |    | 0  |    |  |

|          | RSP                     |    |    |    |    |    |    |  |

# • RSP: Response

Note: 1. The response register can be read by N accesses at the same HSMCI\_RSPR or at consecutive addresses (0x20 to 0x2C). N depends on the size of the response.

through the UDP\_FDRx. Once a transfer is done, the device firmware must release Bank 0 to the USB peripheral device by clearing RX\_DATA\_BK0.

After setting or clearing this bit, a wait time of 3 UDPCK clock cycles and 3 peripheral clock cycles is required before accessing DPR.

# RXSETUP: Received Setup

This flag generates an interrupt while it is set to one.

Read:

0: No setup packet available.

1: A setup data packet has been sent by the host and is available in the FIFO.

Write:

0: Device firmware notifies the USB peripheral device that it has read the setup data in the FIFO.

1: No effect.

This flag is used to notify the USB device firmware that a valid Setup data packet has been sent by the host and successfully received by the USB device. The USB device firmware may transfer Setup data from the FIFO by reading the UDP\_FDRx to the microcontroller memory. Once a transfer has been done, RXSETUP must be cleared by the device firmware.

Ensuing Data OUT transaction is not accepted while RXSETUP is set.

# • STALLSENT: Stall Sent

This flag generates an interrupt while it is set to one.

This ends a STALL handshake.

Read:

- 0: Host has not acknowledged a stall

- 1: Host has acknowledged the stall

Write:

0: Resets the STALLSENT flag, clears the interrupt

1: No effect

This is mandatory for the device firmware to clear this flag. Otherwise the interrupt remains.

Refer to chapters 8.4.5 and 9.4.5 of the Universal Serial Bus Specification, Rev. 2.0 for more information on the STALL handshake.

# 42.8 Ethernet MAC (GMAC) User Interface

| Offset <sup>(1) (2)</sup> | Register                                    | Name       | Access     | Reset       |

|---------------------------|---------------------------------------------|------------|------------|-------------|

| 0x000                     | Network Control Register                    | GMAC_NCR   | Read/Write | 0x0000_0000 |

| 0x004                     | Network Configuration Register              | GMAC_NCFGR | Read/Write | 0x0008_0000 |

| 0x008                     | Network Status Register                     | GMAC_NSR   | Read-only  | 0b01x0      |

| 0x00C                     | User Register                               | GMAC_UR    | Read/Write | 0x0000_0000 |

| 0x010                     | DMA Configuration Register                  | GMAC_DCFGR | Read/Write | 0x0002_0004 |

| 0x014                     | Transmit Status Register                    | GMAC_TSR   | Read/Write | 0x0000_0000 |

| 0x018                     | Receive Buffer Queue Base Address Register  | GMAC_RBQB  | Read/Write | 0x0000_0000 |

| 0x01C                     | Transmit Buffer Queue Base Address Register | GMAC_TBQB  | Read/Write | 0x0000_0000 |

| 0x020                     | Receive Status Register                     | GMAC_RSR   | Read/Write | 0x0000_0000 |

| 0x024                     | Interrupt Status Register                   | GMAC_ISR   | Read-only  | 0x0000_0000 |

| 0x028                     | Interrupt Enable Register                   | GMAC_IER   | Write-only | _           |

| 0x02C                     | Interrupt Disable Register                  | GMAC_IDR   | Write-only | _           |

| 0x030                     | Interrupt Mask Register                     | GMAC_IMR   | Read/Write | 0x07FF_FFFF |

| 0x034                     | PHY Maintenance Register                    | GMAC_MAN   | Read/Write | 0x0000_0000 |

| 0x038                     | Received Pause Quantum Register             | GMAC_RPQ   | Read-only  | 0x0000_0000 |

| 0x03C                     | Transmit Pause Quantum Register             | GMAC_TPQ   | Read/Write | 0x0000_FFFF |

| 0x040-0x07C               | Reserved                                    | -          | _          | _           |

| 0x080                     | Hash Register Bottom                        | GMAC_HRB   | Read/Write | 0x0000_0000 |

| 0x084                     | Hash Register Top                           | GMAC_HRT   | Read/Write | 0x0000_0000 |

| 0x088                     | Specific Address 1 Bottom Register          | GMAC_SAB1  | Read/Write | 0x0000_0000 |

| 0x08C                     | Specific Address 1 Top Register             | GMAC_SAT1  | Read/Write | 0x0000_0000 |

| 0x090                     | Specific Address 2 Bottom Register          | GMAC_SAB2  | Read/Write | 0x0000_0000 |

| 0x094                     | Specific Address 2 Top Register             | GMAC_SAT2  | Read/Write | 0x0000_0000 |

| 0x098                     | Specific Address 3 Bottom Register          | GMAC_SAB3  | Read/Write | 0x0000_0000 |

| 0x09C                     | Specific Address 3 Top Register             | GMAC_SAT3  | Read/Write | 0x0000_0000 |

| 0x0A0                     | Specific Address 4 Bottom Register          | GMAC_SAB4  | Read/Write | 0x0000_0000 |

| 0x0A4                     | Specific Address 4 Top Register             | GMAC_SAT4  | Read/Write | 0x0000_0000 |

| 0x0A8                     | Type ID Match 1 Register                    | GMAC_TIDM1 | Read/Write | 0x0000_0000 |

| 0x0AC                     | Type ID Match 2 Register                    | GMAC_TIDM2 | Read/Write | 0x0000_0000 |

| 0x0B0                     | Type ID Match 3 Register                    | GMAC_TIDM3 | Read/Write | 0x0000_0000 |

| 0x0B4                     | Type ID Match 4 Register                    | GMAC_TIDM4 | Read/Write | 0x0000_0000 |

| 0x0B8                     | Reserved                                    | _          | _          | _           |

| 0x0BC                     | IPG Stretch Register                        | GMAC_IPGS  | Read/Write | 0x0000_0000 |

| 0x0C0                     | Stacked VLAN Register                       | GMAC_SVLAN | Read/Write | 0x0000_0000 |

| 0x0C4                     | Transmit PFC Pause Register                 | GMAC_TPFCP | Read/Write | 0x0000_0000 |

# Table 42-17.Register Mapping

| 42.8.18  | GMAC Hash Regis | ster Top |    |    |    |    |    |  |

|----------|-----------------|----------|----|----|----|----|----|--|

| Name:    | GMAC_HRT        |          |    |    |    |    |    |  |

| Address: | 0x40034084      |          |    |    |    |    |    |  |

| Access:  | Read-only       |          |    |    |    |    |    |  |

| 31       | 30              | 29       | 28 | 27 | 26 | 25 | 24 |  |

|          | ADDR            |          |    |    |    |    |    |  |

| 23       | 22              | 21       | 20 | 19 | 18 | 17 | 16 |  |

|          |                 |          | AD | DR |    |    |    |  |

| 15       | 14              | 13       | 12 | 11 | 10 | 9  | 8  |  |

|          | ADDR            |          |    |    |    |    |    |  |

| 7        | 6               | 5        | 4  | 3  | 2  | 1  | 0  |  |

|          |                 |          | AD | DR |    |    |    |  |

The unicast hash enable (UNIHEN) and the multicast hash enable (MITIHEN) bits in the GMAC Network Configuration Register enable the reception of hash matched frames. See Section 42.6.9 "Hash Addressing".

# • ADDR: Hash Address

Bits 63 to 32 of the Hash Address Register.

| 45.7.2   | ACC Mode Regist | ter     |     |    |          |      |      |

|----------|-----------------|---------|-----|----|----------|------|------|

| Name:    | ACC_MR          |         |     |    |          |      |      |

| Address: | 0x400BC004      |         |     |    |          |      |      |

| Access:  | Read/Write      |         |     |    |          |      |      |

| 31       | 30              | 29      | 28  | 27 | 26       | 25   | 24   |

| _        | -               | _       | _   | _  | _        | _    | —    |

| 23       | 22              | 21      | 20  | 19 | 18       | 17   | 16   |

| _        | -               | _       | _   | _  | _        | _    | —    |

| 15       | 14              | 13      | 12  | 11 | 10       | 9    | 8    |

| _        | FE              | SELFS   | INV | _  | EDG      | ETYP | ACEN |

| 7        | 6               | 5       | 4   | 3  | 2        | 1    | 0    |

| —        |                 | SELPLUS |     | —  | SELMINUS |      |      |

This register can only be written if the WPEN bit is cleared in the ACC Write Protection Mode Register.

# • SELMINUS: Selection for Minus Comparator Input

| Value | Name     | Description     |

|-------|----------|-----------------|

| 0     | TS       | Select TS       |

| 1     | ADVREF   | Select ADVREF   |

| 2     | DAC0     | Select DAC0     |

| 3     | DAC1     | Select DAC1     |

| 4     | AFE0_AD0 | Select AFE0_AD0 |

| 5     | AFE0_AD1 | Select AFE0_AD1 |

| 6     | AFE0_AD2 | Select AFE0_AD2 |

| 7     | AFE0_AD3 | Select AFE0_AD3 |

# • SELPLUS: Selection For Plus Comparator Input

0..7: Selects the input to apply on analog comparator SELPLUS comparison input.

| Value | Name     | Description     |

|-------|----------|-----------------|

| 0     | AFE0_AD0 | Select AFE0_AD0 |

| 1     | AFE0_AD1 | Select AFE0_AD1 |

| 2     | AFE0_AD2 | Select AFE0_AD2 |

| 3     | AFE0_AD3 | Select AFE0_AD3 |

| 4     | AFE0_AD4 | Select AFE0_AD4 |

| 5     | AFE0_AD5 | Select AFE0_AD5 |

| 6     | AFE1_AD0 | Select AFE1_AD0 |

| 7     | AFE1_AD1 | Select AFE1_AD1 |

# • ACEN: Analog Comparator Enable

0 (DIS): Analog comparator disabled.

1 (EN): Analog comparator enabled.

#### 46.7.5.2 ADC Electrical Performances

#### **Single-ended Static Performances**

Table 46-39. Single-ended Static Electrical Characteristics

| Symbol | Parameter                      | Conditions | Min | Тур  | Max | Unit |

|--------|--------------------------------|------------|-----|------|-----|------|

| INL    | ADC Integral Non-linearity     | —          | -2  | ±1   | 2   | LSB  |

| DNL    | ADC Differential Non-linearity | _          | -1  | ±0.5 | 1   | LSB  |

#### **Single-ended Dynamic Performances**

#### Table 46-40. Single-ended Dynamic Electrical Characteristics <sup>(1)</sup>

| Symbol | Parameter                      | Conditions | Min | Тур  | Max | Unit |

|--------|--------------------------------|------------|-----|------|-----|------|

| SNR    | Signal to Noise Ratio          | (1)        | 56  | 64   | 72  | dB   |

| THD    | Total Harmonic Distortion      | (1)        | 66  | 74   |     | dB   |

| SINAD  | Signal to Noise and Distortion | (1)        | 55  | 62   | _   | dB   |

| ENOB   | Effective Number of Bits       | (1)        | 9   | 10.5 | _   | bits |

Note: 1. ADC Clock ( $f_{ADC}$ ) = 20 MHz,  $f_{S}$  = 1 MHz,  $f_{IN}$  = 127 kHz, Frequency band = [1 kHz, 500 kHz] - Nyquist conditions fulfilled.

#### **Differential Static Performances**

#### Table 46-41. Differential Static Electrical Characteristics

| Symbol | Parameter                  | Conditions | Min | Тур  | Max | Unit |

|--------|----------------------------|------------|-----|------|-----|------|

| INL    | Integral Non-linearity     |            | -2  | ±1   | 2   | LSB  |

| DNL    | Differential Non-linearity |            | -1  | ±0.5 | 1   | LSB  |

**Differential Dynamic Performances**

#### Table 46-42. Differential Dynamic Electrical Characteristics

| Symbol | Parameter                      | Conditions | Min | Тур  | Max | Unit |

|--------|--------------------------------|------------|-----|------|-----|------|

| SNR    | Signal to Noise Ratio          | (1)        | 60  | 64   | 74  | dB   |

| THD    | Total Harmonic Distortion      | (1)        | 76  | 80   |     | dB   |

| SINAD  | Signal to Noise and Distortion | (1)        | 60  | 64   | 73  | dB   |

| ENOB   | Effective Number of Bits       | (1)        | 9.5 | 10.5 | 12  | bits |

Note: 1. ADC Clock  $(f_{ADC}) = 20$  MHz,

f<sub>S</sub> = 1 MHz,

$f_{IN} = 127 \text{ kHz},$

Frequency band = [1 kHz, 500 kHz]

Nyquist conditions fulfilled.

#### 10-bit ADC Mode

In 10-bit mode, the ADC produces 12-bit output but the output data in AFEC\_CDR is shifted two bits to the right, removing the two LSBs of the 12-bit ADC.

The gain and offset have the same values as for 12-bit mode, with digital full-scale output code range reduced to 1024 (vs 4096).

The INL and DNL have the same values as for 12-bit mode.

The dynamic performances are the 12-bit mode values, reduced by 12 dB.