Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 120MHz                                                                    |

| Connectivity               | CANbus, EBI/EMI, Ethernet, IrDA, SD, SPI, UART/USART, USB                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 117                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 144-LFBGA                                                                 |

| Supplier Device Package    | 144-LFBGA (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4e16ea-cur |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 11.4.3.5 Exception Priorities

As Table 11-9 shows, all exceptions have an associated priority, with:

- A lower priority value indicating a higher priority

- Configurable priorities for all exceptions except Reset, Hard fault and NMI.

If the software does not configure any priorities, then all exceptions with a configurable priority have a priority of 0. For information about configuring exception priorities see "System Handler Priority Registers", and "Interrupt Priority Registers".

Note: Configurable priority values are in the range 0–15. This means that the Reset, Hard fault, and NMI exceptions, with fixed negative priority values, always have higher priority than any other exception.

For example, assigning a higher priority value to IRQ[0] and a lower priority value to IRQ[1] means that IRQ[1] has higher priority than IRQ[0]. If both IRQ[1] and IRQ[0] are asserted, IRQ[1] is processed before IRQ[0].

If multiple pending exceptions have the same priority, the pending exception with the lowest exception number takes precedence. For example, if both IRQ[0] and IRQ[1] are pending and have the same priority, then IRQ[0] is processed before IRQ[1].

When the processor is executing an exception handler, the exception handler is preempted if a higher priority exception occurs. If an exception occurs with the same priority as the exception being handled, the handler is not preempted, irrespective of the exception number. However, the status of the new interrupt changes to pending.

### 11.4.3.6 Interrupt Priority Grouping

To increase priority control in systems with interrupts, the NVIC supports priority grouping. This divides each interrupt priority register entry into two fields:

- An upper field that defines the group priority

- A lower field that defines a *subpriority* within the group.

Only the group priority determines preemption of interrupt exceptions. When the processor is executing an interrupt exception handler, another interrupt with the same group priority as the interrupt being handled does not preempt the handler.

If multiple pending interrupts have the same group priority, the subpriority field determines the order in which they are processed. If multiple pending interrupts have the same group priority and subpriority, the interrupt with the lowest IRQ number is processed first.

For information about splitting the interrupt priority fields into group priority and subpriority, see "Application Interrupt and Reset Control Register".

### 11.4.3.7 Exception Entry and Return

Descriptions of exception handling use the following terms:

### Preemption

When the processor is executing an exception handler, an exception can preempt the exception handler if its priority is higher than the priority of the exception being handled. See "Interrupt Priority Grouping" for more information about preemption by an interrupt.

When one exception preempts another, the exceptions are called nested exceptions. See "Exception Entry" more information.

### Return

This occurs when the exception handler is completed, and:

- There is no pending exception with sufficient priority to be serviced

- The completed exception handler was not handling a late-arriving exception.

• If subtracting a negative value from a positive value generates a negative value.

The Compare operations are identical to subtracting, for CMP, or adding, for CMN, except that the result is discarded. See the instruction descriptions for more information.

Note: Most instructions update the status flags only if the S suffix is specified. See the instruction descriptions for more information.

### **Condition Code Suffixes**

The instructions that can be conditional have an optional condition code, shown in syntax descriptions as {cond}. Conditional execution requires a preceding IT instruction. An instruction with a condition code is only executed if the condition code flags in the APSR meet the specified condition. Table 11-16 shows the condition codes to use.

A conditional execution can be used with the IT instruction to reduce the number of branch instructions in code.

Table 11-16 also shows the relationship between condition code suffixes and the N, Z, C, and V flags.

| Suffix   | Flags              | Meaning                                                  |  |  |  |

|----------|--------------------|----------------------------------------------------------|--|--|--|

| EQ       | Z = 1              | Equal                                                    |  |  |  |

| NE       | Z = 0              | Not equal                                                |  |  |  |

| CS or HS | C = 1              | Higher or same, unsigned $\geq$                          |  |  |  |

| CC or LO | C = 0              | Lower, unsigned <                                        |  |  |  |

| МІ       | N = 1              | Negative                                                 |  |  |  |

| PL       | N = 0              | Positive or zero                                         |  |  |  |

| VS       | V = 1              | Overflow                                                 |  |  |  |

| VC       | V = 0              | No overflow                                              |  |  |  |

| НІ       | C = 1 and Z = 0    | Higher, unsigned >                                       |  |  |  |

| LS       | C = 0 or Z = 1     | Lower or same, unsigned $\leq$                           |  |  |  |

| GE       | N = V              | Greater than or equal, signed $\geq$                     |  |  |  |

| LT       | N != V             | Less than, signed <                                      |  |  |  |

| GT       | Z = 0 and $N = V$  | Greater than, signed >                                   |  |  |  |

| LE       | Z = 1 and N != V   | Less than or equal, signed ≤                             |  |  |  |

| AL       | Can have any value | Always. This is the default when no suffix is specified. |  |  |  |

Table 11-16. Condition Code Suffixes

### **Absolute Value**

The example below shows the use of a conditional instruction to find the absolute value of a number. R0 = ABS(R1).

| MOVS  | R0, R1     | ; R0 = R1, setting flags                    |

|-------|------------|---------------------------------------------|

| IT    | MI         | ; IT instruction for the negative condition |

| RSBMI | R0, R1, #0 | ; If negative, R0 = -R1                     |

#### **Compare and Update Value**

The example below shows the use of conditional instructions to update the value of R4 if the signed values R0 is greater than R1 and R2 is greater than R3.

| CMP   | R0, R1 | ; Compare R0 and R1, setting flags                    |  |

|-------|--------|-------------------------------------------------------|--|

| ITT   | GT     | ; IT instruction for the two GT conditions            |  |

| CMPGT | R2, R3 | ; If 'greater than', compare R2 and R3, setting flags |  |

| MOVGT | R4, R5 | ; If still 'greater than', do R4 = R5                 |  |

## 11.6.6.10 SMUL and SMULW

Signed Multiply (halfwords) and Signed Multiply (word by halfword)

Syntax

ор

```

op{XY}{cond} Rd,Rn, Rm

op{Y}{cond} Rd. Rn, Rm

```

For SMULXY only:

is one of:

SMUL{XY} Signed Multiply (halfwords).

X and Y specify which halfword of the source registers *Rn* and *Rm* is used as the first and second multiply operand.

If X is B, then the bottom halfword, bits [15:0] of Rn is used.

If X is T, then the top halfword, bits [31:16] of Rn is used. If Y is B, then the bot tom halfword, bits [15:0], of Rm is used.

If Y is T, then the top halfword, bits [31:16], of Rm is used.

SMULW{Y} Signed Multiply (word by halfword).

Y specifies which halfword of the source register *Rm* is used as the second mul tiply operand.

If Y is B, then the bottom halfword (bits [15:0]) of Rm is used.

If Y is T, then the top halfword (bits [31:16]) of *Rm* is used.

cond is an optional condition code, see "Conditional Execution" .

Rd is the destination register.

Rn, Rm are registers holding the first and second operands.

## Operation

The SMULBB, SMULTB, SMULBT and SMULTT instructions interprets the values from *Rn* and *Rm* as four signed 16-bit integers. These instructions:

- Multiplies the specified signed halfword, Top or Bottom, values from *Rn* and *Rm*.

- Writes the 32-bit result of the multiplication in Rd.

The SMULWT and SMULWB instructions interprets the values from *Rn* as a 32-bit signed integer and *Rm* as two halfword 16-bit signed integers. These instructions:

- Multiplies the first operand and the top, T suffix, or the bottom, B suffix, halfword of the second operand.

- Writes the signed most significant 32 bits of the 48-bit result in the destination register.

Restrictions

In these instructions:

- Do not use SP and do not use PC.

- *RdHi* and *RdLo* must be different registers.

### Examples

| SMULBT | R0, R4, R5 ; Multiplies the bottom halfword of R4 with the  |

|--------|-------------------------------------------------------------|

|        | ; top halfword of R5, multiplies results and                |

|        | ; writes to RO                                              |

| SMULBB | R0, R4, R5 ; Multiplies the bottom halfword of R4 with the  |

|        | ; bottom halfword of R5, multiplies results and             |

|        | ; writes to RO                                              |

| SMULTT | R0, R4, R5 ; Multiplies the top halfword of R4 with the top |

|        | ; halfword of R5, multiplies results and writes             |

|        | ; to RO                                                     |

| SMULTB | R0, R4, R5 ; Multiplies the top halfword of R4 with the     |

## 11.6.11.7 VDIV

Divides floating-point values.

Syntax

$VDIV{cond}$ .F32 {Sd,} Sn, Sm

where:

cond is an optional condition code, see "Conditional Execution".

Sd is the destination register.

Sn, Sm are the operand registers.

Operation

This instruction:

- 1. Divides one floating-point value by another floating-point value.

- 2. Writes the result to the floating-point destination register.

Restrictions

There are no restrictions.

**Condition Flags**

These instructions do not change the flags.

| 11.8.3.7 | Software Trigger Interrupt Register |    |    |    |    |    |       |

|----------|-------------------------------------|----|----|----|----|----|-------|

| Name:    | NVIC_STIR                           |    |    |    |    |    |       |

| Access:  | Write-only                          |    |    |    |    |    |       |

| Reset:   | 0x000000000                         |    |    |    |    |    |       |

| 31       | 30                                  | 29 | 28 | 27 | 26 | 25 | 24    |

| -        | -                                   | -  | -  | -  | -  | -  | -     |

| 23       | 22                                  | 21 | 20 | 19 | 18 | 17 | 16    |

| _        | _                                   | _  | -  | -  | -  | _  | -     |

| 15       | 14                                  | 13 | 12 | 11 | 10 | 9  | 8     |

| -        | -                                   | _  | -  | -  | —  | _  | INTID |

| 7        | 6                                   | 5  | 4  | 3  | 2  | 1  | 0     |

|          | INTID                               |    |    |    |    |    |       |

Write to this register to generate an interrupt from the software.

# • INTID: Interrupt ID

Interrupt ID of the interrupt to trigger, in the range 0–239. For example, a value of 0x03 specifies interrupt IRQ3.

# 15.4 Product Dependencies

## 15.4.1 Power Management

The Real-time Clock is continuously clocked at 32.768 kHz. The Power Management Controller has no effect on RTC behavior.

## 15.4.2 Interrupt

RTC interrupt line is connected on one of the internal sources of the interrupt controller. RTC interrupt requires the interrupt controller to be programmed first.

## Table 15-1.Peripheral IDs

| Instance | ID |

|----------|----|

| RTC      | 2  |

# 15.5 Functional Description

The RTC provides a full binary-coded decimal (BCD) clock that includes century (19/20), year (with leap years), month, date, day, hours, minutes and seconds reported in RTC Time Register (RTC\_TIMR) and RTC Calendar Register (RTC\_CALR).

The valid year range is up to 2099 in Gregorian mode (or 1300 to 1499 in Persian mode).

The RTC can operate in 24-hour mode or in 12-hour mode with an AM/PM indicator.

Corrections for leap years are included (all years divisible by 4 being leap years except 1900). This is correct up to the year 2099.

The RTC can generate configurable waveforms on RTCOUT0/1 outputs.

### 15.5.1 Reference Clock

The reference clock is the Slow Clock (SLCK). It can be driven internally or by an external 32.768 kHz crystal.

During low power modes of the processor, the oscillator runs and power consumption is critical. The crystal selection has to take into account the current consumption for power saving and the frequency drift due to temperature effect on the circuit for time accuracy.

### 15.5.2 Timing

The RTC is updated in real time at one-second intervals in Normal mode for the counters of seconds, at oneminute intervals for the counter of minutes and so on.

Due to the asynchronous operation of the RTC with respect to the rest of the chip, to be certain that the value read in the RTC registers (century, year, month, date, day, hours, minutes, seconds) are valid and stable, it is necessary to read these registers twice. If the data is the same both times, then it is valid. Therefore, a minimum of two and a maximum of three accesses are required.

### 15.5.3 Alarm

The RTC has five programmable fields: month, date, hours, minutes and seconds.

Each of these fields can be enabled or disabled to match the alarm condition:

- If all the fields are enabled, an alarm flag is generated (the corresponding flag is asserted and an interrupt generated if enabled) at a given month, date, hour/minute/second.

- If only the "seconds" field is enabled, then an alarm is generated every minute.

# 15.6.11 RTC Interrupt Mask Register

| Name:<br>Address: | RTC_IMR<br>0x400E1888 |       |     |     |     |     |     |

|-------------------|-----------------------|-------|-----|-----|-----|-----|-----|

| Access:           | Read-only             |       |     |     |     |     |     |

| 31                | 30                    | 29    | 28  | 27  | 26  | 25  | 24  |

| _                 | -                     | -     | _   | _   | _   | _   | -   |

| 23                | 22                    | 21    | 20  | 19  | 18  | 17  | 16  |

| _                 | -                     | _     | _   | _   | -   | -   | _   |

| 15                | 14                    | 13    | 12  | 11  | 10  | 9   | 8   |

| _                 | -                     | -     | _   | _   | _   | _   | _   |

| 7                 | 6                     | 5     | 4   | 3   | 2   | 1   | 0   |

| _                 | _                     | TDERR | CAL | TIM | SEC | ALR | ACK |

## ACK: Acknowledge Update Interrupt Mask

0: The acknowledge for update interrupt is disabled.

1: The acknowledge for update interrupt is enabled.

### • ALR: Alarm Interrupt Mask

0: The alarm interrupt is disabled.

1: The alarm interrupt is enabled.

### • SEC: Second Event Interrupt Mask

0: The second periodic interrupt is disabled.

1: The second periodic interrupt is enabled.

## • TIM: Time Event Interrupt Mask

0: The selected time event interrupt is disabled.

1: The selected time event interrupt is enabled.

### • CAL: Calendar Event Interrupt Mask

0: The selected calendar event interrupt is disabled.

1: The selected calendar event interrupt is enabled.

## • TDERR: Time and/or Date Error Mask

- 0: The time and/or date error event is disabled.

- 1: The time and/or date error event is enabled.

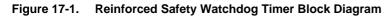

# 17.3 Block Diagram

# 17.4 Functional Description

The RSWDT is supplied by VDDCORE. The RSWDT is initialized with default values on processor reset or on a power-on sequence and is disabled (its default mode) under such conditions.

The RSWDT must not be enabled if the WDT is disabled.

The main RC oscillator divided clock is selected if the main RC oscillator is already enabled by the application (CKGR\_MOR.MOSCRCEN = 1) or if the WDT is driven by the slow RC oscillator.

The RSWDT is built around a 12-bit down counter, which is loaded with a slow clock value other than that of the slow clock in the WDT, defined in the WDV (Watchdog Counter Value) field of the Mode Register (RSWDT\_MR). The RSWDT uses the slow clock divided by 128 to establish the maximum watchdog period to be 16 seconds (with a typical slow clock of 32.768 kHz).

After a processor reset, the value of WDV is 0xFFF, corresponding to the maximum value of the counter with the external reset generation enabled (RSWDT\_MR.WDRSTEN = 1 after a backup reset). This means that a default watchdog is running at reset, i.e., at power-up.

If the watchdog is restarted by writing into the Control Register (RSWDT\_CR), the RSWDT\_MR must not be programmed during a period of time of three slow clock periods following the RSWDT\_CR write access. Programming a new value in the RSWDT\_MR automatically initiates a restart instruction.

## 23.6.1 UART0 Serial Port

Communication is performed through the UART0 initialized to 115200 Baud, 8, n, 1.

The Send and Receive File commands use the Xmodem protocol to communicate. Any terminal performing this protocol can be used to send the application file to the target. The size of the binary file to send depends on the SRAM size embedded in the product. In all cases, the size of the binary file must be lower than the SRAM size because the Xmodem protocol requires some SRAM memory to work. See Section 23.3 "Hardware and Software Constraints".

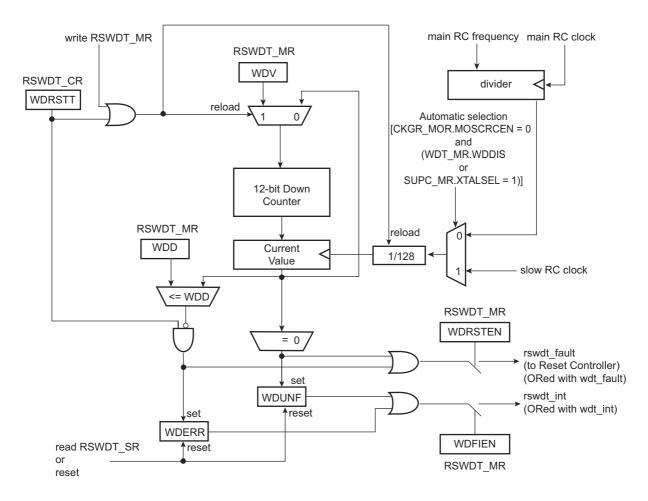

## 23.6.2 Xmodem Protocol

The Xmodem protocol supported is the 128-byte length block. This protocol uses a two-character CRC-16 to guarantee detection of a maximum bit error.

Xmodem protocol with CRC is accurate provided both sender and receiver report successful transmission. Each block of the transfer looks like:

<SOH><blk #><255-blk #><--128 data bytes--><checksum> in which:

- <SOH> = 01 hex

- <blk #> = binary number, starts at 01, increments by 1, and wraps 0FFH to 00H (not to 01)

- <255-blk #> = 1's complement of the blk#.

- <checksum> = 2 bytes CRC16

Figure 23-2 shows a transmission using this protocol.

### Figure 23-2. Xmodem Transfer Example

### 23.6.3 USB Device Port

The device uses the USB communication device class (CDC) drivers to take advantage of the installed PC RS-232 software to talk over the USB. The CDC class is implemented in all releases of Windows<sup>®</sup>, beginning with Windows 98SE. The CDC document, available at www.usb.org, describes a way to implement devices such as ISDN modems and virtual COM ports.

The Vendor ID (VID) is Atmel's vendor ID 0x03EB. The product ID (PID) is 0x6124. These references are used by the host operating system to mount the correct driver. On Windows systems, the INF files contain the correspondence between vendor ID and product ID.

# Table 29-2. Register Mapping (Continued)

| Offset        | Register                              | Name     | Access     | Reset       |

|---------------|---------------------------------------|----------|------------|-------------|

| 0x0110        | Oscillator Calibration Register       | PMC_OCR  | Read/Write | 0x0040_4040 |

| 0x0114-0x0120 | Reserved                              | _        | -          | -           |

| 0x0130        | PLL Maximum Multiplier Value Register | PMC_PMMR | Read/Write | 0x07FF_07FF |

| 0x0134–0x144  | Reserved                              | _        | _          | -           |

Note: If an offset is not listed in the table it must be considered as "reserved".

## 31.8.5 Register Write Protection

To prevent any single software error that may corrupt CAN behavior, the registers listed below can be writeprotected by setting the WPEN bit in the CAN Write Protection Mode Register (CAN\_WPMR).

If a write access in a write-protected register is detected, then the WPVS flag in the CAN Write Protection Status Register (CAN\_WPSR) is set and the field WPVSRC indicates in which register the write access has been attempted.

The WPVS flag is automatically reset after reading the CAN\_WPSR.

The following registers can be write-protected:

- CAN Mode Register

- CAN Baudrate Register

- CAN Message Mode Register

- CAN Message Acceptance Mask Register

- CAN Message ID Register

## 31.9.21 CAN Message Control Register

# Name: CAN\_MCRx [x=0..7]

Address: 0x4001021C (0)[0], 0x4001023C (0)[1], 0x4001025C (0)[2], 0x4001027C (0)[3], 0x4001029C (0)[4], 0x400102BC (0)[5], 0x400102DC (0)[6], 0x400102FC (0)[7], 0x4001421C (1)[0], 0x4001423C (1)[1], 0x4001425C (1)[2], 0x4001427C (1)[3], 0x4001429C (1)[4], 0x400142BC (1)[5], 0x400142DC (1)[6], 0x400142FC (1)[7]

| Access: | Write-only |    |      |      |    |    |    |

|---------|------------|----|------|------|----|----|----|

| 31      | 30         | 29 | 28   | 27   | 26 | 25 | 24 |

| —       | -          | —  | —    | —    | —  | _  | -  |

| 23      | 22         | 21 | 20   | 19   | 18 | 17 | 16 |

| MTCR    | MACR       | —  | MRTR | MDLC |    |    |    |

| 15      | 14         | 13 | 12   | 11   | 10 | 9  | 8  |

| _       | -          | _  | _    | _    | _  | _  | —  |

| 7       | 6          | 5  | 4    | 3    | 2  | 1  | 0  |

| -       | -          | _  | _    | _    | _  | _  | _  |

### • MDLC: Mailbox Data Length Code

| Mailbox Object Type    | Description                                                                |  |  |

|------------------------|----------------------------------------------------------------------------|--|--|

| Receive                | No action.                                                                 |  |  |

| Receive with overwrite | No action.                                                                 |  |  |

| Transmit               | Length of the mailbox message.                                             |  |  |

| Consumer               | No action.                                                                 |  |  |

| Producer               | Length of the mailbox message to be sent after the remote frame reception. |  |  |

## MRTR: Mailbox Remote Transmission Request

| Mailbox Object Type    | Description                                                   |

|------------------------|---------------------------------------------------------------|

| Receive                | No action                                                     |

| Receive with overwrite | No action                                                     |

| Transmit               | Set the RTR bit in the sent frame                             |

| Consumer               | No action, the RTR bit in the sent frame is set automatically |

| Producer               | No action                                                     |

Consumer situations can be handled automatically by setting the mailbox object type in Consumer. This requires only one mailbox.

It can also be handled using two mailboxes, one in reception, the other in transmission. The MRTR and the MTCR bits must be set in the same time.

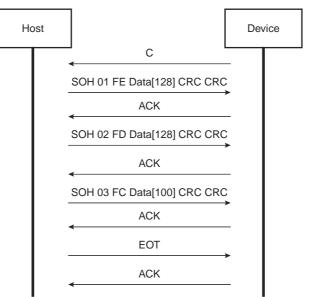

Figure 35-17. TWI Read Operation with Single Data Byte without Internal Address

Atmel

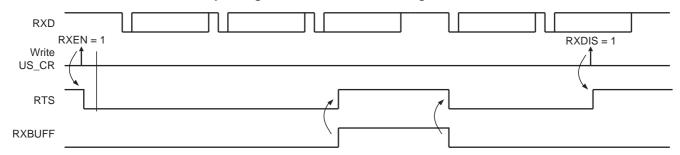

Figure 37-27. Receiver Behavior when Operating with Hardware Handshaking

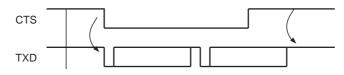

Figure 37-28 shows how the transmitter operates if hardware handshaking is enabled. The CTS pin disables the transmitter. If a character is being processed, the transmitter is disabled only after the completion of the current character and transmission of the next character happens as soon as the pin CTS falls.

Figure 37-28. Transmitter Behavior when Operating with Hardware Handshaking

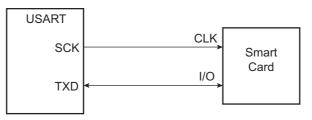

## 37.6.4 ISO7816 Mode

The USART features an ISO7816-compatible operating mode. This mode permits interfacing with smart cards and Security Access Modules (SAM) communicating through an ISO7816 link. Both T = 0 and T = 1 protocols defined by the ISO7816 specification are supported.

Setting the USART in ISO7816 mode is performed by writing the USART\_MODE field in US\_MR to the value 0x4 for protocol T = 0 and to the value 0x5 for protocol T = 1.

## 37.6.4.1 ISO7816 Mode Overview

The ISO7816 is a half duplex communication on only one bidirectional line. The baud rate is determined by a division of the clock provided to the remote device (see Section 37-2 "Baud Rate Generator").

The USART connects to a smart card as shown in Figure 37-29. The TXD line becomes bidirectional and the baud rate generator feeds the ISO7816 clock on the SCK pin. As the TXD pin becomes bidirectional, its output remains driven by the output of the transmitter but only when the transmitter is active while its input is directed to the input of the receiver. The USART is considered as the master of the communication as it generates the clock.

### Figure 37-29. Connection of a Smart Card to the USART

When operating in ISO7816, either in T = 0 or T = 1 modes, the character format is fixed. The configuration is 8 data bits, even parity and 1 or 2 stop bits, regardless of the values programmed in the CHRL, MODE9, PAR and CHMODE fields. MSBF can be used to transmit LSB or MSB first. Parity Bit (PAR) can be used to transmit in Normal or Inverse mode. Refer to Section 37.7.3 "USART Mode Register" and "PAR: Parity Type".

| Name:    | US_BRGR        |              |     |    |    |    |    |

|----------|----------------|--------------|-----|----|----|----|----|

| Address: | 0x400A0020 (0) | , 0x400A4020 | (1) |    |    |    |    |

| Access:  | Read/Write     |              |     |    |    |    |    |

| 31       | 30             | 29           | 28  | 27 | 26 | 25 | 24 |

| _        | -              | -            | -   | _  | -  | _  | -  |

| 23       | 22             | 21           | 20  | 19 | 18 | 17 | 16 |

| _        | -              | -            | -   | -  |    | FP |    |

| 15       | 14             | 13           | 12  | 11 | 10 | 9  | 8  |

|          |                |              | C   | D  |    |    |    |

| 7        | 6              | 5            | 4   | 3  | 2  | 1  | 0  |

|          |                |              | C   | D  |    |    |    |

This register can only be written if the WPEN bit is cleared in the USART Write Protection Mode Register.

# • CD: Clock Divider

37.7.15

|             | SYN                                       | C = 0                                    | SYNC = 1                                    |                                                       |  |  |  |  |  |

|-------------|-------------------------------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|--|--|--|--|--|

| CD          | OVER = 0                                  | OVER = 1                                 | or<br>USART_MODE = SPI<br>(Master or Slave) | USART_MODE = ISO7816                                  |  |  |  |  |  |

| 0           | Baud Rate Clock Disabled                  |                                          |                                             |                                                       |  |  |  |  |  |

| 1 10 655 35 | CD = Selected Clock /<br>(16 × Baud Rate) | CD = Selected Clock /<br>(8 × Baud Rate) | CD = Selected Clock /<br>Baud Rate          | CD = Selected Clock /<br>(FI_DI_RATIO × Baud<br>Rate) |  |  |  |  |  |

# • FP: Fractional Part

0: Fractional divider is disabled.

1–7: Baud rate resolution, defined by FP  $\times$  1/8.

**USART Baud Rate Generator Register**

**Warning**: When the value of field FP is greater than 0, the SCK (oversampling clock) generates non-constant duty cycles. The SCK high duration is increased by "selected clock" period from time to time. The duty cycle depends on the value of the CD field.

# 39.7.17 PWM Interrupt Status Register 2

| Name:<br>Access: | PWM_ISR2<br>Read-only |             |             |             |             |             |             |

|------------------|-----------------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 31               | 30                    | 29          | 28          | 27          | 26          | 25          | 24          |

| _                | -                     | —           | —           | _           | _           | —           | -           |

| 23<br>CMPU7      | 22<br>CMPU6           | 21<br>CMPU5 | 20<br>CMPU4 | 19<br>CMPU3 | 18<br>CMPU2 | 17<br>CMPU1 | 16<br>CMPU0 |

| 15<br>CMPM7      | 14<br>CMPM6           | 13<br>CMPM5 | 12<br>CMPM4 | 11<br>CMPM3 | 10<br>CMPM2 | 9<br>CMPM1  | 8<br>CMPM0  |

| 7                | 6                     | 5           | 4           | 3<br>UNRE   | 2<br>TXBUFE | 1<br>ENDTX  | 0<br>WRDY   |

# • WRDY: Write Ready for Synchronous Channels Update

0: New duty-cycle and dead-time values for the synchronous channels cannot be written.

1: New duty-cycle and dead-time values for the synchronous channels can be written.

## • ENDTX: PDC End of TX Buffer

- 0: The Transmit Counter register has not reached 0 since the last write of the PDC.

- 1: The Transmit Counter register has reached 0 since the last write of the PDC.

## • TXBUFE: PDC TX Buffer Empty

0: PWM\_TCR or PWM\_TCNR has a value other than 0.

1: Both PWM\_TCR and PWM\_TCNR have a value other than 0.

## • UNRE: Synchronous Channels Update Underrun Error

0: No Synchronous Channels Update Underrun has occurred since the last read of the PWM\_ISR2 register.

1: At least one Synchronous Channels Update Underrun has occurred since the last read of the PWM\_ISR2 register.

## • CMPMx: Comparison x Match

0: The comparison x has not matched since the last read of the PWM\_ISR2 register.

1: The comparison x has matched at least one time since the last read of the PWM\_ISR2 register.

## CMPUx: Comparison x Update

0: The comparison x has not been updated since the last read of the PWM\_ISR2 register.

1: The comparison x has been updated at least one time since the last read of the PWM\_ISR2 register.

Note: Reading PWM\_ISR2 automatically clears flags WRDY, UNRE and CMPSx.

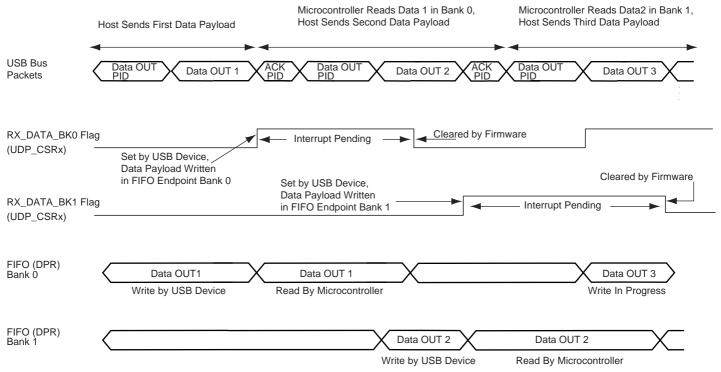

- 5. The number of bytes available in the FIFO is made available by reading RXBYTECNT in the endpoint's UDP\_CSRx.

- 6. The microcontroller transfers out data received from the endpoint's memory to the microcontroller's memory. Data received is made available by reading the endpoint's UDP\_FDRx.

- 7. The microcontroller notifies the USB peripheral device that it has finished the transfer by clearing RX\_DATA\_BK0 in the endpoint's UDP\_CSRx.

- 8. A third Data OUT packet can be accepted by the USB peripheral device and copied in the FIFO Bank 0.

- 9. If a second Data OUT packet has been received, the microcontroller is notified by the flag RX\_DATA\_BK1 set in the endpoint's UDP\_CSRx. An interrupt is pending for this endpoint while RX\_DATA\_BK1 is set.

- 10. The microcontroller transfers out data received from the endpoint's memory to the microcontroller's memory. Data received is available by reading the endpoint's UDP\_FDRx.

- 11. The microcontroller notifies the USB device it has finished the transfer by clearing RX\_DATA\_BK1 in the endpoint's UDP\_CSRx.

- 12. A fourth Data OUT packet can be accepted by the USB device and copied in the FIFO Bank 1.

## Figure 41-11. Data OUT Transfer for Ping-pong Endpoint

Note: An interrupt is pending while the RX\_DATA\_BK0 or RX\_DATA\_BK1 flag is set.

**Warning**: When RX\_DATA\_BK0 and RX\_DATA\_BK1 are both set, there is no way to determine which one to clear first. Thus the software must keep an internal counter to be sure to clear alternatively RX\_DATA\_BK0 then RX\_DATA\_BK1. This situation may occur when the software application is busy elsewhere and the two banks are filled by the USB host. Once the application comes back to the USB driver, the two flags are set.

### 41.6.2.4 Stall Handshake

A stall handshake can be used in one of two distinct occasions. (For more information on the stall handshake, refer to Chapter 8 of the Universal Serial Bus Specification, Rev 2.0.)

• A functional stall is used when the halt feature associated with the endpoint is set. (Refer to Chapter 9 of the *Universal Serial Bus Specification, Rev 2.0,* for more information on the halt feature.)

| 45.7.9   | ACC Write Protect | ction Status Re | egister |    |    |    |      |

|----------|-------------------|-----------------|---------|----|----|----|------|

| Name:    | ACC_WPSR          |                 |         |    |    |    |      |

| Address: | 0x400BC0E8        |                 |         |    |    |    |      |

| Access:  | Read-only         |                 |         |    |    |    |      |

| 31       | 30                | 29              | 28      | 27 | 26 | 25 | 24   |

| -        | -                 | _               | _       | _  | _  | _  | -    |

| 23       | 22                | 21              | 20      | 19 | 18 | 17 | 16   |

| -        | —                 | —               | —       | _  | —  | _  | -    |

| 15       | 14                | 13              | 12      | 11 | 10 | 9  | 8    |

| -        | —                 | —               | —       | _  | —  | _  | -    |

| 7        | 6                 | 5               | 4       | 3  | 2  | 1  | 0    |

| —        | -                 | —               | —       | _  | —  | _  | WPVS |

|          |                   | •               | •       |    | •  |    |      |

# • WPVS: Write Protection Violation Status

0: No write protection violation has occurred since the last read of ACC\_WPSR.

1: A write protection violation (WPEN = 1) has occurred since the last read of ACC\_WPSR.

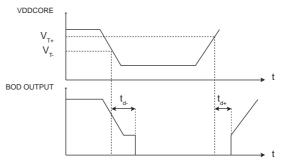

| Symbol               | Parameter                                  | Conditions                                | Min  | Тур | Max  | Unit |

|----------------------|--------------------------------------------|-------------------------------------------|------|-----|------|------|

| V <sub>T-</sub>      | Supply Falling Threshold <sup>(1)</sup>    | —                                         | 0.98 | 1.0 | 1.04 | V    |

| V <sub>hys</sub>     | Hysteresis Voltage                         | _                                         | —    | _   | 110  | mV   |

| V <sub>T+</sub>      | Supply Rising Threshold                    | _                                         | 0.8  | 1.0 | 1.08 | V    |

| t <sub>RST</sub>     | Reset Period                               | $V_{DDIO}$ rising from 0 to 1.2V ± 10%    | 90   | _   | 320  | μs   |

| I <sub>DDON</sub>    |                                            | Brownout Detector enabled                 | —    | _   | 24   | μΑ   |

| IDDOFF               | Current Consumption on VDDCORE             | Brownout Detector disabled                | _    | _   | 2    | μA   |

| I <sub>DD33ON</sub>  |                                            | Brownout Detector enabled                 | _    | _   | 24   | μA   |

| I <sub>DD33OFF</sub> | Current Consumption on VDDIO               | Brownout Detector disabled                | —    | _   | 2    | μΑ   |

| t <sub>d-</sub>      | V <sub>T-</sub> Detection Propagation Time | VDDCORE = $V_{T+}$ to ( $V_{T-}$ - 100mV) | _    | 200 | 300  | ns   |

| t <sub>START</sub>   | Startup Time                               | From disabled state to enabled state      | _    | _   | 300  | μs   |

# Table 46-4. Core Power Supply Brownout Detector Characteristics

Note: 1. The product is guaranteed to be functional at  $V_{T-}$

# Figure 46-1. Core Brownout Output Waveform

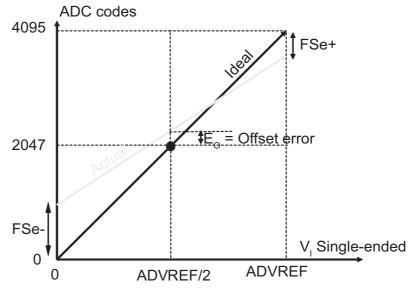

## Single-ended Mode

Figure 46-17 illustrates the ADC output code relative to an input voltage V<sub>I</sub> between 0V (Ground) and V<sub>ADVREF</sub>. The ADC is configured in Single-ended mode by connecting internally the negative differential input to  $V_{ADVREF}/2$ . As the ADC continues to work internally in Differential mode, the offset is measured at  $V_{ADVREF}/2$ .

where:

- FSe = (FSe+) (FSe-) is for full-scale error, unit is LSB code

- Offset error  $E_0$  is the offset error measured for  $V_1 = 0V$

- Gain error  $E_G = 100 \times FSe / 4096$ , unit in %

The error values in Table 46-37 and Table 46-38 include the sample and hold error as well as the PGA gain error.

| Offset Mode            | OFFx = 0 |        | OFFx = 0 |        | OFFx = 1 |        | OFFx = 0 |        | OFFx = 1 |        |

|------------------------|----------|--------|----------|--------|----------|--------|----------|--------|----------|--------|

| Gain Mode              | 1        |        | 2        |        | 2        |        | 4        |        | 4        |        |

| AutoCorrection         | No       | Yes    |

| Average Gain Error (%) | 0.449    | 0.078  | 0.771    | -0.010 | 0.781    | 0.117  | 1.069    | -0.029 | 1.064    | 0.151  |

| Standard Deviation (%) | 0.420    | 0.200  | 0.430    | 0.313  | 0.425    | 0.327  | 0.420    | 0.415  | 0.415    | 0.371  |

| Min Value (%)          | -0.811   | -0.522 | -0.518   | -0.947 | -0.493   | -0.864 | -0.190   | -1.274 | -0.181   | -0.962 |

| Max Value (%)          | 1.709    | 0.679  | 2.061    | 0.928  | 2.056    | 1.099  | 2.329    | 1.216  | 2.310    | 1.265  |

Table 46-37. Single-ended Gain Error

Table 46-38.

Single-ended Output Offset Error

| Offset Mode                | OFFx = 0 | OFFx = 0 | OFFx = 1 | OFFx = 0 | OFFx = 1 |

|----------------------------|----------|----------|----------|----------|----------|

| Gain                       | 1        | 2        | 2        | 4        | 4        |

| Average Offset Error (LSB) | -5.7     | -7.7     | -10.3    | -7.3     | -18.7    |

| Standard Deviation (LSB)   | 1.8      | 3.9      | 3.4      | 6        | 7        |

| Min Value (LSB)            | -11.1    | -19.4    | -20.5    | -25.3    | -39.7    |

| Max Value (LSB)            | -0.3     | 4        | -0.1     | 10.7     | 2.3      |