Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, Ethernet, IrDA, SD, SPI, UART/USART, USB               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 117                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                            |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 144-LFBGA                                                               |

| Supplier Device Package    | 144-LFBGA (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4e8eb-cn |

11.4.1.11 Execution Program Status Register

Name: EPSR

Access: Read/Write

**Reset:** 0x000000000

| 31 | 30 | 29  | 28  | 27 | 26  | 25  | 24 |

|----|----|-----|-----|----|-----|-----|----|

|    |    | _   |     |    | ICI | /IT | Т  |

| 23 | 22 | 21  | 20  | 19 | 18  | 17  | 16 |

|    |    |     | -   | _  |     |     |    |

| 15 | 14 | 13  | 12  | 11 | 10  | 9   | 8  |

|    |    | ICI | /IT |    |     | -   | _  |

| 7  | 6  | 5   | 4   | 3  | 2   | 1   | 0  |

|    |    |     | -   | _  |     |     |    |

The EPSR contains the Thumb state bit, and the execution state bits for either the *If-Then* (IT) instruction, or the *Interrupt-ible-Continuable Instruction* (ICI) field for an interrupted load multiple or store multiple instruction.

Attempts to read the EPSR directly through application software using the MSR instruction always return zero. Attempts to write the EPSR using the MSR instruction in the application software are ignored. Fault handlers can examine the EPSR value in the stacked PSR to indicate the operation that is at fault. See "Exception Entry and Return".

# • ICI: Interruptible-continuable Instruction

When an interrupt occurs during the execution of an LDM, STM, PUSH, POP, VLDM, VSTM, VPUSH, or VPOP instruction, the processor:

- Stops the load multiple or store multiple instruction operation temporarily

- Stores the next register operand in the multiple operation to EPSR bits[15:12].

After servicing the interrupt, the processor:

- Returns to the register pointed to by bits[15:12]

- Resumes the execution of the multiple load or store instruction.

When the EPSR holds the ICI execution state, bits[26:25,11:10] are zero.

#### IT: If-Then Instruction

Indicates the execution state bits of the IT instruction.

The If-Then block contains up to four instructions following an IT instruction. Each instruction in the block is conditional. The conditions for the instructions are either all the same, or some can be the inverse of others. See "IT" for more information.

### • T: Thumb State

The Cortex-M4 processor only supports the execution of instructions in Thumb state. The following can clear the T bit to 0:

- Instructions BLX, BX and POP{PC}

- Restoration from the stacked xPSR value on an exception return

- Bit[0] of the vector value on an exception entry or reset.

Attempting to execute instructions when the T bit is 0 results in a fault or lockup. See "Lockup" for more information.

Table 11-13. Cortex-M4 Instructions (Continued)

| Mnemonic      | Operands                | Description                                    | Flags   |

|---------------|-------------------------|------------------------------------------------|---------|

| LDMDB, LDMEA  | Rn{!}, reglist          | Load Multiple registers, decrement before      | _       |

| LDMFD, LDMIA  | Rn{!}, reglist          | Load Multiple registers, increment after       | _       |

| LDR           | Rt, [Rn, #offset]       | Load Register with word                        | _       |

| LDRB, LDRBT   | Rt, [Rn, #offset]       | Load Register with byte                        | _       |

| LDRD          | Rt, Rt2, [Rn, #offset]  | Load Register with two bytes                   | _       |

| LDREX         | Rt, [Rn, #offset]       | Load Register Exclusive                        | _       |

| LDREXB        | Rt, [Rn]                | Load Register Exclusive with byte              | _       |

| LDREXH        | Rt, [Rn]                | Load Register Exclusive with halfword          | _       |

| LDRH, LDRHT   | Rt, [Rn, #offset]       | Load Register with halfword                    | _       |

| LDRSB, DRSBT  | Rt, [Rn, #offset]       | Load Register with signed byte                 | _       |

| LDRSH, LDRSHT | Rt, [Rn, #offset]       | Load Register with signed halfword             | _       |

| LDRT          | Rt, [Rn, #offset]       | Load Register with word                        | _       |

| LSL, LSLS     | Rd, Rm, <rs #n></rs #n> | Logical Shift Left                             | N,Z,C   |

| LSR, LSRS     | Rd, Rm, <rs #n></rs #n> | Logical Shift Right                            | N,Z,C   |

| MLA           | Rd, Rn, Rm, Ra          | Multiply with Accumulate, 32-bit result        | _       |

| MLS           | Rd, Rn, Rm, Ra          | Multiply and Subtract, 32-bit result           | _       |

| MOV, MOVS     | Rd, Op2                 | Move                                           | N,Z,C   |

| MOVT          | Rd, #imm16              | Move Top                                       | _       |

| MOVW, MOV     | Rd, #imm16              | Move 16-bit constant                           | N,Z,C   |

| MRS           | Rd, spec_reg            | Move from special register to general register | _       |

| MSR           | spec_reg, Rm            | Move from general register to special register | N,Z,C,V |

| MUL, MULS     | {Rd,} Rn, Rm            | Multiply, 32-bit result                        | N,Z     |

| MVN, MVNS     | Rd, Op2                 | Move NOT                                       | N,Z,C   |

| NOP           | _                       | No Operation                                   | _       |

| ORN, ORNS     | {Rd,} Rn, Op2           | Logical OR NOT                                 | N,Z,C   |

| ORR, ORRS     | {Rd,} Rn, Op2           | Logical OR                                     | N,Z,C   |

| PKHTB, PKHBT  | {Rd,} Rn, Rm, Op2       | Pack Halfword                                  | _       |

| POP           | reglist                 | Pop registers from stack                       | _       |

| PUSH          | reglist                 | Push registers onto stack                      | _       |

| QADD          | {Rd,} Rn, Rm            | Saturating double and Add                      | Q       |

| QADD16        | {Rd,} Rn, Rm            | Saturating Add 16                              | _       |

| QADD8         | {Rd,} Rn, Rm            | Saturating Add 8                               | _       |

| QASX          | {Rd,} Rn, Rm            | Saturating Add and Subtract with Exchange      |         |

| QDADD         | {Rd,} Rn, Rm            | Saturating Add                                 | Q       |

| QDSUB         | {Rd,} Rn, Rm            | Saturating double and Subtract                 | Q       |

| QSAX          | {Rd,} Rn, Rm            | Saturating Subtract and Add with Exchange      | _       |

| QSUB          | {Rd,} Rn, Rm            | Saturating Subtract                            | Q       |

### 11.6.8.1 PKHBT and PKHTB

#### Pack Halfword

### Syntax

```

op\{cond\} {Rd}, Rn, Rm {, LSL \#imm} op\{cond\} {Rd}, Rn, Rm {, ASR \#imm}

```

#### where:

op is one of:

PKHBT Pack Halfword, bottom and top with shift. PKHTB Pack Halfword, top and bottom with shift.

cond is an optional condition code, see "Conditional Execution".

Rd is the destination register.

Rn is the first operand register

Rm is the second operand register holding the value to be optionally shifted.

imm is the shift length. The type of shift length depends on the instruction:

For PKHBT

LSL a left shift with a shift length from 1 to 31, 0 means no shift.

For PKHTB

ASR an arithmetic shift right with a shift length from 1 to 32,

a shift of 32-bits is encoded as 0b00000.

### Operation

#### The PKHBT instruction:

- 1. Writes the value of the bottom halfword of the first operand to the bottom halfword of the destination register.

- 2. If shifted, the shifted value of the second operand is written to the top halfword of the destination register.

# The PKHTB instruction:

- 1. Writes the value of the top halfword of the first operand to the top halfword of the destination register.

- 2. If shifted, the shifted value of the second operand is written to the bottom halfword of the destination register.

#### Restrictions

Rd must not be SP and must not be PC.

#### Condition Flags

This instruction does not change the flags.

#### Examples

```

PKHBT R3, R4, R5 LSL #0 ; Writes bottom halfword of R4 to bottom halfword of ; R3, writes top halfword of R5, unshifted, to top ; halfword of R3

PKHTB R4, R0, R2 ASR #1 ; Writes R2 shifted right by 1 bit to bottom halfword ; of R4, and writes top halfword of R0 to top ; halfword of R4.

```

- All conditional instructions except Bcond must be inside an IT block. Bcond can be either outside or inside

an IT block but has a larger branch range if it is inside one

- Each instruction inside the IT block must specify a condition code suffix that is either the same or logical inverse as for the other instructions in the block.

Your assembler might place extra restrictions on the use of IT blocks, such as prohibiting the use of assembler directives within them.

### Condition Flags

This instruction does not change the flags.

# Example

```

; Next 3 instructions are conditional

ITTE NE

ANDNE R0, R0, R1 ; ANDNE does not update condition flags

ADDSNE R2, R2, #1 ; ADDSNE updates condition flags

MOVEQ R2, R3

; Conditional move

CMP

RO, #9

; Convert RO hex value (0 to 15) into ASCII

; ('0'-'9', 'A'-'F')

ITE

GT

; Next 2 instructions are conditional

ADDGT R1, R0, \#55; Convert 0xA \rightarrow 'A'

ADDLE R1, R0, #48 ; Convert 0x0 -> '0'

ΤТ

GT

; IT block with only one conditional instruction

ADDGT R1, R1, #1 ; Increment R1 conditionally

ITTEE EQ

; Next 4 instructions are conditional

MOVEQ R0, R1 ; Conditional move

ADDEQ R2, R2, #10 ; Conditional add

ANDNE R3, R3, #1 ; Conditional AND

BNE.W dloop

; Branch instruction can only be used in the last

; instruction of an IT block

; Next instruction is conditional

IT

RO, RO, R1 ; Syntax error: no condition code used in IT block

ADD

```

# 20.5 Enhanced Embedded Flash Controller (EEFC) User Interface

The User Interface of the Embedded Flash Controller (EEFC) is integrated within the System Controller with base address 0x400E0A00.

Table 20-6. Register Mapping

| Offset    | Register                    | Name     | Access     | Reset State |

|-----------|-----------------------------|----------|------------|-------------|

| 0x00      | EEFC Flash Mode Register    | EEFC_FMR | Read/Write | 0x0400_0000 |

| 0x04      | EEFC Flash Command Register | EEFC_FCR | Write-only | _           |

| 0x08      | EEFC Flash Status Register  | EEFC_FSR | Read-only  | 0x0000_0001 |

| 0x0C      | EEFC Flash Result Register  | EEFC_FRR | Read-only  | 0x0         |

| 0x10-0x14 | Reserved                    | _        | _          | _           |

| 0x18-0xE4 | Reserved                    | _        | _          | _           |

For more details about VID/PID for End Product/Systems, please refer to the Vendor ID form available from the USB Implementers Forum on www.usb.org.

Atmel provides an INF example to see the device as a new serial port and also provides another custom driver used by the SAM-BA application: atm6124.sys. Refer to the application note "USB Basic Application", Atmel literature number 6123, for more details.

#### 23.6.3.1 Enumeration Process

The USB protocol is a master/slave protocol. This is the host that starts the enumeration sending requests to the device through the control endpoint. The device handles standard requests as defined in the USB Specification.

Table 23-3. Handled Standard Requests

| Request           | Definition                                            |

|-------------------|-------------------------------------------------------|

| GET_DESCRIPTOR    | Returns the current device configuration value.       |

| SET_ADDRESS       | Sets the device address for all future device access. |

| SET_CONFIGURATION | Sets the device configuration.                        |

| GET_CONFIGURATION | Returns the current device configuration value.       |

| GET_STATUS        | Returns status for the specified recipient.           |

| SET_FEATURE       | Set or Enable a specific feature.                     |

| CLEAR_FEATURE     | Clear or Disable a specific feature.                  |

The device also handles some class requests defined in the CDC class.

Table 23-4. Handled Class Requests

| Request                | Definition                                                                 |

|------------------------|----------------------------------------------------------------------------|

| SET_LINE_CODING        | Configures DTE rate, stop bits, parity and number of character bits.       |

| GET_LINE_CODING        | Requests current DTE rate, stop bits, parity and number of character bits. |

| SET_CONTROL_LINE_STATE | RS-232 signal used to tell the DCE device the DTE device is now present.   |

Unhandled requests are STALLed.

# 23.6.3.2 Communication Endpoints

There are two communication endpoints and endpoint 0 is used for the enumeration process. Endpoint 1 is a 64-byte Bulk OUT endpoint and endpoint 2 is a 64-byte Bulk IN endpoint. SAM-BA Boot commands are sent by the host through endpoint 1. If required, the message is split by the host into several data payloads by the host driver.

If the command requires a response, the host can send IN transactions to pick up the response.

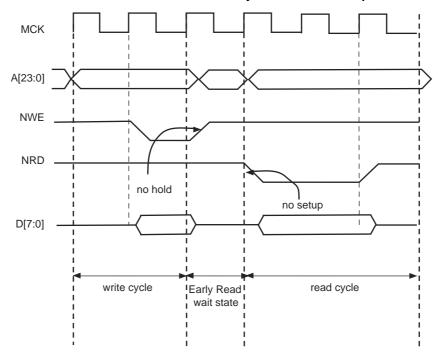

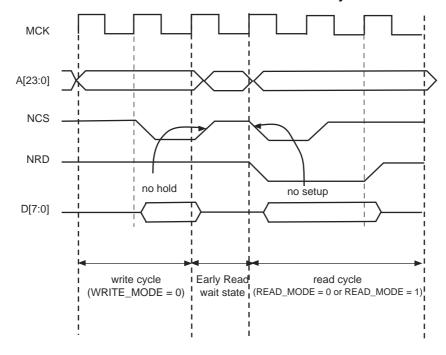

write control signal is not inactivated as expected due to load capacitances, an Early Read Wait State is inserted and address, data and control signals are maintained one more cycle. See Figure 27-16.

Figure 27-14. Early Read Wait State: Write with No Hold Followed by Read with No Setup

Figure 27-15. Early Read Wait State: NCS-controlled write with no hold followed by a read with no NCS setup

# 29.8 Peripheral Clock Controller

The PMC controls the clocks of each embedded peripheral by means of the Peripheral Clock Controller. The user can individually enable and disable the clock on the peripherals.

The user can also enable and disable these clocks by writing Peripheral Clock Enable 0 (PMC\_PCER0), Peripheral Clock Disable 0 (PMC\_PCDR0), Peripheral Clock Enable 1 (PMC\_PCER1) and Peripheral Clock Disable 1 (PMC\_PCDR1) registers. The status of the peripheral clock activity can be read in the Peripheral Clock Status Register (PMC\_PCSR0) and Peripheral Clock Status Register (PMC\_PCSR1).

When a peripheral clock is disabled, the clock is immediately stopped. The peripheral clocks are automatically disabled after a reset.

To stop a peripheral, it is recommended that the system software wait until the peripheral has executed its last programmed operation before disabling the clock. This is to avoid data corruption or erroneous behavior of the system.

The bit number within the Peripheral Clock Control registers (PMC\_PCER0-1, PMC\_PCDR0-1, and PMC\_PCSR0-1) is the Peripheral Identifier defined at the product level. The bit number corresponds to the interrupt source number assigned to the peripheral.

# 29.9 Free-Running Processor Clock

The free-running processor clock (FCLK)used for sampling interrupts and clocking debug blocks ensures that interrupts can be sampled, and sleep events can be traced, while the processor is sleeping. It is connected to master clock (MCK).

# 29.10 Programmable Clock Output Controller

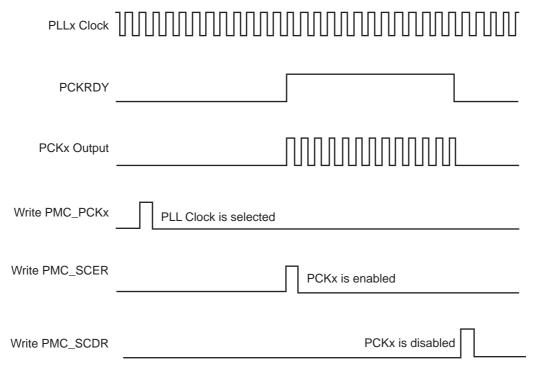

The PMC controls three signals to be output on external pins, PCKx. Each signal can be independently programmed via the Programmable Clock Registers (PMC\_PCKx).

PCKx can be independently selected between the slow clock (SLCK), the main clock (MAINCK), the PLLA clock (PLLACK), and the master clock (MCK) by writing the CSS field in PMC\_PCKx. Each output signal can also be divided by a power of 2 between 1 and 64 by writing the PRES (Prescaler) field in PMC\_PCKx.

Each output signal can be enabled and disabled by writing a 1 to the corresponding PCKx bit of PMC\_SCER and PMC\_SCDR, respectively. Status of the active programmable output clocks are given in the PCKx bits of PMC\_SCSR.

The PCKRDYx status flag in PMC\_SR indicates that the programmable clock is actually what has been programmed in the programmable clock registers.

As the Programmable Clock Controller does not manage with glitch prevention when switching clocks, it is strongly recommended to disable the programmable clock before any configuration change and to re-enable it after the change is actually performed.

# 29.11 Fast Startup

At exit from Wait mode, the device allows the processor to restart in less than 10 microseconds only if the C-code function that manages the Wait mode entry and exit is linked to and executed from on-chip SRAM.

The fast startup time cannot be achieved if the first instruction after an exit is located in the embedded Flash.

If fast startup is not required, or if the first instruction after a Wait mode exit is located in embedded Flash, see Section 29.12 "Startup from Embedded Flash".

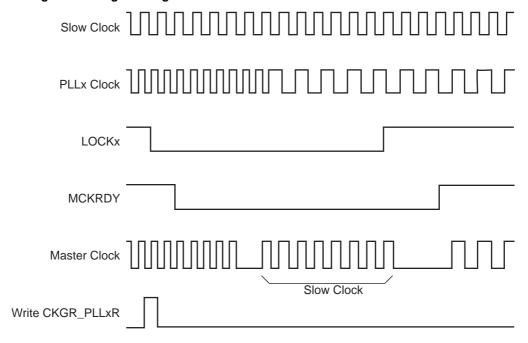

Figure 29-8. Change PLLx Programming

Figure 29-9. Programmable Clock Output Programming

# 29.18.18 PMC Fast Startup Polarity Register

Name: PMC FSPR Address: 0x400E0474 Access: Read/Write 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 12 10 9 8 14 13 11 FSTP15 FSTP14 FSTP13 FSTP12 FSTP11 FSTP10 FSTP9 FSTP8 7 6 5 4 3 2 0 1 FSTP7 FSTP6 FSTP5 FSTP4 FSTP3 FSTP2 FSTP1 FSTP0

This register can only be written if the WPEN bit is cleared in the "PMC Write Protection Mode Register".

# • FSTPx: Fast Startup Input Polarityx

Defines the active polarity of the corresponding wake-up input. If the corresponding wake-up input is enabled and at the FSTP level, it enables a fast restart signal.

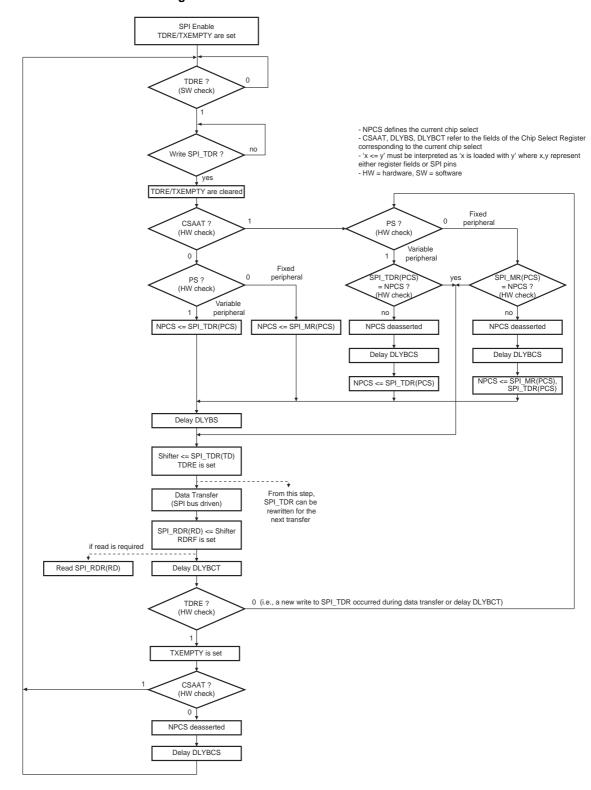

# 34.7.3.2 Master Mode Flow Diagram

Figure 34-7. Master Mode Flow Diagram

# 35.8.13 TWI Write Protection Status Register

Name: TWI\_WPSR

**Address:** 0x400A80E8 (0), 0x400AC0E8 (1)

Access: Read-only

| 31 | 30     | 29 | 28  | 27   | 26 | 25 | 24   |  |

|----|--------|----|-----|------|----|----|------|--|

|    |        |    | WPV | 'SRC |    |    |      |  |

| 23 | 22     | 21 | 20  | 19   | 18 | 17 | 16   |  |

|    | WPVSRC |    |     |      |    |    |      |  |

| 15 | 14     | 13 | 12  | 11   | 10 | 9  | 8    |  |

|    | WPVSRC |    |     |      |    |    |      |  |

| 7  | 6      | 5  | 4   | 3    | 2  | 1  | 0    |  |

| _  | _      | _  | _   | _    | _  | _  | WPVS |  |

### • WPVS: Write Protection Violation Status

0: No write protection violation has occurred since the last read of the TWI\_WPSR.

#### WPVSRC: Write Protection Violation Source

When WPVS = 1, WPVSRC shows the register address offset at which a write access has been attempted.

<sup>1:</sup> A write protection violation has occurred since the last read of the TWI\_WPSR. If this violation is an unauthorized attempt to write a protected register, the violation is reported into field WPVSRC.

36.6.6 UART Status Register

Name: UART SR

Address: 0x400E0614 (0), 0x40060614 (1)

Access: Read-only

| 31   | 30    | 29   | 28     | 27     | 26 | 25      | 24    |

|------|-------|------|--------|--------|----|---------|-------|

| _    | _     | _    | _      | _      | _  | _       | _     |

| 23   | 22    | 21   | 20     | 19     | 18 | 17      | 16    |

| _    | ı     | _    | _      | _      | _  | ı       | _     |

| 15   | 14    | 13   | 12     | 11     | 10 | 9       | 8     |

| _    | ı     | _    | RXBUFF | TXBUFE | _  | TXEMPTY | _     |

| 7    | 6     | 5    | 4      | 3      | 2  | 1       | 0     |

| PARE | FRAME | OVRE | ENDTX  | ENDRX  | _  | TXRDY   | RXRDY |

# • RXRDY: Receiver Ready

0: No character has been received since the last read of the UART\_RHR, or the receiver is disabled.

1: At least one complete character has been received, transferred to UART\_RHR and not yet read.

### TXRDY: Transmitter Ready

0: A character has been written to UART\_THR and not yet transferred to the internal shift register, or the transmitter is disabled.

1: There is no character written to UART\_THR not yet transferred to the internal shift register.

### ENDRX: End of Receiver Transfer

0: The end of transfer signal from the receiver PDC channel is inactive.

1: The end of transfer signal from the receiver PDC channel is active.

# • ENDTX: End of Transmitter Transfer

0: The end of transfer signal from the transmitter PDC channel is inactive.

1: The end of transfer signal from the transmitter PDC channel is active.

### OVRE: Overrun Error

0: No overrun error has occurred since the last RSTSTA.

1: At least one overrun error has occurred since the last RSTSTA.

### • FRAME: Framing Error

0: No framing error has occurred since the last RSTSTA.

1: At least one framing error has occurred since the last RSTSTA.

# • PARE: Parity Error

0: No parity error has occurred since the last RSTSTA.

1: At least one parity error has occurred since the last RSTSTA.

### TXEMPTY: Transmitter Empty

0: There are characters in UART\_THR, or characters being processed by the transmitter, or the transmitter is disabled.

1: There are no characters in UART\_THR and there are no characters being processed by the transmitter.

37.7.1 USART Control Register

Name: US\_CR

Address: 0x400A0000 (0), 0x400A4000 (1)

Access: Write-only

| 31    | 30      | 29    | 28    | 27     | 26     | 25     | 24     |

|-------|---------|-------|-------|--------|--------|--------|--------|

| _     | _       | _     | _     | _      | _      | _      | -      |

| 23    | 22      | 21    | 20    | 19     | 18     | 17     | 16     |

| _     | -       | -     | -     | RTSDIS | RTSEN  | DTRDIS | DTREN  |

|       | -       | -     | -     | -      | •      | •      | -      |

| 15    | 14      | 13    | 12    | 11     | 10     | 9      | 8      |

| RETTO | RSTNACK | RSTIT | SENDA | STTTO  | STPBRK | STTBRK | RSTSTA |

|       |         |       |       |        |        |        |        |

| 7     | 6       | 5     | 4     | 3      | 2      | 1      | 0      |

| TXDIS | TXEN    | RXDIS | RXEN  | RSTTX  | RSTRX  | _      | -      |

For SPI control, see Section 37.7.2 "USART Control Register (SPI\_MODE)".

# • RSTRX: Reset Receiver

0: No effect.

1: Resets the receiver.

### RSTTX: Reset Transmitter

0: No effect.

1: Resets the transmitter.

# • RXEN: Receiver Enable

0: No effect.

1: Enables the receiver, if RXDIS is 0.

# • RXDIS: Receiver Disable

0: No effect.

1: Disables the receiver.

### • TXEN: Transmitter Enable

0: No effect.

1: Enables the transmitter if TXDIS is 0.

# • TXDIS: Transmitter Disable

0: No effect.

1: Disables the transmitter.

# • RSTSTA: Reset Status Bits

0: No effect.

1: Resets the status bits PARE, FRAME, OVRE, MANERR and RXBRK in US\_CSR.

# 37.7.22 USART Write Protection Mode Register

Name: US\_WPMR

Address: 0x400A00E4 (0), 0x400A40E4 (1)

Access: Read/Write

| 31 | 30 | 29 | 28 | 27  | 26 | 25 | 24   |

|----|----|----|----|-----|----|----|------|

|    |    |    | WP | KEY |    |    |      |

| 23 | 22 | 21 | 20 | 19  | 18 | 17 | 16   |

|    |    |    | WP | KEY |    |    |      |

| 15 | 14 | 13 | 12 | 11  | 10 | 9  | 8    |

|    |    |    | WP | KEY |    |    |      |

| 7  | 6  | 5  | 4  | 3   | 2  | 1  | 0    |

| _  | _  | _  | _  | _   | _  | _  | WPEN |

# • WPEN: Write Protection Enable

0: Disables the write protection if WPKEY corresponds to 0x555341 ("USA" in ASCII).

1: Enables the write protection if WPKEY corresponds to 0x555341 ("USA" in ASCII).

See Section 37.6.10 "Register Write Protection" for the list of registers that can be write-protected.

# • WPKEY: Write Protection Key

| Value    | Name   | Description                                                                                          |

|----------|--------|------------------------------------------------------------------------------------------------------|

| 0x555341 | PASSWD | Writing any other value in this field aborts the write operation of the WPEN bit. Always reads as 0. |

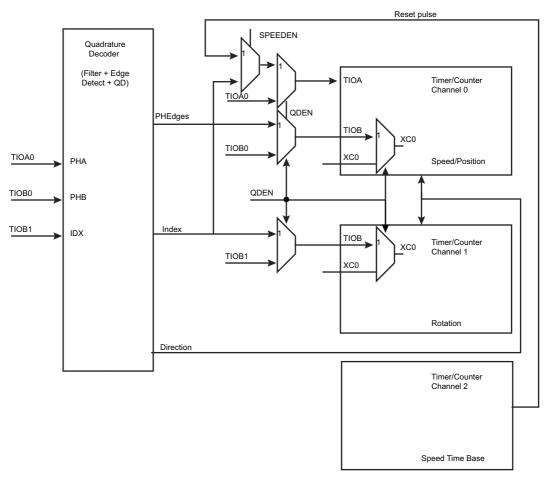

Figure 38-17. Predefined Connection of the Quadrature Decoder with Timer Counters

# 38.6.16.2 Input Pre-processing

Input pre-processing consists of capabilities to take into account rotary sensor factors such as polarities and phase definition followed by configurable digital filtering.

Each input can be negated and swapping PHA, PHB is also configurable.

The MAXFILT field in the TC\_BMR is used to configure a minimum duration for which the pulse is stated as valid. When the filter is active, pulses with a duration lower than MAXFILT +1  $\times$  t<sub>peripheral clock</sub> ns are not passed to down-stream logic.

All of the PWM outputs may or may not be enabled. If an application requires only four channels, then only four PIO lines are assigned to PWM outputs.

### 39.5.2 Power Management

The PWM is not continuously clocked. The programmer must first enable the PWM clock in the Power Management Controller (PMC) before using the PWM. However, if the application does not require PWM operations, the PWM clock can be stopped when not needed and be restarted later. In this case, the PWM will resume its operations where it left off.

# 39.5.3 Interrupt Sources

The PWM interrupt line is connected on one of the internal sources of the Interrupt Controller. Using the PWM interrupt requires the Interrupt Controller to be programmed first.

# 39.5.4 Fault Inputs

The PWM has the fault inputs connected to the different modules. Refer to the implementation of these modules within the product for detailed information about the fault generation procedure. The PWM receives faults from:

- PIO inputs

- the PMC

- the ADC controller

- the Analog Comparator Controller

- Timer/Counters

Table 39-2. Fault Inputs

| Fault Generator | External PWM Fault Input Number | Polarity Level <sup>(1)</sup> | Fault Input ID |

|-----------------|---------------------------------|-------------------------------|----------------|

| Main OSC (PMC)  | -                               | To be configured to 1         | 0              |

| ADC             | -                               | To be configured to 1         | 1              |

| PXyy            | PWMFI0                          | User-defined                  | 2              |

| PXyy            | PWMFI1                          | User-defined                  | 3              |

| PXyy            | PWMFI2                          | User-defined                  | 4              |

| PXyy            | PWMFI3                          | User-defined                  | 5              |

| PXyy            | PWMFI4                          | User-defined                  | 6              |

| PXyy            | PWMFI5                          | User-defined                  | 7              |

Note: 1. FPOL field in PWMC\_FMR.

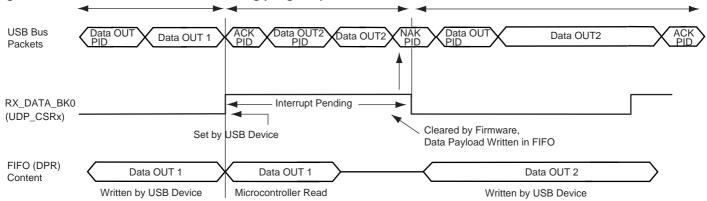

Figure 41-9. Data OUT Transfer for Non Ping-pong Endpoints

An interrupt is pending while the flag RX\_DATA\_BK0 is set. Memory transfer between the USB device, the FIFO and microcontroller memory is not possible after RX\_DATA\_BK0 has been cleared. Otherwise, the USB device would accept the next Data OUT transfer and overwrite the current Data OUT packet in the FIFO.

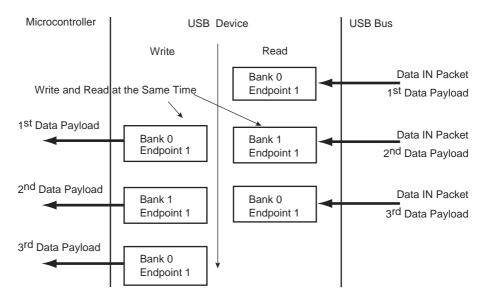

### **Using Endpoints With Ping-pong Attributes**

During isochronous transfer, using an endpoint with ping-pong attributes is obligatory. To be able to guarantee a constant bandwidth, the microcontroller must read the previous data payload sent by the host, while the current data payload is received by the USB device. Thus two banks of memory are used. While one is available for the microcontroller, the other one is locked by the USB device.

Figure 41-10. Bank Swapping in Data OUT Transfers for Ping-pong Endpoints

When using a ping-pong endpoint, the following procedures are required to perform Data OUT transactions:

- 1. The host generates a Data OUT packet.

- 2. This packet is received by the USB device endpoint. It is written in the endpoint's FIFO Bank 0.

- The USB device sends an ACK PID packet to the host. The host can immediately send a second Data OUT packet. It is accepted by the device and copied to FIFO Bank 1.

- 4. The microcontroller is notified that the USB device has received a data payload, polling RX\_DATA\_BK0 in the endpoint's UDP\_CSRx. An interrupt is pending for this endpoint while RX\_DATA\_BK0 is set.

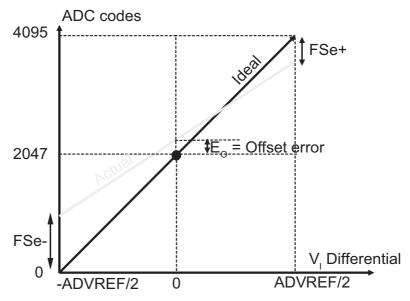

# **Differential Mode**

In differential mode, the offset is defined when the differential input voltage is zero.

Figure 46-16. Gain and Offset Errors in Differential Mode

#### where:

- FSe = (FSe+) (FSe-) is for full-scale error, unit is LSB code

- Offset error E<sub>O</sub> is the offset error measured for V<sub>I</sub> = 0V

- Gain error  $E_G = 100 \times FSe / 4096$ , unit in %

The error values in Table 46-35 and Table 46-36 include the sample and hold error as well as the PGA gain error.

Table 46-35. Differential Gain Error E<sub>G</sub>

| Gain Mode              | 0.5    |        |        | 1      | 2      |        |

|------------------------|--------|--------|--------|--------|--------|--------|

| Auto Correction        | No     | Yes    | No     | Yes    | No     | Yes    |

| Average Gain Error (%) | -0.107 | 0.005  | 0.444  | 0.112  | 0.713  | 0.005  |

| Standard Deviation (%) | 0.410  | 0.210  | 0.405  | 0.229  | 0.400  | 0.317  |

| Gain Min Value (%)     | -1.338 | -0.625 | -0.771 | -0.576 | -0.488 | -0.947 |

| Gain Max Value (%)     | 1.123  | 0.635  | 1.660  | 0.801  | 1.914  | 0.957  |

Table 46-36. Differential Output Offset Error E<sub>O</sub>

| Gain                       | 0.5  | 1    | 2    |

|----------------------------|------|------|------|

| Average Offset Error (LSB) | -1.2 | -1.2 | -0.6 |

| Standard Deviation (LSB)   | 0.3  | 0.4  | 0.4  |

| Offset Min value (LSB)     | -2.1 | -2.4 | -1.8 |

| Offset Max value (LSB)     | -0.3 | 0    | 0.6  |

|     | 11.5        | Power Management                            | 74    |

|-----|-------------|---------------------------------------------|-------|

|     | 11.6        | Cortex-M4 Instruction Set                   | 76    |

|     | 11.7        | Cortex-M4 Core Peripherals                  | . 218 |

|     | 11.8        | Nested Vectored Interrupt Controller (NVIC) | . 219 |

|     | 11.9        | System Control Block (SCB)                  | . 229 |

|     | 11.10       | System Timer (SysTick)                      | 256   |

|     | 11.11       | Memory Protection Unit (MPU)                | 262   |

|     | 11.12       | Floating Point Unit (FPU)                   | . 285 |

|     | 11.13       | Glossary                                    | . 294 |

| 4.0 |             |                                             |       |

| 12. |             | ıg and Test Features                        |       |

|     | 12.1        | Description                                 |       |

|     | 12.2        | Embedded Characteristics                    |       |

|     | 12.3        | Debug and Test Block Diagram                |       |

|     | 12.4        | Application Examples                        | . 300 |

|     | 12.5        | Debug and Test Pin Description              | . 301 |

|     | 12.6        | Functional Description                      | 302   |

| 40  | D           | A Controller (DCTC)                         |       |

| 13. |             | et Controller (RSTC)                        |       |

|     | 13.1        | Description                                 |       |

|     | 13.2        | Embedded Characteristics                    |       |

|     | 13.3        | Block Diagram                               |       |

|     | 13.4        | Functional Description.                     |       |

|     | 13.5        | Reset Controller (RSTC) User Interface      | . 315 |

| 14  | Real.       | -time Timer (RTT)                           | 310   |

|     | 14.1        | Description                                 |       |

|     | 14.1        | Embedded Characteristics                    |       |

|     | 14.2        | Block Diagram                               |       |

|     | 14.3        | Functional Description.                     |       |

|     | 14.4        | Real-time Timer (RTT) User Interface.       |       |

|     | 14.5        | Real-time timer (RTT) Oser interface        | . 322 |

| 15. | Real-       | -time Clock (RTC)                           | . 327 |

|     | 15.1        | Description                                 |       |

|     | 15.2        | Embedded Characteristics                    |       |

|     | 15.3        | Block Diagram                               |       |

|     | 15.4        | Product Dependencies                        |       |

|     | 15.5        | Functional Description.                     |       |

|     | 15.6        | Real-time Clock (RTC) User Interface        |       |

|     |             |                                             |       |

| 16. | Wato        | hdog Timer (WDT)                            | . 356 |

|     | 16.1        | Description                                 | 356   |

|     | 16.2        | Embedded Characteristics                    | 356   |

|     | 16.3        | Block Diagram                               | . 357 |

|     | 16.4        | Functional Description                      | 358   |

|     | 16.5        | Watchdog Timer (WDT) User Interface         | 360   |

|     |             |                                             |       |

| 17. | Rein        | forced Safety Watchdog Timer (RSWDT)        |       |

|     | 17.1        | Description                                 | 365   |

|     | 17.2        | Embedded Characteristics                    | 365   |

|     | 17.3        | Block Diagram                               | . 366 |

|     | 17 <i>4</i> | Functional Description.                     | 366   |