Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, Ethernet, IrDA, SD, SPI, UART/USART, USB                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 117                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128K × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LFBGA                                                                |

| Supplier Device Package    | 144-LFBGA (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4e8eb-cnr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 11.6.5.20 UHSUB16 and UHSUB8

Unsigned Halving Subtract 16 and Unsigned Halving Subtract 8

Syntax

op{cond}{Rd,} Rn, Rm

where:

| ор   | is any of:                                                                                                                      |

|------|---------------------------------------------------------------------------------------------------------------------------------|

|      | UHSUB16 Performs two unsigned 16-bit integer additions, halves the results, and writes the results to the destination register. |

|      | UHSUB8 Performs four unsigned 8-bit integer additions, halves the results, and writes the results to the destination register.  |

| cond | is an optional condition code, see "Conditional Execution" .                                                                    |

| Rd   | is the destination register.                                                                                                    |

| Rn   | is the first register holding the operand.                                                                                      |

| Rm   | is the second register holding the operand.                                                                                     |

#### Operation

Use these instructions to add 16-bit and 8-bit data and then to halve the result before writing the result to the destination register:

The UHSUB16 instruction:

- 1. Subtracts each halfword of the second operand from the corresponding halfword of the first operand.

- 2. Shuffles each halfword result to the right by one bit, halving the data.

- 3. Writes each unsigned halfword result to the corresponding halfwords in the destination register.

#### The UHSUB8 instruction:

- 1. Subtracts each byte of second operand from the corresponding byte of the first operand.

- 2. Shuffles each byte result by one bit to the right, halving the data.

- 3. Writes the unsigned byte results to the corresponding byte of the destination register.

Restrictions

Do not use SP and do not use PC.

**Condition Flags**

These instructions do not change the flags.

Examples

UHSUB16 R1, R0 ; Subtracts halfwords in R0 from corresponding halfword of ; R1 and writes halved result to corresponding halfword in R1 UHSUB8 R4, R0, R5 ; Subtracts bytes of R5 from corresponding byte in R0 and ; writes halved result to corresponding byte in R4.

## 11.8.3 Nested Vectored Interrupt Controller (NVIC) User Interface

| Offset                                         | Register                           | Name       | Access     | Reset      |

|------------------------------------------------|------------------------------------|------------|------------|------------|

| 0xE000E100                                     | Interrupt Set-enable Register 0    | NVIC_ISER0 | Read/Write | 0x0000000  |

|                                                |                                    |            |            |            |

| 0xE000E11C                                     | Interrupt Set-enable Register 7    | NVIC_ISER7 | Read/Write | 0x0000000  |

| 0XE000E180                                     | Interrupt Clear-enable Register 0  | NVIC_ICER0 | Read/Write | 0x0000000  |

|                                                |                                    |            |            |            |

| 0xE000E19C                                     | Interrupt Clear-enable Register 7  | NVIC_ICER7 | Read/Write | 0x0000000  |

| 0XE000E200                                     | Interrupt Set-pending Register 0   | NVIC_ISPR0 | Read/Write | 0x00000000 |

|                                                |                                    |            |            |            |

| 0xE000E21C                                     | Interrupt Set-pending Register 7   | NVIC_ISPR7 | Read/Write | 0x0000000  |

| 0XE000E280                                     | Interrupt Clear-pending Register 0 | NVIC_ICPR0 | Read/Write | 0x00000000 |

|                                                |                                    |            |            |            |

| 0xE000E29C                                     | Interrupt Clear-pending Register 7 | NVIC_ICPR7 | Read/Write | 0x0000000  |

| 0xE000E300                                     | Interrupt Active Bit Register 0    | NVIC_IABR0 | Read/Write | 0x0000000  |

|                                                |                                    |            |            |            |

| 0xE000E31C                                     | Interrupt Active Bit Register 7    | NVIC_IABR7 | Read/Write | 0x0000000  |

| 0xE000E400                                     | Interrupt Priority Register 0      | NVIC_IPR0  | Read/Write | 0x0000000  |

|                                                |                                    |            |            |            |

| 0XE000E42C                                     | Interrupt Priority Register 12     | NVIC_IPR12 | Read/Write | 0x00000000 |

| 0xE000EF00 Software Trigger Interrupt Register |                                    | NVIC_STIR  | Write-only | 0x00000000 |

#### Table 11-32. Nested Vectored Interrupt Controller (NVIC) Register Mapping

11.11.2.6 MPU Region Base Address Register Alias 1

| Name:   | MPU_RBAR_A1 |    |       |    |     |      |    |

|---------|-------------|----|-------|----|-----|------|----|

| Access: | Read/Write  |    |       |    |     |      |    |

| 31      | 30          | 29 | 28    | 27 | 26  | 25   | 24 |

|         |             |    | AD    | DR |     |      |    |

| 23      | 22          | 21 | 20    | 19 | 18  | 17   | 16 |

|         |             |    | AD    | DR |     |      |    |

| 15      | 14          | 13 | 12    | 11 | 10  | 9    | 8  |

|         |             |    | AD    | DR |     |      |    |

| 7       | 6           | 5  | 4     | 3  | 2   | 1    | 0  |

|         | ADDR        |    | VALID |    | REG | SION |    |

The MPU\_RBAR defines the base address of the MPU region selected by the MPU\_RNR, and can update the value of the MPU\_RNR.

Write MPU\_RBAR with the VALID bit set to 1 to change the current region number and update the MPU\_RNR.

# • ADDR: Region Base Address

Software must ensure that the value written to the ADDR field aligns with the size of the selected region.

The value of N depends on the region size. The ADDR field is bits[31:N] of the MPU\_RBAR. The region size, as specified by the SIZE field in the MPU\_RASR, defines the value of N:

N = Log2(Region size in bytes),

If the region size is configured to 4 GB, in the MPU\_RASR, there is no valid ADDR field. In this case, the region occupies the complete memory map, and the base address is 0x00000000.

The base address is aligned to the size of the region. For example, a 64 KB region must be aligned on a multiple of 64 KB, for example, at 0x00010000 or 0x00020000.

## • VALID: MPU Region Number Valid

Write:

.....

0: MPU\_RNR not changed, and the processor updates the base address for the region specified in the MPU\_RNR, and ignores the value of the REGION field.

1: The processor updates the value of the MPU\_RNR to the value of the REGION field, and updates the base address for the region specified in the REGION field.

Always reads as zero.

## • REGION: MPU Region

For the behavior on writes, see the description of the VALID field.

On reads, returns the current region number, as specified by the MPU\_RNR.

# 12.4 Application Examples

## 12.4.1 Debug Environment

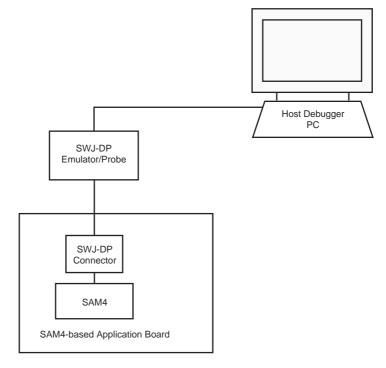

Figure 12-2 shows a complete debug environment example. The SWJ-DP interface is used for standard debugging functions, such as downloading code and single-stepping through the program and viewing core and peripheral registers.

#### Figure 12-2. Application Debug Environment Example

#### 12.4.2 Test Environment

Figure 12-3 shows a test environment example (JTAG Boundary scan). Test vectors are sent and interpreted by the tester. In this example, the "board in test" is designed using a number of JTAG-compliant devices. These devices can be connected to form a single scan chain.

• **Time stamping**: Timestamps are emitted relative to packets. The ITM contains a 21-bit counter to generate the timestamp.

#### 12.6.8.1 How to Configure the ITM

The following example describes how to output trace data in asynchronous trace mode.

- Configure the TPIU for asynchronous trace mode (refer to Section 12.6.8.3 "How to Configure the TPIU")

- Enable the write accesses into the ITM registers by writing "0xC5ACCE55" into the Lock Access Register (Address: 0xE0000FB0)

- Write 0x00010015 into the Trace Control Register:

- Enable ITM

- Enable Synchronization packets

- Enable SWO behavior

- Fix the ATB ID to 1

- Write 0x1 into the Trace Enable Register:

- Enable the Stimulus port 0

- Write 0x1 into the Trace Privilege Register:

- Stimulus port 0 only accessed in privileged mode (Clearing a bit in this register will result in the corresponding stimulus port being accessible in user mode.)

- Write into the Stimulus port 0 register: TPIU (Trace Port Interface Unit)

The TPIU acts as a bridge between the on-chip trace data and the Instruction Trace Macrocell (ITM).

The TPIU formats and transmits trace data off-chip at frequencies asynchronous to the core.

## 12.6.8.2 Asynchronous Mode

The TPIU is configured in asynchronous mode, trace data are output using the single TRACESWO pin. The TRACESWO signal is multiplexed with the TDO signal of the JTAG Debug Port. As a consequence, asynchronous trace mode is only available when the Serial Wire Debug mode is selected since TDO signal is used in JTAG debug mode.

Two encoding formats are available for the single pin output:

- Manchester encoded stream. This is the reset value.

- NRZ\_based UART byte structure

## 12.6.8.3 How to Configure the TPIU

This example only concerns the asynchronous trace mode.

- Set the TRCENA bit to 1 into the Debug Exception and Monitor Register (0xE000EDFC) to enable the use of trace and debug blocks.

- Write 0x2 into the Selected Pin Protocol Register

- Select the Serial Wire Output NRZ

- Write 0x100 into the Formatter and Flush Control Register

- Set the suitable clock prescaler value into the Async Clock Prescaler Register to scale the baud rate of the asynchronous output (this can be done automatically by the debugging tool).

# 12.6.9 IEEE<sup>®</sup> 1149.1 JTAG Boundary Scan

IEEE 1149.1 JTAG Boundary Scan allows pin-level access independent of the device packaging technology.

IEEE1149.1 JTAG Boundary Scan is enabled when TST is tied to high, PA7 tied low, and JTAGSEL tied to high during power-up. These pins must be maintained in their respective states for the duration of the boundary scan operation.

#### 18.4.7.2 Wake-up Inputs

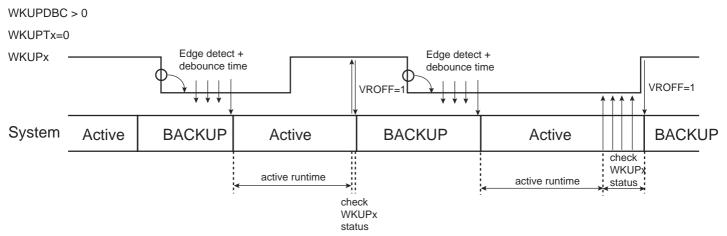

The wake-up inputs, WKUPx, can be programmed to perform a wake-up of the core power supply. Each input can be enabled by writing a 1 to the corresponding bit, WKUPENx, in the Wake-up Inputs register (SUPC\_WUIR). The wake-up level can be selected with the corresponding polarity bit, WKUPTx, also located in SUPC\_WUIR.

The resulting signals are wired-ORed to trigger a debounce counter, which is programmed with the WKUPDBC field in SUPC\_WUMR. The WKUPDBC field selects a debouncing period of 3, 32, 512, 4,096 or 32,768 slow clock cycles. The duration of these periods corresponds, respectively, to about 100 µs, about 1 ms, about 16 ms, about 128 ms and about 1 second (for a typical slow clock frequency of 32 kHz). Programming WKUPDBC to 0x0 selects an immediate wake-up, i.e., an enabled WKUP pin must be active according to its polarity during a minimum of one slow clock period to wake up the core power supply.

If an enabled WKUP pin is asserted for a duration longer than the debouncing period, a wake-up of the core power supply is started and the signals, WKUP0 to WKUPx as shown in Figure 18-4 "Wake-up Sources", are latched in SUPC\_SR. This allows the user to identify the source of the wake-up. However, if a new wake-up condition occurs, the primary information is lost. No new wake-up can be detected since the primary wake-up condition has disappeared.

Before instructing the system to enter Backup mode, if the field WKUPDBC > 0, it must be checked that none of the WKUPx pins that are enabled for a wake-up (exit from Backup mode) holds an active polarity. This is checked by reading the pin status in the PIO Controller. If WKUPENx=1 and the pin WKUPx holds an active polarity, the system must not be instructed to enter Backup mode.

#### Figure 18-5. Entering and Exiting Backup Mode with a WKUP Pin

#### 18.4.7.3 Low-power Tamper Detection and Anti-Tampering

Low-power debouncer inputs (WKUP0, WKUP1) can be used for tamper detection. If the tamper sensor is biased through a resistor and constantly driven by the power supply, this leads to power consumption as long as the tamper detection switch is in its active state. To prevent power consumption when the switch is in active state, the tamper sensor circuitry must be intermittently powered, and thus a specific waveform must be applied to the sensor circuitry.

The waveform is generated using RTCOUTx in all modes including Backup mode. Refer to the section "Real-Time Clock (RTC)" for waveform generation.

Separate debouncers are embedded, one for WKUP0 input, one for WKUP1 input.

The WKUP0 and/or WKUP1 inputs perform a system wake-up upon tamper detection. This is enabled by setting the LPDBCEN0/1 bit in the SUPC\_WUMR.

WKUP0 and/or WKUP1 inputs can also be used when VDDCORE is powered to detect a tamper.

| 24.12.7  | Write Protect Mode Register |    |    |     |    |    |      |

|----------|-----------------------------|----|----|-----|----|----|------|

| Name:    | MATRIX_WPMF                 | R  |    |     |    |    |      |

| Address: | 0x400E03E4                  |    |    |     |    |    |      |

| Access:  | Read-write                  |    |    |     |    |    |      |

| 31       | 30                          | 29 | 28 | 27  | 26 | 25 | 24   |

|          |                             |    | WP | KEY |    |    |      |

| 23       | 22                          | 21 | 20 | 19  | 18 | 17 | 16   |

|          |                             |    | WP | KEY |    |    |      |

| 15       | 14                          | 13 | 12 | 11  | 10 | 9  | 8    |

|          |                             |    | WP | KEY |    |    |      |

| 7        | 6                           | 5  | 4  | 3   | 2  | 1  | 0    |

| -        | -                           | -  | -  | -   | -  | _  | WPEN |

For more details on MATRIX\_WPMR, please refer to Section 24.11 "Write Protect Registers".

The protected registers are:

"Bus Matrix Master Configuration Registers"

"Bus Matrix Slave Configuration Registers"

"Bus Matrix Priority Registers A For Slaves"

"Bus Matrix Master Remap Control Register"

"Write Protect Mode Register"

## • WPEN: Write Protect Enable

0: Disables the Write Protect if WPKEY corresponds to 0x4D4154 ("MAT" in ASCII).

1: Enables the Write Protect if WPKEY corresponds to 0x4D4154 ("MAT" in ASCII).

Protects the entire Bus Matrix address space from address offset 0x000 to 0x1FC.

## • WPKEY: Write Protect KEY (Write-only)

| Value    | Name   | Description                                                                       |  |  |

|----------|--------|-----------------------------------------------------------------------------------|--|--|

| 0x4D4154 | PASSWD | Writing any other value in this field aborts the write operation of the WPEN bit. |  |  |

|          |        | Always reads as 0.                                                                |  |  |

- 4. After the DMAC selected channel has been programmed, enable the channel by setting the ENAx bit in the DMAC Channel Handler Enable Register (DMAC\_CHER), where x is the channel number. Make sure that the ENABLE bit (register bit 0) in DMAC\_EN is set.

- 5. Source and destination request single and chunk DMAC transactions to transfer the buffer of data (assuming non-memory peripherals). The DMAC acknowledges at the completion of every transaction (chunk and single) in the buffer and carries out the buffer transfer.

- 6. Once the transfer completes, the hardware sets the interrupts and disables the channel. At this time, you can either respond to the Buffer Transfer Completed Interrupt or Chained Buffer Transfer Completed Interrupt, or poll for the DMAC\_CHSR.ENAx bit until it is cleared by hardware, to detect when the transfer is complete.

Multi-buffer Transfer with Linked List for Source and Linked List for Destination (Row 4)

- 1. Read the DMAC\_CHSR to choose a free (disabled) channel.

- Set up the chain of Linked List Items (otherwise known as buffer descriptors) in memory. Write the control

information in the LLI.DMAC\_CTRLAx and LLI.DMAC\_CTRLBx registers location of the buffer descriptor for

each LLI in memory (see Figure 25-5 on page 476) for channel x. For example, in the register, it is possible

to program the following:

- a. Set up the transfer type (memory or non-memory peripheral for source and destination) and flow control device by programming the FC field in DMAC\_CTRLBx.

- b. Set up the transfer characteristics, such as:

- i. Transfer width for the source in the SRC\_WIDTH field.

- ii. Transfer width for the destination in the DST\_WIDTH field.

- v. Incrementing/decrementing or fixed address for source in SRC\_INCR field.

- vi. Incrementing/decrementing or fixed address for destination DST\_INCR field.

- 3. Write the channel configuration information into DMAC\_CFGx for channel x.

- a. Designate the handshaking interface type (hardware or software) for the source and destination peripherals. This is not required for memory. This step requires programming the SRC\_H2SEL/DST\_H2SEL bits, respectively. Writing a '1' activates the hardware handshaking interface to handle source/destination requests for the specific channel. Writing a '0' activates the software handshaking interface to handle source/destination requests.

- b. If the hardware handshaking interface is activated for the source or destination peripheral, assign the handshaking interface to the source and destination peripheral. This requires programming the SRC\_PER and DST\_PER bits, respectively.

- 4. Make sure that the LLI.DMAC\_CTRLBx register locations of all LLI entries in memory (except the last) are set as shown in Row 4 of Table 25-3 on page 473. The LLI.DMAC\_CTRLBx register of the last Linked List Item must be set as described in Row 1 of Table 25-3. Figure 25-4 on page 473 shows a Linked List example with two list items.

- 5. Make sure that the LLI.DMAC\_DSCRx register locations of all LLI entries in memory (except the last) are non-zero and point to the base address of the next Linked List Item.

- 6. Make sure that the LLI.DMAC\_SADDRx/LLI.DMAC\_DADDRx register locations of all LLI entries in memory point to the start source/destination buffer address preceding that LLI fetch.

- 7. Make sure that the LLI.DMAC\_CTRLAx.DONE bit of the LLI.DMAC\_CTRLAx register locations of all LLI entries in memory are cleared.

- 8. Clear any pending interrupts on the channel from the previous DMAC transfer by reading DMAC\_EBCISR.

- 9. Program DMAC\_CTRLBx and DMAC\_CFGx according to Row 4 as shown in Table 25-3 on page 473.

- 10. Program DMAC\_DSCRx with DMAC\_DSCRx(0), the pointer to the first Linked List item.

- 11. Finally, enable the channel by setting the DMAC\_CHER.ENAx bit, where x is the channel number. The transfer is performed.

- 12. The DMAC fetches the first LLI from the location pointed to by DMAC\_DSCRx(0).

| 25.8.3   | DMAC Software S | DMAC Software Single Request Register |        |        |        |        |        |

|----------|-----------------|---------------------------------------|--------|--------|--------|--------|--------|

| Name:    | DMAC_SREQ       |                                       |        |        |        |        |        |

| Address: | 0x400C0008      |                                       |        |        |        |        |        |

| Access:  | Read/Write      |                                       |        |        |        |        |        |

| 31       | 30              | 29                                    | 28     | 27     | 26     | 25     | 24     |

| -        | -               | -                                     | -      | -      | -      | -      | -      |

| 23       | 22              | 21                                    | 20     | 19     | 18     | 17     | 16     |

| _        | -               | -                                     | -      | -      | -      | _      | -      |

| 15       | 14              | 13                                    | 12     | 11     | 10     | 9      | 8      |

| _        | —               | -                                     | -      | -      | -      | -      | -      |

| 7        | 6               | 5                                     | 4      | 3      | 2      | 1      | 0      |

| DSREQ    | 3 SSREQ3        | DSREQ2                                | SSREQ2 | DSREQ1 | SSREQ1 | DSREQ0 | SSREQ0 |

## • DSREQx: Destination Request

Request a destination single transfer on channel i.

# • SSREQx: Source Request

Request a source single transfer on channel i.

| 25.8.5   | DMAC Software Last Transfer Flag Register |        |        |        |        |        |          |

|----------|-------------------------------------------|--------|--------|--------|--------|--------|----------|

| Name:    | DMAC_LAST                                 |        |        |        |        |        |          |

| Address: | 0x400C0010                                |        |        |        |        |        |          |

| Access:  | Read/Write                                |        |        |        |        |        |          |

| 31       | 30                                        | 29     | 28     | 27     | 26     | 25     | 24       |

| -        | -                                         | -      | -      | -      | _      | -      | -        |

|          |                                           |        |        |        |        |        |          |

| 23       | 22                                        | 21     | 20     | 19     | 18     | 17     | 16       |

| _        | -                                         | -      | -      | -      | -      | -      | -        |

|          | -                                         | -      | -      | -      |        | -      | -        |

| 15       | 14                                        | 13     | 12     | 11     | 10     | 9      | 8        |

| _        | -                                         | _      | _      | _      | _      | _      | -        |

| B        |                                           | -      |        | •      |        | -      | <u> </u> |

| 7        | 6                                         | 5      | 4      | 3      | 2      | 1      | 0        |

| DLAST    | 3 SLAST3                                  | DLAST2 | SLAST2 | DLAST1 | SLAST1 | DLAST0 | SLAST0   |

# • DLASTx: Destination Last

Writing one to DLASTx prior to writing one to DSREQx or DCREQx indicates that this destination request is the last transfer of the buffer.

# SLASTx: Source Last

Writing one to SLASTx prior to writing one to SSREQx or SCREQx indicates that this source request is the last transfer of the buffer.

- ENDTX flag is set when the PDC Transmit Counter Register (PERIPH\_TCR) reaches zero.

- TXBUFE flag is set when both PERIPH\_TCR and the PDC Transmit Next Counter Register (PERIPH\_TNCR) reach zero.

These status flags are described in the Transfer Status Register (PERIPH\_PTSR).

## 26.4.4 Data Transfers

The serial peripheral triggers its associated PDC channels' transfers using transmit enable (TXEN) and receive enable (RXEN) flags in the transfer control register integrated in the peripheral's user interface.

When the peripheral receives external data, it sends a Receive Ready signal to its PDC receive channel which then requests access to the Matrix. When access is granted, the PDC receive channel starts reading the peripheral Receive Holding register (RHR). The read data are stored in an internal buffer and then written to memory.

When the peripheral is about to send data, it sends a Transmit Ready to its PDC transmit channel which then requests access to the Matrix. When access is granted, the PDC transmit channel reads data from memory and transfers the data to the Transmit Holding register (THR) of its associated peripheral. The same peripheral sends data depending on its mechanism.

## 26.4.5 PDC Flags and Peripheral Status Register

Each peripheral connected to the PDC sends out receive ready and transmit ready flags and the PDC returns flags to the peripheral. All these flags are only visible in the peripheral's Status register.

Depending on whether the peripheral is half- or full-duplex, the flags belong to either one single channel or two different channels.

#### 26.4.5.1 Receive Transfer End

The receive transfer end flag is set when PERIPH\_RCR reaches zero and the last data has been transferred to memory.

This flag is reset by writing a non-zero value to PERIPH\_RCR or PERIPH\_RNCR.

#### 26.4.5.2 Transmit Transfer End

The transmit transfer end flag is set when PERIPH\_TCR reaches zero and the last data has been written to the peripheral THR.

This flag is reset by writing a non-zero value to PERIPH\_TCR or PERIPH\_TNCR.

## 26.4.5.3 Receive Buffer Full

The receive buffer full flag is set when PERIPH\_RCR reaches zero, with PERIPH\_RNCR also set to zero and the last data transferred to memory.

This flag is reset by writing a non-zero value to PERIPH\_TCR or PERIPH\_TNCR.

#### 26.4.5.4 Transmit Buffer Empty

Atmel

The transmit buffer empty flag is set when PERIPH\_TCR reaches zero, with PERIPH\_TNCR also set to zero and the last data written to peripheral THR.

This flag is reset by writing a non-zero value to PERIPH\_TCR or PERIPH\_TNCR.

| 29.18.14 | PMC Interrupt Di | sable Register |    |        |         |         |          |

|----------|------------------|----------------|----|--------|---------|---------|----------|

| Name:    | PMC_IDR          |                |    |        |         |         |          |

| Address: | 0x400E0464       |                |    |        |         |         |          |

| Access:  | Write-only       |                |    |        |         |         |          |

| 31       | 30               | 29             | 28 | 27     | 26      | 25      | 24       |

| _        | -                | _              | -  | —      | -       | —       | -        |

| 23       | 22               | 21             | 20 | 19     | 18      | 17      | 16       |

| -        | -                | XT32KERR       | -  | _      | CFDEV   | MOSCRCS | MOSCSELS |

| 15       | 14               | 13             | 12 | 11     | 10      | 9       | 8        |

| -        | -                | -              | —  | -      | PCKRDY2 | PCKRDY1 | PCKRDY0  |

| 7        | 6                | 5              | 4  | 3      | 2       | 1       | 0        |

| -        | -                | -              | -  | MCKRDY | _       | LOCKA   | MOSCXTS  |

The following configuration values are valid for all listed bit names of this register:

0: No effect.

- 1: Disables the corresponding interrupt.

- MOSCXTS: 3 to 20 MHz Crystal Oscillator Status Interrupt Disable

- LOCKA: PLLA Lock Interrupt Disable

- MCKRDY: Master Clock Ready Interrupt Disable

- PCKRDYx: Programmable Clock Ready x Interrupt Disable

- MOSCSELS: Main Clock Source Oscillator Selection Status Interrupt Disable

- ٠ MOSCRCS: 4/8/12 MHz RC Oscillator Status Interrupt Disable

- CFDEV: Clock Failure Detector Event Interrupt Disable

- XT32KERR: 32768 Hz Oscillator Error Interrupt Disable

#### 31.8.3.2 Transmission Handling

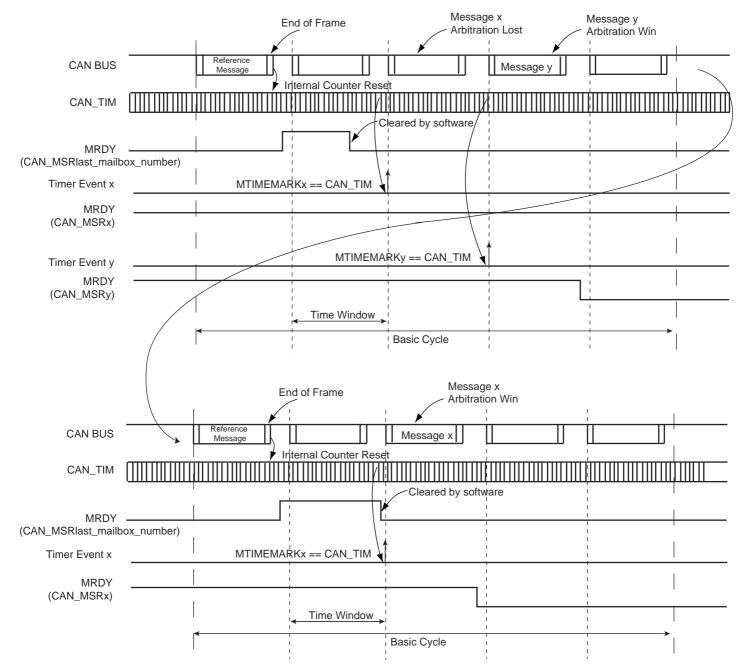

A mailbox is in Transmit Mode once the MOT field in the CAN\_MMRx has been configured. Message ID and Message Acceptance mask must be set before Receive Mode is enabled.

After Transmit Mode is enabled, the MRDY flag in the CAN\_MSR is automatically set until the first command is sent. When the MRDY flag is set, the software application can prepare a message to be sent by writing to the CAN\_MDx registers. The message is sent once the software asks for a transfer command setting the MTCR bit and the message data length in the CAN\_MCRx.

The MRDY flag remains at zero as long as the message has not been sent or aborted. It is important to note that no access to the mailbox data register is allowed while the MRDY flag is cleared. An interrupt is pending for the mailbox while the MRDY flag is set. This interrupt can be masked depending on the mailbox flag in the CAN\_IMR global register.

It is also possible to send a remote frame setting the MRTR bit instead of setting the MDLC field. The answer to the remote frame is handled by another reception mailbox. In this case, the device acts as a consumer but with the help of two mailboxes. It is possible to handle the remote frame emission and the answer reception using only one mailbox configured in Consumer Mode. Refer to the section "Remote Frame Handling" on page 664.

Several messages can try to win the bus arbitration in the same time. The message with the highest priority is sent first. Several transfer request commands can be generated at the same time by setting MBx bits in the CAN\_TCR. The priority is set in the PRIOR field of the CAN\_MMRx. Priority 0 is the highest priority, priority 15 is the lowest priority. Thus it is possible to use a part of the message ID to set the PRIOR field. If two mailboxes have the same priority, the message of the mailbox with the lowest number is sent first. Thus if mailbox 0 and mailbox 5 have the same priority and have a message to send at the same time, then the message of the mailbox 0 is sent first.

Setting the MACR bit in the CAN\_MCRx aborts the transmission. Transmission for several mailboxes can be aborted by writing MBx fields in the CAN\_ACR. If the message is being sent when the abort command is set, then the application is notified by the MRDY bit set and not the MABT in the CAN\_MSRx. Otherwise, if the message has not been sent, then the MRDY and the MABT are set in the CAN\_MSR.

When the bus arbitration is lost by a mailbox message, the CAN controller tries to win the next bus arbitration with the same message if this one still has the highest priority. Messages to be sent are re-tried automatically until they win the bus arbitration. This feature can be disabled by setting the bit DRPT in the CAN\_MR. In this case if the message was not sent the first time it was transmitted to the CAN transceiver, it is automatically aborted. The MABT flag is set in the CAN\_MSRx until the next transfer command.

Figure 31-15 shows three MBx message attempts being made (MRDY of MBx set to 0).

The first MBx message is sent, the second is aborted and the last one is trying to be aborted but too late because it has already been transmitted to the CAN transceiver.

## Figure 31-21. Time Triggered Operations

| 31.9.9  | <b>CAN Error</b> | Counter | Register |

|---------|------------------|---------|----------|

| • • . • | ••••••           | ••••••• |          |

| Name:    | CAN_ECR         |               |    |    |    |    |     |

|----------|-----------------|---------------|----|----|----|----|-----|

| Address: | 0x40010020 (0), | 0x40014020 (1 | 1) |    |    |    |     |

| Access:  | Read-only       |               |    |    |    |    |     |

| 31       | 30              | 29            | 28 | 27 | 26 | 25 | 24  |

| -        | -               | _             | —  | -  | -  | -  | TEC |

| 23       | 22              | 21            | 20 | 19 | 18 | 17 | 16  |

|          |                 |               | Т  | EC |    |    |     |

| 15       | 14              | 13            | 12 | 11 | 10 | 9  | 8   |

| _        | _               | _             | _  | -  | -  | _  | -   |

| 7        | 6 5 4 3 2 1 0   |               |    |    |    |    |     |

|          |                 |               | R  | EC |    |    |     |

|          |                 |               |    |    |    |    |     |

## • REC: Receive Error Counter

When a receiver detects an error, REC will be increased by one, except when the detected error is a BIT ERROR while sending an ACTIVE ERROR FLAG or an OVERLOAD FLAG.

When a receiver detects a dominant bit as the first bit after sending an ERROR FLAG, REC is increased by 8.

When a receiver detects a BIT ERROR while sending an ACTIVE ERROR FLAG, REC is increased by 8.

Any node tolerates up to 7 consecutive dominant bits after sending an ACTIVE ERROR FLAG, PASSIVE ERROR FLAG or OVERLOAD FLAG. After detecting the 14th consecutive dominant bit (in case of an ACTIVE ERROR FLAG or an OVER-LOAD FLAG) or after detecting the 8th consecutive dominant bit following a PASSIVE ERROR FLAG, and after each sequence of additional eight consecutive dominant bits, each receiver increases its REC by 8.

After successful reception of a message, REC is decreased by 1 if it was between 1 and 127. If REC was 0, it stays 0, and if it was greater than 127, then it is set to a value between 119 and 127.

## • TEC: Transmit Error Counter

When a transmitter sends an ERROR FLAG, TEC is increased by 8 except when

- the transmitter is error passive and detects an ACKNOWLEDGMENT ERROR because of not detecting a dominant ACK and does not detect a dominant bit while sending its PASSIVE ERROR FLAG.

- the transmitter sends an ERROR FLAG because a STUFF ERROR occurred during arbitration and should have been recessive and has been sent as recessive but monitored as dominant.

When a transmitter detects a BIT ERROR while sending an ACTIVE ERROR FLAG or an OVERLOAD FLAG, the TEC will be increased by 8.

Any node tolerates up to 7 consecutive dominant bits after sending an ACTIVE ERROR FLAG, PASSIVE ERROR FLAG or OVERLOAD FLAG. After detecting the 14th consecutive dominant bit (in case of an ACTIVE ERROR FLAG or an OVER-LOAD FLAG) or after detecting the 8th consecutive dominant bit following a PASSIVE ERROR FLAG, and after each sequence of additional eight consecutive dominant bits every transmitter increases its TEC by 8.

After a successful transmission the TEC is decreased by 1 unless it was already 0.

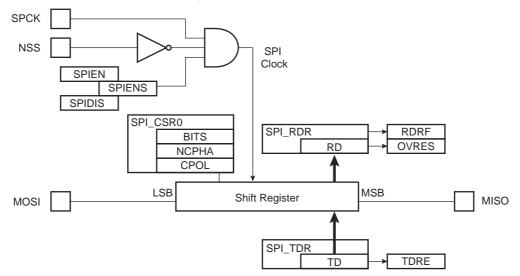

#### 34.7.4 SPI Slave Mode

When operating in Slave mode, the SPI processes data bits on the clock provided on the SPI clock pin (SPCK).

The SPI waits until NSS goes active before receiving the serial clock from an external master. When NSS falls, the clock is validated and the data is loaded in the SPI\_RDR depending on the BITS field configured in SPI\_CSR0. These bits are processed following a phase and a polarity defined respectively by the NCPHA and CPOL bits in SPI\_CSR0. Note that the fileds BITS, CPOL and NCPHA of the other chip select registers (SPI\_CSR1...SPI\_CSR3) have no effect when the SPI is programmed in Slave mode.

The bits are shifted out on the MISO line and sampled on the MOSI line.

Note: For more information on the BITS field, see also the note below the SPI\_CSRx register bitmap (Section 34.8.9 "SPI Chip Select Register").

When all bits are processed, the received data is transferred in the SPI\_RDR and the RDRF bit rises. If the SPI\_RDR has not been read before new data is received, the Overrun Error Status (OVRES) bit in the SPI\_SR is set. As long as this flag is set, data is loaded in the SPI\_RDR. The user must read SPI\_SR to clear the OVRES bit.

When a transfer starts, the data shifted out is the data present in the Shift register. If no data has been written in the SPI\_TDR, the last data received is transferred. If no data has been received since the last reset, all bits are transmitted low, as the Shift register resets to 0.

When a first data is written in the SPI\_TDR, it is transferred immediately in the Shift register and the TDRE flag rises. If new data is written, it remains in the SPI\_TDR until a transfer occurs, i.e., NSS falls and there is a valid clock on the SPCK pin. When the transfer occurs, the last data written in the SPI\_TDR is transferred in the Shift register and the TDRE flag rises. This enables frequent updates of critical variables with single transfers.

Then, new data is loaded in the Shift register from the SPI\_TDR. If no character is ready to be transmitted, i.e., no character has been written in the SPI\_TDR since the last load from the SPI\_TDR to the Shift register, the SPI\_TDR is retransmitted. In this case the Underrun Error Status Flag (UNDES) is set in the SPI\_SR.

Figure 34-13 shows a block diagram of the SPI when operating in Slave mode.

#### Figure 34-13. Slave Mode Functional Block Diagram

# 34.7.5 Register Write Protection

To prevent any single software error from corrupting SPI behavior, certain registers in the address space can be write-protected by setting the WPEN bit in the SPI Write Protection Mode Register (SPI\_WPMR).

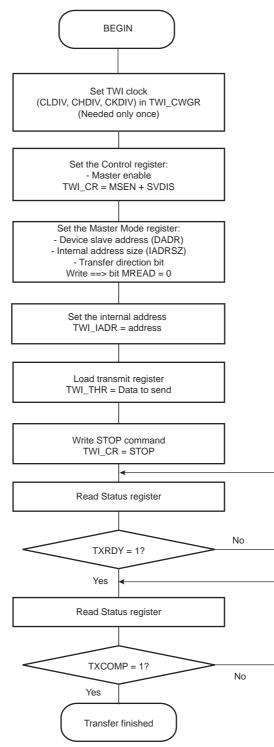

Figure 35-15. TWI Write Operation with Single Data Byte and Internal Address

Atmel

Atmel

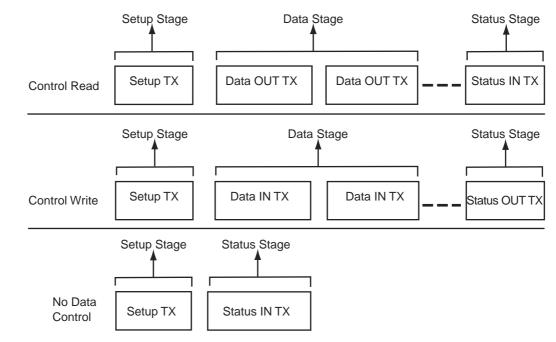

## 41.6.1.3 USB Transfer Event Definitions

As indicated below, transfers are sequential events carried out on the USB bus.

| Transfer                 |                                |                                                                                           |  |  |  |

|--------------------------|--------------------------------|-------------------------------------------------------------------------------------------|--|--|--|

| Direction                | Туре                           | Transaction                                                                               |  |  |  |

|                          |                                | Setup transaction $\rightarrow$ Data IN transactions $\rightarrow$ Status OUT transaction |  |  |  |

| CONTROL (bidirectional)  | Control <sup>(1)(3)</sup>      | Setup transaction $\rightarrow$ Data OUT transactions $\rightarrow$ Status IN transaction |  |  |  |

|                          |                                | Setup transaction $\rightarrow$ Status IN transaction                                     |  |  |  |

|                          | Interrupt IN                   |                                                                                           |  |  |  |

| IN (device toward host)  | Isochronous IN <sup>(2)</sup>  | Data IN transaction $\rightarrow$ Data IN transaction                                     |  |  |  |

|                          | Bulk IN                        |                                                                                           |  |  |  |

|                          | Interrupt OUT                  |                                                                                           |  |  |  |

| OUT (host toward device) | Isochronous OUT <sup>(2)</sup> | Data OUT transaction $\rightarrow$ Data OUT transaction                                   |  |  |  |

|                          | Bulk OUT                       |                                                                                           |  |  |  |

#### Table 41-5. USB Transfer Events

Notes: 1. Control transfer must use endpoints with no ping-pong attributes.

2. Isochronous transfers must use endpoints with ping-pong attributes.

3. Control transfers can be aborted using a stall handshake.

A status transaction is a special type of host-to-device transaction used only in a control transfer. The control transfer must be performed using endpoints with no ping-pong attributes. According to the control sequence (read or write), the USB device sends or receives a status transaction.

#### Figure 41-4. Control Read and Write Sequences

Notes: 1. During the Status IN stage, the host waits for a zero length packet (Data IN transaction with no data) from the device using DATA1 PID. Refer to Chapter 8 of the *Universal Serial Bus Specification, Rev. 2.0,* for more information on the protocol layer.

# Atmel

## 46.7.6.2 Conditions @ 25°C with Gain = 4

- $f_{ADC} = 20 \text{ MHz}$

- f<sub>S</sub> = 1 MHz, ADC Sampling Frequency in Free Run Mode

- V<sub>ADVREF</sub>= 3V

- Signal Amplitude: V<sub>ADVREF</sub>/2, Signal Frequency < 100 Hz

- OSR: Number of Averaged Samples

| Parameter Averaging<br>Resolution<br>RES (AFEC_EMR) | Over<br>Sampling<br>Ratio | Mode<br>(bits) | INL<br>(LSB) | DNL<br>(LSB) | SNR<br>(dB) | THD<br>(dB) | ENOB<br>(bits) | FS<br>(ksps) |

|-----------------------------------------------------|---------------------------|----------------|--------------|--------------|-------------|-------------|----------------|--------------|

| Single-ended Mode                                   |                           |                |              |              |             |             |                |              |

| RES = 0                                             | 1                         | 12             | ±1           | ±0.5         | 59          | -81         | 9.5            | 1000         |

| RES = 2                                             | 4                         | 13             | +1.7 / -1.3  | +1.6 / -1    | 63.1        | -82.9       | 10.2           | 250          |

| RES = 3                                             | 16                        | 14             | +1.7 / -2.5  | +2 / -1      | 67          | -83.6       | 10.8           | 62.5         |

| RES = 4                                             | 64                        | 15             | ±8           | _            | 70.3        | -84.5       | 11.4           | 15.6         |

| RES = 5                                             | 256                       | 16             | ±12          | _            | 74.8        | -85.1       | 12.1           | 3.9          |

| Differential Mode                                   |                           |                |              |              |             |             |                |              |

| RES = 0                                             | 1                         | 12             | ±1           | ±0.5         | 62          | -84.5       | 10             | 1000         |

| RES = 2                                             | 4                         | 13             | ±1           | ±1           | 67.7        | -85.7       | 10.9           | 25           |

| RES = 3                                             | 16                        | 14             | +4.1 / -1.6  | +3.4 / -1    | 73.6        | -86.8       | 11.9           | 6.25         |

| RES = 4                                             | 64                        | 15             | ±3.5         | _            | 78.7        | -86.8       | 12.7           | 1.56         |

| RES = 5                                             | 256                       | 16             | ±7.5         | _            | 82.1        | -86.8       | 13.1           | 0.39         |