Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                               |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 150MHz                                                                               |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, SD, SPI, UART/USART, USB, USB OTG |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                            |

| Number of I/O              | 100                                                                                  |

| Program Memory Size        | 512KB (512K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | 16K x 8                                                                              |

| RAM Size                   | 128K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                         |

| Data Converters            | A/D 58x16b; D/A 2x12b                                                                |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 144-LQFP                                                                             |

| Supplier Device Package    | 144-LQFP (20x20)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mk60fx512vlq15               |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Communication interfaces

- Ethernet controller with MII and RMII interface to external PHY and hardware IEEE 1588 capability

- USB high-/full-/low-speed On-the-Go controller with ULPI interface

- USB full-/low-speed On-the-Go controller with on-chip transceiver

- Two Controller Area Network (CAN) modules

- Three SPI modules

- Two I2C modules

- Six UART modules

- Secure Digital host controller (SDHC)

- Two I2S modules

# 3.4.1 Example

This is an example of an operating rating:

| Symbol          | Description                  | Min. | Max. | Unit |

|-----------------|------------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | -0.3 | 1.2  | V    |

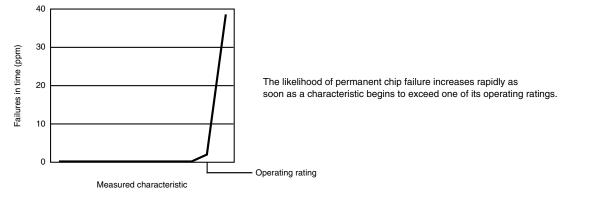

# 3.5 Result of exceeding a rating

# 3.6 Relationship between ratings and operating requirements

# 5 General

# 5.1 AC electrical characteristics

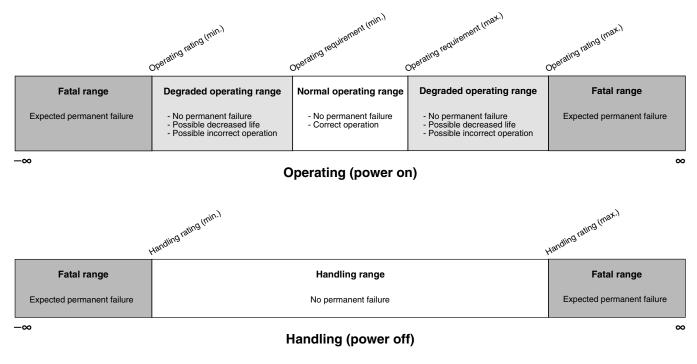

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL} + (V_{IH} - V_{IL})/2$ .

### Figure 1. Input signal measurement reference

All digital I/O switching characteristics assume:

- 1. output pins

- have  $C_L=30$  pF loads,

- are configured for fast slew rate (PORTx\_PCRn[SRE]=0), and

- are configured for high drive strength (PORTx\_PCRn[DSE]=1)

- 2. input pins

- have their passive filter disabled (PORTx\_PCRn[PFE]=0)

# 5.2 Nonswitching electrical specifications

## 5.2.1 Voltage and current operating requirements

Table 1. Voltage and current operating requirements

| Symbol             | Description                                               | Min. | Max. | Unit | Notes |

|--------------------|-----------------------------------------------------------|------|------|------|-------|

| V <sub>DD</sub>    | Supply voltage                                            | 2.0  | 3.6  | V    |       |

| V <sub>DDA</sub>   | Analog supply voltage                                     | 1.71 | 3.6  | V    |       |

| $V_{DD} - V_{DDA}$ | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage | -0.1 | 0.1  | V    |       |

| $V_{SS} - V_{SSA}$ | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage | -0.1 | 0.1  | V    |       |

| V <sub>BAT</sub>   | RTC battery supply voltage                                | 1.71 | 3.6  | V    |       |

Table continues on the next page ...

| Symbol              | Description                                                                                                                                                        | Min.                  | Max.                 | Unit | Notes |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|------|-------|

| V <sub>IH</sub>     | Input high voltage (digital pins)                                                                                                                                  |                       |                      |      |       |

|                     | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$                                                                                                       | $0.7 \times V_{DD}$   | _                    | V    |       |

|                     | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                                                       | $0.75 \times V_{DD}$  | _                    | V    |       |

| V <sub>IL</sub>     | Input low voltage (digital pins)                                                                                                                                   |                       |                      |      |       |

|                     | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$                                                                                                       | _                     | $0.35 \times V_{DD}$ | V    |       |

|                     | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                                                       | _                     | $0.3 \times V_{DD}$  | V    |       |

| V <sub>HYS</sub>    | Input hysteresis (digital pins)                                                                                                                                    | $0.06 \times V_{DD}$  | _                    | V    |       |

| I <sub>ICDIO</sub>  | Digital pin negative DC injection current — single pin<br>• V <sub>IN</sub> < V <sub>SS</sub> -0.3V                                                                | -5                    |                      | mA   | 1     |

| I <sub>ICAIO</sub>  | Analog <sup>2</sup> , EXTAL0/XTAL0, and EXTAL1/XTAL1 pin DC injection current — single pin                                                                         |                       |                      | mA   | 3     |

|                     | <ul> <li>V<sub>IN</sub> &lt; V<sub>SS</sub>-0.3V (Negative current injection)</li> </ul>                                                                           | -5                    | _                    |      |       |

|                     | • V <sub>IN</sub> > V <sub>DD</sub> +0.3V (Positive current injection)                                                                                             | _                     | +5                   |      |       |

| I <sub>ICcont</sub> | Contiguous pin DC injection current —regional limit,<br>includes sum of negative injection currents or sum of<br>positive injection currents of 16 contiguous pins |                       |                      |      |       |

|                     | Negative current injection                                                                                                                                         | -25                   | —                    | mA   |       |

|                     | Positive current injection                                                                                                                                         | _                     | +25                  |      |       |

| V <sub>RAM</sub>    | V <sub>DD</sub> voltage required to retain RAM                                                                                                                     | 1.2                   | —                    | V    |       |

| V <sub>RFVBAT</sub> | V <sub>BAT</sub> voltage required to retain the VBAT register file                                                                                                 | V <sub>POR_VBAT</sub> | —                    | V    |       |

Table 1. Voltage and current operating requirements (continued)

- All 5 V tolerant digital I/O pins are internally clamped to V<sub>SS</sub> through a ESD protection diode. There is no diode connection to V<sub>DD</sub>. If V<sub>IN</sub> greater than V<sub>DIO\_MIN</sub> (=V<sub>SS</sub>-0.3V) is observed, then there is no need to provide current limiting resistors at the pads. If this limit cannot be observed then a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>DIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>IC</sub>I.

- 2. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

- 3. All analog pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub> through ESD protection diodes. If V<sub>IN</sub> is greater than V<sub>AIO\_MIN</sub> (=V<sub>SS</sub>-0.3V) and V<sub>IN</sub> is less than V<sub>AIO\_MAX</sub>(=V<sub>DD</sub>+0.3V) is observed, then there is no need to provide current limiting resistors at the pads. If these limits cannot be observed then a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>AIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>IC</sub>I. The positive injection current limiting resistor is calculated as R=(V<sub>IN</sub>-V<sub>AIO\_MAX</sub>)/II<sub>IC</sub>I. Select the larger of these two calculated resistances.

## 5.2.2 LVD and POR operating requirements Table 2. LVD and POR operating requirements

| Symbol            | Description                                                 | Min. | Тур. | Max. | Unit | Notes |

|-------------------|-------------------------------------------------------------|------|------|------|------|-------|

| V <sub>POR</sub>  | Falling VDD POR detect voltage                              | 0.8  | 1.1  | 1.5  | V    |       |

| V <sub>LVDH</sub> | Falling low-voltage detect threshold — high range (LVDV=01) | 2.48 | 2.56 | 2.64 | V    |       |

Table continues on the next page ...

# 5.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

## 5.2.8 Capacitance attributes

Table 8. Capacitance attributes

| Symbol                 | Description                          | Min. | Max. | Unit |

|------------------------|--------------------------------------|------|------|------|

| C <sub>IN_A</sub>      | Input capacitance: analog pins       | —    | 7    | pF   |

| C <sub>IN_D</sub>      | Input capacitance: digital pins      |      | 7    | pF   |

| C <sub>IN_D_io60</sub> | Input capacitance: fast digital pins | _    | 9    | pF   |

# 5.3 Switching specifications

# 5.3.1 Device clock specifications

### Table 9. Device clock specifications

| Symbol                 | Description                                            | Min. | Max. | Unit | Notes |

|------------------------|--------------------------------------------------------|------|------|------|-------|

|                        | Normal run mode                                        | e    |      | •    |       |

| f <sub>SYS</sub>       | System and core clock                                  | _    | 150  | MHz  |       |

| f <sub>SYS_USBFS</sub> | System and core clock when Full Speed USB in operation | 20   | -    | MHz  |       |

| f <sub>SYS_USBHS</sub> | System and core clock when High Speed USB in operation | 60   | -    | MHz  |       |

| f <sub>ENET</sub>      | System and core clock when ethernet in operation       |      |      | MHz  |       |

|                        | • 10 Mbps                                              | 5    | _    |      |       |

|                        | • 100 Mbps                                             | 50   | _    |      |       |

| f <sub>BUS</sub>       | Bus clock                                              | —    | 75   | MHz  |       |

| FB_CLK                 | FlexBus clock                                          | _    | 50   | MHz  |       |

| f <sub>FLASH</sub>     | Flash clock                                            | —    | 25   | MHz  |       |

| f <sub>LPTMR</sub>     | LPTMR clock                                            | —    | 25   | MHz  |       |

|                        | VLPR mode <sup>1</sup>                                 |      |      | •    |       |

| f <sub>SYS</sub>       | System and core clock                                  |      | 4    | MHz  |       |

Table continues on the next page ...

| Symbol             | Description   | Min. | Max. | Unit | Notes |

|--------------------|---------------|------|------|------|-------|

| f <sub>BUS</sub>   | Bus clock     | —    | 4    | MHz  |       |

| FB_CLK             | FlexBus clock | —    | 4    | MHz  |       |

| f <sub>FLASH</sub> | Flash clock   | —    | 0.5  | MHz  |       |

| f <sub>LPTMR</sub> | LPTMR clock   | —    | 4    | MHz  |       |

Table 9. Device clock specifications (continued)

1. The frequency limitations in VLPR mode here override any frequency specification listed in the timing specification for any other module.

# 5.3.2 General switching specifications

These general purpose specifications apply to all signals configured for GPIO, UART, CAN, CMT, IEEE 1588 timer, and I<sup>2</sup>C signals.

| Symbol | Description                                                                                                 | Min. | Max. | Unit                | Notes |

|--------|-------------------------------------------------------------------------------------------------------------|------|------|---------------------|-------|

|        | GPIO pin interrupt pulse width (digital glitch filter disabled) — Synchronous path                          | 1.5  | -    | Bus clock<br>cycles | 1, 2  |

|        | GPIO pin interrupt pulse width (digital glitch filter disabled, analog filter enabled) — Asynchronous path  | 100  | -    | ns                  | 3     |

|        | GPIO pin interrupt pulse width (digital glitch filter disabled, analog filter disabled) — Asynchronous path | 16   | -    | ns                  | 3     |

|        | External reset pulse width (digital glitch filter disabled)                                                 | 100  | _    | ns                  | 3     |

|        | Mode select (EZP_CS) hold time after reset deassertion                                                      | 2    | -    | Bus clock<br>cycles |       |

|        | Port rise and fall time (high drive strength)                                                               |      |      |                     | 4     |

|        | Slew disabled                                                                                               |      |      |                     |       |

|        | • $1.71 \le V_{DD} \le 2.7V$                                                                                | —    | 14   | ns                  |       |

|        | • $2.7 \le V_{DD} \le 3.6V$                                                                                 | —    | 8    | ns                  |       |

|        | Slew enabled                                                                                                |      |      |                     |       |

|        | • $1.71 \le V_{DD} \le 2.7V$                                                                                | —    | 36   | ns                  |       |

|        | • $2.7 \le V_{DD} \le 3.6V$                                                                                 | —    | 24   | ns                  |       |

|        | Port rise and fall time (low drive strength)                                                                |      |      |                     | 5     |

|        | Slew disabled                                                                                               |      |      |                     |       |

|        | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                                                                             | —    | 14   | ns                  |       |

|        | • $2.7 \le V_{DD} \le 3.6V$                                                                                 | —    | 8    | ns                  |       |

|        | Slew enabled                                                                                                |      |      |                     |       |

|        | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                                                                             | —    | 36   | ns                  |       |

|        | • $2.7 \le V_{DD} \le 3.6V$                                                                                 | —    | 24   | ns                  |       |

Table 10. General switching specifications

Table continues on the next page...

# 6.3.1 MCG specifications

| Symbol                   | Description                                                                                                          |                                                        | Min.                            | Тур.   | Max.              | Unit              | Notes |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------|--------|-------------------|-------------------|-------|

| f <sub>ints_ft</sub>     |                                                                                                                      | frequency (slow clock) —<br>nominal VDD and 25 °C      | —                               | 32.768 | —                 | kHz               |       |

| $f_{ints_t}$             | Internal reference                                                                                                   | frequency (slow clock) — user                          | 31.25                           | _      | 39.0625           | kHz               |       |

| $\Delta_{fdco\_res\_t}$  | Resolution of trimmed average DCO output<br>frequency at fixed voltage and temperature —<br>using SCTRIM and SCFTRIM |                                                        | _                               | ± 0.3  | ± 0.6             | %f <sub>dco</sub> | 1     |

| $\Delta f_{dco\_res\_t}$ | Resolution of trimmed average DCO output<br>frequency at fixed voltage and temperature —<br>using SCTRIM only        |                                                        | _                               | ± 0.2  | ± 0.5             | %f <sub>dco</sub> | 1     |

| $\Delta f_{dco_t}$       | Total deviation of trimmed average DCO output frequency over voltage and temperature                                 |                                                        | —                               | ± 7    | —                 | %f <sub>dco</sub> | 1     |

| $\Delta f_{dco_t}$       | Total deviation of t<br>frequency over fixe<br>range of 0–70°C                                                       | _                                                      | ± 4.5                           | —      | %f <sub>dco</sub> | 1                 |       |

| f <sub>intf_ft</sub>     |                                                                                                                      | frequency (fast clock) —<br>nominal VDD and 25°C       |                                 |        | 4                 | MHz               |       |

| f <sub>intf_t</sub>      | Internal reference frequency (fast clock) — user trimmed at nominal VDD and 25 °C                                    |                                                        | 3                               | _      | 5                 | MHz               |       |

| $f_{loc\_low}$           | Loss of external clock minimum frequency — RANGE = 00                                                                |                                                        | (3/5) x<br>f <sub>ints_t</sub>  |        | —                 | kHz               |       |

| f <sub>loc_high</sub>    | Loss of external clock minimum frequency —<br>RANGE = 01, 10, or 11                                                  |                                                        | (16/5) x<br>f <sub>ints_t</sub> | _      | —                 | kHz               |       |

|                          | 1                                                                                                                    | F                                                      | ĹL                              | L      |                   |                   |       |

| f <sub>fll_ref</sub>     | FLL reference freq                                                                                                   | uency range                                            | 31.25                           | —      | 39.0625           | kHz               |       |

| f <sub>dco</sub>         | DCO output<br>frequency range                                                                                        | Low range (DRS=00)<br>640 × f <sub>fll_ref</sub>       | 20                              | 20.97  | 25                | MHz               | 2, 3  |

|                          |                                                                                                                      | Mid range (DRS=01)<br>1280 × f <sub>fll_ref</sub>      | 40                              | 41.94  | 50                | MHz               | -     |

|                          |                                                                                                                      | Mid-high range (DRS=10)<br>1920 × f <sub>fll_ref</sub> | 60                              | 62.91  | 75                | MHz               | -     |

|                          |                                                                                                                      | High range (DRS=11)<br>2560 × f <sub>fll_ref</sub>     | 80                              | 83.89  | 100               | MHz               | -     |

| dco_t_DMX32              | DCO output<br>frequency                                                                                              | Low range (DRS=00)<br>732 × f <sub>fll ref</sub>       | -                               | 23.99  | -                 | MHz               | 4, 5  |

|                          |                                                                                                                      | Mid range (DRS=01)<br>1464 × f <sub>fll ref</sub>      | -                               | 47.97  | -                 | MHz               |       |

|                          |                                                                                                                      | Mid-high range (DRS=10)<br>2197 × f <sub>fll_ref</sub> | -                               | 71.99  | -                 | MHz               |       |

|                          |                                                                                                                      | High range (DRS=11)<br>2929 × f <sub>fll_ref</sub>     | -                               | 95.98  | -                 | MHz               |       |

### Table 15. MCG specifications

Table continues on the next page...

| Symbol                   | Description                                                                                                                                          | Min. | Тур. | Max.                                                        | Unit | Notes |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------------------------------------------------------------|------|-------|

| J <sub>cyc_fll</sub>     | FLL period jitter                                                                                                                                    |      | 180  | _                                                           | ps   |       |

|                          | <ul> <li>f<sub>VCO</sub> = 48 MHz</li> <li>f<sub>VCO</sub> = 98 MHz</li> </ul>                                                                       | _    | 150  | _                                                           |      |       |

| t <sub>fll_acquire</sub> | FLL target frequency acquisition time                                                                                                                |      |      | 1                                                           | ms   | 6     |

|                          | PLL                                                                                                                                                  | .0,1 |      |                                                             |      |       |

| f <sub>pll_ref</sub>     | PLL reference frequency range                                                                                                                        | 8    | —    | 16                                                          | MHz  |       |

| f <sub>vcoclk_2x</sub>   | VCO output frequency                                                                                                                                 | 180  |      | 360                                                         | MHz  |       |

| f <sub>vcoclk</sub>      | PLL output frequency                                                                                                                                 | 90   |      | 180                                                         | MHz  |       |

| f <sub>vcoclk_90</sub>   | PLL quadrature output frequency                                                                                                                      | 90   |      | 180                                                         | MHz  |       |

| I <sub>pll</sub>         | PLL0 operating current<br>• VCO @ 180 MHz (f <sub>osc_hi_1</sub> = 32 MHz, f <sub>pll_ref</sub><br>= 8 MHz, VDIV multiplier = 22)                    | _    | 2.8  | —                                                           | mA   | 7     |

| I <sub>pll</sub>         | PLL0 operating current<br>• VCO @ 360 MHz (f <sub>osc_hi_1</sub> = 32 MHz, f <sub>pll_ref</sub><br>= 8 MHz, VDIV multiplier = 45)                    | _    | 4.7  | —                                                           | mA   | 7     |

| I <sub>pll</sub>         | <ul> <li>PLL1 operating current</li> <li>VCO @ 180 MHz (f<sub>osc_hi_1</sub> = 32 MHz, f<sub>pll_ref</sub> = 8 MHz, VDIV multiplier = 22)</li> </ul> | _    | 2.3  | —                                                           | mA   | 7     |

| I <sub>pll</sub>         | <ul> <li>PLL1 operating current</li> <li>VCO @ 360 MHz (f<sub>osc_hi_1</sub> = 32 MHz, f<sub>pll_ref</sub> = 8 MHz, VDIV multiplier = 45)</li> </ul> | _    | 3.6  | —                                                           | mA   | 7     |

| t <sub>pll_lock</sub>    | Lock detector detection time                                                                                                                         | _    | _    | $100 \times 10^{-6}$<br>+ 1075(1/<br>f <sub>pll_ref</sub> ) | S    | 8     |

| J <sub>cyc_pll</sub>     | PLL period jitter (RMS)                                                                                                                              |      |      |                                                             |      | 9     |

|                          | • f <sub>vco</sub> = 180 MHz                                                                                                                         | _    | 100  | _                                                           | ps   |       |

|                          | • f <sub>vco</sub> = 360 MHz                                                                                                                         | —    | 75   | _                                                           | ps   |       |

| J <sub>acc_pll</sub>     | PLL accumulated jitter over 1µs (RMS)                                                                                                                |      |      |                                                             |      | 10    |

|                          | • f <sub>vco</sub> = 180 MHz                                                                                                                         | _    | 600  | _                                                           | ps   |       |

|                          | • f <sub>vco</sub> = 360 MHz                                                                                                                         | _    | 300  | _                                                           | ps   |       |

1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

2. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

The resulting system clock frequencies should not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco t</sub>) over voltage and temperature should be considered.

- 4. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

- 5. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

7. Excludes any oscillator currents that are also consuming power while PLL is in operation.

This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

| Symbol                       | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

| R <sub>S</sub>               | Series resistor — low-frequency, low-power mode (HGO=0)                                                | _    | _               | _    | kΩ   |       |

|                              | Series resistor — low-frequency, high-gain mode (HGO=1)                                                | —    | 200             |      | kΩ   |       |

|                              | Series resistor — high-frequency, low-power mode (HGO=0)                                               | —    | _               | _    | kΩ   |       |

|                              | Series resistor — high-frequency, high-gain<br>mode (HGO=1)                                            |      |                 |      |      |       |

|                              |                                                                                                        | —    | 0               | _    | kΩ   |       |

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, low-power mode<br>(HGO=0)  | —    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  | _    | V <sub>DD</sub> | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) |      | V <sub>DD</sub> | —    | V    |       |

#### Table 16. Oscillator DC electrical specifications (continued)

- 1. V<sub>DD</sub>=3.3 V, Temperature =25 °C

- 2. See crystal or resonator manufacturer's recommendation

- 3.  $C_x, C_y$  can be provided by using either the integrated capacitors or by using external components.

- 4. When low power mode is selected, R<sub>F</sub> is integrated and must not be attached externally.

- 5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other devices.

# 6.3.2.2 Oscillator frequency specifications

## Table 17. Oscillator frequency specifications

| Symbol                | Description                                                                                           | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low frequency mode (MCG_C2[RANGE]=00)                     | 32   | _    | 40   | kHz  |       |

| f <sub>osc_hi_1</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (low range)<br>(MCG_C2[RANGE]=01)  | 3    | _    | 8    | MHz  | 1     |

| f <sub>osc_hi_2</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (high range)<br>(MCG_C2[RANGE]=1x) | 8    | _    | 32   | MHz  |       |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                           | _    | —    | 60   | MHz  | 2, 3  |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                          | 40   | 50   | 60   | %    |       |

Table continues on the next page...

| Symbol           | Description                                                                                  | Min. | Тур. | Max. | Unit | Notes |

|------------------|----------------------------------------------------------------------------------------------|------|------|------|------|-------|

| t <sub>cst</sub> | Crystal startup time — 32 kHz low-frequency, low-power mode (HGO=0)                          | _    | 1000 | _    | ms   | 4, 5  |

|                  | Crystal startup time — 32 kHz low-frequency,<br>high-gain mode (HGO=1)                       | _    | 500  |      | ms   |       |

|                  | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), low-power mode<br>(HGO=0) | _    | 0.6  | _    | ms   |       |

|                  | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), high-gain mode<br>(HGO=1) | _    | 1    | _    | ms   |       |

Table 17. Oscillator frequency specifications (continued)

- 1. Frequencies less than 8 MHz are not in the PLL range.

- 2. Other frequency limits may apply when external clock is being used as a reference for the FLL or PLL.

- 3. When transitioning from FBE to FEI mode, restrict the frequency of the input clock so that, when it is divided by FRDIV, it remains within the limits of the DCO input clock frequency.

- 4. Proper PC board layout procedures must be followed to achieve specifications.

- 5. Crystal startup time is defined as the time between the oscillator being enabled and the OSCINIT bit in the MCG\_S register being set.

## NOTE

The 32 kHz oscillator works in low power mode bu default and cannot be moved into high power/gain mode.

## 6.3.3 32 kHz Oscillator Electrical Characteristics

This section describes the module electrical characteristics.

### 6.3.3.1 32 kHz oscillator DC electrical specifications Table 18. 32kHz oscillator DC electrical specifications

| Symbol                       | Description                                   | Min. | Тур. | Max. | Unit |

|------------------------------|-----------------------------------------------|------|------|------|------|

| V <sub>BAT</sub>             | Supply voltage                                | 1.71 | —    | 3.6  | V    |

| R <sub>F</sub>               | Internal feedback resistor                    |      | 100  | _    | MΩ   |

| C <sub>para</sub>            | Parasitical capacitance of EXTAL32 and XTAL32 | —    | 5    | 7    | pF   |

| V <sub>pp</sub> <sup>1</sup> | Peak-to-peak amplitude of oscillation         | _    | 0.6  | —    | V    |

1. When a crystal is being used with the 32 kHz oscillator, the EXTAL32 and XTAL32 pins should only be connected to required oscillator components and must not be connected to any other devices.

| Symbol                   | Description                                            | Min. | Тур. | Max. | Unit | Notes |

|--------------------------|--------------------------------------------------------|------|------|------|------|-------|

|                          | 16-bit write to FlexRAM execution time:                |      |      |      |      |       |

| t <sub>eewr16b64k</sub>  | 64 KB EEPROM backup                                    | -    | 400  | 1700 | μs   |       |

| t <sub>eewr16b128k</sub> | 128 KB EEPROM backup                                   | -    | 450  | 1800 | μs   |       |

| t <sub>eewr16b256k</sub> | • 256 KB EEPROM backup                                 | _    | 525  | 2000 | μs   |       |

| t <sub>eewr32bers</sub>  | 32-bit write to erased FlexRAM location execution time | —    | 180  | 275  | μs   |       |

|                          | 32-bit write to FlexRAM execution time:                |      |      |      |      |       |

| t <sub>eewr32b64k</sub>  | 64 KB EEPROM backup                                    | -    | 475  | 1850 | μs   |       |

| t <sub>eewr32b128k</sub> | 128 KB EEPROM backup                                   | _    | 525  | 2000 | μs   |       |

| t <sub>eewr32b256k</sub> | • 256 KB EEPROM backup                                 | _    | 600  | 2200 | μs   |       |

#### Table 21. Flash command timing specifications (continued)

1. Assumes 25MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

3. For byte-writes to an erased FlexRAM location, the aligned word containing the byte must be erased.

## 6.4.1.3 Flash high voltage current behaviors Table 22. Flash high voltage current behaviors

| Symbol              | Description                                                                       | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | Average current<br>adder during high<br>voltage flash<br>programming<br>operation | _    | 3.5  | 7.5  | mA   |

| I <sub>DD_ERS</sub> | Average current<br>adder during high<br>voltage flash erase<br>operation          | _    | 1.5  | 4.0  | mA   |

## 6.4.1.4 Reliability specifications Table 23. NVM reliability specifications

| Symbol                  | Description                            | Min.    | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|-------------------------|----------------------------------------|---------|-------------------|------|--------|-------|

|                         | Progra                                 | m Flash |                   |      |        |       |

| t <sub>nvmretp10k</sub> | Data retention after up to 10 K cycles | 5       | 50                | _    | years  |       |

| t <sub>nvmretp1k</sub>  | Data retention after up to 1 K cycles  | 20      | 100               | —    | years  |       |

| n <sub>nvmcycp</sub>    | Cycling endurance                      | 10 K    | 50 K              | —    | cycles | 2     |

|                         | Data                                   | Flash   |                   |      |        |       |

| t <sub>nvmretd10k</sub> | Data retention after up to 10 K cycles | 5       | 50                | —    | years  |       |

| t <sub>nvmretd1k</sub>  | Data retention after up to 1 K cycles  | 20      | 100               | —    | years  |       |

Table continues on the next page...

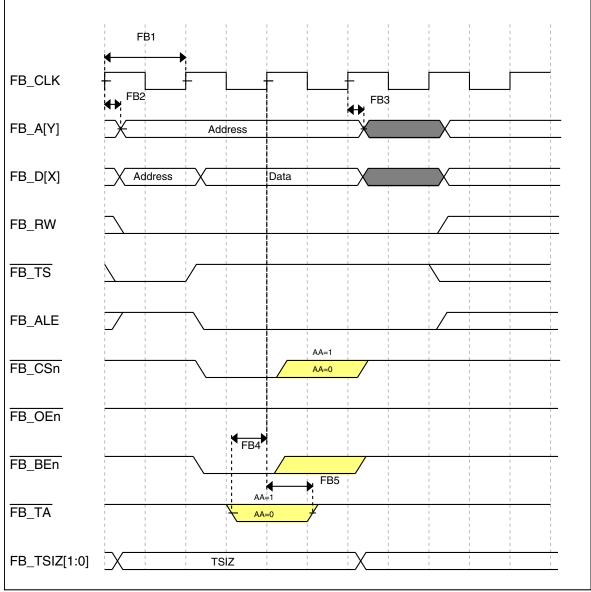

Peripheral operating requirements and behaviors

Figure 18. FlexBus write timing diagram

# 6.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

# 6.6 Analog

| Symbol | Description                                 | Conditions            | Min.     | Typ. <sup>1</sup> | Max. | Unit     | Notes                                                                    |

|--------|---------------------------------------------|-----------------------|----------|-------------------|------|----------|--------------------------------------------------------------------------|

| THD    | Total harmonic<br>distortion                | • Gain=1<br>• Gain=64 | 85<br>49 | 100<br>95         |      | dB<br>dB | 16-bit<br>differential<br>mode,<br>Average=32,<br>f <sub>in</sub> =100Hz |

| SFDR   | Spurious free<br>dynamic range              | • Gain=1<br>• Gain=64 | 85<br>53 | 105<br>88         |      | dB<br>dB | 16-bit<br>differential<br>mode,<br>Average=32,<br>f <sub>in</sub> =100Hz |

| ENOB   | Effective number                            | • Gain=1, Average=4   | 11.6     | 13.4              | —    | bits     | 16-bit                                                                   |

|        | of bits                                     | • Gain=1, Average=8   | 8.0      | 13.6              | _    | bits     | differential<br>mode,f <sub>in</sub> =100Hz                              |

|        |                                             | • Gain=64, Average=4  | 7.2      | 9.6               | _    | bits     | 110000,1 <sub>IN</sub> =100112                                           |

|        |                                             | Gain=64, Average=8    | 6.3      | 9.6               | _    | bits     |                                                                          |

|        |                                             | • Gain=1, Average=32  | 12.8     | 14.5              | _    | bits     |                                                                          |

|        |                                             | • Gain=2, Average=32  | 11.0     | 14.3              | _    | bits     |                                                                          |

|        |                                             | • Gain=4, Average=32  | 7.9      | 13.8              | _    | bits     |                                                                          |

|        |                                             | • Gain=8, Average=32  | 7.3      | 13.1              | _    | bits     |                                                                          |

|        |                                             | • Gain=16, Average=32 | 6.8      | 12.5              | _    | bits     |                                                                          |

|        |                                             | • Gain=32, Average=32 | 6.8      | 11.5              | _    | bits     |                                                                          |

|        |                                             | • Gain=64, Average=32 | 7.5      | 10.6              | _    | bits     |                                                                          |

| SINAD  | Signal-to-noise<br>plus distortion<br>ratio | See ENOB              | 6.02     | × ENOB +          | 1.76 | dB       |                                                                          |

#### Table 31. 16-bit ADC with PGA characteristics (continued)

1. Typical values assume  $V_{DDA}$  =3.0V, Temp=25°C, f<sub>ADCK</sub>=6MHz unless otherwise stated.

- 2. This current is a PGA module adder, in addition to ADC conversion currents.

- Between IN+ and IN-. The PGA draws a DC current from the input terminals. The magnitude of the DC current is a strong function of input common mode voltage (V<sub>CM</sub>) and the PGA gain.

- 4. Gain =  $2^{PGAG}$

- 5. After changing the PGA gain setting, a minimum of 2 ADC+PGA conversions should be ignored.

- 6. Limit the input signal swing so that the PGA does not saturate during operation. Input signal swing is dependent on the PGA reference voltage and gain setting.

# 6.6.2 CMP and 6-bit DAC electrical specifications

Table 32.

Comparator and 6-bit DAC electrical specifications

| Symbol            | Description                                     | Min.                  | Тур. | Max.            | Unit |

|-------------------|-------------------------------------------------|-----------------------|------|-----------------|------|

| V <sub>DD</sub>   | Supply voltage                                  | 1.71                  | —    | 3.6             | V    |

| I <sub>DDHS</sub> | Supply current, High-speed mode (EN=1, PMODE=1) | _                     | —    | 200             | μA   |

| I <sub>DDLS</sub> | Supply current, low-speed mode (EN=1, PMODE=0)  | _                     | —    | 20              | μA   |

| V <sub>AIN</sub>  | Analog input voltage                            | V <sub>SS</sub> – 0.3 | —    | V <sub>DD</sub> | V    |

| V <sub>AIO</sub>  | Analog input offset voltage                     | _                     | —    | 20              | mV   |

Table continues on the next page...

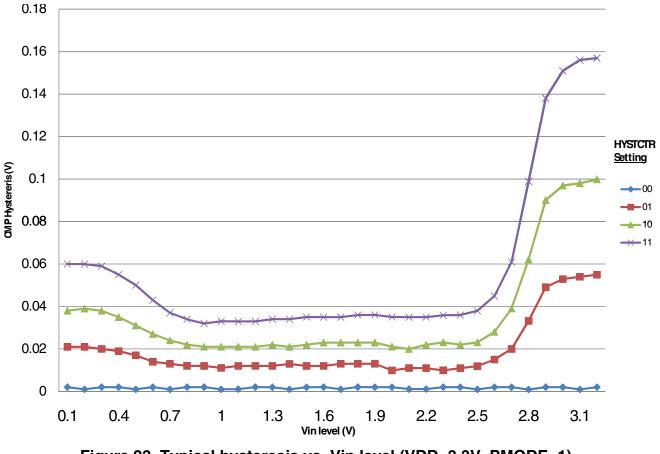

Peripheral operating requirements and behaviors

Figure 23. Typical hysteresis vs. Vin level (VDD=3.3V, PMODE=1)

# 6.6.3 12-bit DAC electrical characteristics

## 6.6.3.1 12-bit DAC operating requirements Table 33. 12-bit DAC operating requirements

| Symbol            | Desciption              | Min.                                      | Max. | Unit | Notes |

|-------------------|-------------------------|-------------------------------------------|------|------|-------|

| V <sub>DDA</sub>  | Supply voltage          | 1.71                                      | 3.6  | V    |       |

| V <sub>DACR</sub> | Reference voltage       | 1.13 3.6                                  |      | V    | 1     |

| T <sub>A</sub>    | Temperature             | Operating temperature range of the device |      | °C   |       |

| CL                | Output load capacitance | — 100                                     |      | pF   | 2     |

| ١L                | Output load current     |                                           | 1    | mA   |       |

1. The DAC reference can be selected to be  $V_{DDA}$  or the voltage output of the VREF module (VREF\_OUT)

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC

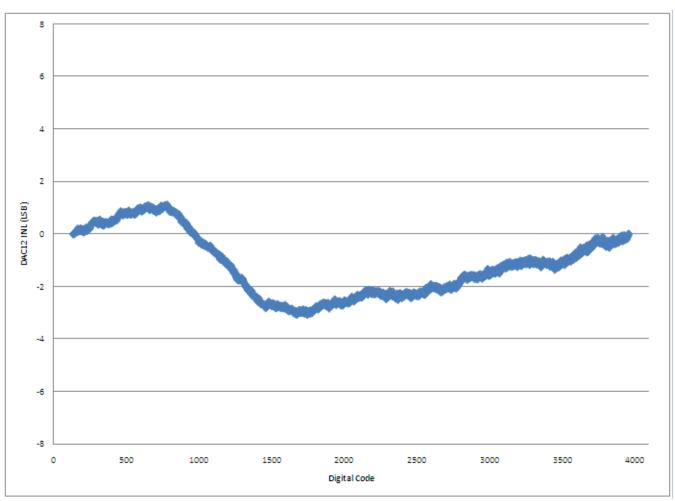

Figure 24. Typical INL error vs. digital code

# 6.8.6 CAN switching specifications

See General switching specifications.

# 6.8.7 DSPI switching specifications (limited voltage range)

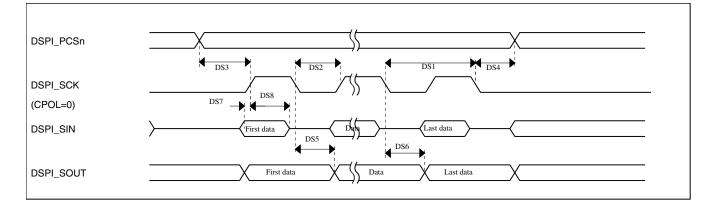

The DMA Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provide DSPI timing characteristics for classic SPI timing modes. Refer to the DSPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

| Num | Description                         | Min.                          | Max.                      | Unit | Notes |

|-----|-------------------------------------|-------------------------------|---------------------------|------|-------|

|     | Operating voltage                   | 2.7                           | 3.6                       | V    |       |

|     | Frequency of operation              | —                             | 30                        | MHz  |       |

| DS1 | DSPI_SCK output cycle time          | 2 x t <sub>BUS</sub>          | —                         | ns   |       |

| DS2 | DSPI_SCK output high/low time       | (t <sub>SCK</sub> /2) – 2     | (t <sub>SCK</sub> /2) + 2 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay   | (t <sub>BUS</sub> x 2) –<br>2 | _                         | ns   | 1     |

| DS4 | DSPI_SCK to DSPI_PCSn invalid delay | (t <sub>BUS</sub> x 2) –<br>2 | _                         | ns   | 2     |

| DS5 | DSPI_SCK to DSPI_SOUT valid         | —                             | 8.5                       | ns   |       |

| DS6 | DSPI_SCK to DSPI_SOUT invalid       | -2                            | —                         | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup    | 15                            | —                         | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold     | 0                             |                           | ns   |       |

Table 44. Master mode DSPI timing (limited voltage range)

1. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

2. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

Figure 35. I2S/SAI timing — slave modes

# 6.8.12.2 Normal Run, Wait and Stop mode performance over the full operating voltage range

This section provides the operating performance over the full operating voltage for the device in Normal Run, Wait and Stop modes.

Table 52.

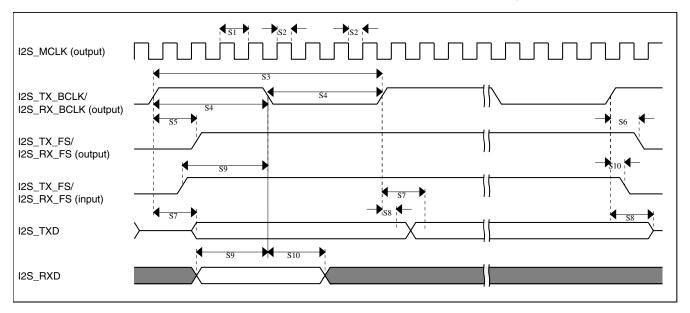

I2S/SAI master mode timing in Normal Run, Wait and Stop modes (full voltage range)

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |

| S1   | I2S_MCLK cycle time                                               | 40   | _    | ns          |

| S2   | I2S_MCLK pulse width high/low                                     | 45%  | 55%  | MCLK period |

| S3   | I2S_TX_BCLK/I2S_RX_BCLK cycle time (output)                       | 80   | _    | ns          |

| S4   | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low                      | 45%  | 55%  | BCLK period |

| S5   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output valid   | —    | 15   | ns          |

| S6   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output invalid | -1.0 | -    | ns          |

| S7   | I2S_TX_BCLK to I2S_TXD valid                                      | —    | 15   | ns          |

| S8   | I2S_TX_BCLK to I2S_TXD invalid                                    | 0    | _    | ns          |

| S9   | I2S_RXD/I2S_RX_FS input setup before<br>I2S_RX_BCLK               | 20.5 | -    | ns          |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK                    | 0    | —    | ns          |

Figure 36. I2S/SAI timing — master modes

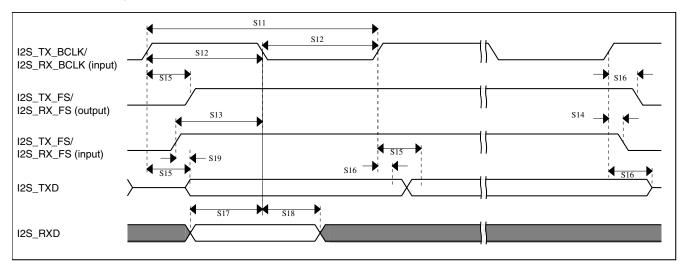

# Table 53.I2S/SAI slave mode timing in Normal Run, Wait and Stop modes<br/>(full voltage range)

| Num. | Characteristic                                                                   | Min. | Max. | Unit        |  |  |

|------|----------------------------------------------------------------------------------|------|------|-------------|--|--|

|      | Operating voltage                                                                | 1.71 | 3.6  | V           |  |  |

| S11  | I2S_TX_BCLK/I2S_RX_BCLK cycle time (input)                                       | 80   | _    | ns          |  |  |

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input)                             | 45%  | 55%  | MCLK period |  |  |

| S13  | I2S_TX_FS/I2S_RX_FS input setup before<br>I2S_TX_BCLK/I2S_RX_BCLK                | 5.8  | _    | ns          |  |  |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after<br>I2S_TX_BCLK/I2S_RX_BCLK                  | 2    | _    | ns          |  |  |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid<br>• Multiple SAI Synchronous mode | _    | 24   | ns          |  |  |

|      | All other modes                                                                  | —    | 20.6 |             |  |  |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                                  | 0    | —    | ns          |  |  |

| S17  | I2S_RXD setup before I2S_RX_BCLK                                                 | 5.8  | —    | ns          |  |  |

| S18  | I2S_RXD hold after I2S_RX_BCLK                                                   | 2    | —    | ns          |  |  |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup>                   | —    | 25   | ns          |  |  |

1. Applies to first bit in each frame and only if the TCR4[FSE] bit is clear

Figure 37. I2S/SAI timing — slave modes

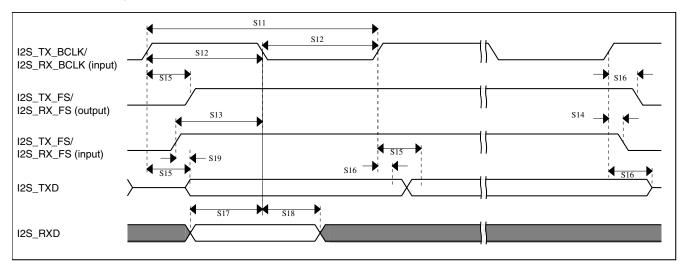

# 6.8.12.3 VLPR, VLPW, and VLPS mode performance over the full operating voltage range

This section provides the operating performance over the full operating voltage for the device in VLPR, VLPW, and VLPS modes.

Table 54.

I2S/SAI master mode timing in VLPR, VLPW, and VLPS modes (full voltage range)

| Num. | Characteristic                                                    | Min. | Max. | Unit        |  |  |

|------|-------------------------------------------------------------------|------|------|-------------|--|--|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |  |  |

| S1   | I2S_MCLK cycle time                                               | 62.5 | —    | ns          |  |  |

| S2   | I2S_MCLK pulse width high/low                                     | 45%  | 55%  | MCLK period |  |  |

| S3   | I2S_TX_BCLK/I2S_RX_BCLK cycle time (output)                       | 250  | _    | ns          |  |  |

| S4   | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low                      | 45%  | 55%  | BCLK period |  |  |

| S5   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output valid   | -    | 45   | ns          |  |  |

| S6   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output invalid | 0    | -    | ns          |  |  |

| S7   | I2S_TX_BCLK to I2S_TXD valid                                      | _    | 45   | ns          |  |  |

| S8   | I2S_TX_BCLK to I2S_TXD invalid                                    | -1.6 | _    | ns          |  |  |

| S9   | I2S_RXD/I2S_RX_FS input setup before<br>I2S_RX_BCLK               | 45   | -    | ns          |  |  |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK                    | 0    | —    | ns          |  |  |

#### Pinout

| 144<br>LQFP | 144<br>Map<br>Bga | Pin Name                                         | Default                                          | ALTO                                             | ALT1             | ALT2                                | ALT3            | ALT4                     | ALT5     | ALT6             | ALT7                   | EzPort   |

|-------------|-------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------------------|-------------------------------------|-----------------|--------------------------|----------|------------------|------------------------|----------|

| 36          | J3                | ADC0_SE16/<br>CMP1_IN2/<br>ADC0_SE21             | ADC0_SE16/<br>CMP1_IN2/<br>ADC0_SE21             | ADC0_SE16/<br>CMP1_IN2/<br>ADC0_SE21             |                  |                                     |                 |                          |          |                  |                        |          |

| 37          | M3                | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 |                  |                                     |                 |                          |          |                  |                        |          |

| 38          | L3                | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              |                  |                                     |                 |                          |          |                  |                        |          |

| 39          | L4                | DAC1_OUT/<br>CMP0_IN4/<br>CMP2_IN3/<br>ADC1_SE23 | DAC1_OUT/<br>CMP0_IN4/<br>CMP2_IN3/<br>ADC1_SE23 | DAC1_OUT/<br>CMP0_IN4/<br>CMP2_IN3/<br>ADC1_SE23 |                  |                                     |                 |                          |          |                  |                        |          |

| 40          | M7                | XTAL32                                           | XTAL32                                           | XTAL32                                           |                  |                                     |                 |                          |          |                  |                        |          |

| 41          | M6                | EXTAL32                                          | EXTAL32                                          | EXTAL32                                          |                  |                                     |                 |                          |          |                  |                        |          |

| 42          | L6                | VBAT                                             | VBAT                                             | VBAT                                             |                  |                                     |                 |                          |          |                  |                        |          |

| 43          | -                 | VDD                                              | VDD                                              | VDD                                              |                  |                                     |                 |                          |          |                  |                        |          |

| 44          | -                 | VSS                                              | VSS                                              | VSS                                              |                  |                                     |                 |                          |          |                  |                        |          |

| 45          | M4                | PTE24                                            | ADC0_SE17/<br>EXTAL1                             | ADC0_SE17/<br>EXTAL1                             | PTE24            | CAN1_TX                             | UART4_TX        | I2S1_TX_FS               |          | EWM_OUT_b        | I2S1_RXD1              |          |

| 46          | K5                | PTE25                                            | ADC0_SE18/<br>XTAL1                              | ADC0_SE18/<br>XTAL1                              | PTE25            | CAN1_RX                             | UART4_RX        | I2S1_TX_<br>BCLK         |          | EWM_IN           | I2S1_TXD1              |          |

| 47          | K4                | PTE26                                            | ADC3_SE5b                                        | ADC3_SE5b                                        | PTE26            | ENET_1588_<br>CLKIN                 | UART4_CTS_<br>b | I2S1_TXD0                |          | RTC_CLKOUT       | USB_CLKIN              |          |

| 48          | J4                | PTE27                                            | ADC3_SE4b                                        | ADC3_SE4b                                        | PTE27            |                                     | UART4_RTS_<br>b | I2S1_MCLK                |          |                  |                        |          |

| 49          | H4                | PTE28                                            | ADC3_SE7a                                        | ADC3_SE7a                                        | PTE28            |                                     |                 |                          |          |                  |                        |          |

| 50          | J5                | PTA0                                             | JTAG_TCLK/<br>SWD_CLK/<br>EZP_CLK                | TSI0_CH1                                         | PTA0             | UART0_CTS_<br>b/<br>UART0_COL_<br>b | FTM0_CH5        |                          |          |                  | JTAG_TCLK/<br>SWD_CLK  | EZP_CLK  |

| 51          | J6                | PTA1                                             | JTAG_TDI/<br>EZP_DI                              | TSI0_CH2                                         | PTA1             | UART0_RX                            | FTM0_CH6        |                          |          |                  | JTAG_TDI               | EZP_DI   |

| 52          | K6                | PTA2                                             | JTAG_TDO/<br>TRACE_SWO/<br>EZP_DO                | TSI0_CH3                                         | PTA2             | UARTO_TX                            | FTM0_CH7        |                          |          |                  | JTAG_TDO/<br>TRACE_SWO | EZP_DO   |

| 53          | K7                | PTA3                                             | JTAG_TMS/<br>SWD_DIO                             | TSI0_CH4                                         | PTA3             | UART0_RTS_<br>b                     | FTM0_CH0        |                          |          |                  | JTAG_TMS/<br>SWD_DIO   |          |

| 54          | L7                | PTA4/<br>LLWU_P3                                 | NMI_b/<br>EZP_CS_b                               | TSI0_CH5                                         | PTA4/<br>LLWU_P3 |                                     | FTM0_CH1        |                          |          |                  | NMI_b                  | EZP_CS_b |

| 55          | M8                | PTA5                                             | DISABLED                                         |                                                  | PTA5             | USB_CLKIN                           | FTM0_CH2        | RMII0_RXER/<br>MII0_RXER | CMP2_OUT | I2S0_TX_<br>BCLK | JTAG_TRST_<br>b        |          |

| 56          | E7                | VDD                                              | VDD                                              | VDD                                              |                  |                                     |                 |                          |          |                  |                        |          |

| 57          | G7                | VSS                                              | VSS                                              | VSS                                              |                  |                                     |                 |                          |          |                  |                        |          |

| 58          | J7                | PTA6                                             | ADC3_SE6a                                        | ADC3_SE6a                                        | PTA6             | ULPI_CLK                            | FTM0_CH3        | I2S1_RXD0                | CLKOUT   |                  | TRACE_<br>CLKOUT       |          |