Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 516096                                                                      |

| Number of I/O                  | 620                                                                         |

| Number of Gates                | 3000000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -55°C ~ 125°C (TJ)                                                          |

| Package / Case                 | 896-BGA                                                                     |

| Supplier Device Package        | 896-FBGA (31x31)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pe3000l-1fg896m |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 – Military ProASIC3/EL Device Family Overview

## **General Description**

The military ProASIC3/EL family of flash FPGAs dramatically reduces dynamic power consumption by 40% and static power by 50%. These power savings are coupled with performance, density, true single chip, 1.2 V to 1.5 V core and I/O operation, reprogrammability, and advanced features.

Microsemi's proven Flash\*Freeze technology enables military ProASIC3EL device users to shut off dynamic power instantaneously and switch the device to static mode without the need to switch off clocks or power supplies, and retaining internal states of the device. This greatly simplifies power management. In addition, optimized software tools using power-driven layout provide instant push-button power reduction.

Nonvolatile flash technology gives military ProASIC3/EL devices the advantage of being a secure, low-power, single-chip solution that is live at power-up (LAPU). Military ProASIC3/EL devices offer dramatic dynamic power savings, giving FPGA users flexibility to combine low power with high performance.

These features enable designers to create high-density systems using existing ASIC or FPGA design flows and tools.

Military ProASIC3/EL devices offer 1 kbit of on-chip, reprogrammable, nonvolatile FlashROM storage as well as clock conditioning circuitry (CCC) based on an integrated phase-locked loop (PLL). Military ProASIC3/EL devices support devices from 250K system gates to 3 million system gates with up to 504 kbits of true dual-port SRAM and 620 user I/Os.

M1 military ProASIC3/EL devices support the high-performance, 32-bit Cortex-M1 processor developed by ARM for implementation in FPGAs. ARM Cortex-M1 is a soft processor that is fully implemented in the FPGA fabric. It has a three-stage pipeline that offers a good balance between low-power consumption and speed when implemented in an M1 military ProASIC3/EL device. The processor runs the ARMv6-M instruction set, has a configurable nested interrupt controller, and can be implemented with or without the debug block. ARM Cortex-M1 is available at no cost from Microsemi for use in M1 military ProASIC3/EL FPGAs.

The ARM-enabled devices have ordering numbers that begin with M1 and do not support AES decryption.

### Flash\*Freeze Technology<sup>†</sup>

Military ProASIC3EL devices offer Flash\*Freeze technology, which allows instantaneous switching from an active state to a static state. When Flash\*Freeze mode is activated, military ProASIC3EL devices enter a static state while retaining the contents of registers and SRAM. Power is conserved without the need for additional external components to turn off I/Os or clocks. Flash\*Freeze technology is combined with in-system programmability, which enables users to quickly and easily upgrade and update their designs in the final stages of manufacturing or in the field. The ability of military ProASIC3EL devices to support a 1.2 V core voltage allows for an even greater reduction in power consumption, which enables low total system power.

When the military ProASIC3EL device enters Flash\*Freeze mode, the device automatically shuts off the clocks and inputs to the FPGA core; when the device exits Flash\*Freeze mode, all activity resumes and data is retained.

The availability of low-power modes, combined with a reprogrammable, single-chip, single-voltage solution, make military ProASIC3EL devices suitable for low-power data transfer and manipulation in military-temperature applications where available power may be limited (e.g., in battery-powered equipment); or where heat dissipation may be limited (e.g., in enclosures with no forced cooling).

<sup>†</sup> Flash\*Freeze technology is not supported on A3P1000.

Military ProASIC3/EL Device Family Overview

### Flash Advantages

### Low Powerf

The military ProASIC3EL family of flash-based FPGAs provides a low-power advantage, and when coupled with high performance, enables designers to make power-smart choices using a single-chip, reprogrammable, and live-at-power-up device.

Military ProASIC3EL devices offer 40% dynamic power and 50% static power savings by reducing the core operating voltage to 1.2 V. In addition, the power-driven layout (PDL) feature in Libero®SoC offers up to 30% additional power reduction. With Flash\*Freeze technology, military ProASIC3EL device is able to retain device SRAM and logic while dynamic power is reduced to a minimum, without the need to stop clock or power supplies. Combining these features provides a low-power, feature-rich, and highperformance solution.

### Security

Nonvolatile, flash-based military ProASIC3/EL devices do not require a boot PROM, so there is no vulnerable external bitstream that can be easily copied. Military ProASIC3/EL devices incorporate FlashLock, which provides a unique combination of reprogrammability and design security without external overhead, advantages that only an FPGA with nonvolatile flash programming can offer.

Military ProASIC3/EL devices utilize a 128-bit flash-based lock and a separate AES key to secure programmed intellectual property and configuration data. In addition, all FlashROM data in military ProASIC3/EL devices can be encrypted prior to loading, using the industry-leading AES-128 (FIPS192) bit block cipher encryption standard. AES was adopted by the National Institute of Standards and Technology (NIST) in 2000 and replaces the 1977 DES standard. Military ProASIC3/EL devices have a built-in AES decryption engine and a flash-based AES key that make them the most comprehensive programmable logic device security solution available today. Military ProASIC3/EL devices with AESbased security allow for secure, remote field updates over public networks such as the Internet, and ensure that valuable IP remains out of the hands of system overbuilders, system cloners, and IP thieves.

Security, built into the FPGA fabric, is an inherent component of the military ProASIC3/EL family. The flash cells are located beneath seven metal layers, and many device design and layout techniques have been used to make invasive attacks extremely difficult. The military ProASIC3/EL family, with FlashLock and AES security, is unique in being highly resistant to both invasive and noninvasive attacks. Your valuable IP is protected and secure, making remote ISP possible. A military ProASIC3/EL device provides the most impenetrable security for programmable logic designs.

### Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system power-up (unlike SRAM-based FPGAs). Therefore, flash-based military ProASIC3/EL FPGAs do not require system configuration components such as EEPROMs or microcontrollers to load device configuration data. This reduces bill-of-materials costs and PCB area, and increases security and system reliability.

### Live at Power-Up

Flash-based military ProASIC3/EL devices support Level 0 of the LAPU classification standard. This feature helps in system component initialization, execution of critical tasks before the processor wakes up, setup and configuration of memory blocks, clock generation, and bus activity management. The LAPU feature of flash-based military ProASIC3/EL devices greatly simplifies total system design and reduces total system cost, often eliminating the need for CPLDs and clock generation PLLs. In addition, glitches and brownouts in system power will not corrupt the military ProASIC3/EL device's flash configuration, and unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables the reduction or complete removal of the configuration PROM, expensive voltage monitor, brownout detection, and clock generator devices from the PCB design. Flash-based military ProASIC3/EL devices simplify total system design and reduce cost and design risk while increasing system reliability and improving system initialization time.

f A3P1000 only supports 1.5 V core operation.

1-2 Revision 5

Table 2-2 • Recommended Operating Conditions <sup>1</sup>

| Symbol                    | Parameter                                                    |                                                   | Military                | Units |

|---------------------------|--------------------------------------------------------------|---------------------------------------------------|-------------------------|-------|

| T <sub>J</sub>            | Junction temperature                                         |                                                   | –55 to 125 <sup>2</sup> | °C    |

| VCC                       | 1.5 V DC core supply voltage <sup>3</sup>                    |                                                   | 1.425 to 1.575          | V     |

|                           | 1.2 V - 1.5 V wide range DC core supply voltage <sup>4</sup> |                                                   | 1.14 to 1.575           | V     |

| VJTAG                     | JTAG DC voltage                                              |                                                   | 1.4 to 3.6              | V     |

| VPUMP <sup>5</sup>        | Programming voltage                                          | Programming mode                                  | 3.15 to 3.45            | V     |

|                           |                                                              | Operation <sup>6</sup>                            | 0 to 3.6                | V     |

| VCCPLL <sup>5</sup>       | Analog power supply (PLL)                                    | 1.5 V DC core supply voltage <sup>3</sup>         | 1.425 to 1.575          | V     |

|                           |                                                              | 1.2 V - 1.5 V DC core supply voltage <sup>4</sup> | 1.14 to 1.575           | V     |

| VCCI and VMV <sup>5</sup> | 1.2 V DC supply voltage <sup>4</sup>                         |                                                   | 1.14 to 1.26            | V     |

|                           | 1.2 V wide range DC supply voltage <sup>4</sup>              |                                                   | 1.14 to 1.575           | V     |

|                           | 1.5 V DC supply voltage                                      |                                                   | 1.425 to 1.575          | V     |

|                           | 1.8 V DC supply voltage                                      |                                                   | 1.7 to 1.9              | V     |

|                           | 2.5 V DC supply voltage                                      |                                                   | 2.3 to 2.7              | V     |

|                           | 3.0 V DC supply voltage <sup>7</sup>                         |                                                   | 2.7 to 3.6              | V     |

|                           | 3.3 V DC supply voltage                                      |                                                   | 3.0 to 3.6              | V     |

|                           | LVDS differential I/O                                        |                                                   | 2.375 to 2.625          | V     |

|                           | LVPECL differential I/O                                      |                                                   | 3.0 to 3.6              | V     |

### Notes:

- 1. All parameters representing voltages are measured with respect to GND unless otherwise specified.

- 2. Default Junction Temperature Range in the Libero SoC software is set from 0°C to +70°C for commercial, and -40°C to +85°C for industrial. To ensure targeted reliability standards are met across the full range of junction temperatures, Microsemi recommends using custom settings for temperature range before running timing and power analysis tools. For more information regarding custom settings, refer to the New Project Dialog Box in the Libero SoC Online Help.

- 3. For A3P250 and A3P1000

- 4. For A3PE600L and A3PE3000L devices only, operating at VCCI ≥ VCC.

- 5. See the "Pin Descriptions and Packaging" section on page 3-1 for instructions and recommendations on tie-off and supply grouping.

- 6. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-25 on page 2-22. VCCI should be at the same voltage within a given I/O bank.

- 7. 3.3 V wide range is compliant to the JESD8-B specification and supports 3.0 V VCCI operation.

- 8. To ensure targeted reliability standards are met across ambient and junction operating temperatures, Microsemi recommends that the user follow best design practices using Microsemi's timing and power simulation tools.

2-2 Revision 5

### **Quiescent Supply Current**

Table 2-8 • Power Supply State Per Mode

|                      |     | Power Supply Configurations |      |       |                 |  |  |  |  |  |  |  |

|----------------------|-----|-----------------------------|------|-------|-----------------|--|--|--|--|--|--|--|

| Modes/Power Supplies | vcc | VCCPLL                      | VCCI | VJTAG | VPUMP           |  |  |  |  |  |  |  |

| Flash*Freeze         | On  | On                          | On   | On    | On/off/floating |  |  |  |  |  |  |  |

| Sleep                | Off | Off                         | On   | Off   | Off             |  |  |  |  |  |  |  |

| Shutdown             | Off | Off                         | Off  | Off   | Off             |  |  |  |  |  |  |  |

| Static and Active    | On  | On                          | On   | On    | On/off/floating |  |  |  |  |  |  |  |

Table 2-9 • Quiescent Supply Current (IDD) Characteristics, Flash\*Freeze Mode\*

|                          | Core Voltage | A3PE600L | A3PE3000L | Units |

|--------------------------|--------------|----------|-----------|-------|

| Nominal (25°C)           | 1.2 V        | 0.55     | 2.75      | mA    |

|                          | 1.5 V        | 0.83     | 4.2       | mA    |

| Typical maximum (25°C)   | 1.2 V        | 9        | 17        | mA    |

|                          | 1.5 V        | 12       | 20        | mA    |

| Military maximum (125°C) | 1.2 V        | 65       | 165       | mA    |

|                          | 1.5 V        | 85       | 185       | mA    |

Note: \*IDD includes VCC, VPUMP, VCCI, VJTAG, and VCCPLL currents. Values do not include I/O static contribution (PDC6 and PDC7).

Table 2-10 • Quiescent Supply Current (IDD) Characteristics, Sleep Mode (VCC = 0 V)\*

|                                                   | Core Voltage  | A3PE600L | A3PE3000L | Units |

|---------------------------------------------------|---------------|----------|-----------|-------|

| VCCI / VJTAG = 1.2 V (per bank)<br>Typical (25°C) | 1.2 V         | 1.7      | 1.7       | μА    |

| VCCI / VJTAG = 1.5 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 1.8      | 1.8       | μΑ    |

| VCCI / VJTAG = 1.8 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 1.9      | 1.9       | μΑ    |

| VCCI / VJTAG = 2.5 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 2.2      | 2.2       | μΑ    |

| VCCI / VJTAG = 3.3 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 2.5      | 2.5       | μΑ    |

Note: \*IDD = N<sub>BANKS</sub> × ICCI. Values do not include I/O static contribution, which is shown in Table 2-22 on page 2-14 (PDC6 and PDC7).

Table 2-11 • Quiescent Supply Current (IDD) Characteristics, Shutdown Mode\*

|                  | Core Voltage  | A3P250 | A3P1000 | A3PE600L | Units |    |

|------------------|---------------|--------|---------|----------|-------|----|

| Nominal (25°C)   | 1.2 V / 1.5 V | N//    | I/A 0   |          |       |    |

| Military (125°C) | 1.2 V / 1.5 V | N//    | 4       |          | 0     | μΑ |

Note: \*This is applicable to A3PE600L and A3PE3000L only for cold-sparable I/O devices. Not available on A3P250 or A3P1000.

### **User I/O Characteristics**

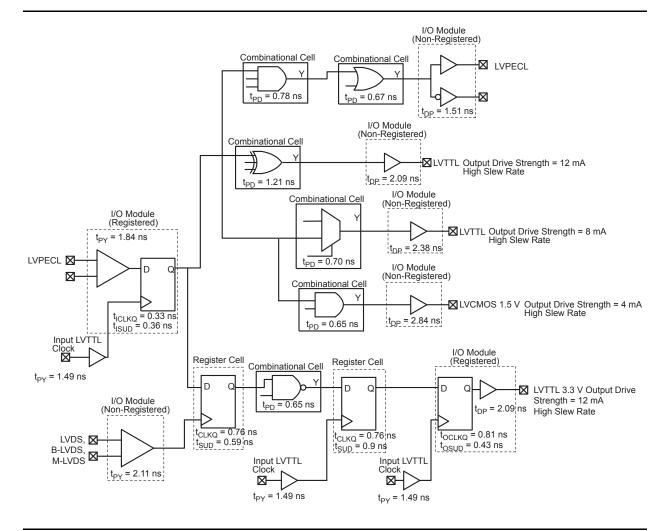

### **Timing Model**

Figure 2-3 • Timing Model

Operating Conditions: -1 Speed, Military Temperature Range (T<sub>J</sub> = 125°C), Worst-Case

VCC = 1.14 V (example for A3PE3000L and A3PE600L)

2-18 Revision 5

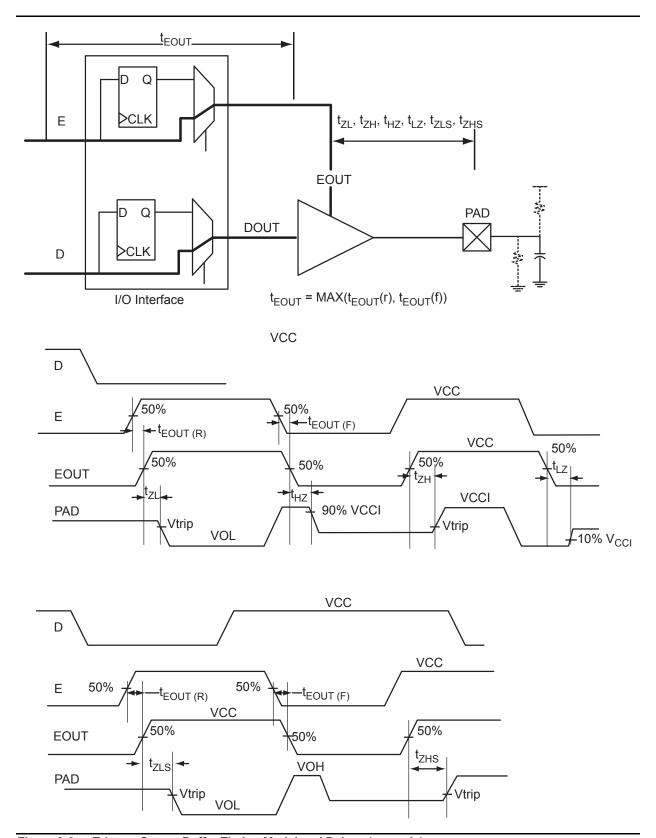

Figure 2-6 • Tristate Output Buffer Timing Model and Delays (example)

### **Timing Characteristics**

1.2 V DC Core Voltage

Table 2-74 • 2.5 V LVCMOS Low Slew

Military-Case Conditions: T<sub>J</sub> = 125°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V

Applicable to Pro I/Os for A3PE600L and A3PE3000L Only

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.80              | 6.87            | 0.05             | 2.04            | 2.56             | 0.52              | 6.99            | 5.83            | 2.70            | 2.19            | 9.20             | 8.03             | ns    |

|                   | -1             | 0.68              | 5.84            | 0.05             | 1.73            | 2.17             | 0.44              | 5.95            | 4.96            | 2.29            | 1.86            | 7.82             | 6.83             | ns    |

| 8 mA              | Std.           | 0.80              | 5.62            | 0.05             | 2.04            | 2.56             | 0.52              | 5.72            | 4.94            | 3.08            | 2.90            | 7.92             | 7.14             | ns    |

|                   | -1             | 0.68              | 4.78            | 0.05             | 1.73            | 2.17             | 044               | 4.86            | 4.20            | 2.62            | 2.47            | 6.74             | 6.08             | ns    |

| 12 mA             | Std.           | 0.80              | 4.73            | 0.05             | 2.04            | 2.56             | 0.52              | 4.81            | 4.30            | 3.34            | 3.38            | 7.01             | 6.50             | ns    |

|                   | -1             | 0.68              | 4.02            | 0.05             | 1.73            | 2.17             | 0.44              | 4.09            | 3.65            | 2.84            | 2.87            | 5.97             | 5.53             | ns    |

| 16 mA             | Std.           | 0.80              | 4.46            | 0.05             | 2.04            | 2.56             | 0.52              | 4.53            | 4.16            | 3.39            | 3.50            | 6.74             | 6.36             | ns    |

|                   | -1             | 0.68              | 3.79            | 0.05             | 1.73            | 2.17             | 0.44              | 3.86            | 3.54            | 2.89            | 2.98            | 5.73             | 5.41             | ns    |

| 24 mA             | Std.           | 0.80              | 4.34            | 0.05             | 2.04            | 2.56             | 0.52              | 4.41            | 4.17            | 3.47            | 3.96            | 6.62             | 6.38             | ns    |

|                   | -1             | 0.68              | 3.69            | 0.05             | 1.73            | 2.17             | 0.44              | 3.75            | 3.55            | 2.95            | 3.96            | 5.63             | 5.43             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-75 • 2.5 V LVCMOS High Slew

Military-Case Conditions: T<sub>J</sub> = 125°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V

Applicable to Pro I/Os for A3PE600L and A3PE3000L Only

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.80              | 3.51            | 0.05             | 2.04            | 2.56             | 0.52              | 3.56            | 3.13            | 2.70            | 2.27            | 5.77             | 5.33             | ns    |

|                   | -1             | 0.68              | 2.98            | 0.05             | 1.73            | 2.17             | 0.44              | 3.03            | 2.66            | 2.29            | 1.93            | 4.91             | 4.53             | ns    |

| 8 mA              | Std.           | 0.80              | 2.87            | 0.05             | 2.04            | 2.56             | 0.52              | 2.92            | 2.40            | 3.08            | 3.01            | 5.12             | 4.61             | ns    |

|                   | -1             | 0.68              | 2.44            | 0.05             | 1.73            | 2.17             | 0.44              | 2.48            | 2.05            | 2.62            | 2.56            | 4.36             | 3.92             | ns    |

| 12 mA             | Std.           | 0.80              | 2.50            | 0.05             | 2.04            | 2.56             | 0.52              | 2.53            | 2.05            | 3.34            | 3.47            | 4.74             | 4.25             | ns    |

|                   | -1             | 0.68              | 2.12            | 0.05             | 1.73            | 2.17             | 0.44              | 2.15            | 1.74            | 2.84            | 2.95            | 4.03             | 3.62             | ns    |

| 16 mA             | Std.           | 0.80              | 2.43            | 0.05             | 2.04            | 2.56             | 0.52              | 2.47            | 1.98            | 3.39            | 3.59            | 4.67             | 4.19             | ns    |

|                   | -1             | 0.68              | 2.07            | 0.05             | 1.73            | 2.17             | 0.44              | 2.10            | 1.69            | 2.89            | 3.06            | 3.97             | 3.56             | ns    |

| 24 mA             | Std.           | 0.80              | 2.44            | 0.05             | 2.04            | 2.56             | 0.52              | 2.48            | 1.90            | 3.47            | 4.08            | 4.68             | 4.10             | ns    |

|                   | -1             | 0.68              | 2.08            | 0.05             | 1.73            | 2.17             | 0.44              | 2.11            | 1.61            | 2.95            | 3.47            | 3.98             | 3.49             | ns    |

#### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### **Voltage-Referenced I/O Characteristics**

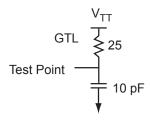

### 3.3 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The  $V_{CCI}$  pin should be connected to 3.3 V.

Table 2-120 • Minimum and Maximum DC Input and Output Levels

| 3.3 V GTL          |           | VIL         | VIH         |           | VOL       | VOH       | I <sub>OL</sub> | $I_{OH}$ | I <sub>OSL</sub>        | I <sub>osh</sub>        | I <sub>IL</sub> 1       | l <sub>IH</sub> <sup>2</sup> |

|--------------------|-----------|-------------|-------------|-----------|-----------|-----------|-----------------|----------|-------------------------|-------------------------|-------------------------|------------------------------|

| Drive<br>Strength  | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V | mA              | mA       | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup>      |

| 20 mA <sup>5</sup> | -0.3      | VREF - 0.05 | VREF + 0.05 | 3.6       | 0.4       | _         | 20              | 20       | 268                     | 181                     | 15                      | 15                           |

#### Notes:

- 1.  $I_{|L|}$  is the input leakage current per I/O pin over recommended operating conditions where -0.3 V < VIN < VIL.

- 2. II<sub>H</sub> is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 125°C junction temperature.

- 5. Output drive strength is below JEDEC specification.

Figure 2-15 • AC Loading

Table 2-121 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF - 0.05   | VREF + 0.05    | 0.8                     | 0.8             | 1.2            | 10                     |

Note: \*Measuring point =  $V_{trip}$ . See Table 2-29 on page 2-25 for a complete table of trip points.

### **Timing Characteristics**

#### Table 2-122 • 3.3 V GTL

Military-Case Conditions:  $T_J$  = 125°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V, VREF = 0.8 V Applicable to Pro I/Os for A3PE600L and A3PE3000L Only

Speed Speed

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.80              | 2.05            | 0.05             | 2.34            | 0.52              | 2.01            | 2.05            | -               | -               | 4.22             | 4.26             | ns    |

| <b>–</b> 1     | 0.68              | 1.75            | 0.05             | 1.99            | 0.44              | 1.71            | 1.75            | -               | -               | 3.59             | 3.62             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### **B-LVDS/M-LVDS**

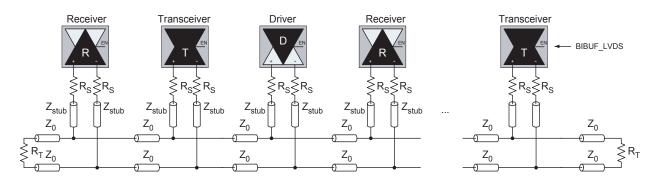

Bus LVDS (B-LVDS) and Multipoint LVDS (M-LVDS) specifications extend the existing LVDS standard to high-performance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate the loading. The drivers require series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus since the driver can be located anywhere on the bus. These configurations can be implemented using the TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 2-26. The input and output buffer delays are available in the LVDS section in Table 2-160 on page 2-86.

Example: For a bus consisting of 20 equidistant loads, the following terminations provide the required differential voltage, in worst-case Industrial operating conditions, at the farthest receiver:  $R_S$  = 60  $\Omega$  and  $R_T$  = 70  $\Omega$ , given  $Z_0$  = 50  $\Omega$  (2") and  $Z_{stub}$  = 50  $\Omega$  (~1.5").

Figure 2-26 • B-LVDS/M-LVDS Multipoint Application Using LVDS I/O Buffers

2-88 Revision 5

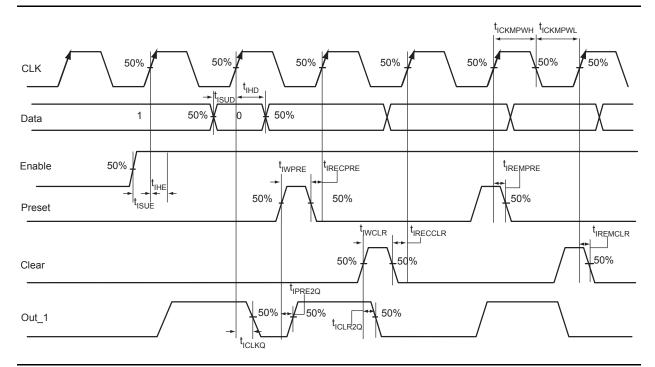

### Input Register

Figure 2-30 • Input Register Timing Diagram

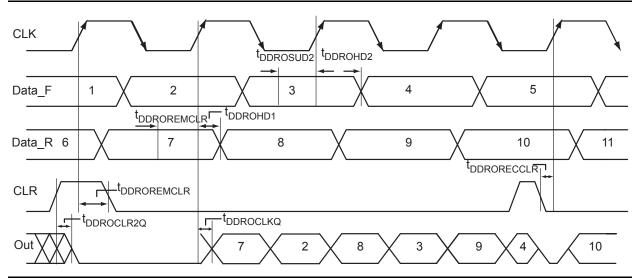

Figure 2-36 • Output DDR Timing Diagram

### **Timing Characteristics**

Table 2-186 • Output DDR Propagation Delays

Military-Case Conditions: T<sub>J</sub> = 125°C, Worst-Case VCC = 1.14 V for A3PE600L and A3PE3000L

| Parameter               | Description                                           | -1   | Std. | Units |

|-------------------------|-------------------------------------------------------|------|------|-------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out of DDR for Output DDR                    | 0.97 | 1.14 | ns    |

| t <sub>DDRISUD1</sub>   | Data_F Data Setup for Output DDR                      | 0.52 | 0.62 | ns    |

| t <sub>DDROSUD2</sub>   | Data_R Data Setup for Output DDR                      | 0.52 | 0.62 | ns    |

| t <sub>DDROHD1</sub>    | Data_F Data Hold for Output DDR                       | 0.00 | 0.00 | ns    |

| t <sub>DDROHD2</sub>    | Data_R Data Hold for Output DDR                       | 0.00 | 0.00 | ns    |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out for Output DDR              | 1.11 | 1.30 | ns    |

| t <sub>DDROREMCLR</sub> | Asynchronous Clear Removal Time for Output DDR        | 0.00 | 0.00 | ns    |

| t <sub>DDRORECCLR</sub> | Asynchronous Clear Recovery Time for Output DDR       | 0.31 | 0.36 | ns    |

| t <sub>DDROWCLR1</sub>  | Asynchronous Clear Minimum Pulse Width for Output DDR | 0.19 | 0.22 | ns    |

| t <sub>DDROCKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Output DDR     | 0.31 | 0.36 | ns    |

| t <sub>DDROCKMPWL</sub> | Clock Minimum Pulse Width LOW for the Output DDR      | 0.28 | 0.32 | ns    |

| F <sub>DDROMAX</sub>    | Maximum Frequency for the Output DDR                  | 160  | 160  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2-108 Revision 5

Table 2-187 • Output DDR Propagation Delays

Military-Case Conditions: T<sub>J</sub> = 125°C, VCC = 1.425 V for A3PE600L and A3PE3000L

| Parameter               | Description                                           | -1   | Std. | Units |

|-------------------------|-------------------------------------------------------|------|------|-------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out of DDR for Output DDR                    | 0.74 | 0.87 | ns    |

| t <sub>DDRISUD1</sub>   | Data_F Data Setup for Output DDR                      | 0.40 | 0.47 | ns    |

| t <sub>DDROSUD2</sub>   | Data_R Data Setup for Output DDR                      | 0.40 | 0.47 | ns    |

| t <sub>DDROHD1</sub>    | Data_F Data Hold for Output DDR                       | 0.00 | 0.00 | ns    |

| t <sub>DDROHD2</sub>    | Data_R Data Hold for Output DDR                       | 0.00 | 0.00 | ns    |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out for Output DDR              | 0.85 | 1.00 | ns    |

| t <sub>DDROREMCLR</sub> | Asynchronous Clear Removal Time for Output DDR        | 0.00 | 0.00 | ns    |

| t <sub>DDRORECCLR</sub> | Asynchronous Clear Recovery Time for Output DDR       | 0.24 | 0.28 | ns    |

| t <sub>DDROWCLR1</sub>  | Asynchronous Clear Minimum Pulse Width for Output DDR | 0.19 | 0.22 | ns    |

| t <sub>DDROCKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Output DDR     | 0.31 | 0.36 | ns    |

| t <sub>DDROCKMPWL</sub> | Clock Minimum Pulse Width LOW for the Output DDR      | 0.28 | 0.32 | ns    |

| F <sub>DDROMAX</sub>    | Maximum Frequency for the Output DDR                  | 250  | 250  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-188 • Output DDR Propagation Delays Military-Case Conditions:  $T_J = 125^{\circ}\text{C}$ , Worst-Case VCC = 1.425 V for A3P250 and A3P1000

| Parameter               | Description                                           | -1   | Std. | Units |

|-------------------------|-------------------------------------------------------|------|------|-------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out of DDR for Output DDR                    | 0.84 | 0.99 | ns    |

| t <sub>DDRISUD1</sub>   | Data_F Data Setup for Output DDR                      | 0.46 | 0.54 | ns    |

| t <sub>DDROSUD2</sub>   | Data_R Data Setup for Output DDR                      | 0.46 | 0.54 | ns    |

| t <sub>DDROHD1</sub>    | Data_F Data Hold for Output DDR                       | 0.00 | 0.00 | ns    |

| t <sub>DDROHD2</sub>    | Data_R Data Hold for Output DDR                       | 0.00 | 0.00 | ns    |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out for Output DDR              | 0.96 | 1.13 | ns    |

| t <sub>DDROREMCLR</sub> | Asynchronous Clear Removal Time for Output DDR        | 0.00 | 0.00 | ns    |

| t <sub>DDRORECCLR</sub> | Asynchronous Clear Recovery Time for Output DDR       | 0.27 | 0.31 | ns    |

| t <sub>DDROWCLR1</sub>  | Asynchronous Clear Minimum Pulse Width for Output DDR | 0.25 | 0.30 | ns    |

| t <sub>DDROCKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Output DDR     | 0.41 | 0.48 | ns    |

| t <sub>DDROCKMPWL</sub> | Clock Minimum Pulse Width LOW for the Output DDR      | 0.37 | 0.43 | ns    |

| F <sub>DDROMAX</sub>    | Maximum Frequency for the Output DDR                  | 309  | 263  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-6 for derating values.

Table 2-191 • Combinatorial Cell Propagation Delays

Military-Case Conditions: T<sub>J</sub> = 125°C, Worst-Case VCC = 1.425 V for A3P250 and A3P1000

| Combinatorial Cell | Equation                | Parameter       | -1   | Std. | Units |

|--------------------|-------------------------|-----------------|------|------|-------|

| INV                | Y = !A                  | t <sub>PD</sub> | 0.48 | 0.57 | ns    |

| AND2               | Y = A · B               | t <sub>PD</sub> | 0.57 | 0.67 | ns    |

| NAND2              | Y = !(A · B)            | t <sub>PD</sub> | 0.57 | 0.67 | ns    |

| OR2                | Y = A + B               | t <sub>PD</sub> | 0.59 | 0.69 | ns    |

| NOR2               | Y = !(A + B)            | t <sub>PD</sub> | 0.59 | 0.69 | ns    |

| XOR2               | Y = A ⊕ B               | t <sub>PD</sub> | 0.89 | 1.04 | ns    |

| MAJ3               | Y = MAJ(A , B, C)       | t <sub>PD</sub> | 0.84 | 0.99 | ns    |

| XOR3               | Y = A ⊕ B ⊕ C           | t <sub>PD</sub> | 1.05 | 1.24 | ns    |

| MUX2               | Y = A !S + B S          | t <sub>PD</sub> | 0.61 | 0.72 | ns    |

| AND3               | $Y = A \cdot B \cdot C$ | t <sub>PD</sub> | 0.68 | 0.79 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-6 for derating values.

### 1.5 V DC Core Voltage

Table 2-197 • A3PE600L Global Resource

Military-Case Conditions: T<sub>J</sub> = 125°C, VCC = 1.425 V

|                      |                                           | -                 | -1 Std.           |                   |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.82              | 1.07              | 0.97              | 1.26              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.81              | 1.10              | 0.95              | 1.30              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |                   |                   |                   |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |                   |                   |                   |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.30              |                   | 0.35              | ns    |

| F <sub>RMAX</sub>    | Maximum Frequency for Global Clock        |                   |                   |                   |                   | MHz   |

### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-198 • A3PE3000L Global Resource

Military-Case Conditions: T<sub>J</sub> = 125°C, VCC = 1.425 V

|                      |                                           | -1                |                   | S                 | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.62              | 1.87              | 1.90              | 2.20              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.61              | 1.90              | 1.89              | 2.24              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |                   |                   |                   |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |                   |                   |                   |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.30              |                   | 0.35              | ns    |

| F <sub>RMAX</sub>    | Maximum Frequency for Global Clock        |                   |                   |                   |                   | MHz   |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-202 • Military ProASIC3/EL CCC/PLL Specification For Devices Operating at 1.5 V DC Core Voltage

| Parameter                                                          | Min.    | Тур.                                           | Max.    | Units    |

|--------------------------------------------------------------------|---------|------------------------------------------------|---------|----------|

| Clock Conditioning Circuitry Input Frequency f <sub>IN_CCC</sub>   | 1.5     |                                                | 350     | MHz      |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT_CCC</sub> | 0.75    |                                                | 350     | MHz      |

| Delay Increments in Programmable Delay Blocks 1, 2,3               |         | 160                                            |         | ps       |

| Number of Programmable Values in Each Programmable Delay Block     |         |                                                | 32      |          |

| Serial Clock (SCLK) for Dynamic PLL <sup>4</sup>                   |         |                                                | 110     | MHz      |

| Input cycle-to-cycle jitter (peak magnitude)                       |         |                                                | 1.5     | ns       |

| Acquisition Time                                                   |         |                                                |         |          |

| LockControl = 0                                                    |         |                                                | 300     | μs       |

| LockControl = 1                                                    |         |                                                | 6.0     | ms       |

| Tracking Jitter <sup>5</sup>                                       |         |                                                |         |          |

| LockControl = 0                                                    |         |                                                | 1.6     | ns       |

| LockControl = 1                                                    |         |                                                | 0.8     | ns       |

| Output Duty Cycle                                                  | 48.5    |                                                | 51.5    | %        |

| Delay Range in Block: Programmable Delay 1 1,2                     | 0.6     |                                                | 5.56    | ns       |

| Delay Range in Block: Programmable Delay 2 1,2                     | 0.025   |                                                | 5.56    | ns       |

| Delay Range in Block: Fixed Delay <sup>1,2</sup>                   |         | 2.2                                            |         | ns       |

| CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub>         | Max. F  | Max. Peak-to-Peak Period Jitter <sup>6,7</sup> |         |          |

| _                                                                  | SSO ≤ 2 | SSO ≤ 4                                        | SSO ≤ 8 | SSO ≤ 16 |

| 0.75 MHz to 50 MHz                                                 | 0.50%   | 0.50%                                          | 0.70%   | 1.00%    |

| 50 MHz to 250 MHz                                                  | 1.00%   | 3.00%                                          | 5.00%   | 9.00%    |

| 250 MHz to 350 MHz                                                 | 2.50%   | 4.00%                                          | 6.00%   | 12.00%   |

#### Notes:

- 1. This delay is a function of voltage and temperature. See Table 2-6 on page 2-6 for deratings.

- 2.  $T_{.I} = 25^{\circ}C$ , VCC = 1.5 V.

- 3. When the CCC/PLL core is generated by Mircosemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero online help associated with the core for more information.

- 4. Maximum value obtained for a -1 speed grade device in worst-case military conditions. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

- 5. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by period jitter parameter.

- 6. Measurements done with LVTTL 3.3 V, 8 mA I/O drive strength and high slew rate. VCC/VCCPLL = 1.425 V, VQ/PQ/TQ type of packages, 20 pF load.

- 7. Switching I/Os are placed outside of the PLL bank.

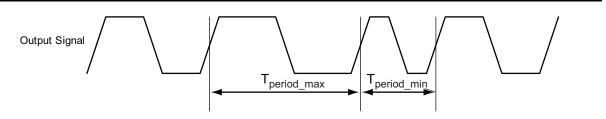

Note: Peak-to-peak jitter measurements are defined by  $T_{peak-to-peak} = T_{period\_max} - T_{period\_min-to-peak}$

Figure 2-42 • Peak-to-Peak Jitter Definition

2-124 Revision 5

Pin Descriptions and Packaging

#### VCOMPLA/B/C/D/E/F PLL Ground

Ground to analog PLL power supplies. When the PLLs are not used, the Microsemi Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground.

- There is one VCOMPLF pin on A3P250 and A3P1000 devices.

- There are six VCOMPL pins (PLL ground) on A3PE600L and A3PE3000L devices.

#### **VJTAG**

### JTAG Supply Voltage

Military ProASIC3/EL devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned for use, the VJTAG pin together with the TRST pin could be tied to GND. It should be noted that VCC is required to be powered for JTAG operation; VJTAG alone is insufficient. If a device is in a JTAG chain of interconnected boards, the board containing the device can be powered down, provided both VJTAG and VCC to the part remain powered; otherwise, JTAG signals will not be able to transition the device, even in bypass mode.

Microsemi recommends that VPUMP and VJTAG power supplies be kept separate with independent filtering capacitors rather than supplying them from a common rail.

#### **VPUMP**

### **Programming Supply Voltage**

A3P250 and A3P1000 devices support single-voltage ISP of the configuration flash and FlashROM. For programming, VPUMP should be 3.3 V nominal. During normal device operation, VPUMP can be left floating or can be tied (pulled up) to any voltage between 0 V and the VPUMP maximum. Programming power supply voltage (VPUMP) range is listed in Table 2-2 on page 2-2.

When the VPUMP pin is tied to ground, it will shut off the charge pump circuitry, resulting in no sources of oscillation from the charge pump circuitry.

For proper programming, 0.01  $\mu$ F and 0.33  $\mu$ F capacitors (both rated at 16 V) are to be connected in parallel across VPUMP and GND, and positioned as close to the FPGA pins as possible.

Microsemi recommends that VPUMP and VJTAG power supplies be kept separate with independent filtering capacitors rather than supplying them from a common rail.

### **User-Defined Supply Pins**

#### VRFF

### I/O Voltage Reference

Reference voltage for I/O minibanks in A3PE600L and A3PE3000L devices. VREF pins are configured by the user from regular I/Os, and any I/O in a bank, except JTAG I/Os, can be designated the voltage reference I/O. Only certain I/O standards require a voltage reference—HSTL (I) and (II), SSTL2 (I) and (II), SSTL3 (I) and GTL/GTL+. One VREF pin can support the number of I/Os available in its minibank.

### **User Pins**

#### I/C

### **User Input/Output**

The I/O pin functions as an input, output, tristate, or bidirectional buffer. Input and output signal levels are compatible with the I/O standard selected.

During programming, I/Os become tristated and weakly pulled up to VCCI. With VCCI, VMV, and VCC supplies continuously powered up, when the device transitions from programming to operating mode, the I/Os are instantly configured to the desired user configuration.

Unused I/Os are configured as follows:

- · Output buffer is disabled (with tristate value of high impedance)

- Input buffer is disabled (with tristate value of high impedance)

- · Weak pull-up is programmed

3-2 Revision 5

| FG144      |                  |            | FG144            | FG144      |                  |  |

|------------|------------------|------------|------------------|------------|------------------|--|

| Pin Number | A3P1000 Function | Pin Number | A3P1000 Function | Pin Number | A3P1000 Function |  |

| A1         | GNDQ             | D1         | IO213PDB3        | G1         | GFA1/IO207PPB3   |  |

| A2         | VMV0             | D2         | IO213NDB3        | G2         | GND              |  |

| A3         | GAB0/IO02RSB0    | D3         | IO223NDB3        | G3         | VCCPLF           |  |

| A4         | GAB1/IO03RSB0    | D4         | GAA2/IO225PPB3   | G4         | GFA0/IO207NPB3   |  |

| A5         | IO10RSB0         | D5         | GAC0/IO04RSB0    | G5         | GND              |  |

| A6         | GND              | D6         | GAC1/IO05RSB0    | G6         | GND              |  |

| A7         | IO44RSB0         | D7         | GBC0/IO72RSB0    | G7         | GND              |  |

| A8         | VCC              | D8         | GBC1/IO73RSB0    | G8         | GDC1/IO111PPB1   |  |

| A9         | IO69RSB0         | D9         | GBB2/IO79PDB1    | G9         | IO96NDB1         |  |

| A10        | GBA0/IO76RSB0    | D10        | IO79NDB1         | G10        | GCC2/IO96PDB1    |  |

| A11        | GBA1/IO77RSB0    | D11        | IO80NPB1         | G11        | IO95NDB1         |  |

| A12        | GNDQ             | D12        | GCB1/IO92PPB1    | G12        | GCB2/IO95PDB1    |  |

| B1         | GAB2/IO224PDB3   | E1         | VCC              | H1         | ∨cc              |  |

| B2         | GND              | E2         | GFC0/IO209NDB3   | H2         | GFB2/IO205PDB3   |  |

| В3         | GAA0/IO00RSB0    | E3         | GFC1/IO209PDB3   | Н3         | GFC2/IO204PSB3   |  |

| B4         | GAA1/IO01RSB0    | E4         | VCCIB3           | H4         | GEC1/IO190PDB3   |  |

| B5         | IO13RSB0         | E5         | IO225NPB3        | H5         | VCC              |  |

| В6         | IO26RSB0         | E6         | VCCIB0           | H6         | IO105PDB1        |  |

| В7         | IO35RSB0         | E7         | VCCIB0           | H7         | IO105NDB1        |  |

| B8         | IO60RSB0         | E8         | GCC1/IO91PDB1    | H8         | GDB2/IO115RSB2   |  |

| В9         | GBB0/IO74RSB0    | E9         | VCCIB1           | H9         | GDC0/IO111NPB1   |  |

| B10        | GBB1/IO75RSB0    | E10        | VCC              | H10        | VCCIB1           |  |

| B11        | GND              | E11        | GCA0/IO93NDB1    | H11        | IO101PSB1        |  |

| B12        | VMV1             | E12        | IO94NDB1         | H12        | VCC              |  |

| C1         | IO224NDB3        | F1         | GFB0/IO208NPB3   | J1         | GEB1/IO189PDB3   |  |

| C2         | GFA2/IO206PPB3   | F2         | VCOMPLF          | J2         | IO205NDB3        |  |

| C3         | GAC2/IO223PDB3   | F3         | GFB1/IO208PPB3   | J3         | VCCIB3           |  |

| C4         | VCC              | F4         | IO206NPB3        | J4         | GEC0/IO190NDB3   |  |

| C5         | IO16RSB0         | F5         | GND              | J5         | IO160RSB2        |  |

| C6         | IO29RSB0         | F6         | GND              | J6         | IO157RSB2        |  |

| C7         | IO32RSB0         | F7         | GND              | J7         | VCC              |  |

| C8         | IO63RSB0         | F8         | GCC0/IO91NDB1    | J8         | TCK              |  |

| C9         | IO66RSB0         | F9         | GCB0/IO92NPB1    | J9         | GDA2/IO114RSB2   |  |

| C10        | GBA2/IO78PDB1    | F10        | GND              | J10        | TDO              |  |

| C11        | IO78NDB1         | F11        | GCA1/IO93PDB1    | J11        | GDA1/IO113PDB1   |  |

| C12        | GBC2/IO80PPB1    | F12        | GCA2/IO94PDB1    | J12        | GDB1/IO112PDB1   |  |

Revision 5 4-7

Package Pin Assignments

| FG256      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | A3P1000 Function |  |  |  |

| A1         | GND              |  |  |  |

| A2         | GAA0/IO00RSB0    |  |  |  |

| A3         | GAA1/IO01RSB0    |  |  |  |

| A4         | GAB0/IO02RSB0    |  |  |  |

| A5         | IO16RSB0         |  |  |  |

| A6         | IO22RSB0         |  |  |  |

| A7         | IO28RSB0         |  |  |  |

| A8         | IO35RSB0         |  |  |  |

| A9         | IO45RSB0         |  |  |  |

| A10        | IO50RSB0         |  |  |  |

| A11        | IO55RSB0         |  |  |  |

| A12        | IO61RSB0         |  |  |  |

| A13        | GBB1/IO75RSB0    |  |  |  |

| A14        | GBA0/IO76RSB0    |  |  |  |

| A15        | GBA1/IO77RSB0    |  |  |  |

| A16        | GND              |  |  |  |

| B1         | GAB2/IO224PDB3   |  |  |  |

| B2         | GAA2/IO225PDB3   |  |  |  |

| В3         | GNDQ             |  |  |  |

| B4         | GAB1/IO03RSB0    |  |  |  |

| B5         | IO17RSB0         |  |  |  |

| B6         | IO21RSB0         |  |  |  |

| В7         | IO27RSB0         |  |  |  |

| B8         | IO34RSB0         |  |  |  |

| B9         | IO44RSB0         |  |  |  |

| B10        | IO51RSB0         |  |  |  |

| B11        | IO57RSB0         |  |  |  |

| B12        | GBC1/IO73RSB0    |  |  |  |

| B13        | GBB0/IO74RSB0    |  |  |  |

| B14        | IO71RSB0         |  |  |  |

| B15        | GBA2/IO78PDB1    |  |  |  |

| B16        | IO81PDB1         |  |  |  |

| C1         | IO224NDB3        |  |  |  |

| C2         | IO225NDB3        |  |  |  |

| C3         | VMV3             |  |  |  |

| C4         | IO11RSB0         |  |  |  |

| C5         | GAC0/IO04RSB0    |  |  |  |

| C6         | GAC1/IO05RSB0    |  |  |  |

|            |                  |  |  |  |

| FG256      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | A3P1000 Function |  |  |  |

| C7         | IO25RSB0         |  |  |  |

| C8         | IO36RSB0         |  |  |  |

| C9         | IO42RSB0         |  |  |  |

| C10        | IO49RSB0         |  |  |  |

| C11        | IO56RSB0         |  |  |  |

| C12        | GBC0/IO72RSB0    |  |  |  |

| C13        | IO62RSB0         |  |  |  |

| C14        | VMV0             |  |  |  |

| C15        | IO78NDB1         |  |  |  |

| C16        | IO81NDB1         |  |  |  |

| D1         | IO222NDB3        |  |  |  |

| D2         | IO222PDB3        |  |  |  |

| D3         | GAC2/IO223PDB3   |  |  |  |

| D4         | IO223NDB3        |  |  |  |

| D5         | GNDQ             |  |  |  |

| D6         | IO23RSB0         |  |  |  |

| D7         | IO29RSB0         |  |  |  |

| D8         | IO33RSB0         |  |  |  |

| D9         | IO46RSB0         |  |  |  |

| D10        | IO52RSB0         |  |  |  |

| D11        | IO60RSB0         |  |  |  |

| D12        | GNDQ             |  |  |  |

| D13        | IO80NDB1         |  |  |  |

| D14        | GBB2/IO79PDB1    |  |  |  |

| D15        | IO79NDB1         |  |  |  |

| D16        | IO82NSB1         |  |  |  |

| E1         | IO217PDB3        |  |  |  |

| E2         | IO218PDB3        |  |  |  |

| E3         | IO221NDB3        |  |  |  |

| E4         | IO221PDB3        |  |  |  |

| E5         | VMV0             |  |  |  |

| E6         | VCCIB0           |  |  |  |

| E7         | VCCIB0           |  |  |  |

| E8         | IO38RSB0         |  |  |  |

| E9         | IO47RSB0         |  |  |  |

| E10        | VCCIB0           |  |  |  |

| E11        | VCCIB0           |  |  |  |

| E12        | VMV1             |  |  |  |

| ·          |                  |  |  |  |

| FG256             |                  |  |  |  |

|-------------------|------------------|--|--|--|

| Pin Number        | A3P1000 Function |  |  |  |

| E13               | GBC2/IO80PDB1    |  |  |  |

| E14               | IO83PPB1         |  |  |  |

| E15               | IO86PPB1         |  |  |  |

| E16               | IO87PDB1         |  |  |  |

| F1                | IO217NDB3        |  |  |  |

| F2                | IO218NDB3        |  |  |  |

| F3                | IO216PDB3        |  |  |  |

| F4                | IO216NDB3        |  |  |  |

| F5                | VCCIB3           |  |  |  |

| F6                | GND              |  |  |  |

| F7                | VCC              |  |  |  |

| F8                | VCC              |  |  |  |

| F9                | VCC              |  |  |  |

| F10               | VCC              |  |  |  |

| F11               | GND              |  |  |  |

| F12               | VCCIB1           |  |  |  |

| F13               | IO83NPB1         |  |  |  |

| F14               | IO86NPB1         |  |  |  |

| F15               | IO90PPB1         |  |  |  |

| F16               | IO87NDB1         |  |  |  |

| G1                | IO210PSB3        |  |  |  |

| G2                | IO213NDB3        |  |  |  |

| G3                | IO213PDB3        |  |  |  |

| G4                | GFC1/IO209PPB3   |  |  |  |

| G5                | VCCIB3           |  |  |  |

| G6                | VCC              |  |  |  |

| G7                | GND              |  |  |  |

| G8                | GND              |  |  |  |

| G9                | GND              |  |  |  |

| G10               | GND              |  |  |  |

| G11               | VCC              |  |  |  |

| G12               | VCCIB1           |  |  |  |

| G13               | GCC1/IO91PPB1    |  |  |  |

| G14               | IO90NPB1         |  |  |  |

| G15               | IO88PDB1         |  |  |  |

| G16               | IO88NDB1         |  |  |  |

| H1                | GFB0/IO208NPB3   |  |  |  |

| H2 GFA0/IO207NDB3 |                  |  |  |  |

4-10 Revision 5

### Military ProASIC3/EL Low Power Flash FPGAs

|               | FG484            |               |  |  |

|---------------|------------------|---------------|--|--|

| Pin<br>Number | A3P1000 Function | Pin<br>Number |  |  |

| A1            | GND              | B14           |  |  |

| A2            | GND              | B15           |  |  |

| A3            | VCCIB0           | B16           |  |  |

| A4            | IO07RSB0         | B17           |  |  |

| A5            | IO09RSB0         | B18           |  |  |

| A6            | IO13RSB0         | B19           |  |  |

| A7            | IO18RSB0         | B20           |  |  |

| A8            | IO20RSB0         | B21           |  |  |

| A9            | IO26RSB0         | B22           |  |  |

| A10           | IO32RSB0         | C1            |  |  |

| A11           | IO40RSB0         | C2            |  |  |

| A12           | IO41RSB0         | C3            |  |  |

| A13           | IO53RSB0         | C4            |  |  |

| A14           | IO59RSB0         | C5            |  |  |

| A15           | IO64RSB0         | C6            |  |  |

| A16           | IO65RSB0         | C7            |  |  |

| A17           | IO67RSB0         | C8            |  |  |

| A18           | IO69RSB0         | C9            |  |  |

| A19           | NC               | C10           |  |  |

| A20           | VCCIB0           | C11           |  |  |

| A21           | GND              | C12           |  |  |

| A22           | GND              | C13           |  |  |

| B1            | GND              | C14           |  |  |

| B2            | VCCIB3           | C15           |  |  |

| В3            | NC               | C16           |  |  |

| B4            | IO06RSB0         | C17           |  |  |

| B5            | IO08RSB0         | C18           |  |  |

| В6            | IO12RSB0         | C19           |  |  |

| В7            | IO15RSB0         | C20           |  |  |

| B8            | IO19RSB0         | C21           |  |  |

| В9            | IO24RSB0         | C22           |  |  |

| B10           | IO31RSB0         | D1            |  |  |

| B11           | IO39RSB0         | D2            |  |  |

| B12           | IO48RSB0         | D3            |  |  |

| B13           | IO54RSB0         | D4            |  |  |

| FG484         |                  |  |  |  |

|---------------|------------------|--|--|--|

| Pin<br>Number | A3P1000 Function |  |  |  |

| B14           | IO58RSB0         |  |  |  |

| B15           | IO63RSB0         |  |  |  |

| B16           | IO66RSB0         |  |  |  |

| B17           | IO68RSB0         |  |  |  |

| B18           | IO70RSB0         |  |  |  |

| B19           | NC               |  |  |  |

| B20           | NC               |  |  |  |

| B21           | VCCIB1           |  |  |  |

| B22           | GND              |  |  |  |

| C1            | VCCIB3           |  |  |  |

| C2            | IO220PDB3        |  |  |  |

| C3            | NC               |  |  |  |

| C4            | NC               |  |  |  |

| C5            | GND              |  |  |  |

| C6            | IO10RSB0         |  |  |  |

| C7            | IO14RSB0         |  |  |  |

| C8            | VCC              |  |  |  |

| C9            | VCC              |  |  |  |

| C10           | IO30RSB0         |  |  |  |

| C11           | IO37RSB0         |  |  |  |

| C12           | IO43RSB0         |  |  |  |

| C13           | NC               |  |  |  |

| C14           | VCC              |  |  |  |

| C15           | VCC              |  |  |  |

| C16           | NC               |  |  |  |

| C17           | NC               |  |  |  |

| C18           | GND              |  |  |  |

| C19           | NC               |  |  |  |

| C20           | NC               |  |  |  |

| C21           | NC               |  |  |  |

| C22           | VCCIB1           |  |  |  |

| D1            | IO219PDB3        |  |  |  |

| D2            | IO220NDB3        |  |  |  |

| D3            | NC               |  |  |  |

| D4            | GND              |  |  |  |

| FG484  |                  |  |

|--------|------------------|--|

| Pin    |                  |  |

| Number | A3P1000 Function |  |

| D5     | GAA0/IO00RSB0    |  |

| D6     | GAA1/IO01RSB0    |  |

| D7     | GAB0/IO02RSB0    |  |

| D8     | IO16RSB0         |  |

| D9     | IO22RSB0         |  |

| D10    | IO28RSB0         |  |

| D11    | IO35RSB0         |  |

| D12    | IO45RSB0         |  |

| D13    | IO50RSB0         |  |

| D14    | IO55RSB0         |  |

| D15    | IO61RSB0         |  |

| D16    | GBB1/IO75RSB0    |  |

| D17    | GBA0/IO76RSB0    |  |

| D18    | GBA1/IO77RSB0    |  |

| D19    | GND              |  |

| D20    | NC               |  |

| D21    | NC               |  |

| D22    | NC               |  |

| E1     | IO219NDB3        |  |

| E2     | NC               |  |

| E3     | GND              |  |

| E4     | GAB2/IO224PDB3   |  |

| E5     | GAA2/IO225PDB3   |  |

| E6     | GNDQ             |  |

| E7     | GAB1/IO03RSB0    |  |

| E8     | IO17RSB0         |  |

| E9     | IO21RSB0         |  |

| E10    | IO27RSB0         |  |

| E11    | IO34RSB0         |  |

| E12    | IO44RSB0         |  |

| E13    | IO51RSB0         |  |

| E14    | IO57RSB0         |  |

| E15    | GBC1/IO73RSB0    |  |

| E16    | GBB0/IO74RSB0    |  |

| E17    | IO71RSB0         |  |

Revision 5 4-19

### Package Pin Assignments

| FG484         |                     |  |

|---------------|---------------------|--|

| Pin<br>Number | A3PE3000L Function  |  |

| V3            | GND                 |  |

| V4            | GEA1/IO234PDB6V0    |  |

| V5            | GEA0/IO234NDB6V0    |  |

| V6            | GNDQ                |  |

| V7            | GEC2/IO231PDB5V4    |  |

| V8            | IO222NPB5V3         |  |

| V9            | IO204NDB5V1         |  |

| V10           | IO204PDB5V1         |  |

| V11           | IO195NDB5V0         |  |

| V12           | IO195PDB5V0         |  |

| V13           | IO178NDB4V3         |  |

| V14           | IO178PDB4V3         |  |

| V15           | IO155NDB4V0         |  |

| V16           | GDB2/IO155PDB4V0    |  |

| V17           | TDI                 |  |

| V18           | GNDQ                |  |

| V19           | TDO                 |  |

| V20           | GND                 |  |

| V21           | IO146PDB3V4         |  |

| V22           | IO142NDB3V3         |  |

| W1            | IO239NDB6V0         |  |

| W2            | IO237PDB6V0         |  |

| W3            | IO230PSB5V4         |  |

| W4            | GND                 |  |

| W5            | IO232NDB5V4         |  |

| W6            | FF/GEB2/IO232PDB5V4 |  |

| W7            | IO231NDB5V4         |  |

| W8            | IO214NDB5V2         |  |

| W9            | IO214PDB5V2         |  |

| W10           | IO200NDB5V0         |  |

| W11           | IO192NDB4V4         |  |

| W12           | IO184NDB4V3         |  |

| W13           | IO184PDB4V3         |  |

| W14           | IO156NDB4V0         |  |

| W15           | GDC2/IO156PDB4V0    |  |

| FG484  |                    |  |

|--------|--------------------|--|

| Pin    |                    |  |

| Number | A3PE3000L Function |  |

| W16    | IO154NDB4V0        |  |

| W17    | GDA2/IO154PDB4V0   |  |

| W18    | TMS                |  |

| W19    | GND                |  |

| W20    | IO150NDB3V4        |  |

| W21    | IO146NDB3V4        |  |

| W22    | IO148PPB3V4        |  |

| Y1     | VCCIB6             |  |

| Y2     | IO237NDB6V0        |  |

| Y3     | IO228NDB5V4        |  |

| Y4     | IO224NDB5V3        |  |

| Y5     | GND                |  |

| Y6     | IO220NDB5V3        |  |

| Y7     | IO220PDB5V3        |  |

| Y8     | VCC                |  |

| Y9     | VCC                |  |

| Y10    | IO200PDB5V0        |  |

| Y11    | IO192PDB4V4        |  |

| Y12    | IO188NPB4V4        |  |

| Y13    | IO187PSB4V4        |  |

| Y14    | VCC                |  |

| Y15    | VCC                |  |

| Y16    | IO164NDB4V1        |  |

| Y17    | IO164PDB4V1        |  |

| Y18    | GND                |  |

| Y19    | IO158PPB4V0        |  |

| Y20    | IO150PDB3V4        |  |

| Y21    | IO148NPB3V4        |  |

| Y22    | VCCIB3             |  |

4-28 Revision 5