Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                               |

|--------------------------------|-------------------------------------------------------------------------------|

| Product Status                 | Active                                                                        |

| Number of LABs/CLBs            | -                                                                             |

| Number of Logic Elements/Cells | -                                                                             |

| Total RAM Bits                 | 516096                                                                        |

| Number of I/O                  | 341                                                                           |

| Number of Gates                | 300000                                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                                               |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | -55°C ~ 125°C (TJ)                                                            |

| Package / Case                 | 484-BGA                                                                       |

| Supplier Device Package        | 484-FPBGA (23x23)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3pe3000l-1fg484m |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The CCC block has these key features:

- Wide input frequency range ( $f_{IN CCC}$ ) = 1.5 MHz up to 250 MHz

- Output frequency range (f<sub>OUT CCC</sub>) = 0.75 MHz up to 250 MHz

- 2 programmable delay types for clock skew minimization

- Clock frequency synthesis

Additional CCC specifications:

- Internal phase shift = 0°, 90°, 180°, and 270°. Output phase shift depends on the output divider configuration.

- Output duty cycle = 50% ± 1.5% or better

- Low output jitter: worst case < 2.5% × clock period peak-to-peak period jitter when single global network used

- Maximum acquisition time is 300 µs

- Exceptional tolerance to input period jitter—allowable input jitter is up to 1.5 ns

- Four precise phases; maximum misalignment between adjacent phases of 40 ps  $\times$  250 MHz /  $\rm ^{f}OUT$  ccc

#### **Global Clocking**

Military ProASIC3/EL devices have extensive support for multiple clocking domains. In addition to the CCC and PLL support described above, there is a comprehensive global clock distribution network.

Each VersaTile input and output port has access to nine VersaNets: six chip (main) and three quadrant global networks. The VersaNets can be driven by the CCC or directly accessed from the core via multiplexers (MUXes). The VersaNets can be used to distribute low-skew clock signals or for rapid distribution of high-fanout nets.

#### I/Os with Advanced I/O Standards

The military ProASIC3/EL family of FPGAs features a flexible I/O structure, supporting a range of voltages (1.5 V, 1.8 V, 2.5 V, and 3.3 V). In addition, 1.2 V I/O operation is supported for military ProASIC3EL devices. Military ProASIC3/EL FPGAs support different I/O standards, including single-ended, differential, and voltage-referenced (military ProASIC3EL). The I/Os are organized into banks, with two, four, or eight (military ProASIC3EL only) banks per device. The configuration of these banks determines the I/O standards supported. For military ProASIC3EL, each I/O bank is subdivided into V<sub>REF</sub> minibanks, which are used by voltage-referenced I/Os. V<sub>REF</sub> minibanks contain 8 to 18 I/Os. All the I/Os in a given minibank share a common V<sub>REF</sub> line. Therefore, if any I/O in a given V<sub>REF</sub> minibank is configured as a V<sub>REF</sub> pin, the remaining I/Os in that minibank will be able to use that reference voltage.

Each I/O module contains several input, output, and enable registers. These registers allow the implementation of the following:

- Single-data-rate applications (e.g., PCI 66 MHz, bidirectional SSTL 2 and 3, Class I and II)

- Double-data-Rate applications (e.g., DDR LVDS, B-LVDS, and M-LVDS I/Os for point-to-point communications, and DDR 200 MHz SRAM using bidirectional HSTL Class II).

Military ProASIC3EL banks support LVPECL, LVDS, B-LVDS, and M-LVDS. B-LVDS and M-LVDS can support up to 20 loads.

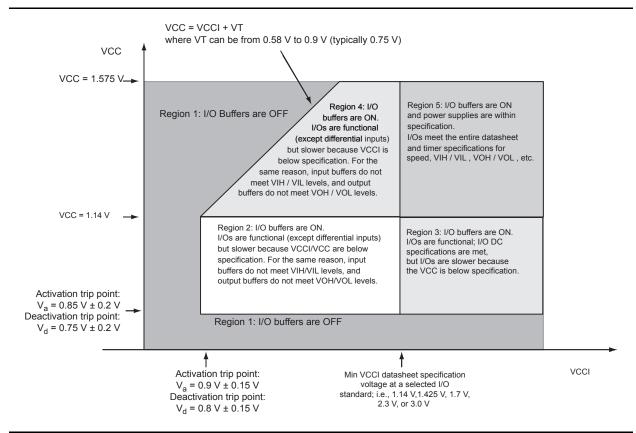

Figure 2-2 • Device Operating at 1.2 V Core Voltage – I/O State as a Function of VCCI and VCC Voltage Levels; Only A3PE600L and A3PE3000L Devices Operate at 1.2 V Core Voltage

### **Thermal Characteristics**

#### Introduction

The temperature variable in the Designer software refers to the junction temperature, not the ambient temperature. This is an important distinction because dynamic and static power consumption cause the chip junction temperature to be higher than the ambient temperature.

EQ 1 can be used to calculate junction temperature.

$T_J$  = Junction Temperature =  $\Delta T + T_A$

EQ 1

where:

T<sub>A</sub> = Ambient Temperature

$\Delta T$  = Temperature gradient between junction (silicon) and ambient  $\Delta T$  =  $\theta_{ia}$  \* P

$\theta_{ja}$  = Junction-to-ambient of the package.  $\theta_{ja}$  numbers are located in Table 2-5.

P = Power dissipation

#### Package Thermal Characteristics

The device junction-to-case thermal resistivity is  $\theta_{jc}$  and the junction-to-ambient air thermal resistivity is  $\theta_{ja}$ . The thermal characteristics for  $\theta_{ja}$  are shown for two air flow rates. The recommended maximum junction temperature is 125°C. EQ 2 shows a sample calculation of the recommended maximum power dissipation allowed for a 484-pin FBGA package at military temperature and in still air.

Maximum Power Allowed =

$$\frac{\text{Max. junction temp. (°C)} - \text{Max. ambient temp. (°C)}}{\theta_{ja}(°C/W)} = \frac{125°C - 70°C}{20.6°C/W} = 2.670$$

### Power Calculation Methodology

This section describes a simplified method to estimate power consumption of an application. For more accurate and detailed power estimations, use the SmartPower tool in the Libero SoC software.

The power calculation methodology described below uses the following variables:

- The number of PLLs as well as the number and the frequency of each output clock generated

- The number of combinatorial and sequential cells used in the design

- The internal clock frequencies

- The number and the standard of I/O pins used in the design

- The number of RAM blocks used in the design

- Toggle rates of I/O pins as well as VersaTiles—guidelines are provided in Table 2-23 on page 2-17.

- Enable rates of output buffers—guidelines are provided for typical applications in Table 2-24 on page 2-17.

- Read rate and write rate to the memory—guidelines are provided for typical applications in Table 2-24 on page 2-17. The calculation should be repeated for each clock domain defined in the design.

#### Methodology

#### Total Power Consumption—P<sub>TOTAL</sub>

$P_{TOTAL} = P_{STAT} + P_{DYN}$

P<sub>STAT</sub> is the total static power consumption.

P<sub>DYN</sub> is the total dynamic power consumption.

#### Total Static Power Consumption—P<sub>STAT</sub>

P<sub>STAT</sub> = (PDC0 or PDC1 or PDC2 or PDC3) + N<sub>BANKS</sub>\* P<sub>DC5</sub> + N<sub>INPUTS</sub>\* PDC6 + N<sub>OUTPUTS</sub>\* PDC7

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

N<sub>BANKS</sub> is the number of I/O banks powered in the design.

#### Total Dynamic Power Consumption—P<sub>DYN</sub>

P<sub>DYN</sub> = P<sub>CLOCK</sub> + P<sub>S-CELL</sub> + P<sub>C-CELL</sub> + P<sub>NET</sub> + P<sub>INPUTS</sub> + P<sub>OUTPUTS</sub> + P<sub>MEMORY</sub> + P<sub>PLL</sub>

#### Global Clock Contribution—P<sub>CLOCK</sub>

$P_{CLOCK} = (PAC1 + N_{SPINE} * PAC2 + N_{ROW} * PAC3 + N_{S-CELL} * PAC4) * F_{CLK}$

$N_{\mbox{\rm SPINE}}$  is the number of global spines used in the user design—guidelines are provided in Table 2-23 on page 2-17.

$N_{ROW}$  is the number of VersaTile rows used in the design—guidelines are provided in Table 2-23 on page 2-17.

F<sub>CLK</sub> is the global clock signal frequency.

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

PAC1, PAC2, PAC3, and PAC4 are device-dependent.

#### Sequential Cells Contribution—P<sub>S-CELL</sub>

$P_{S-CELL} = N_{S-CELL} * (PAC5 + \alpha_1 / 2 * PAC6) * F_{CLK}$

$N_{S\text{-}CELL}$  is the number of VersaTiles used as sequential modules in the design. When a multi-tile sequential cell is used, it should be accounted for as 1.

$\alpha_{1}$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-23 on page 2-17.

F<sub>CLK</sub> is the global clock signal frequency.

Military ProASIC3/EL DC and Switching Characteristics

# **User I/O Characteristics**

## **Timing Model**

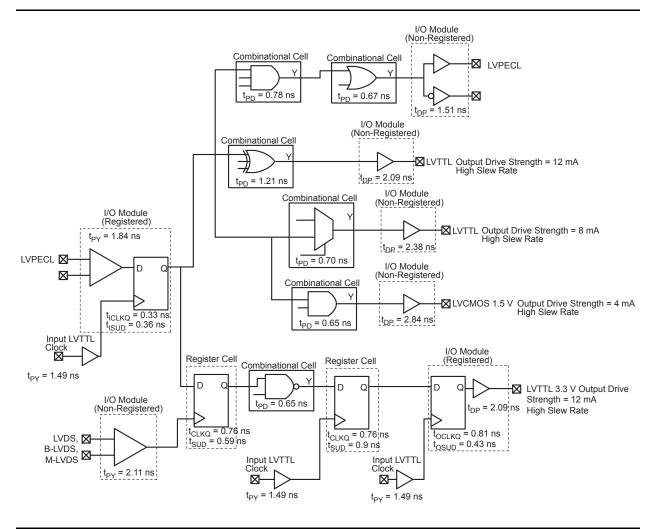

Figure 2-3 • Timing Model Operating Conditions: –1 Speed, Military Temperature Range (T<sub>J</sub> = 125°C), Worst-Case VCC = 1.14 V (example for A3PE3000L and A3PE600L)

Military ProASIC3/EL DC and Switching Characteristics

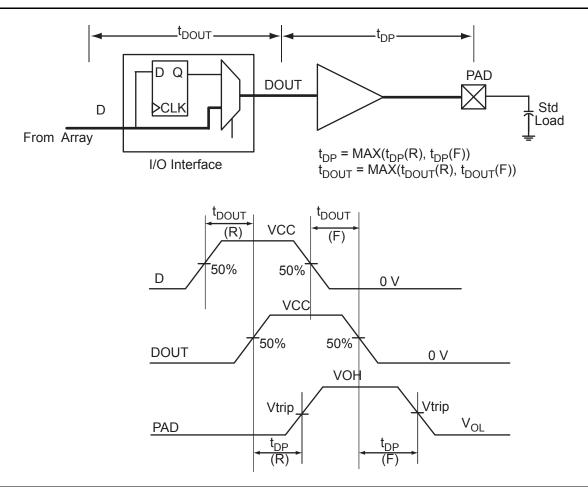

Figure 2-5 • Output Buffer Model and Delays (example)

#### 1.5 V Core Voltage

# Table 2-32 • Summary of I/O Timing Characteristics—Software Default Settings -1 Speed Grade, Military-Case Conditions: T<sub>J</sub> = 125°C, VCC = 1.425 V, Worst Case VCCI Applicable to Pro I/Os for A3PE600L and A3PE3000L Only

| -                                       |                     | -                                                                    |           | 1                                 |                                | 1                      | 1                    | 1                     | 1                    | 1                     |                        |                      |                      |                      | 1                    | 1                     |                       |

|-----------------------------------------|---------------------|----------------------------------------------------------------------|-----------|-----------------------------------|--------------------------------|------------------------|----------------------|-----------------------|----------------------|-----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|

| Standard                                | Drive Strength (mA) | Equivalent Software<br>Default Drive Strength<br>Option <sup>1</sup> | Slew Rate | Capacitive Load (pF) <sup>2</sup> | External Resistor ( $\Omega$ ) | t <sub>bour</sub> (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>PY</sub> (ns) | t <sub>PYS</sub> (ns) | t <sub>EOUT</sub> (ns) | t <sub>ZL</sub> (ns) | t <sub>ZH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | t <sub>ZLS</sub> (ns) | t <sub>ZHS</sub> (ns) |

| 3.3 V LVTTL /<br>3.3 V LVCMOS           | 12 mA               | 12 mA                                                                | High      | 5                                 | _                              | 0.52                   | 1.97                 | 0.03                  | 1.23                 |                       | 0.34                   |                      |                      | 2.63                 | 2.89                 | 3.23                  | 2.71                  |

| 3.3 V LVCOMS<br>Wide Range <sup>3</sup> | 100 µA              | 12 mA                                                                | High      | 5                                 | _                              | 0.52                   | 2.89                 | 0.03                  | 1.61                 | 2.44                  | 0.34                   | 2.88                 | 2.12                 | 3.89                 | 4.25                 | 4.12                  | 3.36                  |

| 2.5 V LVCMOS                            | 12 mA               | 12 mA                                                                | High      | 5                                 | -                              | 0.52                   | 2.01                 | 0.03                  | 1.49                 | 1.93                  | 0.34                   | 2.02                 | 1.65                 | 2.71                 | 2.78                 | 3.27                  | 2.89                  |

| 1.8 V LVCMOS                            | 12 mA               | 12 mA                                                                | High      | 5                                 | -                              | 0.52                   | 2.24                 | 0.03                  | 1.44                 | 2.14                  | 0.34                   | 2.26                 | 1.84                 | 3.02                 | 3.41                 | 3.51                  | 3.08                  |

| 1.5 V LVCMOS                            | 12 mA               | 12 mA                                                                | High      | 5                                 | -                              | 0.52                   | 2.60                 | 0.03                  | 1.60                 | 2.35                  | 0.34                   | 2.62                 | 2.14                 | 3.21                 | 3.52                 | 3.87                  | 3.39                  |

| 3.3 V PCI                               | Per PCI<br>spec     | _                                                                    | High      | 10                                | 25 <sup>4</sup>                | 0.52                   | 2.25                 | 0.03                  | 2.03                 | 2.88                  | 0.34                   | 2.27                 | 1.58                 | 2.64                 | 2.89                 | 3.52                  | 2.83                  |

| 3.3 V PCI-X                             | Per PCI-X<br>spec   | _                                                                    | High      | 10                                | 25 <sup>4</sup>                | 0.52                   | 2.25                 | 0.03                  | 2.03                 | 2.88                  | 0.34                   | 2.27                 | 1.58                 | 2.64                 | 2.89                 | 3.52                  | 2.83                  |

| 3.3 V GTL                               | 20 mA <sup>5</sup>  | 20 mA <sup>5</sup>                                                   | High      | 10                                | 25                             | 0.52                   | 1.68                 | 0.03                  | 1.79                 | -                     | 0.34                   | 1.58                 | 1.68                 | -                    | -                    | 2.83                  | 2.92                  |

| 2.5 V GTL                               | 20 mA <sup>5</sup>  | 20 mA <sup>5</sup>                                                   | High      | 10                                | 25                             | 0.52                   | 1.72                 | 0.03                  | 1.73                 | Ι                     | 0.34                   | 1.69                 | 1.72                 | -                    | -                    | 2.93                  | 2.97                  |

| 3.3 V GTL+                              | 35 mA               | 35 mA                                                                | High      | 10                                | 25                             | 0.52                   | 1.66                 | 0.03                  | 1.79                 | -                     | 0.34                   | 1.63                 | 1.66                 | -                    | -                    | 2.88                  | 2.90                  |

| 2.5 V GTL+                              | 33 mA               | 33 mA                                                                | High      | 10                                | 25                             | 0.52                   | 1.75                 | 0.03                  | 1.73                 | -                     | 0.34                   | 1.76                 | 1.69                 | -                    | -                    | 3.00                  | 2.94                  |

| HSTL (I)                                | 8 mA                | 8 mA                                                                 | High      | 20                                | 25                             | 0.52                   | 2.57                 | 0.03                  | 2.14                 | Ι                     | 0.34                   | 2.59                 | 2.55                 | -                    |                      | 3.84                  | 3.79                  |

| HSTL (II)                               | 15 mA <sup>5</sup>  | 15 mA <sup>5</sup>                                                   | High      | 20                                | 50                             | 0.52                   | 2.44                 | 0.03                  | 2.14                 | -                     | 0.34                   | 2.46                 | 2.19                 | -                    | -                    | 3.71                  | 3.43                  |

| SSTL2 (I)                               | 15 mA               | 15 mA                                                                | High      | 30                                | 25                             | 0.52                   | 1.68                 | 0.03                  | 1.58                 | -                     | 034                    | 1.69                 | 1.46                 | -                    | -                    | 1.69                  | 1.46                  |

| SSTL2 (II)                              | 18 mA               | 18 mA                                                                | High      | 30                                | 50                             | 0.52                   | 1.72                 | 0.03                  | 1.58                 | -                     | 0.34                   | 1.73                 | 1.39                 | -                    | -                    | 1.73                  | 1.39                  |

| SSTL3 (I)                               | 14 mA               | 14 mA                                                                | High      | 30                                | 25                             | 0.52                   | 1.83                 | 0.03                  | 1.51                 | -                     | 0.34                   | 1.84                 | 1.45                 | -                    | -                    | 1.84                  | 1.45                  |

| SSTL3 (II)                              | 21 mA               | 21 mA                                                                | High      | 30                                | 50                             | 0.52                   | 1.63                 | 0.03                  | 1.51                 | -                     | 0.34                   | 1.64                 | 1.31                 | -                    | -                    | 1.64                  | 1.31                  |

| LVDS                                    | 24 mA               | -                                                                    | High      | -                                 | -                              | 0.52                   | 1.48                 | 0.03                  | 1.86                 | -                     | -                      | -                    | -                    | -                    | -                    | -                     | -                     |

| LVPECL                                  | 24 mA               | -                                                                    | High      | -                                 | -                              | 0.52                   | 1.40                 | 0.03                  | 1.61                 | -                     | —                      | -                    | -                    | -                    | -                    | -                     | -                     |

| Notos:                                  |                     |                                                                      |           |                                   |                                |                        |                      |                       |                      |                       |                        |                      |                      |                      |                      |                       |                       |

Notes:

1. Note that 3.3 V LVCMOS wide range is applicable to 100 μA drive strength only. The configuration will not operate at the equivalent software default drive strength. These values are for normal ranges only.

2. Output delays provided in this table were extracted with an output load indicated in the Capacitive Load column. For a specific output load, refer to Designer software.

3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

4. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-14 on page 2-71 for connectivity. This resistor is not required during normal operation.

5. Output drive strength is below JEDEC specification.

6. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Military ProASIC3/EL DC and Switching Characteristics

#### 1.5 V DC Core Voltage

# Table 2-88 •1.8 V LVCMOS Low Slew<br/>Military-Case Conditions: TJ = 125°C, VCC = 1.425 V, Worst-Case VCCI = 1.7 V<br/>Applicable to Pro I/Os for A3PE600L and A3PE3000L Only

| Drive    | Speed |                   |                 |                  |                 |                  |                   |                 |                 |                 |                 |                  |                  |       |

|----------|-------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Strength | Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 2 mA     | Std.  | 0.61              | 9.02            | 0.04             | 1.69            | 2.52             | 0.40              | 9.17            | 7.57            | 2.61            | 1.01            | 10.63            | 9.04             | ns    |

|          | -1    | 0.52              | 7.68            | 0.03             | 1.44            | 2.14             | 0.34              | 7.80            | 6.44            | 2.22            | 0.86            | 9.04             | 7.69             | ns    |

| 4 mA     | Std.  | 0.61              | 7.41            | 0.04             | 1.69            | 2.52             | 0.40              | 7.52            | 6.36            | 3.07            | 2.56            | 8.99             | 7.83             | ns    |

|          | -1    | 0.52              | 6.30            | 0.03             | 1.44            | 2.14             | 0.34              | 6.40            | 5.41            | 2.62            | 2.18            | 7.64             | 6.66             | ns    |

| 6 mA     | Std.  | 0.61              | 6.26            | 0.04             | 1.69            | 2.52             | 0.40              | 6.35            | 5.53            | 3.38            | 3.14            | 7.82             | 7.00             | ns    |

|          | -1    | 0.52              | 5.33            | 0.03             | 1.44            | 2.14             | 0.34              | 5.40            | 4.71            | 2.88            | 2.67            | 6.65             | 5.95             | ns    |

| 8 mA     | Std.  | 0.61              | 5.88            | 0.04             | 1.69            | 2.52             | 0.40              | 5.96            | 5.37            | 3.45            | 3.30            | 7.42             | 6.83             | ns    |

|          | -1    | 0.52              | 5.00            | 0.03             | 1.44            | 2.14             | 0.34              | 5.07            | 4.57            | 2.94            | 2.81            | 6.32             | 5.81             | ns    |

| 12 mA    | Std.  | 0.61              | 5.76            | 0.04             | 1.69            | 2.52             | 0.40              | 5.85            | 5.38            | 3.55            | 3.88            | 7.31             | 6.84             | ns    |

|          | -1    | 0.52              | 4.90            | 0.03             | 1.44            | 2.14             | 0.34              | 4.97            | 4.57            | 3.02            | 3.30            | 6.22             | 5.82             | ns    |

| 16 mA    | Std.  | 0.61              | 5.76            | 0.04             | 1.69            | 2.52             | 0.40              | 5.85            | 5.38            | 3.55            | 3.88            | 7.31             | 6.84             | ns    |

|          | –1    | 0.52              | 4.90            | 0.03             | 1.44            | 2.14             | 0.34              | 4.97            | 4.57            | 3.02            | 3.30            | 6.22             | 5.82             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# Table 2-89 • 1.8 V LVCMOS High Slew<br/>Military-Case Conditions: TJ = 125°C, VCC = 1.425 V, Worst-Case VCCI = 1.7 V

Applicable to Pro I/Os for A3PE600L and A3PE300L Only

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>zL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.61              | 4.01            | 0.04             | 1.69            | 2.52             | 0.40              | 4.06            | 3.94            | 2.60            | 1.03            | 5.52             | 5.40             | ns    |

|                   | -1             | 0.52              | 3.41            | 0.03             | 1.44            | 2.14             | 0.34              | 3.45            | 3.35            | 2.21            | 0.88            | 4.70             | 4.60             | ns    |

| 4 mA              | Std.           | 0.61              | 3.22            | 0.04             | 1.69            | 2.52             | 0.40              | 3.26            | 2.89            | 3.07            | 2.65            | 4.72             | 4.36             | ns    |

|                   | -1             | 0.52              | 2.74            | 0.03             | 1.44            | 2.14             | 0.34              | 2.77            | 2.46            | 2.61            | 2.26            | 4.02             | 3.71             | ns    |

| 6 mA              | Std.           | 0.61              | 2.74            | 0.04             | 1.69            | 2.52             | 0.40              | 2.77            | 2.38            | 3.38            | 3.23            | 4.23             | 3.84             | ns    |

|                   | -1             | 0.52              | 2.33            | 0.03             | 1.44            | 2.14             | 0.34              | 2.36            | 2.02            | 2.88            | 2.75            | 3.60             | 3.27             | ns    |

| 8 mA              | Std.           | 0.61              | 2.65            | 0.04             | 1.69            | 2.52             | 0.40              | 2.68            | 2.28            | 3.45            | 3.40            | 4.14             | 3.75             | ns    |

|                   | -1             | 0.52              | 2.26            | 0.03             | 1.44            | 2.14             | 0.34              | 2.28            | 1.94            | 2.93            | 2.89            | 3.52             | 3.19             | ns    |

| 12 mA             | Std.           | 0.61              | 2.64            | 0.04             | 1.69            | 2.52             | 0.40              | 2.66            | 2.16            | 3.55            | 4.01            | 4.13             | 3.63             | ns    |

|                   | -1             | 0.52              | 2.24            | 0.03             | 1.44            | 2.14             | 0.34              | 2.26            | 1.84            | 3.02            | 3.41            | 3.51             | 3.08             | ns    |

| 16 mA             | Std.           | 0.61              | 2.64            | 0.04             | 1.69            | 2.52             | 0.40              | 2.66            | 2.16            | 3.55            | 4.01            | 4.13             | 3.63             | ns    |

|                   | -1             | 0.52              | 2.24            | 0.03             | 1.44            | 2.14             | 034               | 2.26            | 1.84            | 3.02            | 3.41            | 3.51             | 3.08             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Military ProASIC3/EL DC and Switching Characteristics

#### 1.5 V DC Core Voltage

# Table 2-100 • 1.5 V LVCMOS Low SlewMilitary-Case Conditions: TJ = 125°C, VCC = 1.425 V, Worst-Case VCCI = 1.4 VApplicable to Pro I/Os for A3PE600L and A3PE3000L Only

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.61              | 9.39            | 0.04             | 1.88            | 2.77             | 0.40              | 9.54            | 7.77            | 3.22            | 2.47            | 11.00            | 9.24             | ns    |

|                   | –1             | 0.52              | 7.99            | 0.03             | 1.60            | 2.35             | 0.34              | 8.11            | 6.61            | 2.74            | 2.10            | 9.36             | 7.86             | ns    |

| 4 mA              | Std.           | 0.61              | 8.01            | 0.04             | 1.88            | 2.77             | 0.40              | 8.13            | 6.77            | 3.58            | 3.14            | 9.59             | 8.24             | ns    |

|                   | –1             | 0.52              | 6.81            | 0.03             | 1.60            | 2.35             | 0.34              | 6.91            | 5.76            | 3.05            | 2.67            | 8.16             | 7.01             | ns    |

| 6 mA              | Std.           | 0.61              | 7.51            | 0.04             | 1.88            | 2.77             | 0.40              | 7.62            | 6.59            | 3.66            | 3.32            | 9.09             | 8.05             | ns    |

|                   | –1             | 0.52              | 6.39            | 0.03             | 1.60            | 2.35             | 0.34              | 6.48            | 5.60            | 3.12            | 2.83            | 7.73             | 6.85             | ns    |

| 8 mA              | Std.           | 0.61              | 7.41            | 0.04             | 1.88            | 2.77             | 0.40              | 7.52            | 6.59            | 3.41            | 3.99            | 8.99             | 8.06             | ns    |

|                   | –1             | 0.52              | 6.30            | 0.03             | 1.60            | 2.35             | 0.34              | 6.40            | 5.61            | 2.90            | 3.40            | 7.64             | 6.85             | ns    |

| 12 mA             | Std.           | 0.61              | 7.41            | 0.04             | 1.88            | 2.77             | 0.40              | 7.52            | 6.59            | 3.41            | 3.99            | 8.99             | 8.06             | ns    |

|                   | –1             | 0.52              | 6.30            | 0.03             | 1.60            | 2.35             | 0.34              | 6.40            | 5.61            | 2.90            | 3.40            | 7.64             | 6.85             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-101 • 1.5 V LVCMOS High Slew

| Military-Case Conditions: T <sub>J</sub> = 125°C, VCC = 1.425 V, Worst-Case VCCI = 1.4 V | / |

|------------------------------------------------------------------------------------------|---|

| Applicable to Pro I/Os for A3PE600L and A3PE3000L Only                                   |   |

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.61              | 3.78            | 0.04             | 1.88            | 2.77             | 0.40              | 3.82            | 3.43            | 3.21'           | 2.58            | 5.29             | 4.89             | ns    |

|                   | –1             | 0.52              | 3.21            | 0.03             | 1.60            | 2.35             | 0.34              | 3.25            | 2.92            | 2.73            | 2.20            | 4.50             | 4.16             | ns    |

| 4 mA              | Std.           | 0.61              | 3.20            | 0.04             | 1.88            | 2.77             | 0.40              | 3.23            | 2.79            | 3.57            | 3.25            | 4.70             | 4.25             | ns    |

|                   | –1             | 0.52              | 2.72            | 0.03             | 1.60            | 2.35             | 0.34              | 2.75            | 2.37            | 3.04            | 2.77            | 4.00             | 3.62             | ns    |

| 6 mA              | Std.           | 0.61              | 3.09            | 0.04             | 1.88            | 2.77             | 0.40              | 3.12            | 2.67            | 3.65            | 3.44            | 4.59             | 4.13             | ns    |

|                   | –1             | 0.52              | 2.63            | 0.03             | 1.60            | 2.35             | 0.34              | 2.65            | 2.27            | 3.11            | 2.93            | 3.90             | 3.52             | ns    |

| 8 mA              | Std.           | 0.61              | 3.05            | 0.04             | 1.88            | 2.77             | 0.40              | 3.09            | 2.52            | 3.77            | 4.14            | 4.55             | 3.98             | ns    |

|                   | –1             | 0.52              | 2.60            | 0.03             | 1.60            | 2.35             | 0.34              | 2.62            | 2.14            | 3.21            | 3.52            | 3.87             | 3.39             | ns    |

| 12 mA             | Std.           | 0.61              | 3.05            | 0.04             | 1.88            | 2.77             | 0.40              | 3.09            | 2.52            | 3.77            | 4.14            | 4.55             | 3.98             | ns    |

|                   | –1             | 0.52              | 2.60            | 0.03             | 1.60            | 2.35             | 0.34              | 2.62            | 2.14            | 3.21            | 3.52            | 3.87             | 3.39             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Military ProASIC3/EL DC and Switching Characteristics

#### Table 2-147 • SSTL2 Class I

Military-Case Conditions:  $T_J = 125^{\circ}C$ ,  $V_{CC} = 1.425 V$ , Worst-Case VCCI = 2.3 V, VREF = 1.25 V Applicable to Pro I/Os for A3PE600L and A3PE3000L Only

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.61              | 1.98            | 0.04             | 1.85            | 0.40              | 1.99            | 1.71            | 1               | -               | 1.99             | 1.71             | ns    |

| –1             | 0.52              | 1.68            | 0.03             | 1.58            | 0.34              | 1.69            | 1.46            | _               | -               | 1.69             | 1.46             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

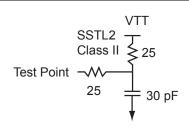

#### SSTL2 Class II

Stub-Speed Terminated Logic for 2.5 V memory bus standard (JESD8-9). Military ProASIC3E devices support Class II. This provides a differential amplifier input buffer and a push-pull output buffer.

| SSTL2 Class II    |           | VIL        | VIH        |           | VOL       | VOH       | $I_{OL}$ | I <sub>OH</sub> | I <sub>OSL</sub>        | I <sub>OSH</sub>        | ۱ <sub>L</sub> 1 | I <sub>IH</sub> <sup>2</sup> |

|-------------------|-----------|------------|------------|-----------|-----------|-----------|----------|-----------------|-------------------------|-------------------------|------------------|------------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V | mA       | mA              | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA⁴              | μA <sup>4</sup>              |

| 18 mA             | -0.3      | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.35      | VCCI-0.43 | 18       | 18              | 169                     | 124                     | 15               | 15                           |

Notes:

1.  $I_{IL}$  is the input leakage current per I/O pin over recommended operating conditions where -0.3 V < VIN < VIL.

2. II<sub>H</sub> is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at 100°C junction temperature and maximum voltage.

4. Currents are measured at 125°C junction temperature.

#### Figure 2-22 • AC Loading

#### Table 2-149 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.2    | VREF + 0.2     | 1.25                    | 1.25            | 1.25           | 30                     |

Note: \*Measuring point =  $V_{trip}$ . See Table 2-29 on page 2-25 for a complete table of trip points.

#### **Timing Characteristics**

Table 2-150 • SSTL2 Class II

Military-Case Conditions:  $T_J = 125^{\circ}C$ , Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V, VREF = 1.25 V Applicable to Pro I/Os for A3PE600L and A3PE3000L Only

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.80              | 2.15            | 0.05             | 2.09            | 0.52              | 2.18            | 1.75            | -               | -               | 2.18             | 1.75             | ns    |

| -1             | 0.68              | 1.83            | 0.05             | 1.78            | 0.44              | 1.86            | 1.49            | _               | -               | 1.86             | 1.49             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Timing Characteristics

#### 1.2 V DC Core Voltage

#### Table 2-162 • LVDS

#### Military-Case Conditions: $T_J = 125^{\circ}$ C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V Applicable to Pro I/Os for A3PE600L and A3PE3000L Only

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.80              | 1.87            | 0.05             | 2.48            | ns    |

| -1          | 0.68              | 1.59            | 0.05             | 2.11            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.5 V DC Core Voltage

#### Table 2-163 • LVDS

#### Military-Case Conditions: $T_J$ = 125°C, VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Pro I/Os for A3PE600L and A3PE3000L Only

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.61              | 1.75            | 0.04             | 2.18            | ns    |

| –1          | 0.52              | 1.48            | 0.03             | 1.86            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-164 • LVDS

#### Military-Case Conditions: $T_J = 125^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Advanced I/O Banks for A3P250 and A3P1000 Only

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.63              | 2.07            | 0.05             | 1.82            | ns    |

| -1          | 0.54              | 1.76            | 0.04             | 1.55            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-6 for derating values.

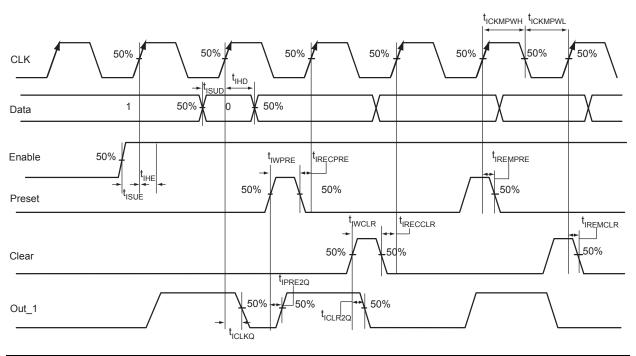

### Input Register

Military ProASIC3/EL DC and Switching Characteristics

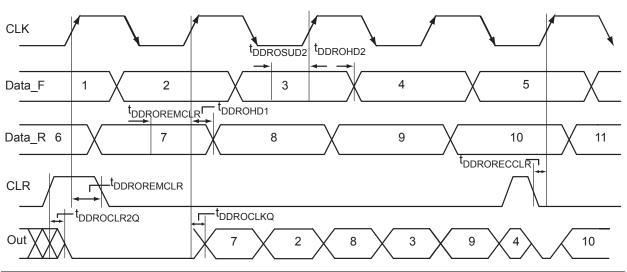

| Eiguro | 2-36 . | Output | סחח | Timina | Diagram   |  |

|--------|--------|--------|-----|--------|-----------|--|

| riyure | 2-30 - | Output | DDK | ruuuy  | Diagraili |  |

#### **Timing Characteristics**

# Table 2-186 • Output DDR Propagation DelaysMilitary-Case Conditions: TJ = 125°C, Worst-Case VCC = 1.14 V for A3PE600L and A3PE3000L

| Parameter               | Description                                           | -1   | Std. | Units |

|-------------------------|-------------------------------------------------------|------|------|-------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out of DDR for Output DDR                    | 0.97 | 1.14 | ns    |

| t <sub>DDRISUD1</sub>   | Data_F Data Setup for Output DDR                      | 0.52 | 0.62 | ns    |

| t <sub>DDROSUD2</sub>   | Data_R Data Setup for Output DDR                      | 0.52 | 0.62 | ns    |

| t <sub>DDROHD1</sub>    | Data_F Data Hold for Output DDR                       | 0.00 | 0.00 | ns    |

| t <sub>DDROHD2</sub>    | Data_R Data Hold for Output DDR                       | 0.00 | 0.00 | ns    |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out for Output DDR              | 1.11 | 1.30 | ns    |

| t <sub>DDROREMCLR</sub> | Asynchronous Clear Removal Time for Output DDR        | 0.00 | 0.00 | ns    |

| t <sub>DDRORECCLR</sub> | Asynchronous Clear Recovery Time for Output DDR       | 0.31 | 0.36 | ns    |

| t <sub>DDROWCLR1</sub>  | Asynchronous Clear Minimum Pulse Width for Output DDR | 0.19 | 0.22 | ns    |

| t <sub>DDROCKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Output DDR     | 0.31 | 0.36 | ns    |

| t <sub>DDROCKMPWL</sub> | Clock Minimum Pulse Width LOW for the Output DDR      | 0.28 | 0.32 | ns    |

| F <sub>DDROMAX</sub>    | Maximum Frequency for the Output DDR                  | 160  | 160  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Military ProASIC3/EL Low Power Flash FPGAs

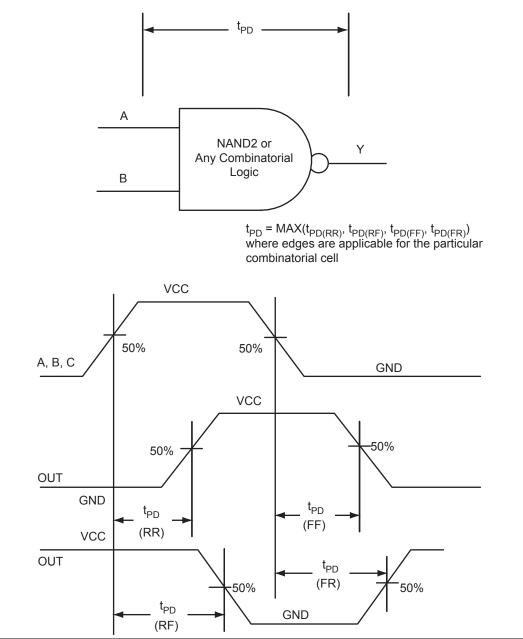

Figure 2-38 • Timing Model and Waveforms

Military ProASIC3/EL DC and Switching Characteristics

### **Global Tree Timing Characteristics**

Global clock delays include the central rib delay, the spine delay, and the row delay. Delays do not include I/O input buffer clock delays, as these are I/O standard–dependent, and the clock may be driven and conditioned internally by the CCC module. For more details on clock conditioning capabilities, refer to the "Clock Conditioning Circuits" section on page 2-123. Table 2-195 to Table 2-198 on page 2-121 present minimum and maximum global clock delays within each device. Minimum and maximum delays are measured with minimum and maximum loading.

#### Timing Characteristics

#### 1.2 V DC Core Voltage

#### Table 2-195 • A3PE600L Global Resource Military-Case Conditions: T<sub>J</sub> = 125°C, VCC = 1.14 V

|                      |                                           | -                 | -1                | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input LOW Delay for Global Clock          | 0.95              | 1.23              | 1.12              | 1.44              | ns    |

| t <sub>RCKH</sub>    | Input HIGH Delay for Global Clock         | 0.94              | 1.26              | 1.10              | 1.48              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width HIGH for Global Clock |                   |                   |                   |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width LOW for Global Clock  |                   |                   |                   |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.32              |                   | 0.38              | ns    |

| F <sub>RMAX</sub>    | Maximum Frequency for Global Clock        |                   |                   |                   |                   | MHz   |

| ' RMAX               |                                           |                   |                   |                   |                   |       |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-196 • A3PE3000L Global Resource Military-Case Conditions: T<sub>J</sub> = 125°C, VCC = 1.14 V

|                      |                                           | -                 | -1                | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input LOW Delay for Global Clock          | 1.81              | 2.09              | 2.13              | 2.42              | ns    |

| t <sub>RCKH</sub>    | Input HIGH Delay for Global Clock         | 1.80              | 2.13              | 2.12              | 2.45              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width HIGH for Global Clock |                   |                   |                   |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width LOW for Global Clock  |                   |                   |                   |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.32              |                   | 0.38              | ns    |

| F <sub>RMAX</sub>    | Maximum Frequency for Global Clock        |                   |                   |                   |                   | MHz   |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

<sup>2.</sup> Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

<sup>3.</sup> For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# **Clock Conditioning Circuits**

### **CCC Electrical Specifications**

#### **Timing Characteristics**

#### Table 2-201 • Military ProASIC3/EL CCC/PLL Specification

For Devices Operating at 1.2 V DC Core Voltage: Applicable to A3PE600L and A3PE3000L Only

| Parameter                                                           | Min.                                           | Тур.         | Max.         | Units         |

|---------------------------------------------------------------------|------------------------------------------------|--------------|--------------|---------------|

| Clock Conditioning Circuitry Input Frequency<br>f <sub>IN_CCC</sub> | 1.5                                            |              | 250          | MHz           |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT_CCC</sub>  | 0.75                                           |              | 250          | MHz           |

| Delay Increments in Programmable Delay Blocks <sup>1, 2.3</sup>     |                                                | 360          |              | ps            |

| Number of Programmable Values in Each Programmable Delay Block      |                                                |              | 32           |               |

| Serial Clock (SCLK) for Dynamic PLL <sup>4</sup>                    |                                                |              | 100          | MHz           |

| Input cycle-to-cycle jitter (peak magnitude)                        |                                                |              | 1            | ns            |

| Acquisition Time                                                    |                                                |              |              |               |

| LockControl = 0                                                     |                                                |              | 300          | μs            |

| LockControl = 1                                                     |                                                |              | 6.0          | ms            |

| Tracking Jitter <sup>5</sup>                                        |                                                |              |              |               |

| LockControl = 0                                                     |                                                |              | 25           | ns            |

| LockControl = 1                                                     |                                                |              | 1.5          | ns            |

| Output Duty Cycle                                                   | 48.5                                           |              | 51.5         | %             |

| Delay Range in Block: Programmable Delay 1 <sup>1,2</sup>           | 1.2                                            |              | 15.65        | ns            |

| Delay Range in Block: Programmable Delay 2 <sup>1,2</sup>           | 0.025                                          |              | 15.65        | ns            |

| Delay Range in Block: Fixed Delay <sup>1,2</sup>                    |                                                | 3.5          |              | ns            |

| CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub>          | Max. Peak-to-Peak Period Jitter <sup>6,7</sup> |              |              |               |

|                                                                     | $SSO \leq 2$                                   | $SSO \leq 4$ | $SSO \leq 8$ | $SSO \leq 16$ |

| 0.75 MHz to 50 MHz                                                  | 0.50%                                          | 0.60%        | 0.80%        | 1.60%         |

| 50 MHz to 160 MHz                                                   | 2.50%                                          | 4.00%        | 6.00%        | 12.00%        |

Notes:

1. This delay is a function of voltage and temperature. See Table 2-6 on page 2-6 for deratings.

2.  $T_J = 25^{\circ}C$ , VCC = 1.2 V.

3. When the CCC/PLL core is generated by Mircosemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero online help associated with the core for more information.

4. Maximum value obtained for a -1 speed grade device in worst-case military conditions. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

5. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by period jitter parameter.

Measurements done with LVTTL 3.3 V, 8 mA I/O drive strength and high slew rate. VCC/VCCPLL = 1.14V, VQ/PQ/TQ type of packages, 20 pF load.

7. Switching I/Os are placed outside of the PLL bank.

| Parameter            | Description                                       | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 4.88 | 5.73 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.00 | 0.00 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 1.66 | 1.95 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.22 | 0.26 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock HIGH to New Data Valid on RD (flow-through) | 2.84 | 3.33 | ns    |

| t <sub>CKQ2</sub>    | Clock HIGH to New Data Valid on RD (pipelined)    |      | 1.27 | ns    |

| t <sub>RCKEF</sub>   | RCLK HIGH to Empty Flag Valid                     |      | 2.43 | ns    |

| t <sub>WCKFF</sub>   | WCLK HIGH to Full Flag Valid                      |      | 2.31 | ns    |

| t <sub>CKAF</sub>    | Clock HIGH to Almost Empty/Full Flag Valid        | 7.45 | 8.76 | ns    |

| t <sub>RSTFG</sub>   | RESET LOW to Empty/Full Flag Valid                | 2.04 | 2.40 | ns    |

| t <sub>RSTAF</sub>   | RESET LOW to Almost Empty/Full Flag Valid         | 7.38 | 8.67 | ns    |

| t <sub>RSTBQ</sub>   | RESET LOW to Data Out LOW on RD (flow-through)    | 1.11 | 1.31 | ns    |

|                      | RESET LOW to Data Out LOW on RD (pipelined)       | 1.11 | 1.31 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.34 | 0.40 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    |      | 2.12 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         |      | 0.30 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.89 | 4.57 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 257  | 219  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-6 for derating values.

#### GL Globals

FF

GL I/Os have access to certain clock conditioning circuitry (and the PLL) and/or have direct access to the global network (spines). Additionally, the global I/Os can be used as regular I/Os, since they have identical capabilities. Unused GL pins are configured as inputs with pull-up resistors.

See more detailed descriptions of global I/O connectivity in the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs " chapter of the *Military ProASIC3/EL FPGA Fabric User's Guide*. All inputs labeled GC/GF are direct inputs into the quadrant clocks. For example, if GAA0 is used for an input, GAA1 and GAA2 are no longer available for input to the quadrant globals. All inputs labeled GC/GF are direct inputs into the chip-level globals, and the rest are connected to the quadrant globals. The inputs to the global network are multiplexed, and only one input can be used as a global input.

Refer to the "I/O Structures in IGLOO and ProASIC3 Devices" chapter (for A3P250 and A3P1000) or "I/O Structures in IGLOOe and ProASIC3E Devices" (for A3PE600L and A3PE3000L) of the *Military ProASIC3/EL FPGA Fabric User's Guide* for an explanation of the naming of global pins.

#### Flash\*Freeze Mode Activation Pin

Flash\*Freeze is available on A3PE600L and A3PE3000L devices. The FF pin is a dedicated input pin used to enter and exit Flash\*Freeze mode. The FF pin is active low, has the same characteristics as a single-ended I/O, and must meet the maximum rise and fall times. When Flash\*Freeze mode is not used in the design, the FF pin is available as a regular I/O. The FF pin can be configured as a Schmitt trigger input.

When Flash\*Freeze mode is used, the FF pin must not be left floating to avoid accidentally entering Flash\*Freeze mode. While in Flash\*Freeze mode, the Flash\*Freeze pin should be constantly asserted.

The Flash\*Freeze pin can be used with any single-ended I/O standard supported by the I/O bank in which the pin is located, and input signal levels compatible with the I/O standard selected. The FF pin should be treated as a sensitive asynchronous signal. When defining pin placement and board layout, simultaneously switching outputs (SSOs) and their effects on sensitive asynchronous pins must be considered.

Unused FF or I/O pins are tristated with weak pull-up. This default configuration applies to both Flash\*Freeze mode and normal operation mode. No user intervention is required.

Table 3-1 shows the Flash\*Freeze pin location on the available packages for Military ProASIC3/EL devices. The Flash\*Freeze pin location is independent of device, allowing migration to larger or smaller devices while maintaining the same pin location on the board. Refer to the "Flash\*Freeze Technology and Low Power Modes" chapter of the *Military ProASIC3/EL FPGA Fabric User Guide* for more information on I/O states during Flash\*Freeze mode.

| Military ProASIC3/EL Packages | Flash*Freeze Pin |

|-------------------------------|------------------|

| FG484                         | W6               |

| FG896                         | AH4              |

Table 3-1 • Flash\*Freeze Pin Location in Military ProASIC3/EL Packages (device-independent)

Military ProASIC3/EL Low Power Flash FPGAs

| FG484         |                   |               | FG484             |               | FG484               |

|---------------|-------------------|---------------|-------------------|---------------|---------------------|

| Pin<br>Number | A3PE600L Function | Pin<br>Number | A3PE600L Function | Pin<br>Number | A3PE600L Function   |

| R8            | VMV5              | T21           | IO64PDB3V1        | V12           | IO83PDB5V0          |

| R9            | VCCIB5            | T22           | IO62NDB3V1        | V13           | IO77NDB4V1          |

| R10           | VCCIB5            | U1            | NC                | V14           | IO77PDB4V1          |

| R11           | IO84NDB5V0        | U2            | IO107PDB6V0       | V15           | IO69NDB4V0          |

| R12           | IO84PDB5V0        | U3            | IO107NDB6V0       | V16           | GDB2/IO69PDB4V0     |

| R13           | VCCIB4            | U4            | GEB1/IO103PDB6V0  | V17           | TDI                 |

| R14           | VCCIB4            | U5            | GEB0/IO103NDB6V0  | V18           | GNDQ                |

| R15           | VMV3              | U6            | VMV6              | V19           | TDO                 |

| R16           | VCCPLD            | U7            | VCCPLE            | V20           | GND                 |

| R17           | GDB1/IO66PPB3V1   | U8            | IO101NPB5V2       | V21           | NC                  |

| R18           | GDC1/IO65PDB3V1   | U9            | IO95PPB5V1        | V22           | IO63NDB3V1          |

| R19           | IO61NDB3V1        | U10           | IO92PDB5V1        | W1            | NC                  |

| R20           | VCC               | U11           | IO90PDB5V1        | W2            | NC                  |

| R21           | IO59NDB3V0        | U12           | IO82PDB5V0        | W3            | NC                  |

| R22           | IO62PDB3V1        | U13           | IO76NDB4V1        | W4            | GND                 |

| T1            | NC                | U14           | IO76PDB4V1        | W5            | IO100NDB5V2         |

| T2            | IO110NDB6V0       | U15           | VMV4              | W6            | FF/GEB2/IO100PDB5V2 |

| Т3            | NC                | U16           | ТСК               | W7            | IO99NDB5V2          |

| T4            | IO105PDB6V0       | U17           | VPUMP             | W8            | IO88NDB5V0          |

| T5            | IO105NDB6V0       | U18           | TRST              | W9            | IO88PDB5V0          |

| T6            | GEC1/IO104PPB6V0  | U19           | GDA0/IO67NDB3V1   | W10           | IO89NDB5V0          |

| Τ7            | VCOMPLE           | U20           | NC                | W11           | IO80NDB4V1          |

| Т8            | GNDQ              | U21           | IO64NDB3V1        | W12           | IO81NDB4V1          |

| Т9            | GEA2/IO101PPB5V2  | U22           | IO63PDB3V1        | W13           | IO81PDB4V1          |

| T10           | IO92NDB5V1        | V1            | NC                | W14           | IO70NDB4V0          |

| T11           | IO90NDB5V1        | V2            | NC                | W15           | GDC2/IO70PDB4V0     |

| T12           | IO82NDB5V0        | V3            | GND               | W16           | IO68NDB4V0          |

| T13           | IO74NDB4V1        | V4            | GEA1/IO102PDB6V0  | W17           | GDA2/IO68PDB4V0     |

| T14           | IO74PDB4V1        | V5            | GEA0/IO102NDB6V0  | W18           | TMS                 |

| T15           | GNDQ              | V6            | GNDQ              | W19           | GND                 |

| T16           | VCOMPLD           | V7            | GEC2/IO99PDB5V2   | W20           | NC                  |

| T17           | VJTAG             | V8            | IO95NPB5V1        | W21           | NC                  |

| T18           | GDC0/IO65NDB3V1   | V9            | IO91NDB5V1        | W22           | NC                  |

| T19           | GDA1/IO67PDB3V1   | V10           | IO91PDB5V1        | Y1            | VCCIB6              |

| T20           | NC                | V11           | IO83NDB5V0        | Y2            | NC                  |

| FG896                         |                  |  |

|-------------------------------|------------------|--|

| Pin Number A3PE3000L Function |                  |  |

| N20                           | VCC              |  |

| N21                           | VCCIB2           |  |

| N22                           | IO106NDB2V3      |  |

| N23                           | IO106PDB2V3      |  |

| N24                           | IO108PDB2V3      |  |

| N25                           | IO108NDB2V3      |  |

| N26                           | IO95NDB2V1       |  |

| N27                           | IO99NDB2V2       |  |

| N28                           | IO99PDB2V2       |  |

| N29                           | IO107PDB2V3      |  |

| N30                           | IO107NDB2V3      |  |

| P1                            | IO276NDB7V0      |  |

| P2                            | IO278NDB7V0      |  |

| P3                            | IO280NDB7V0      |  |

| P4                            | IO284NDB7V1      |  |

| P5                            | IO279NDB7V0      |  |

| P6                            | GFC1/IO275PDB7V0 |  |

| P7                            | GFC0/IO275NDB7V0 |  |

| P8                            | IO277PDB7V0      |  |

| P9                            | IO277NDB7V0      |  |

| P10                           | VCCIB7           |  |

| P11                           | VCC              |  |

| P12                           | GND              |  |

| P13                           | GND              |  |

| P14                           | GND              |  |

| P15                           | GND              |  |

| P16                           | GND              |  |

| P17                           | GND              |  |

| P18                           | GND              |  |

| P19                           | GND              |  |

| P20                           | VCC              |  |

| P21                           | VCCIB2           |  |

| P22                           | GCC1/IO112PDB2V3 |  |

| P23                           | IO110PDB2V3      |  |

| P24                           | IO110NDB2V3      |  |

| P25                           | IO109PPB2V3      |  |

Datasheet Information

| Revision                                                                                                                                                                                          | Changes                                                                                                                                                                                                                          | Page                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Revision 1<br>(continued)                                                                                                                                                                         | The drive strength was changed from 25 mA to 20 mA for 3.3 V and 2.5 V GTL (SAR 31978). This affects the following tables:                                                                                                       |                           |

| . ,                                                                                                                                                                                               | Table 2-25 • Summary of Maximum and Minimum DC Input and Output Levels                                                                                                                                                           | 2-22                      |

|                                                                                                                                                                                                   | Table 2-31 • Summary of I/O Timing Characteristics—Software Default Settings (SAR                                                                                                                                                | 2-26                      |

|                                                                                                                                                                                                   | 32394)                                                                                                                                                                                                                           | 2-27                      |

|                                                                                                                                                                                                   | Table 2-32 • Summary of I/O Timing Characteristics—Software Default Settings                                                                                                                                                     | 2-30                      |

|                                                                                                                                                                                                   | Table 2-36 • I/O Output Buffer Maximum Resistances <sup>1</sup> Applicable to Pro I/Os for A3PE600L and A3PE3000L Only                                                                                                           | 2-33                      |

|                                                                                                                                                                                                   | Table 2-40 • I/O Short Currents IOSH/IOSL Applicable to Pro I/Os for A3PE600L and A3PE3000L Only                                                                                                                                 | 2-73                      |

|                                                                                                                                                                                                   | Table 2-120 • Minimum and Maximum DC Input and Output Levels                                                                                                                                                                     | 2-75                      |

|                                                                                                                                                                                                   | Table 2-124 • Minimum and Maximum DC Input and Output Levels                                                                                                                                                                     |                           |

|                                                                                                                                                                                                   | The values in Table 2-39 • I/O Weak Pull-Up/Pull-Down Resistances were revised (SAR 29793, 28061).                                                                                                                               | 2-32                      |

|                                                                                                                                                                                                   | The AC Loading diagrams in the "Single-Ended I/O Characteristics" section were updated to match summary of I/O timing tables in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section (SAR 32449). | 2-37                      |

| Т                                                                                                                                                                                                 | The tables in the "Voltage-Referenced I/O Characteristics" section and "Differential I/O                                                                                                                                         | 2-73                      |

|                                                                                                                                                                                                   | Characteristics" section were updated with current values (SARs 29793, 32391, 32394).                                                                                                                                            | 2-85                      |

|                                                                                                                                                                                                   | Two note references were added to Table 2-160 • Minimum and Maximum DC Input and Output Levels to clarify the following notes: $\pm 5\%$ [VCCI] and differential input voltage = $\pm 350$ mV [VDIFF] (SAR 29428).               | 2-86                      |