Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Dataila                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Details                    |                                                                          |

| Product Status             | Active                                                                   |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 27                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-TQFP                                                                  |

| Supplier Device Package    | 32-TQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega168pb-au |

|                            |                                                                          |

|             | 29.1. | Features                                                                       | 322  |

|-------------|-------|--------------------------------------------------------------------------------|------|

|             | 29.2. | Overview                                                                       | 322  |

|             | 29.3. | Starting a Conversion                                                          | 324  |

|             | 29.4. | Prescaling and Conversion Timing                                               | 325  |

|             | 29.5. | Changing Channel or Reference Selection                                        | 327  |

|             | 29.6. | ADC Noise Canceler                                                             | 329  |

|             | 29.7. | ADC Conversion Result                                                          | 332  |

|             | 29.8. | Temperature Measurement                                                        | 333  |

|             | 29.9. | Register Description                                                           | 333  |

| 30          | DRG   | - debugWIRE On-chip Debug System                                               | 3//  |

| 50.         |       |                                                                                |      |

|             |       | Features                                                                       |      |

|             |       | Overview                                                                       |      |

|             |       | Physical Interface                                                             |      |

|             |       | Software Break Points.                                                         |      |

|             |       | Limitations of debugWIRE                                                       |      |

|             | 30.6. | Register Description                                                           | 345  |

| 31.         | Self- | Programming the Flash                                                          | 347  |

|             | 31.1. | Overview                                                                       | 347  |

|             | 31.2. | Addressing the Flash During Self-Programming                                   | 348  |

|             | 31.3. | Register Description                                                           | 353  |

| 32          | RTI [ | DR - Boot Loader Support – Read-While-Write Self-Programming                   | 356  |

| JZ.         |       |                                                                                |      |

|             |       | Features                                                                       |      |

|             |       | Overview                                                                       |      |

|             |       | Application and Boot Loader Flash Sections                                     |      |

|             |       | Read-While-Write and No Read-While-Write Flash Sections  Boot Loader Lock Bits |      |

|             |       |                                                                                |      |

|             |       | Entering the Boot Loader Program                                               |      |

|             |       | Addressing the Flash During Self-Programming                                   |      |

|             |       | Register Description                                                           |      |

|             | 32.9. | Register Description.                                                          | 37 1 |

| 33.         | MEN   | PROG- Memory Programming                                                       | 374  |

|             | 33.1. | Program And Data Memory Lock Bits                                              | 374  |

|             | 33.2. | Fuse Bits                                                                      | 375  |

|             | 33.3. | Signature Bytes                                                                | 378  |

|             | 33.4. | Calibration Byte                                                               | 378  |

|             | 33.5. | Page Size                                                                      | 378  |

|             | 33.6. | Parallel Programming Parameters, Pin Mapping, and Commands                     | 379  |

|             | 33.7. | Parallel Programming                                                           | 381  |

|             | 33.8. | Serial Downloading                                                             | 388  |

| 34          | Flect | rical Characteristics                                                          | 303  |

| <b>∪</b> ¬. |       |                                                                                |      |

|             |       | Absolute Maximum Ratings                                                       |      |

|             |       | DC Characteristics                                                             |      |

|             |       | Speed Grades                                                                   |      |

|             | J4.4. | Clock Characteristics                                                          | 97   |

# 2. Configuration Summary

Table 2-1. Configuration Summary

|                         | ATmega48PB      | ATmega88PB | ATmega168PB |  |  |

|-------------------------|-----------------|------------|-------------|--|--|

| Pin count               | 32              | 32         | 32          |  |  |

| Flash (KB)              | 4               | 8          | 16          |  |  |

| SRAM (Bytes)            | 512             | 1024       | 1024        |  |  |

| EEPROM (Bytes)          | 256             | 512        | 512         |  |  |

| Max I/O pins            | 27              |            |             |  |  |

| SPI                     | 1               |            |             |  |  |

| TWI (I <sup>2</sup> C)  | 1               |            |             |  |  |

| USART                   | 1               |            |             |  |  |

| ADC                     | 10-bit 15ksps   |            |             |  |  |

| ADC channels            | 8               |            |             |  |  |

| AC                      | 1               |            |             |  |  |

| 8-bit Timer/Counters    | 2               |            |             |  |  |

| 16-bit Timer/Counters   | 1               |            |             |  |  |

| PWM channels            | 6               |            |             |  |  |

| Operating voltage       | 1.8V - 5.5V     |            |             |  |  |

| Max operating frequency | 20MHz           |            |             |  |  |

| Temperature range       | -40°C to +105°C |            |             |  |  |

PC4 (ADC4/SDA/PCINT12) PC5 (ADC5/SCL/PCINT13) PC6 (RESET/PCINT14) PC3 (ADC3/PCINT11) PC2 (ADC2/PCINT10) PD2 (INT0/PCINT18) PD0 (RXD/PCINT16) PD1 (TXD/PCINT17) 25 (PCINT19/OC2B/INT1) PD3 24 PC1 (ADC1/PCINT9) (PCINT20/XCK/T0) PD4 2 23 PC0 (ADC0/PCINT8) (ACO) PE0 3 22 PE3 (ADC7) VCC 21 **GND** 4 GND 5 20 **AREF** PE1 6 19 PE2 (ADC6) (PCINT6/XTAL1/TOSC1) PB6 7 **AVCC** 18 8 (PCINT7/XTAL2/TOSC2) PB7 17 PB5 (SCK/PCINT5) 13 4 15 16 9 12 NOTE: Bottom pad should be (PCINT21/OC0B/T1) PD5 PCINT22/OC0A/AIN0) PD6 (PCINT23/AIN1) PD7 (PCINT0/CLKO/ICP1) PB0 (PCINT4/MISO) PB4 soldered to ground (PCINT2/SS/OC1B) PB2 (PCINT3/MOSI/OC2A) PB3 (PCINT1/OC1A) PB1

Figure 5-2. 32 VQFN Pinout ATmega48PB/88PB/168PB

# 5.1. Pin Descriptions

# 5.1.1. VCC

Digital supply voltage.

#### 5.1.2. GND

Ground.

#### 12.5.2. Stack Pointer Low Register

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

Reset value of SPL is RAMEND.

Name: SPL Offset: 0x5D Reset: 0xXX

Property: When addressing as I/O Register: address offset is 0x3D

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|        | SP7 | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 |

| Access | R/W |

| Reset  | X   | x   | x   | X   | x   | x   | x   | X   |

Bit 7 - SP7: Stack Pointer Address 7

Bit 6 - SP6: Stack Pointer Address 6

Bit 5 - SP5: Stack Pointer Address 5

Bit 4 - SP4: Stack Pointer Address 4

Bit 3 - SP3: Stack Pointer Address 3

Bit 2 - SP2: Stack Pointer Address 2

Bit 1 - SP1: Stack Pointer Address 1

Bit 0 - SP0: Stack Pointer Address 0

# 12.6. Instruction Execution Timing

This section describes the general access timing concepts for instruction execution. The AVR CPU is driven by the CPU clock clk<sub>CPU</sub>, directly generated from the selected clock source for the chip. No internal clock division is used. The Figure below shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture and the fast-access Register File concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

must be written to '1' before EEPE is written to '1', otherwise no EEPROM write takes place. The following procedure should be followed when writing the EEPROM (the order of steps 3 and 4 is not essential):

- 1. Wait until EEPE becomes zero.

- Wait until SPMEN in SPMCSR becomes zero.

- 3. Write new EEPROM address to EEAR (optional).

- Write new EEPROM data to EEDR (optional).

- 5. Write a '1' to the EEMPE bit while writing a zero to EEPE in EECR.

- 6. Within four clock cycles after setting EEMPE, write a '1' to EEPE.

The EEPROM can not be programmed during a CPU write to the Flash memory. The software must check that the Flash programming is completed before initiating a new EEPROM write. Step 2 is only relevant if the software contains a Boot Loader allowing the CPU to program the Flash. If the Flash is never being updated by the CPU, step 2 can be omitted.

#### Caution:

An interrupt between step 5 and step 6 will make the write cycle fail, since the EEPROM Master Write Enable will time-out. If an interrupt routine accessing the EEPROM is interrupting another EEPROM access, the EEAR or EEDR Register will be modified, causing the interrupted EEPROM access to fail. It is recommended to have the Global Interrupt Flag cleared during all the steps to avoid these problems.

When the write access time has elapsed, the EEPE bit is cleared by hardware. The user software can poll this bit and wait for a zero before writing the next byte. When EEPE has been set, the CPU is halted for two cycles before the next instruction is executed.

#### Bit 0 - EERE: EEPROM Read Enable

The EEPROM Read Enable Signal EERE is the read strobe to the EEPROM. When the correct address is set up in the EEAR Register, the EERE bit must be written to a '1' to trigger the EEPROM read. The EEPROM read access takes one instruction, and the requested data is available immediately. When the EEPROM is read, the CPU is halted for four cycles before the next instruction is executed.

The user should poll the EEPE bit before starting the read operation. If a write operation is in progress, it is neither possible to read the EEPROM, nor to change the EEAR Register.

The calibrated Oscillator is used to time the EEPROM accesses. See the following table for typical programming times for EEPROM access from the CPU.

Table 13-2. EEPROM Programming Time

| Symbol                  | Number of Calibrated RC Oscillator Cycles | Typ. Programming Time |

|-------------------------|-------------------------------------------|-----------------------|

| EEPROM write (from CPU) | 26,368                                    | 3.3ms                 |

The following code examples show one assembly and one C function for writing to the EEPROM. The examples assume that interrupts are controlled (e.g. by disabling interrupts globally) so that no interrupts will occur during execution of these functions. The examples also assume that no Flash Boot Loader is present in the software. If such code is present, the EEPROM write function must also wait for any ongoing SPM command to finish.

#### **Assembly Code Example**

```

EEPROM write:

; Wait for completion of previous write

sbic EECR, EEPE

```

# 14. System Clock and Clock Options

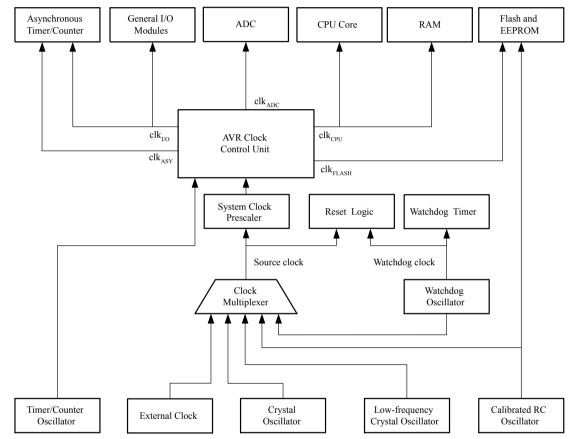

# 14.1. Clock Systems and Their Distribution

The following figure illustrates the principal clock systems in the device and their distribution. All the clocks need not be active at a given time. In order to reduce power consumption, the clocks to modules not being used can be halted by using different sleep modes. The clock systems are described in the following sections.

The system clock frequency refers to the frequency generated from the System Clock Prescaler. All clock outputs from the AVR Clock Control Unit runs in the same frequency.

Figure 14-1. Clock Distribution

#### **Related Links**

Power Management and Sleep Modes on page 60

# 14.1.1. CPU Clock - clk<sub>CPU</sub>

The CPU clock is routed to parts of the system concerned with operation of the AVR core. Examples of such modules are the General Purpose Register File, the Status Register and the data memory holding the Stack Pointer. Halting the CPU clock inhibits the core from performing general operations and calculations.

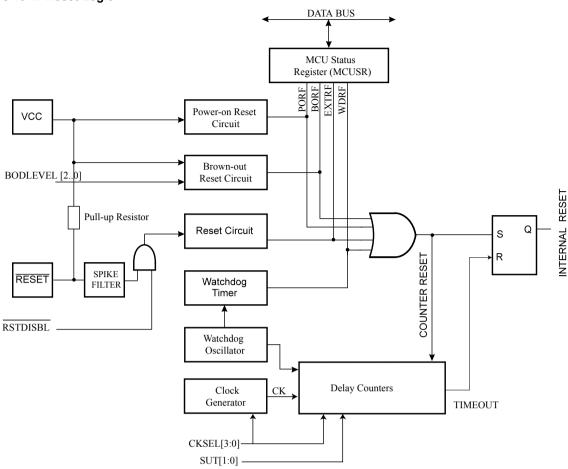

Figure 16-1. Reset Logic

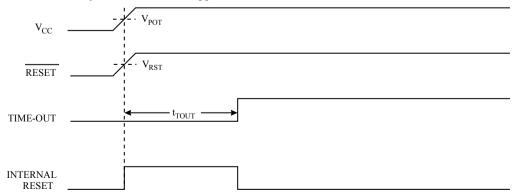

# 16.3. Power-on Reset

A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The POR is activated whenever  $V_{CC}$  is below the detection level. The POR circuit can be used to trigger the start-up Reset, as well as to detect a failure in supply voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the Power-on Reset threshold voltage invokes the delay counter, which determines how long the device is kept in Reset after  $V_{CC}$  rise. The Reset signal is activated again, without any delay, when  $V_{CC}$  decreases below the detection level.

Figure 16-2. MCU Start-up, RESET Tied to V<sub>CC</sub>

Thus, when the BOD is not enabled, after setting ACSR.ACBG or enabling the ADC, the user must always allow the reference to start up before the output from the Analog Comparator or ADC is used. To reduce power consumption in Power-Down mode, the user can avoid the three conditions above to ensure that the reference is turned off before entering Power-Down mode.

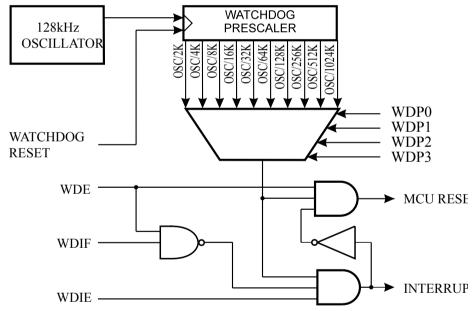

# 16.8. Watchdog Timer

If the watchdog timer is not needed in the application, the module should be turned off. If the watchdog timer is enabled, it will be enabled in all sleep modes and hence always consume power. In the deeper sleep modes, this will contribute significantly to the total current consumption.

Refer to Watchdog System Reset for details on how to configure the watchdog timer.

#### 16.8.1. Overview

The device has an Enhanced Watchdog Timer (WDT). The WDT is a timer counting cycles of a separate on-chip 128kHz oscillator. The WDT gives an interrupt or a system reset when the counter reaches a given time-out value. In normal operation mode, it is required that the system uses the Watchdog Timer Reset (WDR) instruction to restart the counter before the time-out value is reached. If the system doesn't restart the counter, an interrupt or system reset will be issued.

Figure 16-7. Watchdog Timer

In Interrupt mode, the WDT gives an interrupt when the timer expires. This interrupt can be used to wake the device from sleep-modes, and also as a general system timer. One example is to limit the maximum time allowed for certain operations, giving an interrupt when the operation has run longer than expected. In System Reset mode, the WDT gives a reset when the timer expires. This is typically used to prevent system hang-up in case of runaway code. The third mode, Interrupt and System Reset mode, combines the other two modes by first giving an interrupt and then switch to System Reset mode. This mode will for instance allow a safe shutdown by saving critical parameters before a system reset.

The Watchdog always on (WDTON) fuse, if programmed, will force the Watchdog Timer to System Reset mode. With the fuse programmed the System Reset mode bit (WDE) and Interrupt mode bit (WDIE) are locked to 1 and 0 respectively. To further ensure program security, alterations to the Watchdog set-up must follow timed sequences. The sequence for clearing WDE and changing time-out configuration is as follows:

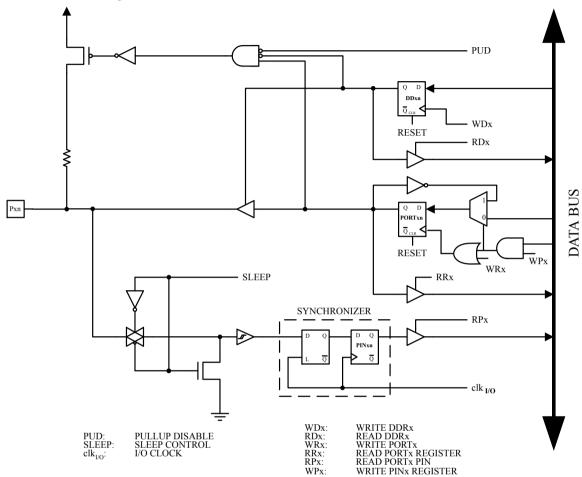

# 19.2. Ports as General Digital I/O

The ports are bi-directional I/O ports with optional internal pull-ups. The following figure shows the functional description of one I/O-port pin, here generically called Pxn.

Figure 19-2. General Digital I/O(1)

Note: 1. WRx, WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port.  $clk_{I/O}$ , SLEEP, and PUD are common to all ports.

# 19.2.1. Configuring the Pin

Each port pin consists of three register bits: DDxn, PORTxn, and PINxn. As shown in the Register Description, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the PORTx I/O address, and the PINxn bits at the PINx I/O address.

The DDxn bit in the DDRx Register selects the direction of this pin. If DDxn is written to '1', Pxn is configured as an output pin. If DDxn is written to '0', Pxn is configured as an input pin.

If PORTxn is written to '1' when the pin is configured as an input pin, the pull-up resistor is activated. To switch the pull-up resistor off, PORTxn has to be written to '0' or the pin has to be configured as an output pin. The port pins are tri-stated when reset condition becomes active, even if no clocks are running.

If PORTxn is written to '1' when the pin is configured as an output pin, the port pin is driven high. If PORTxn is written logic zero when the pin is configured as an output pin, the port pin is driven low.

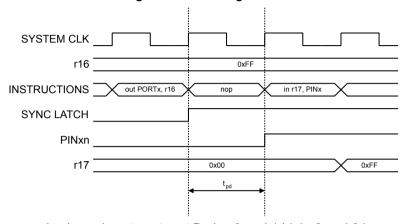

region of the "SYNC LATCH" signal. The signal value is latched when the system clock goes low. It is clocked into the PINxn Register at the succeeding positive clock edge. As indicated by the two arrows tpd,max and tpd,min, a single signal transition on the pin will be delayed between  $\frac{1}{2}$  and  $\frac{1}{2}$  system clock period depending upon the time of assertion.

When reading back a software assigned pin value, a nop instruction must be inserted as indicated in the following figure. The out instruction sets the "SYNC LATCH" signal at the positive edge of the clock. In this case, the delay tpd through the synchronizer is 1 system clock period.

Figure 19-4. Synchronization when Reading a Software Assigned Pin Value

The following code example shows how to set port B pins 0 and 1 high, 2 and 3 low, and define the port pins from 4 to 7 as input with pull-ups assigned to port pins 6 and 7. The resulting pin values are read back again, but as previously discussed, a nop instruction is included to be able to read back the value recently assigned to some of the pins.

```

Assembly Code Example<sup>(1)</sup>

...

; Define pull-ups and set outputs high

; Define directions for port pins

ldi r16, (1<<PB7) | (1<<PB6) | (1<<PB1) | (1<<PB0)

ldi r17, (1<<DDB3) | (1<<DDB2) | (1<<DDB1) | (1<<DDB0)

out PORTB, r16

out DDRB, r17

; Insert nop for synchronization

nop

; Read port pins

in r16, PINB

...

```

**Note:** 1. For the assembly program, two temporary registers are used to minimize the time from pull-ups are set on pins 0, 1, 6, and 7, until the direction bits are correctly set, defining bit 2 and 3 as low and redefining bits 0 and 1 as strong high drivers.

# **Port C Data Direction Register**

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

**DDRC** Name: Offset: 0x27 Reset: 0x00

Property: When addressing as I/O Register: address offset is 0x07

| Bit    | 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|---|-------|-------|-------|-------|-------|-------|-------|

|        |   | DDRC6 | DDRC5 | DDRC4 | DDRC3 | DDRC2 | DDRC1 | DDRC0 |

| Access |   | R/W   |

| Reset  |   | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Bits 6:0 – DDRCn: Port C Data Direction [n = 6:0]

# 23.11.5. TC2 Output Compare Register B

OCR2B Name: Offset: 0xB4 Reset: 0x00 Property: -

| Bit    | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|------------|-----|-----|-----|-----|-----|-----|-----|

|        | OCR2B[7:0] |     |     |     |     |     |     |     |

| Access | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset  | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

# Bits 7:0 - OCR2B[7:0]: Output Compare 2 B

The Output Compare Register B contains an 8-bit value that is continuously compared with the counter value (TCNT2). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC2B pin.

## 24.5.2. SPI Status Register 0

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

Name: SPSR Offset: 0x4D Reset: 0x00

Property: When addressing as I/O Register: address offset is 0x2D

| Bit    | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|------|------|---|---|---|---|---|-------|

|        | SPIF | WCOL |   |   |   |   |   | SPI2X |

| Access | R    | R    |   |   |   |   |   | R/W   |

| Reset  | 0    | 0    |   |   |   |   |   | 0     |

## Bit 7 - SPIF: SPI Interrupt Flag

When a serial transfer is complete, the SPIF Flag is set. An interrupt is generated if SPIE in SPCR is set and global interrupts are enabled. If  $\overline{SS}$  is an input and is driven low when the SPI is in Master mode, this will also set the SPIF Flag. SPIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, the SPIF bit is cleared by first reading the SPI Status Register with SPIF set, then accessing the SPI Data Register (SPDR).

### Bit 6 - WCOL: Write Collision Flag

The WCOL bit is set if the SPI Data Register (SPDR) is written during a data transfer. The WCOL bit (and the SPIF bit) are cleared by first reading the SPI Status Register with WCOL set, and then accessing the SPI Data Register.

## Bit 0 - SPI2X: Double SPI Speed Bit

When this bit is written to logic one the SPI speed (SCK Frequency) will be doubled when the SPI is in Master mode (refer to Table 24-5 Relationship between SCK and Oscillator Frequency). This means that the minimum SCK period will be two CPU clock periods. When the SPI is configured as Slave, the SPI is only guaranteed to work at fosc/4 or lower.

The SPI interface is also used for program memory and EEPROM downloading or uploading. See *Serial Downloading* for serial programming and verification.

# 26. USARTSPI - USART in SPI Mode

## 26.1. Features

- Full Duplex, Three-wire Synchronous Data Transfer

- Master Operation

- Supports all four SPI Modes of Operation (Mode 0, 1, 2, and 3)

- LSB First or MSB First Data Transfer (Configurable Data Order)

- Queued Operation (Double Buffered)

- High Resolution Baud Rate Generator

- High Speed Operation (f<sub>XCKmax</sub> = f<sub>CK</sub>/2)

- Flexible Interrupt Generation

### 26.2. Overview

The Universal Synchronous and Asynchronous serial Receiver and Transmitter (USART) can be set to a master SPI compliant mode of operation.

Setting both UMSELn[1:0] bits to one enables the USART in MSPIM logic. In this mode of operation the SPI master control logic takes direct control over the USART resources. These resources include the transmitter and receiver shift register and buffers, and the baud rate generator. The parity generator and checker, the data and clock recovery logic, and the RX and TX control logic is disabled. The USART RX and TX control logic is replaced by a common SPI transfer control logic. However, the pin control logic and interrupt generation logic is identical in both modes of operation.

The I/O register locations are the same in both modes. However, some of the functionality of the control registers changes when using MSPIM.

## 26.3. Clock Generation

The Clock Generation logic generates the base clock for the Transmitter and Receiver. For USART MSPIM mode of operation only internal clock generation (i.e. master operation) is supported. The Data Direction Register for the XCKn pin (DDR\_XCKn) must therefore be set to one (i.e. as output) for the USART in MSPIM to operate correctly. Preferably the DDR\_XCKn should be set up before the USART in MSPIM is enabled (i.e. TXENn and RXENn bit set to one).

The internal clock generation used in MSPIM mode is identical to the USART synchronous master mode. The table below contains the equations for calculating the baud rate or UBRRn setting for Synchronous Master Mode.

Table 26-1. Equations for Calculating Baud Rate Register Setting

| Operating Mode          | Equation for Calculating Baud Rate <sup>(1)</sup> | Equation for Calculating UBRRn<br>Value                         |

|-------------------------|---------------------------------------------------|-----------------------------------------------------------------|

| Synchronous Master mode | $BAUD = \frac{f_{OSC}}{2(\mathbf{UBRR}n + 1)}$    | $\mathbf{UBRR}n = \frac{f_{\mathrm{OSC}}}{2\mathrm{BAUD}} + -1$ |

Note: 1. The baud rate is defined to be the transfer rate in bit per second (bps)

# 27.9.1. TWI Bit Rate Register

**TWBR** Name: Offset: 0xB8 Reset: 0x00 Property: -

| Bit    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

|        | TWBR7 | TWBR6 | TWBR5 | TWBR4 | TWBR3 | TWBR2 | TWBR1 | TWBR0 |

| Access | R/W   |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Bits 7:0 – TWBRn: TWI Bit Rate Register [n = 7:0]

TWBR selects the division factor for the bit rate generator. The bit rate generator is a frequency divider which generates the SCL clock frequency in the Master modes.

### 27.9.4. TWI Data Register

In Transmit mode, TWDR contains the next byte to be transmitted. In Receive mode, the TWDR contains the last byte received. It is writable while the TWI is not in the process of shifting a byte. This occurs when the TWI Interrupt Flag (TWINT) is set by hardware. Note that the Data Register cannot be initialized by the user before the first interrupt occurs. The data in TWDR remains stable as long as TWINT is set. While data is shifted out, data on the bus is simultaneously shifted in. TWDR always contains the last byte present on the bus, except after a wake up from a sleep mode by the TWI interrupt. In this case, the contents of TWDR is undefined. In the case of a lost bus arbitration, no data is lost in the transition from Master to Slave. Handling of the ACK bit is controlled automatically by the TWI logic, the CPU cannot access the ACK bit directly.

Name: TWDR

Offset: 0xBB

Reset: 0xFF

Property: -

| Bit    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|------|------|------|------|------|------|------|------|

|        | TWD7 | TWD6 | TWD5 | TWD4 | TWD3 | TWD2 | TWD1 | TWD0 |

| Access | R/W  |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    |

Bits 7:0 - TWDn: TWI Data [n = 7:0]

These eight bits constitute the next data byte to be transmitted, or the latest data byte received on the 2-wire Serial Bus.

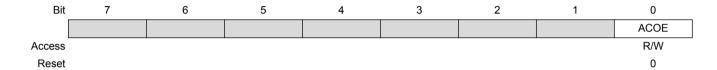

## 28.3.2. Analog Comparator Control and Status Register C

The Store Program Memory Control and Status Register contains the control bits needed to control the Boot Loader operations.

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

Name: ACSR0 Offset: 0x4F Reset: 0x00

Property: When addressing as I/O Register: address offset is 0x2F

# Bit 0 - ACOE: Analog Comparator Output Enable

When this bit is set, the analog comparator output is connected to the ACO pin.

### 29.9.2. ADC Control and Status Register A

Name: ADCSRA

Offset: 0x7A

Reset: 0x00

Property: -

| Bit    | 7    | 6    | 5     | 4    | 3    | 2     | 1     | 0     |

|--------|------|------|-------|------|------|-------|-------|-------|

|        | ADEN | ADSC | ADATE | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 |

| Access | R/W  | R/W  | R/W   | R/W  | R/W  | R/W   | R/W   | R/W   |

| Reset  | 0    | 0    | 0     | 0    | 0    | 0     | 0     | 0     |

#### Bit 7 - ADEN: ADC Enable

Writing this bit to one enables the ADC. By writing it to zero, the ADC is turned off. Turning the ADC off while a conversion is in progress, will terminate this conversion.

#### Bit 6 - ADSC: ADC Start Conversion

In Single Conversion mode, write this bit to one to start each conversion. In Free Running mode, write this bit to one to start the first conversion. The first conversion after ADSC has been written after the ADC has been enabled, or if ADSC is written at the same time as the ADC is enabled, will take 25 ADC clock cycles instead of the normal 13. This first conversion performs initialization of the ADC.

ADSC will read as one as long as a conversion is in progress. When the conversion is complete, it returns to zero. Writing zero to this bit has no effect.

# Bit 5 - ADATE: ADC Auto Trigger Enable

When this bit is written to one, Auto Triggering of the ADC is enabled. The ADC will start a conversion on a positive edge of the selected trigger signal. The trigger source is selected by setting the ADC Trigger Select bits, ADTS in ADCSRB.

#### Bit 4 - ADIF: ADC Interrupt Flag

This bit is set when an ADC conversion completes and the Data Registers are updated. The ADC Conversion Complete Interrupt is executed if the ADIE bit and the I-bit in SREG are set. ADIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ADIF is cleared by writing a logical one to the flag. Beware that if doing a Read-Modify-Write on ADCSRA, a pending interrupt can be disabled. This also applies if the SBI and CBI instructions are used.

# Bit 3 - ADIE: ADC Interrupt Enable

When this bit is written to one and the I-bit in SREG is set, the ADC Conversion Complete Interrupt is activated.

#### Bits 2:0 - ADPSn: ADC Prescaler Select [n = 2:0]

These bits determine the division factor between the system clock frequency and the input clock to the ADC.

Table 29-5. Input Channel Selection

| ADPS[2:0] | Division Factor |

|-----------|-----------------|

| 000       | 2               |

| 001       | 2               |

**ZPCMSB** ZPAGEMSB Z - REGISTER 0 PCMSB PAGEMSB PROGRAM PCPAGE PCWORD COUNTER PAGE ADDRESS WORD ADDRESS WITHIN THE FLASH WITHIN A PAGE PROGRAM MEMORY **PAGE** PCWORD[PAGEMSB:0]: PAGE INSTRUCTION WORD 01 02 **PAGEEND**

Figure 32-3. Addressing the Flash During SPM

**Note:** The different variables used in this figure are listed in the Related Links.

## **Related Links**

Page Size on page 378

ATmega88PB Boot Loader Parameters on page 369

# 32.8. Self-Programming the Flash

The program memory is updated in a page by page fashion. Before programming a page with the data stored in the temporary page buffer, the page must be erased. The temporary page buffer is filled one word at a time using SPM and the buffer can be filled either before the Page Erase command or between a Page Erase and a Page Write operation:

#### Alternative 1, fill the buffer before a Page Erase

- Fill temporary page buffer

- Perform a Page Erase

- Perform a Page Write

# Alternative 2, fill the buffer after Page Erase

- Perform a Page Erase

- Fill temporary page buffer

- Perform a Page Write

#### **Instruction Set Summary 37**.

| ARITHMETIC AND LOGIC INSTRUCTIONS |          |                                          |                                     |           |         |

|-----------------------------------|----------|------------------------------------------|-------------------------------------|-----------|---------|

| Mnemonics                         | Operands | Description                              | Operation                           | Flags     | #Clocks |

| ADD                               | Rd, Rr   | Add two Registers without Carry          | Rd ← Rd + Rr                        | Z,C,N,V,H | 1       |

| ADC                               | Rd, Rr   | Add two Registers with Carry             | $Rd \leftarrow Rd + Rr + C$         | Z,C,N,V,H | 1       |

| ADIW                              | RdI,K    | Add Immediate to Word                    | Rdh:Rdl ← Rdh:Rdl + K               | Z,C,N,V,S | 2       |

| SUB                               | Rd, Rr   | Subtract two Registers                   | Rd ← Rd - Rr                        | Z,C,N,V,H | 1       |

| SUBI                              | Rd, K    | Subtract Constant from Register          | Rd ← Rd - K                         | Z,C,N,V,H | 1       |

| SBC                               | Rd, Rr   | Subtract two Registers with Carry        | Rd ← Rd - Rr - C                    | Z,C,N,V,H | 1       |

| SBCI                              | Rd, K    | Subtract Constant from Reg with Carry.   | Rd ← Rd - K - C                     | Z,C,N,V,H | 1       |

| SBIW                              | RdI,K    | Subtract Immediate from Word             | Rdh:Rdl ← Rdh:Rdl - K               | Z,C,N,V,S | 2       |

| AND                               | Rd, Rr   | Logical AND Registers                    | $Rd \leftarrow Rd \cdot Rr$         | Z,N,V     | 1       |

| ANDI                              | Rd, K    | Logical AND Register and Constant        | $Rd \leftarrow Rd \cdot K$          | Z,N,V     | 1       |

| OR                                | Rd, Rr   | Logical OR Registers                     | Rd ← Rd v Rr                        | Z,N,V     | 1       |

| ORI                               | Rd, K    | Logical OR Register and Constant         | $Rd \leftarrow Rd \vee K$           | Z,N,V     | 1       |

| EOR                               | Rd, Rr   | Exclusive OR Registers                   | $Rd \leftarrow Rd \oplus Rr$        | Z,N,V     | 1       |

| COM                               | Rd       | One's Complement                         | Rd ← 0xFF - Rd                      | Z,C,N,V   | 1       |

| NEG                               | Rd       | Two's Complement                         | Rd ← 0x00 - Rd                      | Z,C,N,V,H | 1       |

| SBR                               | Rd,K     | Set Bit(s) in Register                   | $Rd \leftarrow Rd \vee K$           | Z,N,V     | 1       |

| CBR                               | Rd,K     | Clear Bit(s) in Register                 | $Rd \leftarrow Rd \cdot (0xFF - K)$ | Z,N,V     | 1       |

| INC                               | Rd       | Increment                                | Rd ← Rd + 1                         | Z,N,V     | 1       |

| DEC                               | Rd       | Decrement                                | Rd ← Rd - 1                         | Z,N,V     | 1       |

| TST                               | Rd       | Test for Zero or Minus                   | $Rd \leftarrow Rd \cdot Rd$         | Z,N,V     | 1       |

| CLR                               | Rd       | Clear Register                           | $Rd \leftarrow Rd \oplus Rd$        | Z,N,V     | 1       |

| SER                               | Rd       | Set Register                             | Rd ← 0xFF                           | None      | 1       |

| MUL                               | Rd, Rr   | Multiply Unsigned                        | R1:R0 ← Rd x Rr                     | Z,C       | 2       |

| MULS                              | Rd, Rr   | Multiply Signed                          | R1:R0 ← Rd x Rr                     | Z,C       | 2       |

| MULSU                             | Rd, Rr   | Multiply Signed with Unsigned            | R1:R0 ← Rd x Rr                     | Z,C       | 2       |

| FMUL                              | Rd, Rr   | Fractional Multiply Unsigned             | R1:R0 ← (Rd x Rr) << 1              | Z,C       | 2       |

| FMULS                             | Rd, Rr   | Fractional Multiply Signed               | R1:R0 ← (Rd x Rr) << 1              | Z,C       | 2       |

| FMULSU                            | Rd, Rr   | Fractional Multiply Signed with Unsigned | R1:R0 ← (Rd x Rr) << 1              | Z,C       | 2       |

| BRANCH INSTRUCTIONS |          |                          |                 |       |         |

|---------------------|----------|--------------------------|-----------------|-------|---------|

| Mnemonics           | Operands | Description              | Operation       | Flags | #Clocks |

| RJMP                | k        | Relative Jump            | PC ← PC + k + 1 | None  | 2       |

| IJMP                |          | Indirect Jump to (Z)     | PC ← Z          | None  | 2       |

| JMP(1)              | k        | Direct Jump              | PC ← k          | None  | 3       |

| RCALL               | k        | Relative Subroutine Call | PC ← PC + k + 1 | None  | 3       |