# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 27                                                                      |

| Program Memory Size        | 4KB (2K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-TQFP                                                                 |

| Supplier Device Package    | 32-TQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega48pb-an |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Flags can also be cleared by writing a logic one to the flag bit position(s) to be cleared. If an interrupt condition occurs while the corresponding interrupt enable bit is cleared, the Interrupt Flag will be set and remembered until the interrupt is enabled, or the flag is cleared by software. Similarly, if one or more interrupt conditions occur while the Global Interrupt Enable bit is cleared, the corresponding Interrupt Flag(s) will be set and remembered until the Global Interrupt Enable bit is set, and will then be executed by order of priority.

The second type of interrupts will trigger as long as the interrupt condition is present. These interrupts do not necessarily have Interrupt Flags. If the interrupt condition disappears before the interrupt is enabled, the interrupt will not be triggered. When the AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served.

The Status Register is not automatically stored when entering an interrupt routine, nor restored when returning from an interrupt routine. This must be handled by software.

When using the CLI instruction to disable interrupts, the interrupts will be immediately disabled. No interrupt will be executed after the CLI instruction, even if it occurs simultaneously with the CLI instruction. The following example shows how this can be used to avoid interrupts during the timed EEPROM write sequence.

#### Assembly Code Example

```

in r16, SREG ; store SREG value

cli ; disable interrupts during timed sequence

sbi EECR, EEMPE ; start EEPROM write

sbi EECR, EEPE

out SREG, r16 ; restore SREG value (I-bit)

```

#### C Code Example

```

char cSREG;

cSREG = SREG; /* store SREG value */

/* disable interrupts during timed sequence */

_CLI();

EECR |= (1<<EEMPE); /* start EEPROM write */

EECR |= (1<<EEPE);

SREG = cSREG; /* restore SREG value (I-bit) */

```

When using the SEI instruction to enable interrupts, the instruction following SEI will be executed before any pending interrupts, as shown in this example.

#### Assembly Code Example

```

sei ; set Global Interrupt Enable

sleep ; enter sleep, waiting for interrupt

; note: will enter sleep before any pending interrupt(s)

```

#### C Code Example

```

__enable_interrupt(); /* set Global Interrupt Enable */

__sleep(); /* enter sleep, waiting for interrupt */

/* note: will enter sleep before any pending interrupt(s) */

```

#### **Related Links**

Interrupts on page 80

Memory Programming on page 374

Boot Loader Support – Read-While-Write Self-Programming on page 356

#### 16.9.2. Watchdog Timer Control Register

Name: WDTCSR Offset: 0x60 Reset: 0x00 / 0x08 Property: -

| Bit    | 7    | 6    | 5    | 4    | 3   | 2    | 1    | 0    |

|--------|------|------|------|------|-----|------|------|------|

|        | WDIF | WDIE | WDP3 | WDCE | WDE | WDP2 | WDP1 | WDP0 |

| Access | R/W  | R/W  | R/W  | R/W  | R/W | R/W  | R/W  | R/W  |

| Reset  | 0    | 0    | 0    | 0    | x   | 0    | 0    | 0    |

#### Bit 7 – WDIF: Watchdog Interrupt Flag

This bit is set when a time-out occurs in the Watchdog Timer and the Watchdog Timer is configured for interrupt. WDIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, WDIF is cleared by writing a logic one to the flag. When the I-bit in SREG and WDIE are set, the Watchdog Time-out Interrupt is executed.

#### Bit 6 – WDIE: Watchdog Interrupt Enable

When this bit is written to one and the I-bit in the Status Register is set, the Watchdog Interrupt is enabled. If WDE is cleared in combination with this setting, the Watchdog Timer is in Interrupt Mode, and the corresponding interrupt is executed if time-out in the Watchdog Timer occurs. If WDE is set, the Watchdog Timer is in Interrupt and System Reset Mode. The first time-out in the Watchdog Timer will set WDIF. Executing the corresponding interrupt vector will clear WDIE and WDIF automatically by hardware (the Watchdog goes to System Reset Mode).

This is useful for keeping the Watchdog Timer security while using the interrupt. To stay in Interrupt and System Reset Mode, WDIE must be set after each interrupt. This should however not be done within the interrupt service routine itself, as this might compromise the safety-function of the Watchdog System Reset mode. If the interrupt is not executed before the next time-out, a System Reset will be applied.

| WDTON <sup>(1)</sup> | WDE | WDIE | Mode                            | Action on Time-out                      |

|----------------------|-----|------|---------------------------------|-----------------------------------------|

| 1                    | 0   | 0    | Stopped                         | None                                    |

| 1                    | 0   | 1    | Interrupt Mode                  | Interrupt                               |

| 1                    | 1   | 0    | System Reset Mode               | Reset                                   |

| 1                    | 1   | 1    | Interrupt and System Reset Mode | Interrupt, then go to System Reset Mode |

| 0                    | Х   | Х    | System Reset Mode               | Reset                                   |

| Table 16-1. | Watchdog | Timer | Configuration |

|-------------|----------|-------|---------------|

|-------------|----------|-------|---------------|

#### Note:

1. WDTON Fuse set to '0' means programmed and '1' means unprogrammed.

#### Bit 4 – WDCE: Watchdog Change Enable

This bit is used in timed sequences for changing WDE and prescaler bits. To clear the WDE bit, and/or change the prescaler bits, WDCE must be set.

Once written to '1', hardware will clear WDCE after four clock cycles.

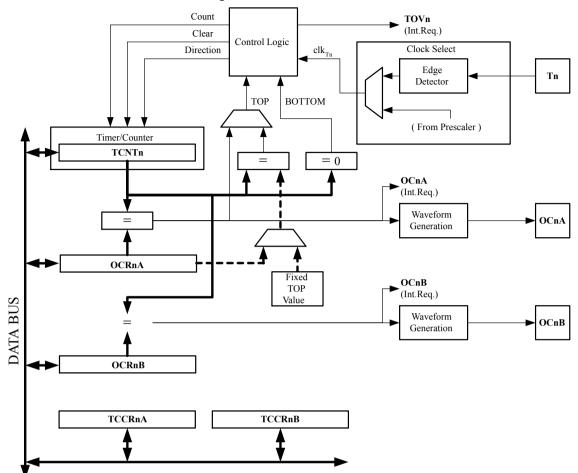

Figure 20-1. 8-bit Timer/Counter Block Diagram

#### **Related Links**

Minimizing Power Consumption on page 63 Register Description on page 151 Pin Configurations on page 14

#### 20.2.1. Definitions

Many register and bit references in this section are written in general form:

- n=1 represents the Timer/Counter number

- x=A,B represents the Output Compare Unit A or B

However, when using the register or bit definitions in a program, the precise form must be used, i.e., TCNT1 for accessing Timer/Counter1 counter value.

The following definitions are used throughout the section:

by the Data Direction Register (DDR) for the port pin. In the Data Direction Register, the bit for the OC1x pin (DDR.OC1x) must be set as output before the OC1x value is visible on the pin. The port override function is independent of the Waveform Generation mode.

The design of the Output Compare pin logic allows initialization of the OC1x register state before the output is enabled. Some TCCR1A.COM1x[1:0] bit settings are reserved for certain modes of operation.

The TCCR1A.COM1x[1:0] bits have no effect on the Input Capture unit.

#### **Related Links**

Modes of Operation on page 145

#### 20.6.1. Compare Output Mode and Waveform Generation

The Waveform Generator uses the TCCR0A.COM0x[1:0] bits differently in Normal, CTC, and PWM modes. For all modes, setting the TCCR0A.COM0x[1:0]=0x0 tells the Waveform Generator that no action on the OC0x Register is to be performed on the next compare match. Refer also to the descriptions of the output modes.

A change of the TCCR0A.COM0x[1:0] bits state will have effect at the first compare match after the bits are written. For non-PWM modes, the action can be forced to have immediate effect by using the TCCR0C.FOC0x strobe bits.

#### 20.7. Modes of Operation

The mode of operation determines the behavior of the Timer/Counter and the Output Compare pins. It is defined by the combination of the Waveform Generation mode bits and Compare Output mode bits in the Timer/Counter control Registers A and B (TCCRnB.WGMn2, TCCRnA.WGMn1, TCCRnA.WGMn0, and TCCRnA.COMnx[1:0]). The Compare Output mode bits do not affect the counting sequence, while the Waveform Generation mode bits do. The COMnx[1:0] bits control whether the PWM output generated should be inverted or not (inverted or non-inverted PWM). For non-PWM modes the COMnx[1:0] bits control whether the output should be set, cleared, or toggled at a compare match (See previous section *Compare Match Output Unit*).

For detailed timing information refer to the following section Timer/Counter Timing Diagrams.

#### 20.7.1. Normal Mode

The simplest mode of operation is the Normal mode (WGMn[2:0] = 0x0). In this mode the counting direction is always up (incrementing), and no counter clear is performed. The counter simply overruns when it passes its maximum 8-bit value (TOP=0xFF) and then restarts from the bottom (0x00). In Normal mode operation, the Timer/Counter Overflow Flag (TOVn) will be set in the same clock cycle in which the TCNTn becomes zero. In this case, the TOVn Flag behaves like a ninth bit, except that it is only set, not cleared. However, combined with the timer overflow interrupt that automatically clears the TOVn Flag, the timer resolution can be increased by software. There are no special cases to consider in the Normal mode, a new counter value can be written anytime.

The Output Compare unit can be used to generate interrupts at some given time. Using the Output Compare to generate waveforms in Normal mode is not recommended, since this will occupy too much of the CPU time.

#### 20.7.2. Clear Timer on Compare Match (CTC) Mode

In Clear Timer on Compare or CTC mode (WGMn[2:0]=0x2), the OCRnA Register is used to manipulate the counter resolution: the counter is cleared to ZERO when the counter value (TCNTn) matches the OCRnA. The OCRnA defines the top value for the counter, hence also its resolution. This mode allows greater control of the compare match output frequency. It also simplifies the counting of external events.

the Analog Comparator Control and Status Register (ACSR). Be aware that changing trigger source can trigger a capture. The Input Capture Flag must therefore be cleared after the change.

Both the Input Capture pin (ICP1) and the Analog Comparator output (ACO) inputs are sampled using the same technique as for the T1 pin. The edge detector is also identical. However, when the noise canceler is enabled, additional logic is inserted before the edge detector, which increases the delay by four system clock cycles. The input of the noise canceler and edge detector is always enabled unless the Timer/ Counter is set in a Waveform Generation mode that uses ICR1 to define TOP.

An Input Capture can be triggered by software by controlling the port of the ICP1 pin.

#### **Related Links**

Timer/Counter0 and Timer/Counter1 Prescalers on page 202 External Clock Source on page 202

#### 21.7.2. Noise Canceler

The noise canceler improves noise immunity by using a simple digital filtering scheme. The noise canceler input is monitored over four samples, and all four must be equal for changing the output that in turn is used by the edge detector.

The noise canceler is enabled by setting the Input Capture Noise Canceler bit in the Timer/Counter Control Register B (TCCR1B.ICNC). When enabled, the noise canceler introduces an additional delay of four system clock cycles between a change applied to the input and the update of the ICR1 Register. The noise canceler uses the system clock and is therefore not affected by the prescaler.

#### 21.7.3. Using the Input Capture Unit

The main challenge when using the Input Capture unit is to assign enough processor capacity for handling the incoming events. The time between two events is critical. If the processor has not read the captured value in the ICR1 Register before the next event occurs, the ICR1 will be overwritten with a new value. In this case the result of the capture will be incorrect.

When using the Input Capture interrupt, the ICR1 Register should be read as early in the interrupt handler routine as possible. Even though the Input Capture interrupt has relatively high priority, the maximum interrupt response time is dependent on the maximum number of clock cycles it takes to handle any of the other interrupt requests.

Using the Input Capture unit in any mode of operation when the TOP value (resolution) is actively changed during operation, is not recommended.

Measurement of an external signal's duty cycle requires that the trigger edge is changed after each capture. Changing the edge sensing must be done as early as possible after the ICR1 Register has been read. After a change of the edge, the Input Capture Flag (ICF) must be cleared by software (writing a logical one to the I/O bit location). For measuring frequency only, the clearing of the ICF Flag is not required (if an interrupt handler is used).

#### 21.8. Output Compare Units

The 16-bit comparator continuously compares TCNT1 with the Output Compare Register (OCR1x). If TCNT equals OCR1x the comparator signals a match. A match will set the Output Compare Flag (TIFR1.OCFx) at the next timer clock cycle. If enabled (TIMSK1.OCIEx = 1), the Output Compare Flag generates an Output Compare interrupt. The OCFx Flag is automatically cleared when the interrupt is executed. Alternatively the OCFx Flag can be cleared by software by writing a logical one to its I/O bit location. The Waveform Generator uses the match signal to generate an output according to operating mode set by the Waveform Generation mode (WGM1[3:0]) bits and Compare Output mode (COM1x[1:0])

### 21.12.11. Output Compare Register 1 B High byte

|        | Name:<br>Offset:<br>Reset:<br>Property | OCR1BH<br>0x8B<br>0x00<br>: - |     |      |         |     |     |     |

|--------|----------------------------------------|-------------------------------|-----|------|---------|-----|-----|-----|

| Bit    | 7                                      | 6                             | 5   | 4    | 3       | 2   | 1   | 0   |

|        |                                        |                               |     | OCR1 | BH[7:0] |     |     |     |

| Access | R/W                                    | R/W                           | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0                                      | 0                             | 0   | 0    | 0       | 0   | 0   | 0   |

Bits 7:0 – OCR1BH[7:0]: Output Compare 1 B High byte Refer to OCR1AL.

upcounting, and set on the compare match while downcounting. In inverting Output Compare mode, the operation is inverted. The dual-slope operation has lower maximum operation frequency than single slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.

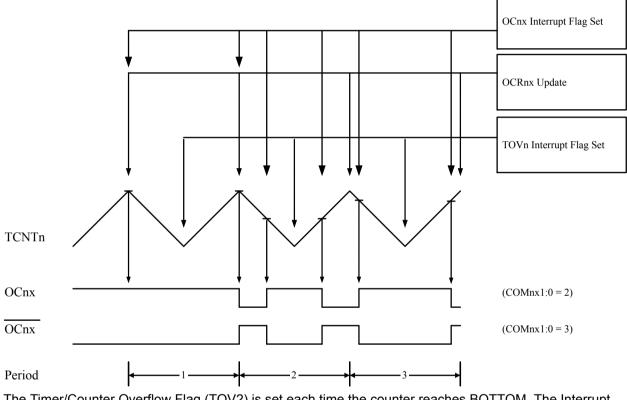

In phase correct PWM mode the counter is incremented until the counter value matches TOP. When the counter reaches TOP, it changes the count direction. The TCNT2 value will be equal to TOP for one timer clock cycle. The timing diagram for the phase correct PWM mode is shown on Figure 23-7 Phase Correct PWM Mode, Timing Diagram. The TCNT2 value is in the timing diagram shown as a histogram for illustrating the dual-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT2 slopes represent compare matches between OCR2x and TCNT2.

#### Figure 23-7. Phase Correct PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches BOTTOM. The Interrupt Flag can be used to generate an interrupt each time the counter reaches the BOTTOM value.

In phase correct PWM mode, the compare unit allows generation of PWM waveforms on the OC2x pin. Setting the COM2x[1:0] bits to two will produce a non-inverted PWM. An inverted PWM output can be generated by setting the COM2x[1:0] to three. TOP is defined as 0xFF when WGM2[2:0] = 0x3, and OCR2A when WGM2[2:0] = 7. The actual OC2x value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by clearing (or setting) the OC2x Register at the compare match between OCR2x and TCNT2 when the counter increments, and setting (or clearing) the OC2x Register at compare match between OCR2x and TCNT2 when the counter decrements. The PWM frequency for the output when using phase correct PWM can be calculated by the following equation:

$$f_{\text{OCnxPCPWM}} = \frac{f_{\text{clk}\_I/0}}{N \cdot 510}$$

## Atmel

| Name:    | TCCR2B |

|----------|--------|

| Offset:  | 0xB1   |

| Reset:   | 0x00   |

| Property | -      |

| Bit    | 7     | 6     | 5 | 4 | 3     | 2    | 1    | 0    |

|--------|-------|-------|---|---|-------|------|------|------|

| [      | FOC2A | FOC2B |   |   | WGM22 | CS22 | CS21 | CS20 |

| Access | R/W   | R/W   |   |   | R/W   | R/W  | R/W  | R/W  |

| Reset  | 0     | 0     |   |   | 0     | 0    | 0    | 0    |

#### Bit 7 – FOC2A: Force Output Compare A

The FOC2A bit is only active when the WGM bits specify a non-PWM mode.

To ensure compatibility with future devices, this bit must be set to zero when TCCR2B is written when operating in PWM mode. When writing a logical one to the FOC2A bit, an immediate Compare Match is forced on the Waveform Generation unit. The OC2A output is changed according to its COM2A1:0 bits setting. Note that the FOC2A bit is implemented as a strobe. Therefore it is the value present in the COM2A1:0 bits that determines the effect of the forced compare.

A FOC2A strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR2A as TOP.

The FOC2A bit is always read as zero.

#### Bit 6 – FOC2B: Force Output Compare B

The FOC2B bit is only active when the WGM bits specify a non-PWM mode.

To ensure compatibility with future devices, this bit must be set to zero when TCCR2B is written when operating in PWM mode. When writing a logical one to the FOC2B bit, an immediate Compare Match is forced on the Waveform Generation unit. The OC2B output is changed according to its COM2B1:0 bits setting. Note that the FOC2B bit is implemented as a strobe. Therefore it is the value present in the COM2B1:0 bits that determines the effect of the forced compare.

A FOC2B strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR2B as TOP.

The FOC2B bit is always read as zero.

#### Bit 3 – WGM22: Waveform Generation Mode

Refer to TCCR2A.

#### Bits 2:0 – CS2n: Clock Select [n = 0..2]

The three Clock Select bits select the clock source to be used by the Timer/Counter.

| Table 23-10. | Clock Select | Bit Description |

|--------------|--------------|-----------------|

|--------------|--------------|-----------------|

| CA22 | CA21 | CS20 | Description                              |

|------|------|------|------------------------------------------|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped). |

| 0    |      | 1    | clk <sub>I/O</sub> /1 (No prescaling)    |

| 0    | 1    | 0    | clk <sub>I/O</sub> /8 (From prescaler)   |

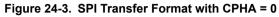

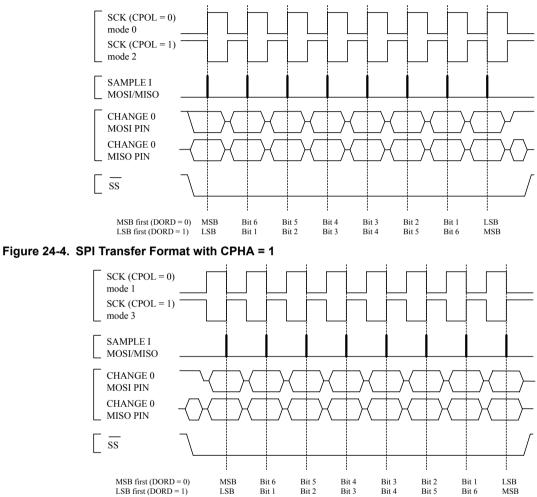

| SPI Mode | Conditions     | Leading Edge     | Trailing Edge   |

|----------|----------------|------------------|-----------------|

| 2        | CPOL=1, CPHA=0 | Sample (Falling) | Setup (Rising)  |

| 3        | CPOL=1, CPHA=1 | Setup (Falling)  | Sample (Rising) |

The SPI data transfer formats are shown in the following figure.

### 24.5. Register Description

#### 24.5.2. SPI Status Register 0

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

Name:

SPSR

Offset:

0x4D

Reset:

0x00

Property:

When addressing as I/O Register: address offset is 0x2D

| Bit    | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|------|------|---|---|---|---|---|-------|

|        | SPIF | WCOL |   |   |   |   |   | SPI2X |

| Access | R    | R    |   |   |   |   | • | R/W   |

| Reset  | 0    | 0    |   |   |   |   |   | 0     |

#### Bit 7 – SPIF: SPI Interrupt Flag

When a serial transfer is complete, the SPIF Flag is set. An interrupt is generated if SPIE in SPCR is set and global interrupts are enabled. If  $\overline{SS}$  is an input and is driven low when the SPI is in Master mode, this will also set the SPIF Flag. SPIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, the SPIF bit is cleared by first reading the SPI Status Register with SPIF set, then accessing the SPI Data Register (SPDR).

#### Bit 6 – WCOL: Write Collision Flag

The WCOL bit is set if the SPI Data Register (SPDR) is written during a data transfer. The WCOL bit (and the SPIF bit) are cleared by first reading the SPI Status Register with WCOL set, and then accessing the SPI Data Register.

#### Bit 0 – SPI2X: Double SPI Speed Bit

When this bit is written to logic one the SPI speed (SCK Frequency) will be doubled when the SPI is in Master mode (refer to Table 24-5 Relationship between SCK and Oscillator Frequency). This means that the minimum SCK period will be two CPU clock periods. When the SPI is configured as Slave, the SPI is only guaranteed to work at fosc/4 or lower.

The SPI interface is also used for program memory and EEPROM downloading or uploading. See *Serial Downloading* for serial programming and verification.

Register Empty interrupt routine must either write new data to UDRn in order to clear UDRE or disable the Data Register Empty interrupt - otherwise, a new interrupt will occur once the interrupt routine terminates.

The Transmit Complete (TXC) Flag bit is set when the entire frame in the Transmit Shift Register has been shifted out and there are no new data currently present in the transmit buffer. The TXC Flag bit is either automatically cleared when a transmit complete interrupt is executed, or it can be cleared by writing a '1' to its bit location. The TXC Flag is useful in half-duplex communication interfaces (like the RS-485 standard), where a transmitting application must enter receive mode and free the communication bus immediately after completing the transmission.

When the Transmit Compete Interrupt Enable (TXCIE) bit in UCSRnB is written to '1', the USART Transmit Complete Interrupt will be executed when the TXC Flag becomes set (provided that global interrupts are enabled). When the transmit complete interrupt is used, the interrupt handling routine does not have to clear the TXC Flag, this is done automatically when the interrupt is executed.

#### 25.7.4. Parity Generator

The Parity Generator calculates the parity bit for the serial frame data. When parity bit is enabled (UCSRnC.UPM[1]=1), the transmitter control logic inserts the parity bit between the last data bit and the first stop bit of the frame that is sent.

#### 25.7.5. Disabling the Transmitter

When writing the TX Enable bit in the USART Control and Status Register n B (UCSRnB.TXEN) to zero, the disabling of the Transmitter will not become effective until ongoing and pending transmissions are completed, i.e., when the Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted. When disabled, the Transmitter will no longer override the TxDn pin.

#### 25.8. Data Reception – The USART Receiver

The USART Receiver is enabled by writing the Receive Enable (RXEN) bit in the UCSRnB Register to '1'. When the Receiver is enabled, the normal pin operation of the RxDn pin is overridden by the USART and given the function as the Receiver's serial input. The baud rate, mode of operation and frame format must be set up once before any serial reception can be done. If synchronous operation is used, the clock on the XCKn pin will be used as transfer clock.

#### 25.8.1. Receiving Frames with 5 to 8 Data Bits

The Receiver starts data reception when it detects a valid start bit. Each bit that follows the start bit will be sampled at the baud rate or XCKn clock, and shifted into the Receive Shift Register until the first stop bit of a frame is received. A second stop bit will be ignored by the Receiver. When the first stop bit is received, i.e., a complete serial frame is present in the Receive Shift Register, the contents of the Shift Register will be moved into the receive buffer. The receive buffer can then be read by reading the UDRn I/O location.

The following code example shows a simple USART receive function based on polling of the Receive Complete (RXC) Flag. When using frames with less than eight bits the most significant bits of the data read from the UDR0 will be masked to zero. The USART 0 has to be initialized before the function can be used. For the assembly code, the received data will be stored in R16 after the code completes.

#### Assembly Code Example

```

USART Receive:

; Wait for data to be received

```

## Atmel

| Baud          | f <sub>osc</sub> = 1.0000MHz |        |          |        | f <sub>osc</sub> = 1.8432MHz |        |          |       | f <sub>osc</sub> = 2.0000MHz |        |          |       |

|---------------|------------------------------|--------|----------|--------|------------------------------|--------|----------|-------|------------------------------|--------|----------|-------|

| Rate<br>[bps] | U2Xn = (                     | )      | U2Xn = 1 |        | U2Xn = 0                     |        | U2Xn = 1 |       | U2Xn = 0                     |        | U2Xn = 1 |       |

| [             | UBRRn                        | Error  | UBRRn    | Error  | UBRRn                        | Error  | UBRRn    | Error | UBRRn                        | Error  | UBRRn    | Error |

| 2400          | 25                           | 0.2%   | 51       | 0.2%   | 47                           | 0.0%   | 95       | 0.0%  | 51                           | 0.2%   | 103      | 0.2%  |

| 4800          | 12                           | 0.2%   | 25       | 0.2%   | 23                           | 0.0%   | 47       | 0.0%  | 25                           | 0.2%   | 51       | 0.2%  |

| 9600          | 6                            | -7.0%  | 12       | 0.2%   | 11                           | 0.0%   | 23       | 0.0%  | 12                           | 0.2%   | 25       | 0.2%  |

| 14.4k         | 3                            | 8.5%   | 8        | -3.5%  | 7                            | 0.0%   | 15       | 0.0%  | 8                            | -3.5%  | 16       | 2.1%  |

| 19.2k         | 2                            | 8.5%   | 6        | -7.0%  | 5                            | 0.0%   | 11       | 0.0%  | 6                            | -7.0%  | 12       | 0.2%  |

| 28.8k         | 1                            | 8.5%   | 3        | 8.5%   | 3                            | 0.0%   | 7        | 0.0%  | 3                            | 8.5%   | 8        | -3.5% |

| 38.4k         | 1                            | -18.6% | 2        | 8.5%   | 2                            | 0.0%   | 5        | 0.0%  | 2                            | 8.5%   | 6        | -7.0% |

| 57.6k         | 0                            | 8.5%   | 1        | 8.5%   | 1                            | 0.0%   | 3        | 0.0%  | 1                            | 8.5%   | 3        | 8.5%  |

| 76.8k         | _                            | _      | 1        | -18.6% | 1                            | -25.0% | 2        | 0.0%  | 1                            | -18.6% | 2        | 8.5%  |

| 115.2k        | -                            | _      | 0        | 8.5%   | 0                            | 0.0%   | 1        | 0.0%  | 0                            | 8.5%   | 1        | 8.5%  |

| 230.4k        | -                            | _      | -        | _      | _                            | _      | 0        | 0.0%  | -                            | _      | -        | -     |

| 250k          | -                            | _      | -        | _      | _                            | _      | _        | _     | -                            | _      | 0        | 0.0%  |

| Max.(1)       | 62.5kbps                     |        | 125kbps  |        | 115.2kbp                     | S      | 230.4kbp | S     | 125kbps                      |        | 250kbps  |       |

Table 25-6. Examples of UBRRn Settings for Commonly Used Oscillator Frequencies

Note: 1. UBRRn = 0, Error = 0.0%

#### Table 25-7. Examples of UBRRn Settings for Commonly Used Oscillator Frequencies

| Baud          | f <sub>osc</sub> = 3.6 | 864MH | Z        |       | f <sub>osc</sub> = 4.0 | 0000MH | Z        |       | f <sub>osc</sub> = 7.3 | 8728MH | z        |       |

|---------------|------------------------|-------|----------|-------|------------------------|--------|----------|-------|------------------------|--------|----------|-------|

| Rate<br>[bps] | U2Xn = 0               |       | U2Xn = 1 |       | U2Xn = 0               |        | U2Xn = 1 |       | U2Xn = 0               |        | U2Xn = 1 |       |

|               | UBRRn                  | Error | UBRRn    | Error | UBRRn                  | Error  | UBRRn    | Error | UBRRn                  | Error  | UBRRn    | Error |

| 2400          | 95                     | 0.0%  | 191      | 0.0%  | 103                    | 0.2%   | 207      | 0.2%  | 191                    | 0.0%   | 383      | 0.0%  |

| 4800          | 47                     | 0.0%  | 95       | 0.0%  | 51                     | 0.2%   | 103      | 0.2%  | 95                     | 0.0%   | 191      | 0.0%  |

| 9600          | 23                     | 0.0%  | 47       | 0.0%  | 25                     | 0.2%   | 51       | 0.2%  | 47                     | 0.0%   | 95       | 0.0%  |

| 14.4k         | 15                     | 0.0%  | 31       | 0.0%  | 16                     | 2.1%   | 34       | -0.8% | 31                     | 0.0%   | 63       | 0.0%  |

| 19.2k         | 11                     | 0.0%  | 23       | 0.0%  | 12                     | 0.2%   | 25       | 0.2%  | 23                     | 0.0%   | 47       | 0.0%  |

| 28.8k         | 7                      | 0.0%  | 15       | 0.0%  | 8                      | -3.5%  | 16       | 2.1%  | 15                     | 0.0%   | 31       | 0.0%  |

| 38.4k         | 5                      | 0.0%  | 11       | 0.0%  | 6                      | -7.0%  | 12       | 0.2%  | 11                     | 0.0%   | 23       | 0.0%  |

| 57.6k         | 3                      | 0.0%  | 7        | 0.0%  | 3                      | 8.5%   | 8        | -3.5% | 7                      | 0.0%   | 15       | 0.0%  |

| 76.8k         | 2                      | 0.0%  | 5        | 0.0%  | 2                      | 8.5%   | 6        | -7.0% | 5                      | 0.0%   | 11       | 0.0%  |

| 115.2k        | 1                      | 0.0%  | 3        | 0.0%  | 1                      | 8.5%   | 3        | 8.5%  | 3                      | 0.0%   | 7        | 0.0%  |

| 230.4k        | 0                      | 0.0%  | 1        | 0.0%  | 0                      | 8.5%   | 1        | 8.5%  | 1                      | 0.0%   | 3        | 0.0%  |

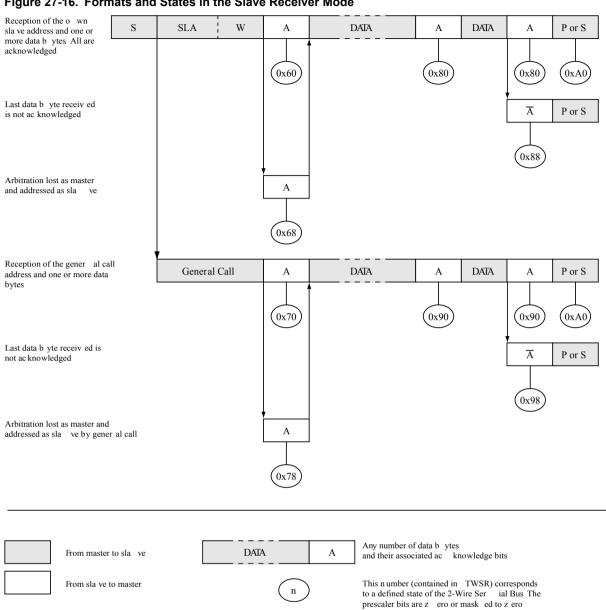

#### Figure 27-16. Formats and States in the Slave Receiver Mode

#### 27.7.4. **Slave Transmitter Mode**

In the Slave Transmitter (ST) mode, a number of data bytes are transmitted to a Master Receiver, as in the figure below. All the status codes mentioned in this section assume that the prescaler bits are zero or are masked to zero.

#### 29.8. Temperature Measurement

The temperature measurement is based on an on-chip temperature sensor that is coupled to a single ended ADC8 channel. Selecting the ADC8 channel by writing ADMUX.MUX[3:0] to '1000' enables the temperature sensor. The internal 1.1V voltage reference must also be selected for the ADC voltage reference source in the temperature sensor measurement. When the temperature sensor is enabled, the ADC converter can be used in single conversion mode to measure the voltage over the temperature sensor.

The measured voltage has a linear relationship to the temperature as described in the following table. The voltage sensitivity is approximately  $1mV/^{\circ}C$ , the accuracy of the temperature measurement is  $\pm 10^{\circ}C$ .

| Temperature | -45°C | +25°C | +85°C |

|-------------|-------|-------|-------|

| Voltage     | 198mV | 273mV | 338mV |

The values described in the table above are typical values. However, due to process variations the temperature sensor output voltage varies from one chip to another. To be capable of achieving more accurate results the temperature measurement can be calibrated in the application software. The software calibration requires that a calibration value is measured and stored in a register or EEPROM for each chip, as a part of the production test. The software calibration can be done utilizing the formula:

$T = \{ [(ADCH << 8) | ADCL] - T_{OS} \} / k$

where ADCH and ADCL are the ADC data registers, k is a fixed coefficient and  $T_{OS}$  is the temperature sensor offset value determined and stored into EEPROM as a part of the production test.

#### 29.9. Register Description

#### 32.4. Read-While-Write and No Read-While-Write Flash Sections

Whether the CPU supports Read-While-Write or if the CPU is halted during a Boot Loader software update is dependent on which address that is being programmed. In addition to the two sections that are configurable by the BOOTSZ Fuses as described above, the Flash is also divided into two fixed sections, the Read-While-Write (RWW) section and the No Read-While-Write (NRWW) section. The limit between the RWW- and NRWW sections is given in the *Boot Loader Parameters* section and Figure 32-2 Memory Sections. The main difference between the two sections is:

- When erasing or writing a page located inside the RWW section, the NRWW section can be read during the operation

- When erasing or writing a page located inside the NRWW section, the CPU is halted during the entire operation

The user software can never read any code that is located inside the RWW section during a Boot Loader software operation. The syntax "Read-While-Write section" refers to which section that is being programmed (erased or written), not which section that actually is being read during a Boot Loader software update.

#### **Related Links**

ATmega168PB Boot Loader Parameters on page 370 ATmega88PB Boot Loader Parameters on page 369

#### 32.4.1. RWW – Read-While-Write Section

If a Boot Loader software update is programming a page inside the RWW section, it is possible to read code from the Flash, but only code that is located in the NRWW section. During an on-going programming, the software must ensure that the RWW section never is being read. If the user software is trying to read code that is located inside the RWW section (i.e., by a call/jmp/lpm or an interrupt) during programming, the software might end up in an unknown state. To avoid this, the interrupts should either be disabled or moved to the Boot Loader section. The Boot Loader section is always located in the NRWW section. The RWW Section Busy bit (RWWSB) in the Store Program Memory Control and Status Register (SPMCSR) will be read as logical one as long as the RWW section is blocked for reading. After a programming is completed, the RWWSB must be cleared by software before reading code located in the RWW section. Please refer to SPMCSR – Store Program Memory Control and Status Register in this chapter for details on how to clear RWWSB.

#### 32.4.2. NRWW – No Read-While-Write Section

The code located in the NRWW section can be read when the Boot Loader software is updating a page in the RWW section. When the Boot Loader code updates the NRWW section, the CPU is halted during the entire Page Erase or Page Write operation.

#### Table 32-1. Read-While-Write Features

| Which Section does the Z-<br>pointer Address during the<br>Programming? | Which Section can be read during Programming? |     | Read-While-Write<br>Supported? |

|-------------------------------------------------------------------------|-----------------------------------------------|-----|--------------------------------|

| RWW Section                                                             | NRWW Section                                  | No  | Yes                            |

| NRWW Section                                                            | None                                          | Yes | No                             |

Table 33-12. Pin Name Mapping

| Signal Name in<br>Programming Mode | Pin Name           | I/O | Function                                                          |

|------------------------------------|--------------------|-----|-------------------------------------------------------------------|

| RDY/BSY                            | PD1                | 0   | 0: Device is busy programming, 1: Device is ready for new command |

| ŌĒ                                 | PD2                | I   | Output Enable (Active low)                                        |

| WR                                 | PD3                | I   | Write Pulse (Active low)                                          |

| BS1                                | PD4                | I   | Byte Select 1 ("0" selects Low byte, "1" selects High byte)       |

| XA0                                | PD5                | I   | XTAL Action Bit 0                                                 |

| XA1                                | PD6                | I   | XTAL Action Bit 1                                                 |

| PAGEL                              | PD7                | I   | Program memory and EEPROM Data Page Load                          |

| BS2                                | PC2                | I   | Byte Select 2 ("0" selects Low byte, "1" selects 2'nd High byte)  |

| DATA                               | {PC[1:0]: PB[5:0]} | I/O | Bi-directional Data bus (Output when OE is low)                   |

#### Table 33-13. Pin Values Used to Enter Programming Mode

| Pin   | Symbol         | Value |

|-------|----------------|-------|

| PAGEL | Prog_enable[3] | 0     |

| XA1   | Prog_enable[2] | 0     |

| XA0   | Prog_enable[1] | 0     |

| BS1   | Prog_enable[0] | 0     |

#### Table 33-14. XA1 and XA0 Coding

| XA1 | XA0 | Action when XTAL1 is Pulsed                                               |

|-----|-----|---------------------------------------------------------------------------|

| 0   | 0   | Load Flash or EEPROM Address (High or low address byte determined by BS1) |

| 0   | 1   | Load Data (High or Low data byte for Flash determined by BS1)             |

| 1   | 0   | Load Command                                                              |

| 1   | 1   | No Action, Idle                                                           |

#### Table 33-15. Command Byte Bit Coding

| Command Byte | Command Executed |

|--------------|------------------|

| 1000 0000    | Chip Erase       |

| 0100 0000    | Write Fuse bits  |

| 0010 0000    | Write Lock bits  |

| 0001 0000    | Write Flash      |

| 0001 0001    | Write EEPROM     |

| Symbo             | l Parameter                               | Condition                                   |                       | Min.                              | Тур. | Max.                  | Units |

|-------------------|-------------------------------------------|---------------------------------------------|-----------------------|-----------------------------------|------|-----------------------|-------|

| V <sub>IH3</sub>  | Input High Voltage,<br>RESET pin as I/O   | V <sub>CC</sub> = 1.8V -                    | 2.4V                  | 0.7V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5 | V     |

|                   |                                           | V <sub>CC</sub> = 2.4V -                    | 5.5V                  | 0.6V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5 |       |

| V <sub>OL</sub>   | Output Low Voltage <sup>(4)</sup>         | I <sub>OL</sub> = 20mA,                     | T <sub>A</sub> =85°C  |                                   |      | 0.9                   |       |

|                   | except RESET pin                          | V <sub>CC</sub> = 5V                        | T <sub>A</sub> =105°C |                                   |      | 1.0                   |       |

|                   |                                           | I <sub>OL</sub> = 10mA,                     | T <sub>A</sub> =85°C  |                                   |      | 0.6                   |       |

|                   |                                           | $V_{\rm CC} = 3V$                           | T <sub>A</sub> =105°C |                                   |      | 0.7                   | V     |

| V <sub>OH</sub>   | Output High Voltage <sup>(3)</sup>        | I <sub>OH</sub> = -20mA,                    | T <sub>A</sub> =85°C  | 4.2                               |      |                       |       |

|                   | except Reset pin                          | $V_{\rm CC} = 5V$                           | T <sub>A</sub> =105°C | 4.1                               |      |                       |       |

|                   |                                           | I <sub>OH</sub> = -10mA,                    | T <sub>A</sub> =85°C  | 2.3                               |      |                       |       |

|                   |                                           | $V_{\rm CC} = 3V$                           | T <sub>A</sub> =105°C | 2.1                               |      |                       | V     |

| IIL               | Input Leakage<br>Current I/O Pin          | V <sub>CC</sub> = 5.5V, p<br>(absolute valu |                       |                                   |      | 1                     | μA    |

| I <sub>IH</sub>   | Input Leakage<br>Current I/O Pin          | V <sub>CC</sub> = 5.5V, p<br>(absolute valu | -                     |                                   |      | 1                     | μA    |

| R <sub>RST</sub>  | Reset Pull-up Resistor                    |                                             |                       | 30                                |      | 60                    | kΩ    |

| R <sub>PU</sub>   | I/O Pin Pull-up Resistor                  |                                             |                       | 20                                |      | 50                    | kΩ    |

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage | $V_{CC} = 5V,$<br>$V_{in} = V_{CC}/2$       |                       |                                   | <10  | 40                    | mV    |

| 1                 | Analog Comparator                         |                                             |                       | -50                               |      | 50                    | nA    |

| I <sub>ACLK</sub> | Input Leakage Current                     | $V_{CC}=5V$<br>,<br>$V_{in}=V_{CC}/2$       |                       | -50                               |      | 50                    |       |

| 4                 | Analog Competator                         |                                             |                       |                                   | 750  |                       | 20    |

| t <sub>ACID</sub> | Analog Comparator<br>Propagation Delay    | $V_{\rm CC} = 2.7 V$                        |                       |                                   | 750  |                       | ns    |

|                   |                                           | $V_{CC} = 4.0V$                             |                       |                                   | 500  |                       |       |

#### Note:

- 1. "Max." means the highest value where the pin is guaranteed to be read as low.

- 2. "Min." means the lowest value where the pin is guaranteed to be read as high.

- 3. Although each I/O port can source more than the test conditions (20mA at V<sub>CC</sub> = 5V, 10mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

1]The sum of all I<sub>OH</sub>, for ports C0 C5, D0- D4, ADC7, RESET should not exceed 150mA.

2] The sum of all I<sub>OH</sub>, for ports B0 B5, D5 D7, ADC6, XTAL1, XTAL2 should not exceed 150mA.

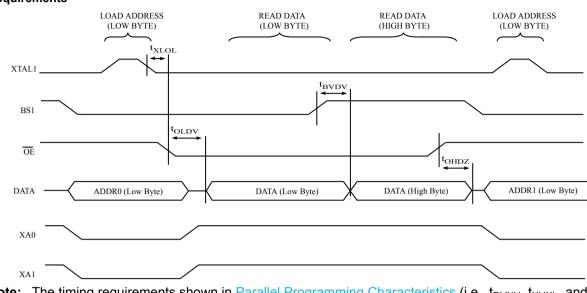

Figure 34-8. Parallel Programming Timing, Reading Sequence (within the Same Page) with Timing Requirements

**Note:** The timing requirements shown in Parallel Programming Characteristics (i.e.,  $t_{DVXH}$ ,  $t_{XHXL}$ , and  $t_{XLDX}$ ) also apply to reading operation.

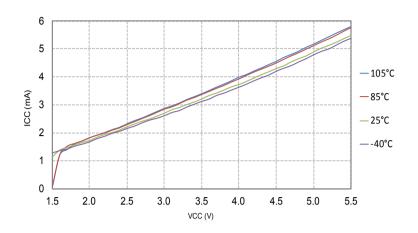

Figure 35-53. ATmega168PB: Active Supply Current vs. V<sub>CC</sub> (Internal RC Oscillator, 8MHz)

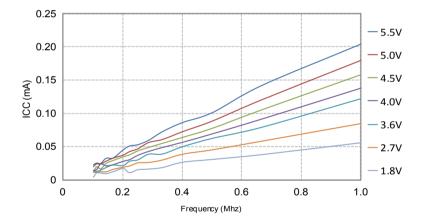

#### 35.2.2. Idle Supply Current Figure 35-54. ATmega168PB: Idle Supply Current vs. Low Frequency (0.1-1.0MHz)

| DATA TRANSF | ER INSTRUCTIC | DNS                               |                                            |       |         |

|-------------|---------------|-----------------------------------|--------------------------------------------|-------|---------|

| Mnemonics   | Operands      | Description                       | Operation                                  | Flags | #Clocks |

| LD          | Rd, - Y       | Load Indirect and Pre-Decrement   | $Y \gets Y - 1,  Rd \gets (Y)$             | None  | 2       |

| LDD         | Rd,Y+q        | Load Indirect with Displacement   | $Rd \gets (Y + q)$                         | None  | 2       |

| LD          | Rd, Z         | Load Indirect                     | $Rd \leftarrow (Z)$                        | None  | 2       |

| LD          | Rd, Z+        | Load Indirect and Post-Increment  | $Rd \gets (Z),  Z \gets Z\text{+}1$        | None  | 2       |

| LD          | Rd, -Z        | Load Indirect and Pre-Decrement   | $Z \leftarrow Z - 1, Rd \leftarrow (Z)$    | None  | 2       |

| LDD         | Rd, Z+q       | Load Indirect with Displacement   | $Rd \leftarrow (Z + q)$                    | None  | 2       |

| LDS         | Rd, k         | Load Direct from SRAM             | $Rd \leftarrow (k)$                        | None  | 2       |

| ST          | X, Rr         | Store Indirect                    | (X) ← Rr                                   | None  | 2       |

| ST          | X+, Rr        | Store Indirect and Post-Increment | $(X) \leftarrow Rr, X \leftarrow X + 1$    | None  | 2       |

| ST          | - X, Rr       | Store Indirect and Pre-Decrement  | $X \leftarrow X - 1,  (X) \leftarrow Rr$   | None  | 2       |

| ST          | Y, Rr         | Store Indirect                    | (Y) ← Rr                                   | None  | 2       |

| ST          | Y+, Rr        | Store Indirect and Post-Increment | $(Y) \leftarrow Rr,  Y \leftarrow Y + 1$   | None  | 2       |

| ST          | - Y, Rr       | Store Indirect and Pre-Decrement  | $Y \leftarrow Y - 1,  (Y) \leftarrow Rr$   | None  | 2       |

| STD         | Y+q,Rr        | Store Indirect with Displacement  | (Y + q) ← Rr                               | None  | 2       |

| ST          | Z, Rr         | Store Indirect                    | (Z) ← Rr                                   | None  | 2       |

| ST          | Z+, Rr        | Store Indirect and Post-Increment | $(Z) \leftarrow Rr, Z \leftarrow Z + 1$    | None  | 2       |

| ST          | -Z, Rr        | Store Indirect and Pre-Decrement  | $Z \leftarrow Z - 1$ , (Z) $\leftarrow Rr$ | None  | 2       |

| STD         | Z+q,Rr        | Store Indirect with Displacement  | $(Z + q) \leftarrow Rr$                    | None  | 2       |

| STS         | k, Rr         | Store Direct to SRAM              | (k) ← Rr                                   | None  | 2       |

| LPM         |               | Load Program Memory               | R0 ← (Z)                                   | None  | 3       |

| LPM         | Rd, Z         | Load Program Memory               | $Rd \leftarrow (Z)$                        | None  | 3       |

| LPM         | Rd, Z+        | Load Program Memory and Post-Inc  | $Rd \leftarrow (Z), Z \leftarrow Z+1$      | None  | 3       |

| SPM         |               | Store Program Memory              | (Z) ← R1:R0                                | None  | -       |

| IN          | Rd, A         | In from I/O Location              | Rd ← I/O (A)                               | None  | 1       |

| OUT         | A, Rr         | Out to I/O Location               | I/O (A) ← Rr                               | None  | 1       |

| PUSH        | Rr            | Push Register on Stack            | $STACK \leftarrow Rr$                      | None  | 2       |

| POP         | Rd            | Pop Register from Stack           | $Rd \gets STACK$                           | None  | 2       |

| MCU CONTROL INSTRUCTIONS |          |                |                                          |       |         |

|--------------------------|----------|----------------|------------------------------------------|-------|---------|

| Mnemonics                | Operands | Description    | Operation                                | Flags | #Clocks |

| NOP                      |          | No Operation   | No Operation                             | None  | 1       |

| SLEEP                    |          | Sleep          | (see specific descr. for Sleep function) | None  | 1       |

| WDR                      |          | Watchdog Reset | (see specific descr. for WDR/timer)      | None  | 1       |

| BREAK                    |          | Break          | For On-chip Debug Only                   | None  | N/A     |