Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | 903                                                       |

| Number of Logic Elements/Cells | 14448                                                     |

| Total RAM Bits                 | 239616                                                    |

| Number of I/O                  | 152                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 256-LBGA                                                  |

| Supplier Device Package        | 256-FBGA (17x17)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c15af256c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Contents**

| Chapter Revision Dates                       | xi   |

|----------------------------------------------|------|

| About This Handbook  How to Contact Altera   |      |

| Typographic Conventions                      |      |

| Section I. Cyclone II Device Family Data She | eet  |

| Revision History                             | 1–1  |

| Chapter 1. Introduction                      |      |

| Introduction                                 | 1 1  |

| Low-Cost Embedded Processing Solutions       |      |

| Low-Cost Embedded Processing Solutions       |      |

| Features                                     |      |

| Referenced Documents                         |      |

| Document Revision History                    |      |

| Document Revision Phistory                   | 1 /  |

| Chapter 2. Cyclone II Architecture           |      |

| Functional Description                       | 2–1  |

| Logic Elements                               |      |

| LE Operating Modes                           |      |

| Logic Array Blocks                           |      |

| LAB Interconnects                            |      |

| LAB Control Signals                          |      |

| MultiTrack Interconnect                      |      |

| Row Interconnects                            | 2–10 |

| Column Interconnects                         | 2–12 |

| Device Routing                               |      |

| Global Clock Network & Phase-Locked Loops    |      |

| Dedicated Clock Pins                         |      |

| Dual-Purpose Clock Pins                      |      |

| Global Clock Network                         |      |

| Global Clock Network Distribution            |      |

| PLLs                                         |      |

| Embedded Memory                              |      |

| Memory Modes                                 |      |

| Clock Modes                                  |      |

| M4K Routing Interface                        |      |

**Altera Corporation**

| Guidelines for IEEE Std. 1149.1 Boundary-Scan Testing  | 14–18 |

|--------------------------------------------------------|-------|

| Boundary-Scan Description Language (BSDL) Support      | 14–19 |

| Conclusion                                             | 14–19 |

| References                                             | 14–19 |

| Document Revision History                              | 14–20 |

| ·                                                      |       |

|                                                        |       |

| Costion VII DCD Loveut Cuidelines                      |       |

| Section VII. PCB Layout Guidelines                     |       |

| Revision History                                       | 14–1  |

|                                                        |       |

| Chapter 15. Package Information for Cyclone II Devices |       |

| Introduction                                           | 15–1  |

| Thermal Resistance                                     | 15–2  |

| Package Outlines                                       |       |

| 144-Pin Plastic Thin Quad Flat Pack (TQFP) – Wirebond  | 15–4  |

| 208-Pin Plastic Quad Flat Pack (PQFP) – Wirebond       |       |

| 240-Pin Plastic Quad Flat Pack (PQFP)                  |       |

| 256-Pin FineLine Ball-Grid Array, Option 2 – Wirebond  |       |

| 484-Pin FineLine BGA, Option 3 – Wirebond              |       |

| 484-Pin Ultra FineLine BGA – Wirebond                  |       |

| 672-Pin FineLine BGA Package, Option 3 – Wirebond      |       |

|                                                        | 13–1/ |

| Table 1–1. Cyclone II FPGA Family Features (Part 2 of 2) |           |           |            |            |        |        |        |

|----------------------------------------------------------|-----------|-----------|------------|------------|--------|--------|--------|

| Feature                                                  | EP2C5 (2) | EP2C8 (2) | EP2C15 (1) | EP2C20 (2) | EP2C35 | EP2C50 | EP2C70 |

| Maximum user I/O pins                                    | 158       | 182       | 315        | 315        | 475    | 450    | 622    |

### Notes to Table 1-1:

- (1) The EP2C15A is only available with the Fast On feature, which offers a faster POR time. This device is available in both commercial and industrial grade.

- (2) The EP2C5, EP2C8, and EP2C20 optionally support the Fast On feature, which is designated with an "A" in the device ordering code. The EP2C5A is only available in the automotive speed grade. The EP2C8A and EP2C20A devices are only available in industrial grade.

- (3) This is the total number of  $18 \times 18$  multipliers. For the total number of  $9 \times 9$  multipliers per device, multiply the total number of  $18 \times 18$  multipliers by 2.

A LAB-wide asynchronous load signal to control the logic for the register's preset signal is not available. The register preset is achieved by using a NOT gate push-back technique. Cyclone II devices can only support either a preset or asynchronous clear signal.

In addition to the clear port, Cyclone II devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals.

# MultiTrack Interconnect

In the Cyclone II architecture, connections between LEs, M4K memory blocks, embedded multipliers, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive™ technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement within the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

The MultiTrack interconnect consists of row (direct link, R4, and R24) and column (register chain, C4, and C16) interconnects that span fixed distances. A routing structure with fixed-length resources for all devices allows predictable and repeatable performance when migrating through different device densities.

### Row Interconnects

Dedicated row interconnects route signals to and from LABs, PLLs, M4K memory blocks, and embedded multipliers within the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks

- R4 interconnects traversing four blocks to the right or left

- R24 interconnects for high-speed access across the length of the device

Table 2–6 summarizes the features supported by the M4K memory.

| Table 2–6. M4K Memory Features                       |                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Feature                                              | Description                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Maximum performance (1)                              | 250 MHz                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Total RAM bits per M4K block (including parity bits) | 4,608                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Configurations supported                             | 4K × 1<br>2K × 2<br>1K × 4<br>512 × 8<br>512 × 9<br>256 × 16<br>256 × 18<br>128 × 32 (not available in true dual-port mode)<br>128 × 36 (not available in true dual-port mode)                                                                                     |  |  |  |  |  |

| Parity bits                                          | One parity bit for each byte. The parity bit, along with internal user logic, can implement parity checking for error detection to ensure data integrity.                                                                                                          |  |  |  |  |  |

| Byte enable                                          | M4K blocks support byte writes when the write port has a data width of 1, 2, 4, 8, 9, 16, 18, 32, or 36 bits. The byte enables allow the input data to be masked so the device can write to specific bytes. The unwritten bytes retain the previous written value. |  |  |  |  |  |

| Packed mode                                          | Two single-port memory blocks can be packed into a single M4K block if each of the two independent block sizes are equal to or less than half of the M4K block size, and each of the single-port memory blocks is configured in single-clock mode.                 |  |  |  |  |  |

| Address clock enable                                 | M4K blocks support address clock enable, which is used to hold the previous address value for as long as the signal is enabled. This feature is useful in handling misses in cache applications.                                                                   |  |  |  |  |  |

| Memory initialization file (.mif)                    | When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.                                                                                                                                                                 |  |  |  |  |  |

| Power-up condition                                   | Outputs cleared                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Register clears                                      | Output registers only                                                                                                                                                                                                                                              |  |  |  |  |  |

| Same-port read-during-write                          | New data available at positive clock edge                                                                                                                                                                                                                          |  |  |  |  |  |

| Mixed-port read-during-write                         | Old data available at positive clock edge                                                                                                                                                                                                                          |  |  |  |  |  |

### Note to Table 2-6:

(1) Maximum performance information is preliminary until device characterization.

Cyclone II devices also use the JTAG port to monitor the logic operation of the device with the SignalTap $^{\$}$  II embedded logic analyzer. Cyclone II devices support the JTAG instructions shown in Table 3–1.

| Table 3–1. Cyclone | II JTAG Instructions | (Part 1 of 2)                                                                                                                                                                                                                                                                   |

|--------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Instruction   | Instruction Code     | Description                                                                                                                                                                                                                                                                     |

| SAMPLE/PRELOAD     | 00 0000 0101         | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap II embedded logic analyzer.                                         |

| EXTEST (1)         | 00 0000 1111         | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                                                             |

| BYPASS             | 11 1111 1111         | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                                                     |

| USERCODE           | 00 0000 0111         | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                       |

| IDCODE             | 00 0000 0110         | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                                                           |

| HIGHZ (1)          | 00 0000 1011         | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                              |

| CLAMP (1)          | 00 0000 1010         | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register. |

| ICR instructions   |                      | Used when configuring a Cyclone II device via the JTAG port with a USB Blaster <sup>™</sup> , ByteBlaster <sup>™</sup> II, MasterBlaster <sup>™</sup> or ByteBlasterMV <sup>™</sup> download cable, or when using a Jam File or JBC File via an embedded processor.             |

| PULSE_NCONFIG      | 00 0000 0001         | Emulates pulsing the nCONFIG pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                     |

# 4. Hot Socketing & Power-On Reset

CII51004-3.1

### Introduction

Cyclone<sup>®</sup> II devices offer hot socketing (also known as hot plug-in, hot insertion, or hot swap) and power sequencing support without the use of any external devices. You can insert or remove a Cyclone II board in a system during system operation without causing undesirable effects to the board or to the running system bus.

The hot-socketing feature lessens the board design difficulty when using Cyclone II devices on printed circuit boards (PCBs) that also contain a mixture of 3.3-, 2.5-, 1.8-, and 1.5-V devices. With the Cyclone II hot-socketing feature, you no longer need to ensure a proper power-up sequence for each device on the board.

The Cyclone II hot-socketing feature provides:

- Board or device insertion and removal without external components or board manipulation

- Support for any power-up sequence

- Non-intrusive I/O buffers to system buses during hot insertion

This chapter also discusses the power-on reset (POR) circuitry in Cyclone II devices. The POR circuitry keeps the devices in the reset state until the  $V_{\rm CC}$  is within operating range.

# Cyclone II Hot-Socketing Specifications

Cyclone II devices offer hot-socketing capability with all three features listed above without any external components or special design requirements. The hot-socketing feature in Cyclone II devices offers the following:

- The device can be driven before power-up without any damage to the device itself.

- I/O pins remain tri-stated during power-up. The device does not drive out before or during power-up, thereby affecting other buses in operation.

Table 5–19. M4K Block Internal Timing Microparameters (Part 2 of 3) -6 Speed Grade (1) -7 Speed Grade (2) -8 Speed Grade (3) Parameter Unit Min Max Min Max Min Max TM4KBEH 234 267 267 ps 250 267 ps TM4KDATAASU 35 46 46 ps 40 46 ps TM4KDATAAH 234 267 267 ps 250 267 ps TM4KADDRASU 35 46 46 ps 40 46 ps TM4KADDRAH 234 267 267 ps 250 267 ps TM4KDATABSU 35 46 46 ps 40 46 ps TM4KDATABH 234 267 267 ps 250 267 ps TM4KRADDRBSU 46 35 46 ps 40 46 ps TM4KRADDRBH 234 267 267 ps 250 267 ps TM4KDATACO1 724 445 826 445 930 466 ps 466 466 ps 2345 TM4KDATACO2 3680 2234 4157 2234 4636 ps 2345 2345 ps TM4KCLKH 1923 2769 2769 ps 2307 2769 ps ps TM4KCLKL 1923 2769 2769 2307 2769 ps

= 1000 / (1000/toggle rate at default load + derating factor \* load value in pF/1000)

For example, the output toggle rate at 0 pF (default) load for SSTL-18 Class II 18mA I/O standard is 270 MHz on a -6 device column I/O pin. The derating factor is 29 ps/pF. For a 10pF load, the toggle rate is calculated as:

$1000 / (1000/270 + 29 \times 10/1000) = 250 (MHz)$

Tables 5–44 through 5–46 show the I/O toggle rates for Cyclone II devices.

| Table 5–44. Maximum Input Clock Toggle Rate on Cyclone II Devices (Part 1 of 2) |                                                             |                      |                      |                      |                      |                      |                           |                      |                      |  |

|---------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------------|----------------------|----------------------|--|

|                                                                                 | Maximum Input Clock Toggle Rate on Cyclone II Devices (MHz) |                      |                      |                      |                      |                      |                           |                      |                      |  |

| I/O Standard                                                                    | Column I/O Pins                                             |                      |                      | Row I/O Pins         |                      |                      | Dedicated Clock<br>Inputs |                      |                      |  |

| ·                                                                               | -6<br>Speed<br>Grade                                        | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade      | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade |  |

| LVTTL                                                                           | 450                                                         | 405                  | 360                  | 450                  | 405                  | 360                  | 420                       | 380                  | 340                  |  |

| 2.5V                                                                            | 450                                                         | 405                  | 360                  | 450                  | 405                  | 360                  | 450                       | 405                  | 360                  |  |

| 1.8V                                                                            | 450                                                         | 405                  | 360                  | 450                  | 405                  | 360                  | 450                       | 405                  | 360                  |  |

| 1.5V                                                                            | 300                                                         | 270                  | 240                  | 300                  | 270                  | 240                  | 300                       | 270                  | 240                  |  |

| LVCMOS                                                                          | 450                                                         | 405                  | 360                  | 450                  | 405                  | 360                  | 420                       | 380                  | 340                  |  |

| SSTL_2_CLASS_I                                                                  | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| SSTL_2_CLASS_II                                                                 | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| SSTL_18_CLASS_I                                                                 | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| SSTL_18_CLASS_II                                                                | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| 1.5V_HSTL_CLASS_I                                                               | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| 1.5V_HSTL_CLASS_II                                                              | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| 1.8V_HSTL_CLASS_I                                                               | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| 1.8V_HSTL_CLASS_II                                                              | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| PCI                                                                             | _                                                           | _                    | _                    | 350                  | 315                  | 280                  | 350                       | 315                  | 280                  |  |

| PCI-X                                                                           | _                                                           | _                    | _                    | 350                  | 315                  | 280                  | 350                       | 315                  | 280                  |  |

| DIFFERENTIAL_SSTL_2_<br>CLASS_I                                                 | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| DIFFERENTIAL_SSTL_2_<br>CLASS_II                                                | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| Table 5–44. Maximum Input Clock Toggle Rate on Cyclone II Devices (Part 2 of 2) |                                                             |                      |                      |                      |                      |                      |                           |                      |                      |  |

|---------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------------|----------------------|----------------------|--|

|                                                                                 | Maximum Input Clock Toggle Rate on Cyclone II Devices (MHz) |                      |                      |                      |                      |                      |                           |                      |                      |  |

| I/O Standard                                                                    | Column I/O Pins                                             |                      |                      | Row I/O Pins         |                      |                      | Dedicated Clock<br>Inputs |                      |                      |  |

| , o otamana                                                                     | -6<br>Speed<br>Grade                                        | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade      | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade |  |

| DIFFERENTIAL_SSTL_18_<br>CLASS_I                                                | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| DIFFERENTIAL_SSTL_18_<br>CLASS_II                                               | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| 1.8V_DIFFERENTIAL_HSTL_<br>CLASS_I                                              | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| 1.8V_DIFFERENTIAL_HSTL_<br>CLASS_II                                             | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| 1.5V_DIFFERENTIAL_HSTL_<br>CLASS_I                                              | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| 1.5V_DIFFERENTIAL_HSTL_<br>CLASS_II                                             | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |

| LVPECL                                                                          | _                                                           | _                    | _                    | _                    | _                    | _                    | 402                       | 402                  | 402                  |  |

| LVDS                                                                            | 402                                                         | 402                  | 402                  | 402                  | 402                  | 402                  | 402                       | 402                  | 402                  |  |

| 1.2V_HSTL                                                                       | 110                                                         | 90                   | 80                   | _                    | _                    | _                    | 110                       | 90                   | 80                   |  |

| 1.2V_DIFFERENTIAL_HSTL                                                          | 110                                                         | 90                   | 80                   | _                    | _                    | _                    | 110                       | 90                   | 80                   |  |

| Table 5–45. Maximum Output Clock Toggle Rate on Cyclone II Devices (Part 1 of 4) |          |                                                              |                      |                      |                      |                      |                      |                            |                      |                      |

|----------------------------------------------------------------------------------|----------|--------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------------|----------------------|----------------------|

|                                                                                  |          | Maximum Output Clock Toggle Rate on Cyclone II Devices (MHz) |                      |                      |                      |                      |                      |                            | VIHz)                |                      |

| I/O Standard                                                                     | Drive    |                                                              |                      |                      | Row I/O Pins (1)     |                      |                      | Dedicated Clock<br>Outputs |                      |                      |

| ,,o otaniana                                                                     | Strength | -6<br>Speed<br>Grade                                         | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade       | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade |

| LVTTL                                                                            | 4 mA     | 120                                                          | 100                  | 80                   | 120                  | 100                  | 80                   | 120                        | 100                  | 80                   |

|                                                                                  | 8 mA     | 200                                                          | 170                  | 140                  | 200                  | 170                  | 140                  | 200                        | 170                  | 140                  |

|                                                                                  | 12 mA    | 280                                                          | 230                  | 190                  | 280                  | 230                  | 190                  | 280                        | 230                  | 190                  |

|                                                                                  | 16 mA    | 290                                                          | 240                  | 200                  | 290                  | 240                  | 200                  | 290                        | 240                  | 200                  |

|                                                                                  | 20 mA    | 330                                                          | 280                  | 230                  | 330                  | 280                  | 230                  | 330                        | 280                  | 230                  |

|                                                                                  | 24 mA    | 360                                                          | 300                  | 250                  | 360                  | 300                  | 250                  | 360                        | 300                  | 250                  |

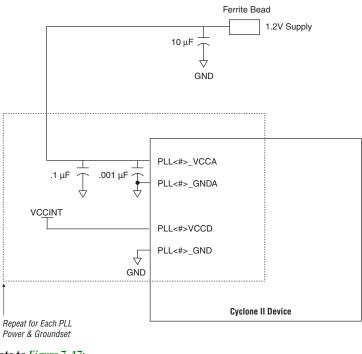

Figure 7–17. PLL Power Schematic for Cyclone II PLLs

Note to Figure 7–17:

(1) Applies to PLLs 1 through 4.

### **VCCD & GND**

The digital power and ground pins are labeled VCCD\_ PLL</br/>

PLL (PLL number) and GND\_PLL</br/>

PLL (PLL number). The VCCD pin supplies the power for the digital circuitry in the PLL. Connect these VCCD pins to the quietest digital supply on the board. In most systems, this is the digital 1.2-V supply supplied to the device's  $V_{CCINT}$  pins. Connect the VCCD pins to a power supply even if you do not use the PLL. When connecting the  $V_{CCD}$  pins to  $V_{CCINT}$ , you do not need any filtering or isolation. You can connect the GND pins directly to the same ground plane as the device's digital ground. See Figure 7–17.

## Conclusion

Cyclone II device PLLs provide you with complete control of device clocks and system timing. These PLLs support clock multiplication/division, phase shift, and programmable duty cycle for your cost-sensitive clock synthesis applications.

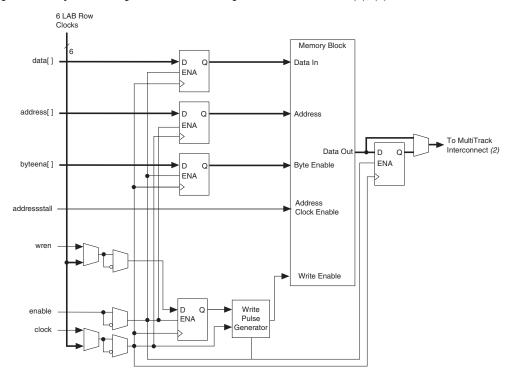

Figure 8–20. Cyclone II Single-Clock Mode in Single-Port Mode Notes (1), (2)

Notes to Figure 8-20:

- (1) Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

- (2) See the Cyclone II Device Family Data Sheet in Volume 1 of the Cyclone II Device Handbook for more information on the MultiTrack interconnect.

## **Power-Up Conditions & Memory Initialization**

The Cyclone II memory block outputs always power-up to zero, regardless of whether the output registers are used or bypassed. Even if an MIF pre-loads the contents of the memory block, the outputs still power up cleared. For example, if address 0 is pre-initialized to FF, M4K blocks power up with the output at 00. A subsequent read after power up from address 0 outputs the pre-initialized value of FF.

# Selectable I/O Standards in Cyclone II Devices

CII51010-2.4

### Introduction

The proliferation of I/O standards and the need for improved I/O performance have made it critical that low-cost devices have flexible I/O capabilities. Selectable I/O capabilities such as SSTL-18, SSTL-2, and LVDS compatibility allow Cyclone® II devices to connect to other devices on the same printed circuit board (PCB) that may require different operating and I/O voltages. With these aspects of implementation easily manipulated using the Altera® Quartus® II software, the Cyclone II device family allows you to use low cost FPGAs while keeping pace with increasing design complexity.

This chapter is a guide to understanding the input and output capabilities of the Cyclone II devices, including:

- Supported I/O standards

- Cyclone II I/O banks

- Programmable current drive strength

- I/O termination

- Pad placement and DC guidelines

For information on hot socketing, refer to the *Hot Socketing & Power-On Reset* chapter in volume 1 of the *Cyclone II Device Handbook*.

For information on ESD specifications, refer to the *Altera Reliability Report*.

# Supported I/O Standards

Cyclone II devices support the I/O standards shown in Table 10–1.

For more details on the I/O standards discussed in this section, including target data rates and voltage values for each I/O standard, refer to the *DC Characteristics and Timing Specifications* chapter in volume 1 of the *Cyclone II Device Handbook*.

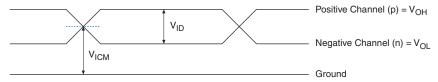

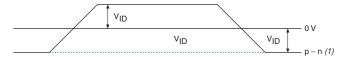

Figure 11-4. Receiver Input Waveforms for the LVDS Differential I/O Standard

### Single-Ended Waveform

#### Differential Waveform (Mathematical Function of Positive & Negative Channel)

Note to Figure 11-4:

(1) The p-n waveform is a function of the positive channel (p) and the negative channel (n).

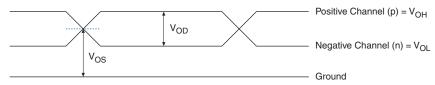

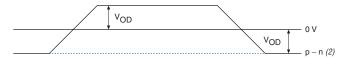

Figure 11–5. Transmitter Output Waveform for the LVDS Differential I/O Standard Note (2)

### Single-Ended Waveform

### Differential Waveform (Mathematical Function of Positive & Negative Channel)

*Notes to Figure 11–5:*

- (1) The V<sub>OD</sub> specifications apply at the resistor network output.

- The p n waveform is a function of the positive channel (p) and the negative channel (n).

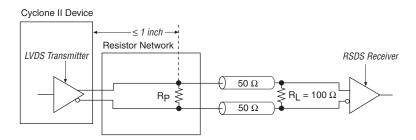

Figure 11–8. RSDS Single Resistor Network Note (1)

Note to Figure 11–8: (1)  $R_p = 100 \Omega$

### RSDS Software Support

When designing for the RSDS I/O standard, assign the RSDS I/O standard to the I/O pins intended for RSDS in the Quartus® II software. Contact Altera Applications for reference designs.

### mini-LVDS Standard Support in Cyclone II Devices

The mini-LVDS specification defines its use in chip-to-chip applications between the timing controller and the column drivers on display panels. Cyclone II devices meet the Texas Instruments mini-LVDS Interface Specification and support the mini-LVDS output standard. Table 11–3 shows the mini-LVDS electrical characteristics for Cyclone II devices.

| Table 11–3.                     | Table 11–3. mini-LVDS Electrical Characteristics for Cyclone II Devices Note (1) |                        |       |      |       |       |  |  |

|---------------------------------|----------------------------------------------------------------------------------|------------------------|-------|------|-------|-------|--|--|

| Symbol                          | Parameters                                                                       | Condition              | Min   | Тур  | Max   | Units |  |  |

| V <sub>CCIO</sub>               | Output supply voltage                                                            |                        | 2.375 | 2.5  | 2.625 | V     |  |  |

| V <sub>OD</sub> (2)             | Differential output voltage                                                      | R <sub>L</sub> = 100 Ω | 300   |      | 600   | mV    |  |  |

| V <sub>OS</sub> (3)             | Output offset voltage                                                            | $R_L = 100 \Omega$     | 1125  | 1250 | 1375  | mV    |  |  |

| T <sub>r</sub> / T <sub>f</sub> | Transition time                                                                  | 20% to 80%             |       |      | 500   | ps    |  |  |

*Notes to Table 11–3:*

- (1) The  $V_{OD}$  specifications apply at the resistor network output.

- $(2) V_{OD} = V_{OH} V_{OL}.$

- (3)  $V_{OS} = (V_{OH} + V_{OL}) / 2$ .

DATA3, you can leave the corresponding bit 3 line blank in the Quartus II software. On the printed circuit board (PCB), leave the DATA3 line from the enhanced configuration device unconnected. Use the Quartus II **Convert Programming Files** window (Tools menu) setup for this scheme.

You can also connect two FPGAs to one of the configuration device's DATA pins while the other DATA pins drive one device each. For example, you could use the 2-bit PS mode to drive two FPGAs with DATA bit 0 (two EP2C5 devices) and the third device (an EP2C8 device) with DATA bit 1. In this example, the memory space required for DATA bit 0 is the sum of the SOF file size for the two EP2C5 devices.

1,223,980 bits + 1,223,980 bits = 2,447,960 bits

The memory space required for DATA bit 1 is the SOF file size for on EP2C8 device (1,983,792 bits). Since the memory space required for DATA bit 0 is larger than the memory space required for DATA bit 1, the size of the POF file is  $2 \times 2,447,960 = 4,895,920$ .

For more information on using *n*-bit PS modes with enhanced configuration devices, see the *Using Altera Enhanced Configuration Devices* in the *Configuration Handbook*.

When configuring SRAM-based devices using n-bit PS modes, use Table 13–8 to select the appropriate configuration mode for the fastest configuration times.

| Table 13–8. Recommended Configu | Table 13–8. Recommended Configuration Using n-Bit PS Modes |  |  |  |  |  |

|---------------------------------|------------------------------------------------------------|--|--|--|--|--|

| Number of Devices (1)           | Recommended Configuration Mode                             |  |  |  |  |  |

| 1                               | 1-bit PS                                                   |  |  |  |  |  |

| 2                               | 2-bit PS                                                   |  |  |  |  |  |

| 3                               | 4-bit PS                                                   |  |  |  |  |  |

| 4                               | 4-bit PS                                                   |  |  |  |  |  |

| 5                               | 8-bit PS                                                   |  |  |  |  |  |

| 6                               | 8-bit PS                                                   |  |  |  |  |  |

| 7                               | 8-bit PS                                                   |  |  |  |  |  |

| 8                               | 8-bit PS                                                   |  |  |  |  |  |

Note to Table 13-8:

Assume that each DATA line is only configuring one device, not a daisy chain of devices. feature. To use this feature successfully, set the MSEL[1..0] pins of the master Cyclone II device to select the AS configuration scheme or fast AS configuration scheme (see Table 13–1).

The Quartus II software version 4.1 and higher supports serial configuration device ISP through an FPGA JTAG interface using a JIC file.

The serial configuration device in-system programming through the Cyclone II JTAG interface has three stages, which are described in the following sections.

### Loading the Serial Flash Loader Design

The serial flash loader design is a design inside the Cyclone II device that bridges the JTAG interface and AS interface inside the Cyclone II device using glue logic.

The intelligent host uses the JTAG interface to configure the master Cyclone II device with a serial flash loader design. The serial flash loader design allows the master Cyclone II device to control the access of four serial configuration device pins, also known as the Active Serial Memory Interface (ASMI) pins, through the JTAG interface. The ASMI pins are the serial clock input (DCLK), serial data output (DATA), AS data input (ASDI), and an active-low chip select (nCS) pins.

If you configure a master Cyclone II device with a serial flash loader design, the master Cyclone II device can enter user mode even though the slave devices in the multiple device chain are not being configured. The master Cyclone II device can enter user mode with a serial flash loader design even though the CONF\_DONE signal is externally held low by the other slave devices in chain. Figure 13–25 shows the JTAG configuration of a single Cyclone II device with a serial flash loader design.

# Document Revision History

Table 13–14 shows the revision history for this document.

| Table 13–14. De               | Table 13–14. Document Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Date &<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Summary of Changes                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| February 2007<br>v3.1         | <ul> <li>Added document revision history.</li> <li>Added Note (1) to Table 13–1.</li> <li>Added Note (1) to Table 13–4.</li> <li>Updated Figure 13–3.</li> <li>Updated Figures 13–6 and 13–7.</li> <li>Updated Note (2) to Figure 13–13.</li> <li>Updated "Single Device PS Configuration Using a Configuration Device" section.</li> <li>Updated Note (2) to Figure 13–14.</li> <li>Updated Note (2) to Figure 13–15.</li> <li>Updated Note (2) to Figure 13–16.</li> <li>Updated Note (2) to Figure 13–17.</li> <li>Updated Note (4) to Figure 13–21.</li> <li>Updated Note (2) to Figure 13–25.</li> </ul>                                                                                                       | <ul> <li>Changed unit 'kw' to 'kΩ' in Figures 13–6 and 13–7.</li> <li>Added note about serial configuration devices supporting 20 MHz and 40 MHz DCLK.</li> <li>Added infomation about the need for a resistor on nCONFIG if reconfiguration is required.</li> <li>Added information about MSEL [10] internal pull-down resistor value.</li> </ul> |  |  |  |  |  |  |

| July 2005 v2.0                | <ul> <li>Updated "Configuration Stage" section.</li> <li>Updated "PS Configuration Using a Download Cable" section.</li> <li>Updated Figures 13–8, 13–12, and 13–18.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| November 2004<br>v1.1         | <ul> <li>Updated "Configuration Stage" section in "Single Device AS Configuration" section.</li> <li>Updated "Initialization Stage" section in "Single Device AS Configuration" section.</li> <li>Updated Figure 13-8.</li> <li>Updated "Initialization Stage" section in "Single Device PS Configuration Using a MAX II Device as an External Host" section.</li> <li>Updated Table 13-7.</li> <li>Updated "Single Device PS Configuration Using a Configuration Device" section.</li> <li>Updated "Initialization Stage" section in "Single Device PS Configuration Using a Configuration Device" section.</li> <li>Updated Figure 13-18.</li> <li>Updated "Single Device JTAG Configuration" section.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| June 2004 v1.0                | Added document to the Cyclone II Device Handbook.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

Tables 15–5 and 15–6 show the package information and package outline figure references, respectively, for the 144-pin TQFP package.

| Table 15–5. 144-Pin TQFP Package Information |                                                |  |  |

|----------------------------------------------|------------------------------------------------|--|--|

| Description                                  | Specification                                  |  |  |

| Ordering code reference                      | Т                                              |  |  |

| Package acronym                              | TQFP                                           |  |  |

| Lead frame material                          | Copper                                         |  |  |

| Lead finish (plating)                        | Regular: 85Sn:15Pb (Typ.)<br>Pb-free: Matte Sn |  |  |

| JEDEC Outline Reference                      | MS-026 Variation: BFB                          |  |  |

| Maximum lead coplanarity                     | 0.003 inches (0.08mm)                          |  |  |

| Weight                                       | 1.3 g                                          |  |  |

| Moisture sensitivity level                   | Printed on moisture barrier bag                |  |  |

| Table 15–6. 144-Pin TQFP Package Outline Dimensions |            |      |            |  |  |

|-----------------------------------------------------|------------|------|------------|--|--|

| Symbol -                                            | Millimeter |      |            |  |  |

|                                                     | Min.       | Nom. | Max.       |  |  |

| Α                                                   | _          | _    | 1.60       |  |  |

| A1                                                  | 0.05       | -    | 0.15       |  |  |

| A2                                                  | 1.35       | 1.40 | 1.45       |  |  |

| D                                                   | 22.00 BSC  |      |            |  |  |

| D1                                                  | 20.00 BSC  |      |            |  |  |

| E                                                   | 22.00 BSC  |      |            |  |  |

| E1                                                  | 20.00 BSC  |      |            |  |  |

| L                                                   | 0.45       | 0.60 | 0.75       |  |  |

| L1                                                  | 1.00 REF   |      |            |  |  |

| S                                                   | 0.20       | _    | _          |  |  |

| b                                                   | 0.17       | 0.22 | 0.27       |  |  |

| С                                                   | 0.09       | _    | 0.20       |  |  |

| е                                                   | 0.50 BSC   |      |            |  |  |

| θ                                                   | 0°         | 3.5° | <b>7</b> ° |  |  |

## 208-Pin Plastic Quad Flat Pack (PQFP) - Wirebond

- All dimensions and tolerances conform to ASME Y14.5M 1994.

- Controlling dimension is in millimeters.

- Pin 1 may be indicated by an ID dot in its proximity on package surface.

Tables 15–7 and 15–8 show the package information and package outline figure references, respectively, for the 208-pin PQFP package.

| Table 15–7. 208-Pin PQFP Package Information |                                                |  |  |  |

|----------------------------------------------|------------------------------------------------|--|--|--|

| Description                                  | Specification                                  |  |  |  |

| Ordering code reference                      | Q                                              |  |  |  |

| Package acronym                              | PQFP                                           |  |  |  |

| Lead material                                | Copper                                         |  |  |  |

| Lead finish (plating)                        | Regular: 85Sn:15Pb (Typ.)<br>Pb-free: Matte Sn |  |  |  |

| JEDEC Outline Reference                      | MS-029 Variation: FA-1                         |  |  |  |

| Maximum lead coplanarity                     | 0.003 inches (0.08 mm)                         |  |  |  |

| Weight                                       | 5.7 g                                          |  |  |  |

| Moisture sensitivity level                   | Printed on moisture barrier bag                |  |  |  |

| Table 15–8. 208-Pin PQFP Package Outline Dimensions (Part 1 of 2) |            |      |      |  |  |

|-------------------------------------------------------------------|------------|------|------|--|--|

| Symbol                                                            | Millimeter |      |      |  |  |

|                                                                   | Min.       | Nom. | Max. |  |  |

| Α                                                                 | _          | _    | 4.10 |  |  |

| A1                                                                | 0.25       | _    | 0.50 |  |  |

| A2                                                                | 3.20       | 3.40 | 3.60 |  |  |

| D                                                                 | 30.60 BSC  |      |      |  |  |

| D1                                                                | 28.00 BSC  |      |      |  |  |

| E                                                                 | 30.60 BSC  |      |      |  |  |

| E1                                                                | 28.00 BSC  |      |      |  |  |

| L                                                                 | 0.50       | 0.60 | 0.75 |  |  |

| L1                                                                | 1.30 REF   |      |      |  |  |

| S                                                                 | 0.20       | _    | _    |  |  |

| b                                                                 | 0.17       | _    | 0.27 |  |  |

| С                                                                 | 0.09       | _    | 0.20 |  |  |