### Intel - EP2C15AF256C8N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | 903                                                       |

| Number of Logic Elements/Cells | 14448                                                     |

| Total RAM Bits                 | 239616                                                    |

| Number of I/O                  | 152                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 256-LBGA                                                  |

| Supplier Device Package        | 256-FBGA (17x17)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c15af256c8n |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ]   | nternal Timing                                        | 5-18 |

|-----|-------------------------------------------------------|------|

| (   | Cyclone II Clock Timing Parameters                    | 5-23 |

|     | Clock Network Skew Adders                             |      |

| ]   | OE Programmable Delay                                 | 5-30 |

|     | Default Capacitive Loading of Different I/O Standards |      |

|     | /O Delays                                             |      |

| l   | Maximum Input and Output Clock Rate                   | 5-46 |

|     | High Speed I/O Timing Specifications                  |      |

|     | External Memory Interface Specifications              |      |

| J   | TAG Timing Specifications                             | 5-64 |

| j   | PLL Timing Specifications                             | 5-66 |

|     | y Cycle Distortion                                    |      |

|     | DCD Measurement Techniques                            |      |

|     | erenced Documents                                     |      |

| Doc | rument Revision History                               | 5-74 |

|     |                                                       |      |

# Chapter 6. Reference & Ordering Information

| Software                  | 5–1 |

|---------------------------|-----|

| Device Pin-Outs           |     |

| Ordering Information      | 5–1 |

| Document Revision History |     |

|                           | -   |

# Section II. Clock Management

| Revision History |  | 6– | -1 |

|------------------|--|----|----|

|------------------|--|----|----|

# Chapter 7. PLLs in Cyclone II Devices

| Introduction                                 | 7–1  |

|----------------------------------------------|------|

| Cyclone II PLL Hardware Overview             | 7–2  |

| PLL Reference Clock Generation               | 7–6  |

| Clock Feedback Modes                         | 7–10 |

| Normal Mode                                  | 7–10 |

| Zero Delay Buffer Mode                       | 7–11 |

| No Compensation Mode                         | 7–12 |

| Source-Synchronous Mode                      |      |

| Hardware Features                            |      |

| Clock Multiplication & Division              | 7–14 |

| Programmable Duty Cycle                      |      |

| Phase-Shifting Implementation                |      |

| Control Signals                              | 7–17 |

| Manual Clock Switchover                      |      |

| Clocking                                     | 7–21 |

| Global Clock Network                         | 7–21 |

| Clock Control Block                          | 7–24 |

| Global Clock Network Clock Source Generation | 7–26 |

| Global Clock Network Power Down              | 7–28 |

- Chapter 10. Selectable I/O Standards in Cyclone II Devices Revised: *February 2008* Part number: *CII51010-2.4*

- Chapter 11. High-Speed Differential Interfaces in Cyclone II Devices Revised: *February* 2007 Part number: *CII51011-2.2*

- Chapter 12. Embedded Multipliers in Cyclone II Devices Revised: *February* 2007 Part number: *CII51012-1.2*

- Chapter 13. Configuring Cyclone II Devices Revised: February 2007 Part number: CII51013-3.1

- Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Revised: *February* 2007 Part number: *CII51014-2.1*

- Chapter 15. Package Information for Cyclone II Devices Revised: *February* 2007 Part number: *CII51015-2.3*

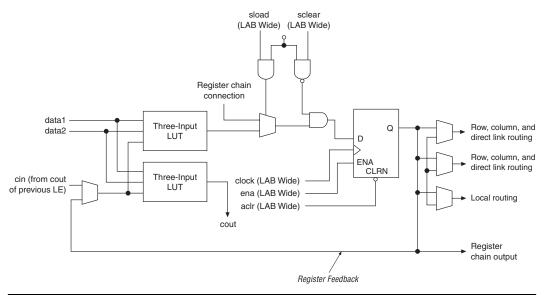

The Quartus II Compiler automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 16 LEs by automatically linking LABs in the same column. For enhanced fitting, a long carry chain runs vertically, which allows fast horizontal connections to M4K memory blocks or embedded multipliers through direct link interconnects. For example, if a design has a long carry chain in a LAB column next to a column of M4K memory blocks, any LE output can feed an adjacent M4K memory block through the direct link interconnect. Whereas if the carry chains ran horizontally, any LAB not next to the column of M4K memory blocks would use other row or column interconnects to drive a M4K memory block. A carry chain continues as far as a full column.

## **Global Clock Network Distribution**

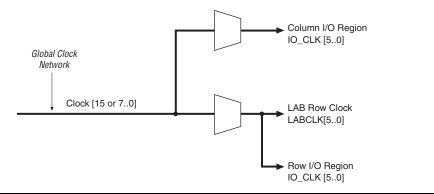

Cyclone II devices contains 16 global clock networks. The device uses multiplexers with these clocks to form six-bit buses to drive column IOE clocks, LAB row clocks, or row IOE clocks (see Figure 2–14). Another multiplexer at the LAB level selects two of the six LAB row clocks to feed the LE registers within the LAB.

Figure 2–14. Global Clock Network Multiplexers

LAB row clocks can feed LEs, M4K memory blocks, and embedded multipliers. The LAB row clocks also extend to the row I/O clock regions.

IOE clocks are associated with row or column block regions. Only six global clock resources feed to these row and column regions. Figure 2–15 shows the I/O clock regions.

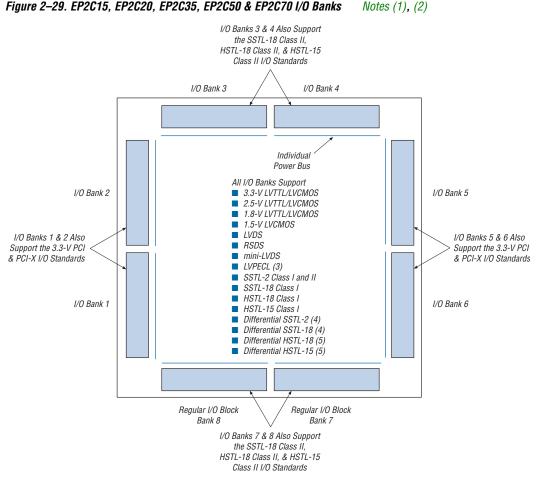

#### Notes to Figure 2–29:

- (1) This is a top view of the silicon die.

- (2) This is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (5) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

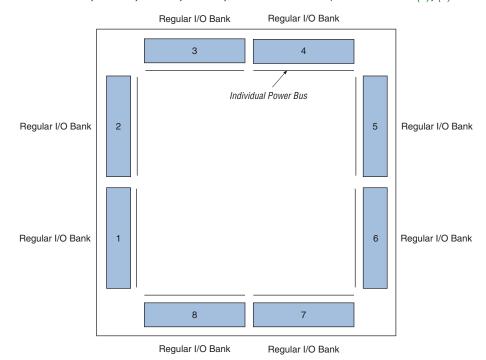

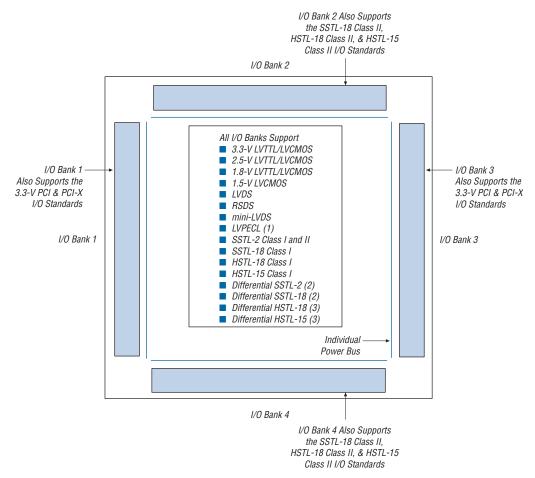

Each I/O bank has its own VCCIO pins. A single device can support 1.5-V, 1.8-V, 2.5-V, and 3.3-V interfaces; each individual bank can support a different standard with different I/O voltages. Each bank also has dual-purpose VREF pins to support any one of the voltage-referenced

Table 5–13 shows the Cyclone II device pin capacitance for different I/O pin types.

| Table 5–13. Device Capacitance Note (1) |                                                                                |      |    |  |  |  |  |  |

|-----------------------------------------|--------------------------------------------------------------------------------|------|----|--|--|--|--|--|

| Symbol                                  | Typical                                                                        | Unit |    |  |  |  |  |  |

| C <sub>IO</sub>                         | Input capacitance for user I/O pin.                                            | 6    | pF |  |  |  |  |  |

| C <sub>LVDS</sub>                       | Input capacitance for dual-purpose<br>LVDS/user I/O pin.                       | 6    | pF |  |  |  |  |  |

| C <sub>VREF</sub>                       | Input capacitance for dual-purpose VREF pin when used as VREF or user I/O pin. | 21   | pF |  |  |  |  |  |

| C <sub>CLK</sub>                        | Input capacitance for clock pin.                                               | 5    | pF |  |  |  |  |  |

Note to Table 5–13:

(1) Capacitance is sample-tested only. Capacitance is measured using time-domain reflectometry (TDR). Measurement accuracy is within ±0.5 pF.

# Power Consumption

You can calculate the power usage for your design using the PowerPlay Early Power Estimator and the PowerPlay Power Analyzer feature in the Quartus<sup>®</sup> II software.

The interactive PowerPlay Early Power Estimator is typically used during the early stages of FPGA design, prior to finalizing the project, to get a magnitude estimate of the device power. The Quartus II software PowerPlay Power Analyzer feature is typically used during the later stages of FPGA design. The PowerPlay Power Analyzer also allows you to apply test vectors against your design for more accurate power consumption modeling.

In both cases, only use these calculations as an estimation of power, not as a specification. For more information on PowerPlay tools, refer to the *PowerPlay Early Power Estimator User Guide* and the *Power Estimation and Analysis* section in volume 3 of the *Quartus II Handbook*.

You can obtain the Excel-based PowerPlay Early Power Estimator at www.altera.com. Refer to Table 5–3 on page 5–3 for typical I<sub>CC</sub> standby specifications.

The power-up current required by Cyclone II devices does not exceed the maximum static current. The rate at which the current increases is a function of the system power supply. The exact amount of current consumed varies according to the process, temperature, and power ramp rate. The duration of the I<sub>CCINT</sub> power-up requirement depends on the  $V_{\text{CCINT}}$  voltage supply rise time.

| Devementer | –6 Speed | Grade (1) | –7 Speed | Grade (2) | –8 Speed |     |      |

|------------|----------|-----------|----------|-----------|----------|-----|------|

| Parameter  | Min      | Max       | Min      | Max       | Min      | Max | Unit |

| TPRE       | 191      | —         | 244      | —         | 244      | —   | ps   |

|            | —        | —         | 217      | —         | 244      | —   | ps   |

| TCLKL      | 1000     | —         | 1242     | —         | 1242     |     | ps   |

|            | _        | —         | 1111     | —         | 1242     |     | ps   |

| TCLKH      | 1000     | —         | 1242     | —         | 1242     | —   | ps   |

|            | _        | —         | 1111     | —         | 1242     |     | ps   |

| tLUT       | 180      | 438       | 172      | 545       | 172      | 651 | ps   |

|            | _        |           | 180      | —         | 180      |     | ps   |

#### Notes to Table 5–16:

(1) For the -6 speed grades, the minimum timing is for the commercial temperature grade. The -7 speed grade devices offer the automotive temperature grade. The -8 speed grade devices offer the industrial temperature grade.

(2) For each parameter of the -7 speed grade columns, the value in the first row represents the minimum timing parameter for automotive devices. The second row represents the minimum timing parameter for commercial devices.

(3) For each parameter of the -8 speed grade columns, the value in the first row represents the minimum timing parameter for industrial devices. The second row represents the minimum timing parameter for commercial devices.

| Table 5–17. IOE Internal Timing Microparameters (Part 1 of 2) |          |           |          |           |          |       |      |  |

|---------------------------------------------------------------|----------|-----------|----------|-----------|----------|-------|------|--|

| Devemeter                                                     | –6 Speed | Grade (1) | –7 Speed | Grade (2) | –8 Speed | 11-14 |      |  |

| Parameter                                                     | Min      | Max       | Min      | Max       | Min      | Мах   | Unit |  |

| TSU                                                           | 76       | —         | 101      | —         | 101      | —     | ps   |  |

|                                                               | —        | —         | 89       | —         | 101      | _     | ps   |  |

| тн                                                            | 88       | —         | 106      | —         | 106      | —     | ps   |  |

|                                                               | —        | —         | 97       | —         | 106      | —     | ps   |  |

| тсо                                                           | 99       | 155       | 95       | 171       | 95       | 187   | ps   |  |

|                                                               | —        | —         | 99       | —         | 99       | _     | ps   |  |

| TPIN2COMBOUT_R                                                | 384      | 762       | 366      | 784       | 366      | 855   | ps   |  |

|                                                               | —        | —         | 384      | —         | 384      | _     | ps   |  |

| TPIN2COMBOUT_C                                                | 385      | 760       | 367      | 783       | 367      | 854   | ps   |  |

|                                                               | —        | —         | 385      | —         | 385      | —     | ps   |  |

| TCOMBIN2PIN_R                                                 | 1344     | 2490      | 1280     | 2689      | 1280     | 2887  | ps   |  |

|                                                               | —        | —         | 1344     | —         | 1344     | _     | ps   |  |

Tables 5–50 and 5–51 show the LVDS timing budget for Cyclone II devices. Cyclone II devices support LVDS receivers at data rates up to 805 Mbps, and LVDS transmitters at data rates up to 640 Mbps.

|                                       |            |     | -6 Spee | ed Grade   | )          |     | -7 Spee | ed Grad    | e          |     | –8 Spee | ed Grade            | )                   |      |

|---------------------------------------|------------|-----|---------|------------|------------|-----|---------|------------|------------|-----|---------|---------------------|---------------------|------|

| Symbol                                | Conditions | Min | Тур     | Max<br>(1) | Max<br>(2) | Min | Тур     | Max<br>(1) | Max<br>(2) | Min | Тур     | Max<br>(1)          | Max<br><i>(2)</i>   | Unit |

| f <sub>HSCLK</sub><br>(input          | ×10        | 10  | —       | 320        | 320        | 10  | —       | 275        | 320        | 10  | —       | 155.5<br><i>(4)</i> | 320<br><i>(6)</i>   | MHz  |

| clock<br>fre-                         | ×8         | 10  | _       | 320        | 320        | 10  | _       | 275        | 320        | 10  | _       | 155.5<br><i>(4)</i> | 320<br><i>(6)</i>   | MHz  |

| quency)                               | ×7         | 10  | —       | 320        | 320        | 10  | _       | 275        | 320        | 10  | _       | 155.5<br><i>(4)</i> | 320<br>(6)          | MHz  |

|                                       | ×4         | 10  | —       | 320        | 320        | 10  |         | 275        | 320        | 10  | —       | 155.5<br><i>(4)</i> | 320<br><i>(6)</i>   | MHz  |

|                                       | ×2         | 10  | —       | 320        | 320        | 10  | _       | 275        | 320        | 10  | _       | 155.5<br><i>(4)</i> | 320<br>(6)          | MHz  |

|                                       | ×1         | 10  | —       | 402.5      | 402.5      | 10  | —       | 402.5      | 402.5      | 10  | —       | 402.5<br><i>(8)</i> | 402.5<br><i>(8)</i> | MHz  |

| HSIODR                                | ×10        | 100 | -       | 640        | 640        | 100 | —       | 550        | 640        | 100 | —       | 311<br><i>(5)</i>   | 550<br>(7)          | Mbps |

|                                       | ×8         | 80  | -       | 640        | 640        | 80  | —       | 550        | 640        | 80  | —       | 311<br><i>(5)</i>   | 550<br>(7)          | Mbps |

|                                       | ×7         | 70  | -       | 640        | 640        | 70  | —       | 550        | 640        | 70  | —       | 311<br><i>(5)</i>   | 550<br>(7)          | Mbps |

|                                       | ×4         | 40  | -       | 640        | 640        | 40  | —       | 550        | 640        | 40  | —       | 311<br><i>(5)</i>   | 550<br>(7)          | Mbps |

|                                       | ×2         | 20  | —       | 640        | 640        | 20  | —       | 550        | 640        | 20  | —       | 311<br><i>(5)</i>   | 550<br>(7)          | Mbps |

|                                       | ×1         | 10  | —       | 402.5      | 402.5      | 10  | —       | 402.5      | 402.5      | 10  | —       | 402.5<br><i>(9)</i> | 402.5<br><i>(9)</i> | Mbps |

| t <sub>DUTY</sub>                     | —          | 45  | —       | 55         |            | 45  | _       | 55         | —          | 45  | _       | 55                  | —                   | %    |

|                                       | —          | _   |         | —          | 160        | —   | _       | —          | 312.5      | _   | _       |                     | 363.6               | ps   |

| TCCS<br>(3)                           | —          | _   | —       | 20         | 00         | _   | —       | 2          | 00         | _   | —       | 2                   | 00                  | ps   |

| Output<br>jitter<br>(peak to<br>peak) | —          | _   | _       | 50         | 00         | _   | _       | 5          | 00         | _   | _       | 550                 | (10)                | ps   |

| t <sub>RISE</sub>                     | 20-80%     | 150 | 200     | 25         | 50         | 150 | 200     | 2          | 50         | 150 | 200     | 250                 | (11)                | ps   |

# VCCA & GNDA

Each Cyclone II PLL uses separate VCC and ground pin pairs for their analog circuitry. The analog circuit power and ground pin for each PLL is called VCCA\_PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>PLL</br/>P

- Use separate VCCA power planes

- Use a partitioned VCCA island within the VCCINT plane

- Use thick VCCA traces

### Separate VCCA Power Plane

A mixed signal system is already partitioned into analog and digital sections, each with its own power planes on the board. To isolate the VCCA pin using a separate VCCA power plane, connect the VCCA pin to the analog 1.2-V power plane.

## Partitioned VCCA Island Within the VCCINT Plane

Fully digital systems do not have a separate analog power plane on the board. Since it is expensive to add new planes to the board, you can create islands for VCCA\_PLL. Figure 7–16 shows an example board layout with an analog power island. The dielectric boundary that creates the island should be 25 mils thick. Figure 7–16 shows a partitioned plane within  $V_{\rm CCINT}$  for VCCA.

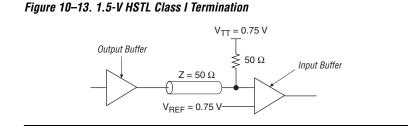

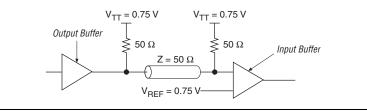

## 1.5-V Pseudo-Differential HSTL Class I and II

The 1.5-V differential HSTL standard is formulated under EIA/JEDEC Standard, EIA/JESD8-6: A 1.5V Output Buffer Supply Voltage Based Interface Standard for Digital Integrated Circuits.

The 1.5-V differential HSTL specification is the same as the 1.5-V single-ended HSTL specification. It is used for applications designed to operate in the 0.0- to 1.5-V HSTL logic switching range, such as QDR memory clock interfaces. Cyclone II devices support both input and output levels. Refer to Figures 10–15 and 10–16 for details on the 1.5-V differential HSTL termination.

Cyclone II devices do not support true 1.5-V differential HSTL standards. Cyclone II devices support pseudo-differential HSTL outputs for PLL\_OUT pins and pseudo-differential HSTL inputs for clock pins. Pseudo-differential inputs require an input reference voltage as opposed to the true differential inputs. Refer to Table 10–1 on page 10–2 for information about pseudo-differential HSTL.

Figure 10–20. EP2C15, EP2C20, EP2C35, EP2C50, and EP2C70 Device I/O Banks Notes (1), (2)

*Notes to Figure 10–20:*

(1) This is a top view of the silicon die.

(2) This is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

pins in each I/O bank (on both rows and columns) support the high-speed I/O interface. Cyclone II pin tables list the pins that support the high-speed I/O interface.

#### Notes to Figure 11–1:

- The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (2) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (3) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

All information in the "Single Device PS Configuration Using a MAX II Device as an External Host" on page 13–22 section is also applicable when using a microprocessor as an external host. Refer to that section for all configuration information.

The MicroBlaster<sup>™</sup> software driver allows you to configure Altera FPGAs, including Cyclone II devices, through the ByteBlaster II or ByteBlasterMV cable in PS mode. The MicroBlaster software driver supports a RBF programming input file and is targeted for embedded PS configuration. The source code is developed for the Windows NT operating system, although you can customize it to run on other operating systems.

Since the Cyclone II device can decompress the compressed configuration data on-the-fly during PS configuration, the MicroBlaster software can accept a compressed RBF file as its input file.

For more information on the MicroBlaster software driver, see the *Configuring the MicroBlaster Passive Serial Software Driver White Paper* and source files on the Altera web site at **www.altera.com**.

If you turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Quartus II software, the Cyclone II devices does not enter user mode after the MicroBlaster has transmitted all the configuration data in the RBF file. You need to supply enough initialization clock cycles to CLKUSR pin to enter user mode.

## Single Device PS Configuration Using a Configuration Device

You can use an Altera configuration device (for example, an EPC2, EPC1, or enhanced configuration device) to configure Cyclone II devices using a serial configuration bitstream. Configuration data is stored in the configuration device. Figure 13–13 shows the configuration interface connections between the Cyclone II device and a configuration device.

The figures in this chapter only show the configuration-related pins and the configuration pin connections between the configuration device and the FPGA.

For more information on enhanced configuration devices and flash interface pins (e.g., PGM[2..0], EXCLK, PORSEL, A[20..0], and DQ[15..0]), see the *Enhanced Configuration Devices* (EPC4, EPC8 & EPC16) Data Sheet.

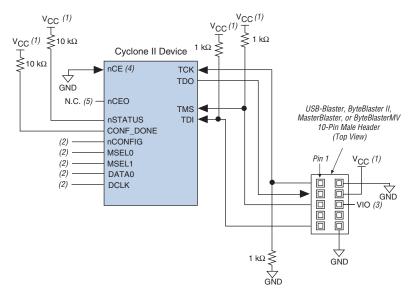

## Single Device JTAG Configuration

During JTAG configuration, you can use the USB-Blaster, MasterBlaster, ByteBlaster II, or ByteBlasterMV download cable to download data to the device. Configuring Cyclone II devices through a cable is similar to programming devices in system. Figure 13–22 shows JTAG configuration of a single Cyclone II device using a download cable.

Figure 13–22. JTAG Configuration of a Single Device Using a Download Cable

#### Notes to Figure 13–22:

- The pull-up resistor should be connected to the same supply voltage as the USB-Blaster, MasterBlaster (VIO pin), ByteBlaster II, or ByteBlasterMV cable.

- (2) Connect the nCONFIG and MSEL[1..0] pins to support a non-JTAG configuration scheme. If only JTAG configuration is used, connect the nCONFIG pin to V<sub>CC</sub>, and the MSEL[1..0] pins to ground. In addition, pull DCLK and DATA0 to either high or low, whichever is convenient on your board.

- (3) Pin 6 of the header is a V<sub>IO</sub> reference voltage for the MasterBlaster output driver. V<sub>IO</sub> should match the device's V<sub>CCIO</sub>. Refer to the *MasterBlaster Serial/USB Communications Cable Data Sheet* for this value. In the ByteBlasterMV, this pin is a no connect. In the USB-Blaster and ByteBlaster II, this pin is connected to nCE when it is used for AS programming, otherwise it is a no connect.

- (4) nCE must be connected to GND or driven low for successful JTAG configuration.

- (5) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

To configure a single device in a JTAG chain, the programming software places all other devices in BYPASS mode. In BYPASS mode, Cyclone II devices pass programming data from the TDI pin to the TDO pin through a single bypass register without being affected internally. This scheme

# 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices

#### CII51014-2.1

# Introduction

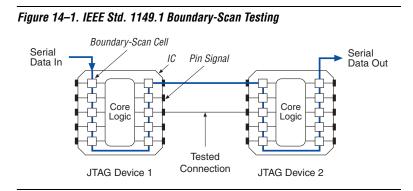

As printed circuit boards (PCBs) become more complex, the need for thorough testing becomes increasingly important. Advances in surfacemount packaging and PCB manufacturing have resulted in smaller boards, making traditional test methods (e.g., external test probes and "bed-of-nails" test fixtures) harder to implement. As a result, cost savings from PCB space reductions are sometimes offset by cost increases in traditional testing methods.

In the 1980s, the Joint Test Action Group (JTAG) developed a specification for boundary-scan testing that was later standardized as the IEEE Std. 1149.1 specification. This boundary-scan test (BST) architecture offers the capability to efficiently test components on PCBs with tight lead spacing.

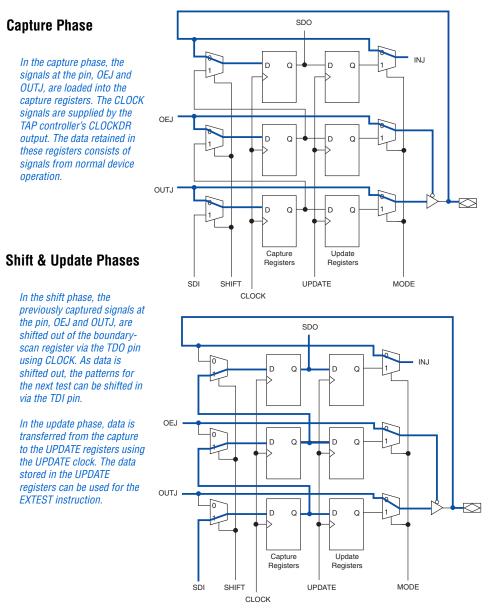

This BST architecture tests pin connections without using physical test probes and captures functional data while a device is operating normally. Boundary-scan cells in a device force signals onto pins or capture data from pin or logic array signals. Forced test data is serially shifted into the boundary-scan cells. Captured data is serially shifted out and externally compared with expected results. Figure 14–1 shows the concept of boundary-scan testing.

Figure 14-8. IEEE Std. 1149.1 BST SAMPLE/PRELOAD Mode

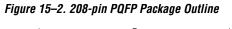

| Table 15–8. 208-Pin PQFP Package Outline Dimensions (Part 2 of 2) |            |            |      |  |  |  |  |

|-------------------------------------------------------------------|------------|------------|------|--|--|--|--|

| Symbol                                                            | Millimeter |            |      |  |  |  |  |

| Symbol                                                            | Min.       | Nom.       | Max. |  |  |  |  |

| е                                                                 | 0.50 BSC   |            |      |  |  |  |  |

| q                                                                 | 0°         | 0° 3.5° 8° |      |  |  |  |  |

Figure 15–2 shows a 208-pin PQFP package outline.

# DocumentTable 15–21 shows the revision history for this document.Revision History

| Table 15–21. Document Revision History |                                                   |                    |  |  |  |

|----------------------------------------|---------------------------------------------------|--------------------|--|--|--|

| Date &<br>Document<br>Version          | Changes Made                                      | Summary of Changes |  |  |  |

| February 2007<br>v2.3                  | Added document revision history.                  |                    |  |  |  |

| November 2005<br>v2.1                  | Updated information throughout.                   |                    |  |  |  |

| July 2005 v2.0                         | Updated packaging information.                    |                    |  |  |  |

| November 2004<br>v1.0                  | Added document to the Cyclone II Device Handbook. |                    |  |  |  |