Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | 903                                                       |

| Number of Logic Elements/Cells | 14448                                                     |

| Total RAM Bits                 | 239616                                                    |

| Number of I/O                  | 152                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                        |

| Package / Case                 | 256-LBGA                                                  |

| Supplier Device Package        | 256-FBGA (17x17)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c15af256i8n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Contents**

| Chapter Revision Dates                       | xi   |

|----------------------------------------------|------|

| About This Handbook  How to Contact Altera   |      |

| Typographic Conventions                      |      |

| Section I. Cyclone II Device Family Data She | eet  |

| Revision History                             | 1–1  |

| Chapter 1. Introduction                      |      |

| Introduction                                 | 1 1  |

| Low-Cost Embedded Processing Solutions       |      |

| Low-Cost Embedded Processing Solutions       |      |

| Features                                     |      |

| Referenced Documents                         |      |

| Document Revision History                    |      |

| Document Revision Phistory                   | 1 /  |

| Chapter 2. Cyclone II Architecture           |      |

| Functional Description                       | 2–1  |

| Logic Elements                               |      |

| LE Operating Modes                           |      |

| Logic Array Blocks                           |      |

| LAB Interconnects                            |      |

| LAB Control Signals                          |      |

| MultiTrack Interconnect                      |      |

| Row Interconnects                            | 2–10 |

| Column Interconnects                         | 2–12 |

| Device Routing                               |      |

| Global Clock Network & Phase-Locked Loops    |      |

| Dedicated Clock Pins                         |      |

| Dual-Purpose Clock Pins                      |      |

| Global Clock Network                         |      |

| Global Clock Network Distribution            |      |

| PLLs                                         |      |

| Embedded Memory                              |      |

| Memory Modes                                 |      |

| Clock Modes                                  |      |

| M4K Routing Interface                        |      |

**Altera Corporation**

#### Global Clock Network

The 16 or 8 global clock networks drive throughout the entire device. Dedicated clock pins (CLK[]), PLL outputs, the logic array, and dual-purpose clock (DPCLK[]) pins can also drive the global clock network.

The global clock network can provide clocks for all resources within the device, such as IOEs, LEs, memory blocks, and embedded multipliers. The global clock lines can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin, or DQS signals for DDR SDRAM or QDRII SRAM interfaces. Internal logic can also drive the global clock network for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fan-out.

#### Clock Control Block

There is a clock control block for each global clock network available in Cyclone II devices. The clock control blocks are arranged on the device periphery and there are a maximum of 16 clock control blocks available per Cyclone II device. The larger Cyclone II devices (EP2C15 devices and larger) have 16 clock control blocks, four on each side of the device. The smaller Cyclone II devices (EP2C5 and EP2C8 devices) have eight clock control blocks, four on the left and right sides of the device.

The control block has these functions:

- Dynamic global clock network clock source selection

- Dynamic enable/disable of the global clock network

In Cyclone II devices, the dedicated CLK[] pins, PLL counter outputs, DPCLK[] pins, and internal logic can all feed the clock control block. The output from the clock control block in turn feeds the corresponding global clock network.

The following sources can be inputs to a given clock control block:

- Four clock pins on the same side as the clock control block

- Three PLL clock outputs from a PLL

- Four DPCLK pins (including CDPCLK pins) on the same side as the clock control block

- Four internally-generated signals

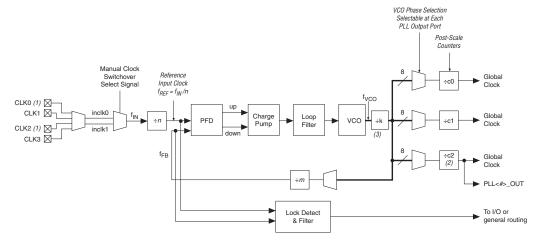

Figure 2–16 shows a block diagram of the Cyclone II PLL.

Figure 2–16. Cyclone II PLL Note (1)

#### Notes to Figure 2–16:

- (1) This input can be single-ended or differential. If you are using a differential I/O standard, then two CLK pins are used. LVDS input is supported via the secondary function of the dedicated CLK pins. For example, the CLK0 pin's secondary function is LVDSCLK1p and the CLK1 pin's secondary function is LVDSCLK1n. If a differential I/O standard is assigned to the PLL clock input pin, the corresponding CLK(n) pin is also completely used. The Figure 2–16 shows the possible clock input connections (CLK0/CLK1) to PLL1.

- (2) This counter output is shared between a dedicated external clock output I/O and the global clock network.

For more information on Cyclone II PLLs, see the PLLs in the *Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

# Embedded Memory

The Cyclone II embedded memory consists of columns of M4K memory blocks. The M4K memory blocks include input registers that synchronize writes and output registers to pipeline designs and improve system performance. The output registers can be bypassed, but input registers cannot.

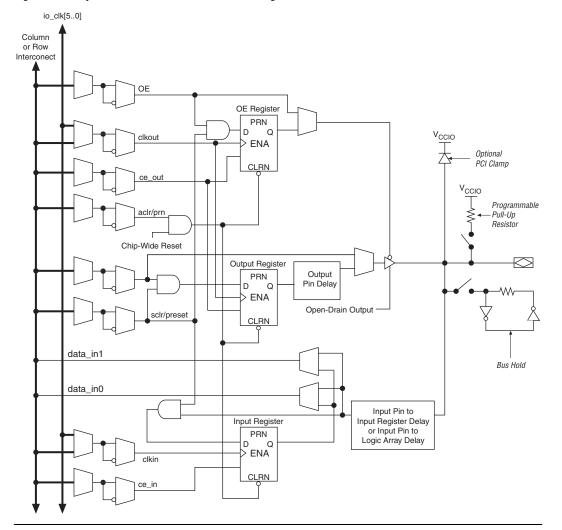

Figure 2–25. Cyclone II IOE in Bidirectional I/O Configuration

The Cyclone II device IOE includes programmable delays to ensure zero hold times, minimize setup times, or increase clock to output times.

A path in which a pin directly drives a register may require a programmable delay to ensure zero hold time, whereas a path in which a pin drives a register through combinational logic may not require the delay. Programmable delays decrease input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time.

# Document Revision History

Table 2–21 shows the revision history for this document.

| Table 2–21. Do                | Table 2–21. Document Revision History                                                                                                                                                                                                                                 |                                                                                                                                                                                |  |  |  |  |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Date &<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                          | Summary of Changes                                                                                                                                                             |  |  |  |  |  |  |  |

| February 2007<br>v3.1         | <ul> <li>Added document revision history.</li> <li>Removed Table 2-1.</li> <li>Updated Figure 2-25.</li> <li>Added new <i>Note</i> (1) to Table 2-17.</li> <li>Added handpara note in "I/O Banks" section.</li> <li>Updated <i>Note</i> (2) to Table 2-20.</li> </ul> | <ul> <li>Removed Drive Strength         Control from Figure 2–25.</li> <li>Elaboration of DDR2 and         QDRII interfaces supported         by I/O bank included.</li> </ul> |  |  |  |  |  |  |  |

| November 2005<br>v2.1         | <ul> <li>Updated Table 2–7.</li> <li>Updated Figures 2–11 and 2–12.</li> <li>Updated Programmable Drive Strength table.</li> <li>Updated Table 2–16.</li> <li>Updated Table 2–18.</li> <li>Updated Table 2–19.</li> </ul>                                             |                                                                                                                                                                                |  |  |  |  |  |  |  |

| July 2005 v2.0                | <ul> <li>Updated technical content throughout.</li> <li>Updated Table 2–16.</li> </ul>                                                                                                                                                                                |                                                                                                                                                                                |  |  |  |  |  |  |  |

| February 2005<br>v1.2         | Updated figure 2-12.                                                                                                                                                                                                                                                  |                                                                                                                                                                                |  |  |  |  |  |  |  |

| November 2004<br>v1.1         | Updated Table 2–19.                                                                                                                                                                                                                                                   |                                                                                                                                                                                |  |  |  |  |  |  |  |

| June 2004 v1.0                | Added document to the Cyclone II Device Handbook.                                                                                                                                                                                                                     |                                                                                                                                                                                |  |  |  |  |  |  |  |

| Table 5–23. EP2C8/A Column Pins Global Clock Timing Parameters (Part 2 of 2) |                           |            |          |              |                  |          |      |  |

|------------------------------------------------------------------------------|---------------------------|------------|----------|--------------|------------------|----------|------|--|

|                                                                              | Fast Corner               |            | –6 Speed | -7 Speed     | -7 Speed         | –8 Speed |      |  |

| Parameter                                                                    | Industrial/<br>Automotive | Commercial | Grade    | Grade<br>(1) | <b>Grade</b> (2) | Grade    | Unit |  |

| t <sub>PLLCOUT</sub>                                                         | -0.179                    | -0.189     | 0.089    | 0.047        | 0.045            | 0.055    | ns   |  |

Notes to Table 5-23:

- (1) These numbers are for commercial devices.

- (2) These numbers are for automotive devices.

| Table 5–24. EP2C8/A Row Pins Global Clock Timing Parameters |                           |            |         |                  |          |                   |      |  |  |

|-------------------------------------------------------------|---------------------------|------------|---------|------------------|----------|-------------------|------|--|--|

|                                                             | Fast (                    | Corner     | Leen2 A | -7 Speed         | -7 Speed | 0 Cnood           |      |  |  |

| Parameter                                                   | Industrial/<br>Automotive | Commercial | Grade   | -o Speed   Grade |          | –8 Speed<br>Grade | Unit |  |  |

| t <sub>CIN</sub>                                            | 1.256                     | 1.314      | 2.270   | 2.416            | 2.596    | 2.606             | ns   |  |  |

| t <sub>COUT</sub>                                           | 1.258                     | 1.316      | 2.286   | 2.429            | 2.604    | 2.614             | ns   |  |  |

| t <sub>PLLCIN</sub>                                         | -0.276                    | -0.294     | -0.08   | -0.134           | -0.152   | -0.142            | ns   |  |  |

| t <sub>PLLCOUT</sub>                                        | -0.274                    | -0.292     | -0.064  | -0.121           | -0.144   | -0.134            | ns   |  |  |

#### Notes to Table 5-24:

- (1) These numbers are for commercial devices.

- (2) These numbers are for automotive devices.

# EP2C15A Clock Timing Parameters

Tables 5–25 and 5–26 show the clock timing parameters for EP2C15A devices.

| Table 5–25. EP2C15A Column Pins Global Clock Timing Parameters |                           |            |                 |          |                  |          |      |  |

|----------------------------------------------------------------|---------------------------|------------|-----------------|----------|------------------|----------|------|--|

|                                                                | Fast Corner               |            | _6 Snood        | -7 Speed | -7 Speed         | -8 Speed | Unit |  |

| Parameter                                                      | Industrial/<br>Automotive | Commercial | Grade Grade (1) |          | <b>Grade</b> (2) | Grade    |      |  |

| t <sub>CIN</sub>                                               | 1.621                     | 1.698      | 2.590           | 2.766    | 3.009            | 2.989    | ns   |  |

| t <sub>COUT</sub>                                              | 1.635                     | 1.713      | 2.624           | 2.798    | 3.038            | 3.018    | ns   |  |

| t <sub>PLLCIN</sub>                                            | -0.351                    | -0.372     | 0.045           | 0.008    | 0.046            | 0.016    | ns   |  |

| Table 5–45. Maximum | Output Gloc |                      |                      | -                    |                                           | •                    |                      |                      | nuince (                   | M11=/                |  |

|---------------------|-------------|----------------------|----------------------|----------------------|-------------------------------------------|----------------------|----------------------|----------------------|----------------------------|----------------------|--|

| I/O Standard        | Drive       | Column I/O Pins (1)  |                      |                      | ock Toggle Rate on Cycle Row I/O Pins (1) |                      |                      | l                    | Dedicated Clock<br>Outputs |                      |  |

| ,                   | Strength    | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | -6<br>Speed<br>Grade                      | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade       | –8<br>Speed<br>Grade |  |

| SSTL_18_ CLASS_II   | 16 mA       | 260                  | 220                  | 180                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

|                     | 18 mA       | 270                  | 220                  | 180                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

| 1.8V_HSTL_ CLASS_I  | 8 mA        | 260                  | 220                  | 180                  | 260                                       | 220                  | 180                  | 260                  | 220                        | 180                  |  |

|                     | 10 mA       | 300                  | 250                  | 210                  | 300                                       | 250                  | 210                  | 300                  | 250                        | 210                  |  |

|                     | 12 mA       | 320                  | 270                  | 220                  | 320                                       | 270                  | 220                  | 320                  | 270                        | 220                  |  |

| 1.8V_HSTL_ CLASS_II | 16 mA       | 230                  | 190                  | 160                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

|                     | 18 mA       | 240                  | 200                  | 160                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

|                     | 20 mA       | 250                  | 210                  | 170                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

| 1.5V_HSTL_ CLASS_I  | 8 mA        | 210                  | 170                  | 140                  | 210                                       | 170                  | 140                  | 210                  | 170                        | 140                  |  |

|                     | 10 mA       | 220                  | 180                  | 150                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

|                     | 12 mA       | 230                  | 190                  | 160                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

| 1.5V_HSTL_ CLASS_II | 16 mA       | 210                  | 170                  | 140                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

| DIFFERENTIAL_       | 8 mA        | 400                  | 340                  | 280                  | 400                                       | 340                  | 280                  | 400                  | 340                        | 280                  |  |

| SSTL_2_CLASS_I      | 12 mA       | 400                  | 340                  | 280                  | 400                                       | 340                  | 280                  | 400                  | 340                        | 280                  |  |

| DIFFERENTIAL_       | 16 mA       | 350                  | 290                  | 240                  | 350                                       | 290                  | 240                  | 350                  | 290                        | 240                  |  |

| SSTL_2_CLASS_II     | 20 mA       | 400                  | 340                  | 280                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

|                     | 24 mA       | 400                  | 340                  | 280                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

| DIFFERENTIAL_       | 6 mA        | 260                  | 220                  | 180                  | 260                                       | 220                  | 180                  | 260                  | 220                        | 180                  |  |

| SSTL_18_CLASS_I     | 8 mA        | 260                  | 220                  | 180                  | 260                                       | 220                  | 180                  | 260                  | 220                        | 180                  |  |

|                     | 10 mA       | 270                  | 220                  | 180                  | 270                                       | 220                  | 180                  | 270                  | 220                        | 180                  |  |

|                     | 12 mA       | 280                  | 230                  | 190                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

| DIFFERENTIAL_SSTL   | 16 mA       | 260                  | 220                  | 180                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

| _18_CLASS_II        | 18 mA       | 270                  | 220                  | 180                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

| 1.8V_               | 8 mA        | 260                  | 220                  | 180                  | 260                                       | 220                  | 180                  | 260                  | 220                        | 180                  |  |

| DIFFERENTIAL_HSTL   | 10 mA       | 300                  | 250                  | 210                  | 300                                       | 250                  | 210                  | 300                  | 250                        | 210                  |  |

| _CLASS_I            | 12 mA       | 320                  | 270                  | 220                  | 320                                       | 270                  | 220                  | 320                  | 270                        | 220                  |  |

| 1.8V_               | 16 mA       | 230                  | 190                  | 160                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

| DIFFERENTIAL_HSTL   | 18 mA       | 240                  | 200                  | 160                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

| _CLASS_II           | 20 mA       | 250                  | 210                  | 170                  | _                                         | _                    | _                    | _                    | _                          | _                    |  |

| Table 5–46. Maximum O | utput Clock       | Toggle                                                    | Rate De              | rating F             | actors (             | Part 2 o             | f 4)                 |                      |                            |                      |  |

|-----------------------|-------------------|-----------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------------|----------------------|--|

|                       |                   | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |                      |                      |                      |                      |                      |                      |                            |                      |  |

| I/O Standard          | Drive<br>Strength | Colu                                                      | Column I/O Pins      |                      |                      | Row I/O Pins         |                      |                      | Dedicated Clock<br>Outputs |                      |  |

|                       |                   | -6<br>Speed<br>Grade                                      | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade       | –8<br>Speed<br>Grade |  |

| SSTL_2_CLASS_II       | 16 mA             | 42                                                        | 43                   | 45                   | 15                   | 29                   | 42                   | 15                   | 29                         | 42                   |  |

|                       | 20 mA             | 41                                                        | 42                   | 44                   | _                    | _                    | _                    | _                    | _                          | _                    |  |

|                       | 24 mA             | 40                                                        | 42                   | 43                   | _                    | _                    | _                    | _                    | _                          | _                    |  |

| SSTL_18_              | 6 mA              | 20                                                        | 22                   | 24                   | 46                   | 47                   | 49                   | 46                   | 47                         | 49                   |  |

| CLASS_I               | 8 mA              | 20                                                        | 22                   | 24                   | 47                   | 49                   | 51                   | 47                   | 49                         | 51                   |  |

|                       | 10 mA             | 20                                                        | 22                   | 25                   | 23                   | 25                   | 27                   | 23                   | 25                         | 27                   |  |

|                       | 12 mA             | 19                                                        | 23                   | 26                   | _                    | _                    | _                    | _                    | _                          |                      |  |

| SSTL_18_ CLASS_II     | 16 mA             | 30                                                        | 33                   | 36                   | _                    | _                    | _                    | _                    | _                          | _                    |  |

|                       | 18 mA             | 29                                                        | 29                   | 29                   | _                    | _                    | _                    | _                    | _                          | _                    |  |

| 1.8V_HSTL_ CLASS_I    | 8 mA              | 26                                                        | 28                   | 29                   | 59                   | 61                   | 63                   | 59                   | 61                         | 63                   |  |

|                       | 10 mA             | 46                                                        | 47                   | 48                   | 65                   | 66                   | 68                   | 65                   | 66                         | 68                   |  |

|                       | 12 mA             | 67                                                        | 67                   | 67                   | 71                   | 71                   | 72                   | 71                   | 71                         | 72                   |  |

| 1.8V_HSTL_ CLASS_II   | 16 mA             | 62                                                        | 65                   | 68                   | _                    | _                    | _                    | _                    | _                          | _                    |  |

|                       | 18 mA             | 59                                                        | 62                   | 65                   | _                    | _                    | _                    | _                    | _                          | _                    |  |

|                       | 20 mA             | 57                                                        | 59                   | 62                   | _                    | _                    | _                    | _                    | _                          | _                    |  |

| 1.5V_HSTL_ CLASS_I    | 8 mA              | 40                                                        | 40                   | 41                   | 28                   | 32                   | 36                   | 28                   | 32                         | 36                   |  |

|                       | 10 mA             | 41                                                        | 42                   | 42                   | _                    | _                    | _                    | _                    | _                          | _                    |  |

|                       | 12 mA             | 43                                                        | 43                   | 43                   | _                    | _                    | _                    | _                    | _                          | _                    |  |

| 1.5V_HSTL_ CLASS_II   | 16 mA             | 18                                                        | 20                   | 21                   | _                    | _                    | _                    | _                    | _                          | _                    |  |

| DIFFERENTIAL_SSTL_2   | 8 mA              | 46                                                        | 47                   | 49                   | 25                   | 40                   | 56                   | 25                   | 40                         | 56                   |  |

| _CLASS_I              | 12 mA             | 67                                                        | 69                   | 70                   | 23                   | 42                   | 60                   | 23                   | 42                         | 60                   |  |

| DIFFERENTIAL_SSTL_2   | 16 mA             | 42                                                        | 43                   | 45                   | 15                   | 29                   | 42                   | 15                   | 29                         | 42                   |  |

| _CLASS_II             | 20 mA             | 41                                                        | 42                   | 44                   |                      |                      | _                    |                      |                            |                      |  |

|                       | 24 mA             | 40                                                        | 42                   | 43                   | _                    |                      | _                    |                      |                            | _                    |  |

| DIFFERENTIAL_SSTL_    | 6 mA              | 20                                                        | 22                   | 24                   | 46                   | 47                   | 49                   | 46                   | 47                         | 49                   |  |

| 18_CLASS_I            | 8 mA              | 20                                                        | 22                   | 24                   | 47                   | 49                   | 51                   | 47                   | 49                         | 51                   |  |

|                       | 10 mA             | 20                                                        | 22                   | 25                   | 23                   | 25                   | 27                   | 23                   | 25                         | 27                   |  |

|                       | 12 mA             | 19                                                        | 23                   | 26                   | _                    | _                    | _                    | _                    | _                          | _                    |  |

| Table 5-48                         | Table 5–48. RSDS Transmitter Timing Specification (Part 2 of 2) |                |     |                |     |     |                |     |     |           |      |

|------------------------------------|-----------------------------------------------------------------|----------------|-----|----------------|-----|-----|----------------|-----|-----|-----------|------|

| Cumbal                             | Conditions                                                      | -6 Speed Grade |     | -7 Speed Grade |     |     | –8 Speed Grade |     |     | I I m i A |      |

| Symbol                             | Conditions                                                      | Min            | Тур | Max(1)         | Min | Тур | Max(1)         | Min | Тур | Max(1)    | Unit |

| TCCS                               | _                                                               | _              | _   | 200            | _   | _   | 200            | _   | _   | 200       | ps   |

| Output<br>jitter (peak<br>to peak) | _                                                               | _              | _   | 500            | _   | _   | 500            | _   | _   | 500       | ps   |

| t <sub>RISE</sub>                  | 20–80%,<br>C <sub>LOAD</sub> = 5 pF                             | _              | 500 | _              | _   | 500 | _              |     | 500 | _         | ps   |

| t <sub>FALL</sub>                  | 80–20%,<br>C <sub>LOAD</sub> = 5 pF                             | _              | 500 | _              | _   | 500 | _              | _   | 500 | _         | ps   |

| t <sub>LOCK</sub>                  | _                                                               | _              |     | 100            | _   |     | 100            | _   | _   | 100       | μs   |

#### Note to Table 5-48:

(1) These specifications are for a three-resistor RSDS implementation. For single-resistor RSDS in ×10 through ×2 modes, the maximum data rate is 170 Mbps and the corresponding maximum input clock frequency is 85 MHz. For single-resistor RSDS in ×1 mode, the maximum data rate is 170 Mbps, and the maximum input clock frequency is 170 MHz. For more information about the different RSDS implementations, refer to the *High-Speed Differential Interfaces in Cyclone II Devices* chapter of the Cyclone II Device Handbook.

In order to determine the transmitter timing requirements, RSDS receiver timing requirements on the other end of the link must be taken into consideration. RSDS receiver timing parameters are typically defined as  $t_{SU}$  and  $t_{H}$  requirements. Therefore, the transmitter timing parameter specifications are  $t_{CO}$  (minimum) and  $t_{CO}$  (maximum). Refer to Figure 5–4 for the timing budget.

The AC timing requirements for RSDS are shown in Figure 5–5.

# **PLL Timing Specifications**

Table 5–54 describes the Cyclone II PLL specifications when operating in the commercial junction temperature range (0° to 85° C), the industrial junction temperature range (–40° to 100° C), the automotive junction temperature range (–40° to 125° C), and the extended temperature range (–40° to 125° C). Follow the PLL specifications for –8 speed grade devices when operating in the industrial, automotive, or extended temperature range.

| Symbol                                       | Parameter                                                              | Min | Тур | Max     | Unit |

|----------------------------------------------|------------------------------------------------------------------------|-----|-----|---------|------|

| f <sub>IN</sub>                              | Input clock frequency (–6 speed grade)                                 | 10  | _   | (4)     | MHz  |

|                                              | Input clock frequency (–7 speed grade)                                 | 10  | _   | (4)     | MHz  |

|                                              | Input clock frequency (–8 speed grade)                                 | 10  | _   | (4)     | MHz  |

| f <sub>INPFD</sub>                           | PFD input frequency (-6 speed grade)                                   | 10  | _   | 402.5   | MHz  |

|                                              | PFD input frequency (-7 speed grade)                                   | 10  | _   | 402.5   | MHz  |

|                                              | PFD input frequency (–8 speed grade)                                   | 10  | _   | 402.5   | MHz  |

| f <sub>INDUTY</sub>                          | Input clock duty cycle                                                 | 40  | _   | 60      | %    |

| t <sub>INJITTER</sub> (5)                    | Input clock period jitter                                              | _   | 200 | _       | ps   |

| f <sub>OUT_EXT</sub> (external clock output) | PLL output frequency (–6 speed grade)                                  | 10  | _   | (4)     | MHz  |

|                                              | PLL output frequency (-7 speed grade)                                  | 10  | _   | (4)     | MHz  |

|                                              | PLL output frequency (–8 speed grade)                                  | 10  | _   | (4)     | MHz  |

| f <sub>OUT</sub> (to global clock)           | PLL output frequency (–6 speed grade)                                  | 10  | _   | 500     | MHz  |

|                                              | PLL output frequency (–7 speed grade)                                  | 10  | _   | 450     | MHz  |

|                                              | PLL output frequency (-8 speed grade)                                  | 10  | _   | 402.5   | MHz  |

| toutduty                                     | Duty cycle for external clock output (when set to 50%)                 | 45  | _   | 55      | %    |

| t <sub>JITTER</sub> (p-p) (2)                | Period jitter for external clock output f <sub>OUT_EXT</sub> > 100 MHz | _   | _   | 300     | ps   |

|                                              | f <sub>OUT_EXT</sub> ≤100 MHz                                          | _   | _   | 30      | mUI  |

| t <sub>LOCK</sub>                            | Time required to lock from end of device configuration                 | _   | _   | 100 (6) | μs   |

| t <sub>PLL PSERR</sub>                       | Accuracy of PLL phase shift                                            | _   | _   | ±60     | ps   |

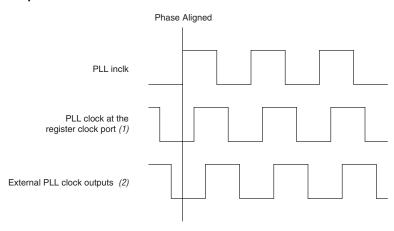

Figure 7–6. Phase Relationship between Cyclone II PLL Clocks in No Compensation Mode

Notes to Figure 7-6:

- (1) Internal clocks fed by the PLL are in phase with each other.

- (2) The external clock outputs can lead or lag the PLL internal clocks.

## Source-Synchronous Mode

If data and clock arrive at the same time at the input pins, they are guaranteed to keep the same phase relationship at the clock and data ports of any IOE input register. Figure 7–7 shows an example waveform of the clock and data in this mode. This mode is recommended for source-synchronous data transfer. Data and clock signals at the IOE experience similar buffer delays as long as the same I/O standard is used.

#### areset

The PLL areset signal is the reset and resynchronization input for each PLL. The areset signal should be asserted every time the PLL loses lock to guarantee correct phase relationship between the PLL input and output clocks. You should include the areset signal in designs if any of the following conditions are true:

- Manual clock switchover is enabled in the design

- Phase relationships between input and output clocks need to be maintained after a loss of lock condition

- If the input clock to the PLL is not toggling or is unstable upon powerup, assert the areset signal after the input clock is toggling, staying within the input jitter specification

Altera recommends using the areset and locked signals in your designs to control and observe the status of your PLL.

The areset signal is an active high signal and, when driven high, the PLL counters reset, clearing the PLL output and causing the PLL to lose lock. The VCO is also set back to its nominal frequency. The clock outputs from the PLL are driven to ground as long as areset is active. When areset transitions low, the PLL resynchronizes to its input clock as the PLL relocks. If the target VCO frequency is below this nominal frequency, then the PLL clock output frequency starts at a higher value than desired during the lock process. In this case, Altera recommends monitoring the gated locked signal to ensure the PLL is fully in lock before enabling the clock outputs from the PLL. The Cyclone II device can drive this PLL input signal from LEs or any general-purpose I/O pin. The areset signal is optional. When it is not enabled in the Quartus II software, the port is internally tied to GND.

#### pfdena

The pfdena signal is an active high signal that controls the PFD output in the PLL with a programmable gate. If you disable the PFD by transitioning pfdena low, the VCO operates at its last set control voltage and frequency value with some long-term drift to a lower frequency. Even though the PLL clock outputs continue to toggle regardless of the input clock, the PLL could lose lock. The system continues running when the PLL goes out of lock or if the input clock is disabled. By maintaining the current frequency, the system has time to store its current settings before shutting down. If the pfdena signal transitions high, the PLL relocks and resynchronizes to the input clock. The pfdena input signal can be driven by any general-purpose I/O pin or from LEs. This signal is optional. When it is not enabled in the Quartus II software, the port is internally tied to  $V_{\rm CC}$ .

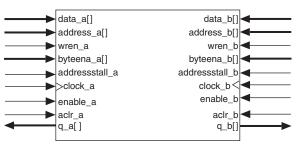

Figure 8–10. Cyclone II True Dual-Port Mode Note (1)

Note to Figure 8-10:

True dual-port memory supports input and output clock mode in addition to the independent clock mode shown.

The widest bit configuration of the M4K blocks in true dual-port mode is  $256 \times 16$ -bit (18-bit with parity).

The  $128 \times 32$ -bit (36-bit with parity) configuration of the M4K block is unavailable because the number of output drivers is equivalent to the maximum bit width. The maximum width of the true dual-port RAM equals half of the total number of output drivers because true dual-port RAM has outputs on two ports. Table 8–6 lists the possible M4K block mixed-port width configurations.

| Dood Dout |          | Write Port |          |          |          |          |          |  |  |  |  |

|-----------|----------|------------|----------|----------|----------|----------|----------|--|--|--|--|

| Read Port | 4K×1     | 2K × 2     | 1K×4     | 512 × 8  | 256 × 16 | 512 × 9  | 256 × 18 |  |  |  |  |

| 4K × 1    | <b>✓</b> | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |  |  |

| 2K × 2    | <b>✓</b> | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |  |  |

| 1K × 4    | <b>✓</b> | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |  |  |

| 512 × 8   | <b>✓</b> | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |  |  |

| 256 × 16  | <b>✓</b> | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |  |  |

| 512 × 9   |          |            |          |          |          | <b>✓</b> | ✓        |  |  |  |  |

| 256 × 18  |          |            |          |          |          | <b>✓</b> | <b>✓</b> |  |  |  |  |

In true dual-port configuration, the RAM outputs are in read-during-write mode. This means that during a write operation, data being written to the A or B port of the RAM flows through to the A or B

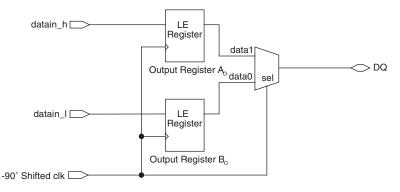

### **DDR Output Registers**

Figure 9–14 shows a schematic representation of DDR output implemented in a Cyclone II device. The DDR output logic is implemented using LEs in the LAB adjacent to the output pin. Two registers synchronize two serial data streams. The registered outputs are then multiplexed by the common clock to drive the DDR output pin at two times the data rate.

Figure 9–14. DDR Output Implementation for DDR Memory Interfaces

While the clock signal is logic-high, the output from output register  $A_{\circ}$  is driven onto the DDR output pin. While the clock signal is logic-low, the output from output register  $B_{\circ}$  is driven onto the DDR output pin. The DDR output pin can be any available user I/O pin. Altera recommends the use of altdq and altdqs megafunctions to implement this output logic. This automatically provides the required tight placement and routing constraints on the LE registers and the output multiplexer.

Figure 9–15 shows examples of functional waveforms from a DDR output implementation.

Section IV-2 Altera Corporation

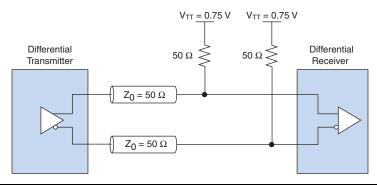

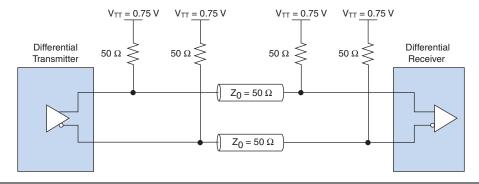

Figure 10-15. 1.5-V Differential HSTL Class I Termination

Figure 10–16. 1.5-V Differential HSTL Class II Termination

### LVDS, RSDS and mini-LVDS

The LVDS standard is formulated under ANSI/TIA/EIA Standard, ANSI/TIA/EIA-644: Electrical Characteristics of Low Voltage Differential Signaling Interface Circuits.

The LVDS I/O standard is a differential high-speed, low-voltage swing, low-power, general-purpose I/O interface standard. This standard is used in applications requiring high-bandwidth data transfer, backplane drivers, and clock distribution. Cyclone II devices are capable of running at a maximum data rate of 805 Mbps for input and 640 Mbps for output and still meet the ANSI/TIA/EIA-644 standard.

Because of the low voltage swing of the LVDS I/O standard, the electromagnetic interference (EMI) effects are much smaller than complementary metal-oxide semiconductor (CMOS),

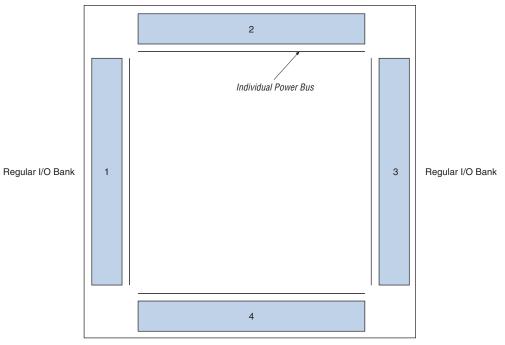

Figure 10–19. EP2C5 and EP2C8 Device I/O Banks Notes (1), (2)

Regular I/O Bank

Regular I/O Bank

#### Notes to Figure 10–19:

- (1) This is a top view of the silicon die.

- (2) This is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

# Document Revision History

Table 11–6 shows the revision history for this document.

| Table 11–6. Dou               | Table 11–6. Document Revision History                                                                                                                                                                                                                                                                             |                                                                                                                                           |  |  |  |  |  |  |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Date &<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                      | Summary of Changes                                                                                                                        |  |  |  |  |  |  |

| February 2007<br>v2.2         | <ul> <li>Added document revision history.</li> <li>Added Note (1) to Table 11-1.</li> <li>Updated Figure 11-5 and added Note (1)</li> <li>Added Note (1) to Table 11-2.</li> <li>Updated Figure 11-6 and added Note (1)</li> <li>Added Note (1) to Table 11-3.</li> <li>Added Note (1) to Figure 11-9.</li> </ul> | Added information stating<br>LVDS/RSDS/mini-LVDS<br>I/O standards<br>specifications apply at the<br>external resistors network<br>output. |  |  |  |  |  |  |

| November 2005<br>v2.1         | <ul> <li>Updated Table 11–2.</li> <li>Updated Figures 11–7 through 11–9.</li> <li>Added Resistor Network Solution for RSDS.</li> <li>Updated note for mini-LVDS Resistor Network table.</li> </ul>                                                                                                                |                                                                                                                                           |  |  |  |  |  |  |

| July 2005 v2.0                | <ul> <li>Updated "I/O Standards Support" section.</li> <li>Updated Tables 11–1 through 11–3.</li> </ul>                                                                                                                                                                                                           |                                                                                                                                           |  |  |  |  |  |  |

| November 2004<br>v1.1         | <ul> <li>Updated Table 11–1.</li> <li>Updated Figures 11–4, 11–5, 11–7, and 11–9.</li> </ul>                                                                                                                                                                                                                      |                                                                                                                                           |  |  |  |  |  |  |

| June 2004, v1.0               | Added document to the Cyclone II Device Handbook.                                                                                                                                                                                                                                                                 |                                                                                                                                           |  |  |  |  |  |  |

device releases its <code>nSTATUS</code> pin after a reset time-out period (maximum of 40 µs). When the <code>nSTATUS</code> pin is released and pulled high by a pull-up resistor, the configuration device reconfigures the chain. If this option is turned off, the external system must monitor <code>nSTATUS</code> for errors and then pulse <code>nCONFIG</code> low for at least 2 µs to restart configuration. The external system can pulse the <code>nCONFIG</code> pin if the pin is under system control rather than tied to  $V_{CC}$ .

Additionally, if the configuration device sends all of its data and then detects that the CONF\_DONE pin has not transitioned high, it recognizes that the FPGA has not configured successfully. Enhanced configuration devices wait for 64 DCLK cycles after the last configuration bit was sent for the CONF\_DONE pin to transition high. EPC2 devices wait for 16 DCLK cycles. After that, the configuration device pulls its OE pin low, which in turn drives the target device's nSTATUS pin low. If you turn on the **Autorestart configuration after error** option in the Quartus II software, the target device resets and then releases its nSTATUS pin after a reset timeout period (maximum of 40 µs). When nSTATUS transitions high again, the configuration device reconfigures the FPGA.

For more information on configuration issues, see the *Debugging Configuration Problems* chapter of the *Configuration Handbook* and the FPGA Configuration Troubleshooter on the Altera web site (www.altera.com).

# Multiple Device PS Configuration Using a Configuration Device

You can use Altera enhanced configuration devices (EPC16, EPC8, and EPC4 devices) or EPC2 and EPC1 configuration devices to configure multiple Cyclone II devices in a PS configuration chain.

Figure 13–14 shows how to configure multiple devices with an enhanced configuration device. This circuit is similar to the configuration device circuit for a single device, except Cyclone II devices are cascaded for multiple device configuration.

You can use a single configuration chain to configure Cyclone II devices with other Altera devices. To ensure that all devices in the chain complete configuration at the same time or that an error flagged by one device initiates reconfiguration in all devices, connect all the Cyclone II device CONF\_DONE pins and connect all Cyclone II device nSTATUS pins together.

For more information on configuring multiple Altera devices in the same configuration chain, see the *Configuring Mixed Altera FPGA Chains* chapter in the *Configuration Handbook*.

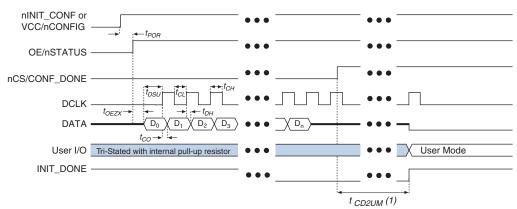

During PS configuration, the design must meet the setup and hold timing parameters and maximum DCLK frequency. The enhanced configuration and EPC2 devices are designed to meet these interface timing specifications.

Figure 13–18 shows the timing waveform for the PS configuration scheme using a configuration device.

Figure 13–18. Cyclone II PS Configuration Using a Configuration Device Timing Waveform

Note to Figure 13-18:

(1) Cyclone II devices enter user mode 299 clock cycles after CONF\_DONE goes high. The initialization clock can come from the Cyclone II internal oscillator or the CLKUSR pin.

For timing information, refer to the *Enhanced Configuration Devices* (EPC4, EPC8, and EPC16) Data Sheet or the Configuration Devices for SRAM-based LUT Devices Data Sheet in the Configuration Handbook.

For more information on device configuration options and how to create configuration files, see the *Software Settings* section in Volume 2 of the *Configuration Handbook*.