### Intel - EP2C15AF484A7N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detailo                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | 903                                                       |

| Number of Logic Elements/Cells | 14448                                                     |

| Total RAM Bits                 | 239616                                                    |

| Number of I/O                  | 315                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | -40°C ~ 125°C (TJ)                                        |

| Package / Case                 | 484-BGA                                                   |

| Supplier Device Package        | 484-FBGA (23x23)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c15af484a7n |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ]   | nternal Timing                                        | 5-18 |

|-----|-------------------------------------------------------|------|

| (   | Cyclone II Clock Timing Parameters                    | 5-23 |

|     | Clock Network Skew Adders                             |      |

| ]   | OE Programmable Delay                                 | 5-30 |

|     | Default Capacitive Loading of Different I/O Standards |      |

|     | /O Delays                                             |      |

| l   | Maximum Input and Output Clock Rate                   | 5-46 |

|     | High Speed I/O Timing Specifications                  |      |

|     | External Memory Interface Specifications              |      |

| J   | TAG Timing Specifications                             | 5-64 |

| j   | PLL Timing Specifications                             | 5-66 |

|     | y Cycle Distortion                                    |      |

|     | DCD Measurement Techniques                            |      |

|     | erenced Documents                                     |      |

| Doc | cument Revision History                               | 5-74 |

|     |                                                       |      |

# Chapter 6. Reference & Ordering Information

| Software                  | <b>)</b> –1 |

|---------------------------|-------------|

| Device Pin-Outs           |             |

| Ordering Information      | -1          |

| Document Revision History |             |

|                           | -           |

# Section II. Clock Management

| Revision History |  | 6– | -1 |

|------------------|--|----|----|

|------------------|--|----|----|

## Chapter 7. PLLs in Cyclone II Devices

| Introduction                                 | 7–1  |

|----------------------------------------------|------|

| Cyclone II PLL Hardware Overview             | 7–2  |

| PLL Reference Clock Generation               | 7–6  |

| Clock Feedback Modes                         | 7–10 |

| Normal Mode                                  | 7–10 |

| Zero Delay Buffer Mode                       | 7–11 |

| No Compensation Mode                         | 7–12 |

| Source-Synchronous Mode                      |      |

| Hardware Features                            |      |

| Clock Multiplication & Division              | 7–14 |

| Programmable Duty Cycle                      |      |

| Phase-Shifting Implementation                |      |

| Control Signals                              | 7–17 |

| Manual Clock Switchover                      |      |

| Clocking                                     | 7–21 |

| Global Clock Network                         | 7–21 |

| Clock Control Block                          | 7–24 |

| Global Clock Network Clock Source Generation | 7–26 |

| Global Clock Network Power Down              | 7–28 |

| Conclusion                | 10–36 |

|---------------------------|-------|

| References                | 10-37 |

| Referenced Documents      | 10–38 |

| Document Revision History | 10–38 |

## Chapter 11. High-Speed Differential Interfaces in Cyclone II Devices

| Introduction                                     |       |

|--------------------------------------------------|-------|

| Cyclone II High-Speed I/O Banks                  | 11–1  |

| Cyclone II High-Speed I/O Interface              | 11–3  |

| I/O Standards Support                            |       |

| LVDS Standard Support in Cyclone II Devices      |       |

| RSDS I/O Standard Support in Cyclone II Devices  | 11–7  |

| mini-LVDS Standard Support in Cyclone II Devices | 11–9  |

| LVPECL Support in Cyclone II                     | 11–11 |

| Differential SSTL Support in Cyclone II Devices  |       |

| Differential HSTL Support in Cyclone II Devices  | 11–13 |

| High-Speed I/O Timing in Cyclone II Devices      | 11–14 |

| Design Guidelines                                | 11–16 |

| Differential Pad Placement Guidelines            |       |

| Board Design Considerations                      | 11–16 |

| Conclusion                                       | 11–17 |

|                                                  |       |

# Section V. DSP

| Revision History 11-1 |

|-----------------------|

|-----------------------|

# Chapter 12. Embedded Multipliers in Cyclone II Devices

| Introduction     |                     | 12–1 |

|------------------|---------------------|------|

| Embedded Multip  | lier Block Overview | 12–2 |

|                  |                     |      |

| Input Registers  | 5                   | 12–4 |

|                  | е                   |      |

|                  | rs                  |      |

| Operational Mode | 25                  | 12–6 |

| 18-Bit Multiplie | 2rs                 | 12–7 |

| 9-Bit Multiplier | °S                  | 12–7 |

| Software Support |                     | 12–9 |

| Conclusion       |                     | 12–9 |

|                  |                     |      |

# Section VI. Configuration & Test

| Revision History                           | 12–1 |

|--------------------------------------------|------|

| Chapter 13. Configuring Cyclone II Devices |      |

| Introduction                               | 13–1 |

# **Chapter Revision Dates**

The chapters in this book, *Cyclone II Device Handbook*, *Volume 1*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

| Chapter 1. | Introduction<br>Revised:<br>Part number:    |               |

|------------|---------------------------------------------|---------------|

| Chapter 2. | Cyclone II Arcl<br>Revised:<br>Part number: | February 2007 |

| Chapter 3. | Configuration<br>Revised:<br>Part number:   | February 2007 |

| Chapter 4. | Hot Socketing<br>Revised:<br>Part number:   |               |

| Chapter 5. | DC Characteris<br>Revised:<br>Part number:  |               |

| Chapter 6. | Reference & Or<br>Revised:<br>Part number:  |               |

| Chapter 7. | PLLs in Cyclor<br>Revised:<br>Part number:  | February 2007 |

| Chapter 8. | Cyclone II Mer<br>Revised:<br>Part number:  | February 2008 |

| Chapter 9. | External Memo<br>Revised:<br>Part number:   | February 2007 |

# About This Handbook

This handbook provides comprehensive information about the Altera  $^{\circledast}$  Cyclone  $^{\circledast}$  II family of devices.

# How to Contact Altera

For the most up-to-date information about Altera products, refer to the following table.

| Contact (1)                     | Contact<br>Method | Address                   |

|---------------------------------|-------------------|---------------------------|

| Technical support               | Website           | www.altera.com/support    |

| Technical training              | Website           | www.altera.com/training   |

|                                 | Email             | custrain@altera.com       |

| Product literature              | Website           | www.altera.com/literature |

| Altera literature services      | Email             | literature@altera.com     |

| Non-technical support (General) | Email             | nacomp@altera.com         |

| (Software Licensing)            | Email             | authorization@altera.com  |

Note to table:

(1) You can also contact your local Altera sales office or sales representative.

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                     |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                  |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: <b>f</b> <sub>MAX</sub> , <b>\qdesigns</b> directory, <b>d:</b> drive, <b>chiptrip.gdf</b> file. |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: <i>AN 75: High-Speed Board Design.</i>                                                                                                                                                      |

|          | <ul> <li>DSP intellectual property (IP) cores</li> <li>DSP Builder interface to The Mathworks Simulink and Matlab design environment</li> <li>DSP Development Kit, Cyclone II Edition</li> <li>Cyclone II devices include a powerful FPGA feature set optimized for low-cost applications including a wide range of density, memory, embedded multiplier, and packaging options. Cyclone II devices support a wide range of common external memory interfaces and I/O protocols required in low-cost applications. Parameterizable IP cores from Altera and partners make using Cyclone II interfaces and protocols fast and easy.</li> </ul> |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Features | The Cyclone II device family offers the following features:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | <ul> <li>High-density architecture with 4,608 to 68,416 LEs</li> <li>M4K embedded memory blocks</li> <li>Up to 1.1 Mbits of RAM available without reducing available logic</li> <li>4,096 memory bits per block (4,608 bits per block including 512 parity bits)</li> <li>Variable port configurations of ×1, ×2, ×4, ×8, ×9, ×16, ×18, ×32, and ×36</li> <li>True dual-port (one read and one write, two reads, or two writes) operation for ×1, ×2, ×4, ×8, ×9, ×16, and ×18 modes</li> <li>Byte enables for data input masking during writes</li> <li>Up to 260-MHz operation</li> </ul>                                                   |

|          | <ul> <li>Embedded multipliers</li> <li>Up to 150 18- × 18-bit multipliers are each configurable as two independent 9- × 9-bit multipliers with up to 250-MHz performance</li> <li>Optional input and output registers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                              |

|          | <ul> <li>Advanced I/O support</li> <li>High-speed differential I/O standard support, including LVDS, RSDS, mini-LVDS, LVPECL, differential HSTL, and differential SSTL</li> <li>Single-ended I/O standard support, including 2.5-V and 1.8-V, SSTL class I and II, 1.8-V and 1.5-V HSTL class I and II, 3.3-V PCI and PCI-X 1.0, 3.3-, 2.5-, 1.8-, and 1.5-V LVCMOS, and 3.3-, 2.5-, and 1.8-V LVTTL</li> </ul>                                                                                                                                                                                                                               |

|          | • Peripheral Component Interconnect Special Interest Group (PCI<br>SIG) <i>PCI Local Bus Specification, Revision 3.0</i> compliance for 3.3-V<br>operation at 33 or 66 MHz for 32- or 64-bit interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                       |

• PCI Express with an external TI PHY and an Altera PCI Express ×1 Megacore<sup>®</sup> function

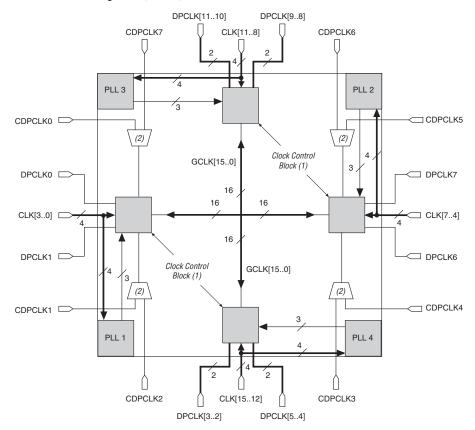

Figure 2–12. EP2C15 & Larger PLL, CLK[], DPCLK[] & Clock Control Block Locations

#### *Notes to Figure 2–12:*

- (1) There are four clock control blocks on each side.

- (2) Only one of the corner CDPCLK pins in each corner can feed the clock control block at a time. The other CDPCLK pins can be used as general-purpose I/O pins.

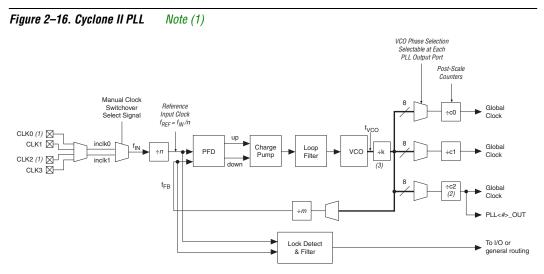

#### Figure 2–16 shows a block diagram of the Cyclone II PLL.

#### Notes to Figure 2–16:

- (1) This input can be single-ended or differential. If you are using a differential I/O standard, then two CLK pins are used. LVDS input is supported via the secondary function of the dedicated CLK pins. For example, the CLK0 pin's secondary function is LVDSCLK1p and the CLK1 pin's secondary function is LVDSCLK1n. If a differential I/O standard is assigned to the PLL clock input pin, the corresponding CLK (n) pin is also completely used. The Figure 2–16 shows the possible clock input connections (CLK0/CLK1) to PLL1.

- (2) This counter output is shared between a dedicated external clock output I/O and the global clock network.

For more information on Cyclone II PLLs, see the PLLs in the *Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

# Embedded Memory

The Cyclone II embedded memory consists of columns of M4K memory blocks. The M4K memory blocks include input registers that synchronize writes and output registers to pipeline designs and improve system performance. The output registers can be bypassed, but input registers cannot.

### **Clock Modes**

Table 2–8 summarizes the different clock modes supported by the M4K memory.

| Table 2–8. M4K Clock Modes |                                                                                                                                                                                                 |  |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Clock Mode                 | de Description                                                                                                                                                                                  |  |  |  |

| Independent                | In this mode, a separate clock is available for each port (ports A and B). Clock A controls all registers on the port A side, while clock B controls all registers on the port B side.          |  |  |  |

| Input/output               | On each of the two ports, A or B, one clock controls all registers for inputs into the memory block: data input, wren, and address. The other clock controls the block's data output registers. |  |  |  |

| Read/write                 | Up to two clocks are available in this mode. The write clock controls the block's data inputs, wraddress, and wren. The read clock controls the data output, rdaddress, and rden.               |  |  |  |

| Single                     | In this mode, a single clock, together with clock enable, is used to control all registers of the memory block. Asynchronous clear signals for the registers are not supported.                 |  |  |  |

Table 2–9 shows which clock modes are supported by all M4K blocks when configured in the different memory modes.

| Table 2–9. Cyclone II M4K Memory Clock Modes                      |              |              |   |  |  |  |

|-------------------------------------------------------------------|--------------|--------------|---|--|--|--|

| Clocking Modes True Dual-Port Simple Dual-Port Node Single-Port N |              |              |   |  |  |  |

| Independent                                                       | $\checkmark$ |              |   |  |  |  |

| Input/output                                                      | $\checkmark$ | ~            | ~ |  |  |  |

| Read/write                                                        |              | ~            |   |  |  |  |

| Single clock                                                      | ~            | $\checkmark$ | ~ |  |  |  |

### **M4K Routing Interface**

The R4, C4, and direct link interconnects from adjacent LABs drive the M4K block local interconnect. The M4K blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 16 direct link input connections to the M4K block are possible from the left adjacent LAB and another 16 possible from the right adjacent LAB. M4K block outputs can also connect to left and right LABs through each 16 direct link interconnects. Figure 2–17 shows the M4K block to logic array interface.

Cyclone II devices also use the JTAG port to monitor the logic operation of the device with the SignalTap<sup>®</sup> II embedded logic analyzer. Cyclone II devices support the JTAG instructions shown in Table 3–1.

| JTAG Instruction    | Instruction Code | Description                                                                                                                                                                                                                                                                     |

|---------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE/PRELOAD      | 00 0000 0101     | Allows a snapshot of signals at the device pins to be captured and<br>examined during normal device operation, and permits an initial<br>data pattern to be output at the device pins. Also used by the<br>SignalTap II embedded logic analyzer.                                |

| extest (1)          | 00 0000 1111     | Allows the external circuitry and board-level interconnects to be<br>tested by forcing a test pattern at the output pins and capturing test<br>results at the input pins.                                                                                                       |

| BYPASS              | 11 1111 1111     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                                                     |

| USERCODE            | 00 0000 0111     | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                       |

| IDCODE              | 00 0000 0110     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                                                           |

| HIGHZ (1)           | 00 0000 1011     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                              |

| CLAMP (1)           | 00 0000 1010     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register. |

| ICR<br>instructions |                  | Used when configuring a Cyclone II device via the JTAG port with<br>a USB Blaster <sup>™</sup> , ByteBlaster <sup>™</sup> II, MasterBlaster <sup>™</sup> or<br>ByteBlasterMV <sup>™</sup> download cable, or when using a Jam File or JBC<br>File via an embedded processor.    |

| PULSE_NCONFIG       | 00 0000 0001     | Emulates pulsing the nCONFIG pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                     |

The Cyclone II device instruction register length is 10 bits and the USERCODE register length is 32 bits. Tables 3–2 and 3–3 show the boundary-scan register length and device IDCODE information for Cyclone II devices.

| Table 3–2. Cyclone II Boundary-Scan Register Length |       |  |  |  |  |

|-----------------------------------------------------|-------|--|--|--|--|

| Device Boundary-Scan Register Length                |       |  |  |  |  |

| EP2C5                                               | 498   |  |  |  |  |

| EP2C8                                               | 597   |  |  |  |  |

| EP2C15                                              | 969   |  |  |  |  |

| EP2C20                                              | 969   |  |  |  |  |

| EP2C35                                              | 1,449 |  |  |  |  |

| EP2C50                                              | 1,374 |  |  |  |  |

| EP2C70                                              | 1,890 |  |  |  |  |

| Table 3–3. 32-Bit Cyclone II Device IDCODE |                      |                       |                                 |                 |  |  |  |

|--------------------------------------------|----------------------|-----------------------|---------------------------------|-----------------|--|--|--|

| Deview                                     | IDCODE (32 Bits) (1) |                       |                                 |                 |  |  |  |

| Device                                     | Version (4 Bits)     | Part Number (16 Bits) | Manufacturer Identity (11 Bits) | LSB (1 Bit) (2) |  |  |  |

| EP2C5                                      | 0000                 | 0010 0000 1011 0001   | 000 0110 1110                   | 1               |  |  |  |

| EP2C8                                      | 0000                 | 0010 0000 1011 0010   | 000 0110 1110                   | 1               |  |  |  |

| EP2C15                                     | 0000                 | 0010 0000 1011 0011   | 000 0110 1110                   | 1               |  |  |  |

| EP2C20                                     | 0000                 | 0010 0000 1011 0011   | 000 0110 1110                   | 1               |  |  |  |

| EP2C35                                     | 0000                 | 0010 0000 1011 0100   | 000 0110 1110                   | 1               |  |  |  |

| EP2C50                                     | 0000                 | 0010 0000 1011 0101   | 000 0110 1110                   | 1               |  |  |  |

| EP2C70                                     | 0000                 | 0010 0000 1011 0110   | 000 0110 1110                   | 1               |  |  |  |

#### Notes to Table 3–3:

(1) The most significant bit (MSB) is on the left.

(2) The IDCODE's least significant bit (LSB) is always 1.

For more information on the Cyclone II JTAG specifications, refer to the *DC Characteristics & Timing Specifications* chapter in the *Cyclone II Device Handbook, Volume 1.*

| Table 5-3. D              | Table 5–3. DC Characteristics for User 1/U, Dual-Purpose, and Dedicated Pins (Part 2 of 2)           |                                     |         |         |         |      |

|---------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------|---------|---------|---------|------|

| Symbol                    | Parameter                                                                                            | Conditions                          | Minimum | Typical | Maximum | Unit |

| R <sub>CONF</sub> (5) (6) | Value of I/O pin                                                                                     | $V_{IN} = 0 V$ ; $V_{CCIO} = 3.3 V$ | 10      | 25      | 50      | kΩ   |

|                           | pull-up resistor<br>before and during<br>configuration                                               | $V_{IN} = 0$ V; $V_{CCIO} = 2.5$ V  | 15      | 35      | 70      | kΩ   |

|                           |                                                                                                      | $V_{IN} = 0 V; V_{CCIO} = 1.8 V$    | 30      | 50      | 100     | kΩ   |

|                           |                                                                                                      | $V_{IN} = 0 V; V_{CCIO} = 1.5 V$    | 40      | 75      | 150     | kΩ   |

|                           |                                                                                                      | $V_{IN} = 0 V; V_{CCIO} = 1.2 V$    | 50      | 90      | 170     | kΩ   |

|                           | Recommended<br>value of I/O pin<br>external pull-down<br>resistor before and<br>during configuration | (7)                                 | _       | 1       | 2       | kΩ   |

Table 5–3. DC Characteristics for User I/O, Dual-Purpose, and Dedicated Pins (Part 2 of 2)

#### Notes to Table 5–3:

- All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (2) The minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to the voltages shown in Table 5-4, based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

- (3) This value is specified for normal device operation. The value may vary during power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, and 1.5 V).

- (4) Maximum values depend on the actual T<sub>J</sub> and design utilization. See the Excel-based PowerPlay Early Power Estimator (www.altera.com) or the Quartus II PowerPlay Power Analyzer feature for maximum values. Refer to "Power Consumption" on page 5–13 for more information.

- (5)  $R_{CONF}$  values are based on characterization.  $R_{CONF} = V_{CCIO}/I_{RCONF}$  values may be different if  $V_{IN}$  value is not 0 V. Pin pull-up resistance values will be lower if an external source drives the pin higher than  $V_{CCIO}$ .

- (6) Minimum condition at  $-40^{\circ}$ C and high V<sub>CC</sub>, typical condition at 25°C and nominal V<sub>CC</sub> and maximum condition at 125°C and low V<sub>CC</sub> for R<sub>CONF</sub> values.

- (7) These values apply to all  $V_{CCIO}$  settings.

Table 5–4 shows the maximum  $V_{\rm IN}$  overshoot voltage and the dependency on the duty cycle of the input signal. Refer to Table 5–3 for more information.

| ble 5–4. V <sub>IN</sub> Overshoot Voltage for All Input Buffers |                         |  |  |

|------------------------------------------------------------------|-------------------------|--|--|

| Maximum V <sub>IN</sub> (V)                                      | Input Signal Duty Cycle |  |  |

| 4.0                                                              | 100% (DC)               |  |  |

| 4.1                                                              | 90%                     |  |  |

| 4.2                                                              | 50%                     |  |  |

| 4.3                                                              | 30%                     |  |  |

| 4.4                                                              | 17%                     |  |  |

| 4.5                                                              | 10%                     |  |  |

| Parameter    | –6 Speed | -6 Speed Grade (1) |      | -7 Speed Grade (2) |      | -8 Speed Grade (3) |      |

|--------------|----------|--------------------|------|--------------------|------|--------------------|------|

|              | Min      | Max                | Min  | Max                | Min  | Max                | Unit |

| TM4KBEH      | 234      | —                  | 267  | _                  | 267  | —                  | ps   |

|              | _        | —                  | 250  | —                  | 267  | —                  | ps   |

| TM4KDATAASU  | 35       | —                  | 46   | —                  | 46   | _                  | ps   |

|              | —        | _                  | 40   | _                  | 46   | _                  | ps   |

| TM4KDATAAH   | 234      | _                  | 267  | _                  | 267  | _                  | ps   |

|              | _        | —                  | 250  | _                  | 267  | _                  | ps   |

| TM4KADDRASU  | 35       | —                  | 46   | _                  | 46   | _                  | ps   |

|              | —        | _                  | 40   | _                  | 46   | _                  | ps   |

| TM4KADDRAH   | 234      | _                  | 267  | —                  | 267  | _                  | ps   |

|              | _        | _                  | 250  | —                  | 267  | _                  | ps   |

| TM4KDATABSU  | 35       | _                  | 46   | —                  | 46   | _                  | ps   |

|              | _        | —                  | 40   | _                  | 46   | _                  | ps   |

| TM4KDATABH   | 234      | _                  | 267  | —                  | 267  | _                  | ps   |

|              | _        | _                  | 250  | —                  | 267  | _                  | ps   |

| TM4KRADDRBSU | 35       | —                  | 46   | _                  | 46   | _                  | ps   |

|              | _        | _                  | 40   | —                  | 46   | _                  | ps   |

| TM4KRADDRBH  | 234      | _                  | 267  | —                  | 267  | _                  | ps   |

|              | _        | —                  | 250  | _                  | 267  | _                  | ps   |

| TM4KDATACO1  | 466      | 724                | 445  | 826                | 445  | 930                | ps   |

|              | _        | _                  | 466  | _                  | 466  | _                  | ps   |

| TM4KDATACO2  | 2345     | 3680               | 2234 | 4157               | 2234 | 4636               | ps   |

|              | —        | —                  | 2345 | —                  | 2345 | —                  | ps   |

| TM4KCLKH     | 1923     | —                  | 2769 | —                  | 2769 | —                  | ps   |

|              | _        | _                  | 2307 | —                  | 2769 | _                  | ps   |

| TM4KCLKL     | 1923     | —                  | 2769 | —                  | 2769 | —                  | ps   |

|              | _        | _                  | 2307 | _                  | 2769 | _                  | ps   |

| (Part 2 of 2)                   |                 |      |  |  |

|---------------------------------|-----------------|------|--|--|

| I/O Standard                    | Capacitive Load | Unit |  |  |

| SSTL_18_CLASS_II                | 0               | pF   |  |  |

| 1.5V_HSTL_CLASS_I               | 0               | pF   |  |  |

| 1.5V_HSTL_CLASS_II              | 0               | pF   |  |  |

| 1.8V_HSTL_CLASS_I               | 0               | pF   |  |  |

| 1.8V_HSTL_CLASS_II              | 0               | pF   |  |  |

| DIFFERENTIAL_SSTL_2_CLASS_I     | 0               | pF   |  |  |

| DIFFERENTIAL_SSTL_2_CLASS_II    | 0               | pF   |  |  |

| DIFFERENTIAL_SSTL_18_CLASS_I    | 0               | pF   |  |  |

| DIFFERENTIAL_SSTL_18_CLASS_II   | 0               | pF   |  |  |

| 1.5V_DIFFERENTIAL_HSTL_CLASS_I  | 0               | pF   |  |  |

| 1.5V_DIFFERENTIAL_HSTL_CLASS_II | 0               | pF   |  |  |

| 1.8V_DIFFERENTIAL_HSTL_CLASS_I  | 0               | pF   |  |  |

| 1.8V_DIFFERENTIAL_HSTL_CLASS_II | 0               | pF   |  |  |

| LVDS                            | 0               | pF   |  |  |

| 1.2V_HSTL                       | 0               | pF   |  |  |

| 1.2V_DIFFERENTIAL_HSTL          | 0               | pF   |  |  |

Table 5–38. Default Loading of Different I/O Standards for Cyclone II Device

# 7. PLLs in Cyclone II Devices

#### CII51007-3.1

# Introduction

Cyclone<sup>®</sup> II devices have up to four phase-locked loops (PLLs) that provide robust clock management and synthesis for device clock management, external system clock management, and I/O interfaces. Cyclone II PLLs are versatile and can be used as a zero delay buffer, a jitter attenuator, a low skew fan out buffer, or a frequency synthesizer.

Each Cyclone II device has up to four PLLs, supporting advanced capabilities such as clock switchover and programmable switchover. These PLLs offer clock multiplication and division, phase shifting, and programmable duty cycle and can be used to minimize clock delay and clock skew, and to reduce or adjust clock-to-out ( $t_{CO}$ ) and set-up ( $t_{SU}$ ) times.

Cyclone II devices also support a power-down mode where unused clock networks can be turned off. The Altera<sup>®</sup> Quartus<sup>®</sup> II software enables the PLLs and their features without requiring any external devices.

Cyclone II PLLs have been characterized to operate in the commercial junction temperature range (0° to 85° C), the industrial junction temperature range (-40° to 100° C) and the extended temperature range (-40° to 125° C).

| Table 7–1. Cyclone II Device PLL Availability |              |              |              |              |  |  |

|-----------------------------------------------|--------------|--------------|--------------|--------------|--|--|

| Device                                        | PLL1         | PLL2         | PLL3         | PLL4         |  |  |

| EP2C5                                         | $\checkmark$ | $\checkmark$ |              |              |  |  |

| EP2C8                                         | $\checkmark$ | $\checkmark$ |              |              |  |  |

| EP2C15                                        | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |  |

| EP2C20                                        | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |  |

| EP2C35                                        | $\checkmark$ | $\checkmark$ | ~            | $\checkmark$ |  |  |

| EP2C50                                        | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |  |

| EP2C70                                        | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |  |

Table 7–1 shows the PLLs available in each Cyclone II device.

| Global Clock<br>Network Clock<br>Sources      | Giobal Clock Networks  |              |   |   |              |              |   |                                    |              |              |              |              |              |              |              |              |

|-----------------------------------------------|------------------------|--------------|---|---|--------------|--------------|---|------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

|                                               | All Cyclone II Devices |              |   |   |              |              |   | EP2C15 through EP2C70 Devices Only |              |              |              |              |              |              |              |              |

|                                               | 0                      | 1            | 2 | 3 | 4            | 5            | 6 | 7                                  | 8            | 9            | 10           | 11           | 12           | 13           | 14           | 15           |

| PLL4_c0                                       |                        |              |   |   |              |              |   |                                    |              |              |              |              | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

| PLL4_c1                                       |                        |              |   |   |              |              |   |                                    |              |              |              |              | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |

| PLL4_c2                                       |                        |              |   |   |              |              |   |                                    |              |              |              |              |              | $\checkmark$ | $\checkmark$ |              |

| DPCLK0 (1)                                    | $\checkmark$           |              |   |   |              |              |   |                                    |              |              |              |              |              |              |              |              |

| DPCLK1 (1)                                    |                        | $\checkmark$ |   |   |              |              |   |                                    |              |              |              |              |              |              |              |              |

| DPCLK10 (1), (2)<br>CDPCLK0 or<br>CDPCLK7 (3) |                        |              | ~ |   |              |              |   |                                    |              |              |              |              |              |              |              |              |

| DPCLK2 (1), (2)<br>CDPCLK1 or<br>CDPCLK2 (3)  |                        |              |   | ~ |              |              |   |                                    |              |              |              |              |              |              |              |              |

| DPCLK7 (1)                                    |                        |              |   |   | $\checkmark$ |              |   |                                    |              |              |              |              |              |              |              |              |

| DPCLK6 (1)                                    |                        |              |   |   |              | $\checkmark$ |   |                                    |              |              |              |              |              |              |              |              |

| DPCLK8 (1), (2)<br>CDPCLK5 or<br>CDPCLK6 (3)  |                        |              |   |   |              |              | > |                                    |              |              |              |              |              |              |              |              |

| DPCLK4 (1), (2)<br>CDPCLK4 or<br>CDPCLK3 (3)  |                        |              |   |   |              |              |   | >                                  |              |              |              |              |              |              |              |              |

| DPCLK8 (1)                                    |                        |              |   |   |              |              |   |                                    | $\checkmark$ |              |              |              |              |              |              |              |

| DPCLK11 (1)                                   |                        |              |   |   |              |              |   |                                    |              | $\checkmark$ |              |              |              |              |              |              |

| DPCLK9 (1)                                    |                        |              |   |   |              |              |   |                                    |              |              | $\checkmark$ |              |              |              |              |              |

| DPCLK10 (1)                                   |                        |              |   |   |              |              |   |                                    |              |              |              | $\checkmark$ |              |              |              |              |

| DPCLK5 (1)                                    |                        |              |   |   |              |              |   |                                    |              |              |              |              | $\checkmark$ |              |              |              |

| DPCLK2 (1)                                    |                        |              |   |   |              |              |   |                                    |              |              |              |              |              | $\checkmark$ |              |              |

| DPCLK4 (1)                                    |                        |              |   |   |              |              |   |                                    |              |              |              |              |              |              | $\checkmark$ |              |

# I/O Termination The major

The majority of the Cyclone II I/O standards are single-ended, non-voltage-referenced I/O standards and, as such, the following I/O standards do not specify a recommended termination scheme:

- 3.3-V LVTTL and LVCMOS

- 2.5-V LVTTL and LVCMOS

- 1.8-V LVTTL and LVCMOS

- 1.5-V LVCMOS

- 3.3-V PCI and PCI-X

### Voltage-Referenced I/O Standard Termination

Voltage-referenced I/O standards require both an input reference voltage,  $V_{REF}$ , and a termination voltage,  $V_{TT}$ . The reference voltage of the receiving device tracks the termination voltage of the transmitting device.

For more information on termination for voltage-referenced I/O standards, refer to "Supported I/O Standards" on page 10–1.

### **Differential I/O Standard Termination**

Differential I/O standards typically require a termination resistor between the two signals at the receiver. The termination resistor must match the differential load impedance of the bus.

Cyclone II devices support differential I/O standards LVDS, RSDS, and mini-LVDS, and differential LVPECL.

For more information on termination for differential I/O standards, refer to "Supported I/O Standards" on page 10–1.

For more information on configuration issues, see the *Debugging Configuration Problems* chapter of the *Configuration Handbook* and the FPGA Configuration Troubleshooter on the Altera web site (www.altera.com).

### **Multiple Device AS Configuration**

You can configure multiple Cyclone II devices using a single serial configuration device. You can cascade multiple Cyclone II devices using the chip-enable (nCE) and chip-enable-out (nCEO) pins. Connect the nCE pin of the first device in the chain to ground and connect the nCEO pin to the nCE pin of the next device in the chain. Use an external 10-k $\Omega$  pull-up resistor to pull the nCEO signal high to its V<sub>CCIO</sub> level to help the internal weak pull-up resistor. When the first device captures all of its configuration data from the bitstream, it transitions its nCEO pin low, initiating the configuration of the next device unconnected or use it as a user I/O pin after configuration if the last device in chain is a Cyclone II device.

The Quartus II software sets the Cyclone II device nCEO pin as an output pin driving to ground by default. If the device is in a chain, and the nCEO pin is connected to the next device's nCE pin, you must make sure that the nCEO pin is not used as a user I/O pin after configuration. The software setting is in the **Dual-Purpose Pins** tab of the **Device & Pin Options** dialog box in Quartus II software.

The first Cyclone II device in the chain is the configuration master and controls the configuration of the entire chain. Select the AS configuration scheme for the first Cyclone II device and the PS configuration scheme for the remaining Cyclone II devices (configuration slaves). Any other Altera<sup>®</sup> device that supports PS configuration can also be part of the chain as a configuration slave. In a multiple device chain, the nCONFIG, nSTATUS, CONF\_DONE, DCLK, and DATAO pins of each device in the chain are connected (see Figure 13–4). Figure 13–4 shows the pin connections for this setup.

All information in the "Single Device PS Configuration Using a MAX II Device as an External Host" on page 13–22 section is also applicable when using a microprocessor as an external host. Refer to that section for all configuration information.

The MicroBlaster<sup>™</sup> software driver allows you to configure Altera FPGAs, including Cyclone II devices, through the ByteBlaster II or ByteBlasterMV cable in PS mode. The MicroBlaster software driver supports a RBF programming input file and is targeted for embedded PS configuration. The source code is developed for the Windows NT operating system, although you can customize it to run on other operating systems.

Since the Cyclone II device can decompress the compressed configuration data on-the-fly during PS configuration, the MicroBlaster software can accept a compressed RBF file as its input file.

For more information on the MicroBlaster software driver, see the *Configuring the MicroBlaster Passive Serial Software Driver White Paper* and source files on the Altera web site at **www.altera.com**.

If you turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Quartus II software, the Cyclone II devices does not enter user mode after the MicroBlaster has transmitted all the configuration data in the RBF file. You need to supply enough initialization clock cycles to CLKUSR pin to enter user mode.

### Single Device PS Configuration Using a Configuration Device

You can use an Altera configuration device (for example, an EPC2, EPC1, or enhanced configuration device) to configure Cyclone II devices using a serial configuration bitstream. Configuration data is stored in the configuration device. Figure 13–13 shows the configuration interface connections between the Cyclone II device and a configuration device.

The figures in this chapter only show the configuration-related pins and the configuration pin connections between the configuration device and the FPGA.

For more information on enhanced configuration devices and flash interface pins (e.g., PGM[2..0], EXCLK, PORSEL, A[20..0], and DQ[15..0]), see the *Enhanced Configuration Devices* (EPC4, EPC8 & EPC16) Data Sheet.

### **Combining JTAG & Active Serial Configuration Schemes**

You can combine the AS configuration scheme with JTAG-based configuration. Set the MSEL[1..0] pins to 00 (AS mode) or 10 (Fast AS mode) in this setup, which uses two 10-pin download cable headers on the board. The first header programs the serial configuration device in the system via the AS programming interface, and the second header configures the Cyclone II directly via the JTAG interface.

If you try configuring the device using both schemes simultaneously, JTAG configuration takes precedence and AS configuration is terminated.

When a blank serial configuration device is attached to Cyclone II device, turn on the **Halt on-chip configuration controller** option under the Tools menu by clicking **Options**. The Options dialog box appears. In the **Category** list, select **Programmer** before starting the JTAG configuration with the Quartus II programmer. This option stops the AS reconfiguration loop from a blank serial configuration device before starting the JTAG configuration. This includes using the Serial Flash Loader IP because JTAG is used for configuring the Cyclone II device. Users do not need to recompile their Quartus II designs after turning on this Option.

# Programming Serial Configuration Devices In-System Using the JTAG Interface

Cyclone II devices in a single device chain or in a multiple device chain support in-system programming of a serial configuration device using the JTAG interface via the serial flash loader design. The board's intelligent host or download cable can use the four JTAG pins on the Cyclone II device to program the serial configuration device in system, even if the host or download cable cannot access the configuration device's configuration pins (DCLK, DATA, ASDI, and nCS pins).

The serial flash loader design is a JTAG-based in-system programming solution for Altera serial configuration devices. The serial flash loader is a bridge design for the FPGA that uses its JTAG interface to access the EPCS JIC (JTAG Indirect Configuration Device Programming) file and then uses the AS interface to program the EPCS device. Both the JTAG interface and AS interface are bridged together inside the serial flash loader design.

In a multiple device chain, you only need to configure the master Cyclone II device which is controlling the serial configuration device. The slave devices in the multiple device chain which are configured by the serial configuration device do not need to be configured when using this

## 896-Pin FineLine BGA Package – Wirebond

- All dimensions and tolerances conform to ASME Y14.5M 1994.

- Controlling dimension is in millimeters.

- Pin A1's location may be indicated by an ID dot in its proximity on the package surface.

Tables 15–19 and 15–20 show the package information and package outline figure references, respectively, for the 896-pin FineLine BGA.

| Table 15–19. 896-Pin FineLine BGA Package Information |                                                                      |  |  |  |  |  |

|-------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|

| Description                                           | Specification                                                        |  |  |  |  |  |

| Ordering code reference                               | F                                                                    |  |  |  |  |  |

| Package acronym                                       | FineLine BGA                                                         |  |  |  |  |  |

| Substrate material                                    | вт                                                                   |  |  |  |  |  |

| Solder ball composition                               | Regular: 63Sn: 37Pb (typical)<br>Pb-free: Sn: 3.0Ag: 0.5Cu (typical) |  |  |  |  |  |

| JEDEC outline reference                               | MS-034 variation AAN-1                                               |  |  |  |  |  |

| Maximum lead coplanarity                              | 0.008 inches (0.20 mm)                                               |  |  |  |  |  |

| Weight                                                | 11.5 g                                                               |  |  |  |  |  |

| Moisture sensitivity level                            | Printed on moisture barrier bag                                      |  |  |  |  |  |

| Table 15–20. 896-Pin FineLine BGA Package Outline Dimensions |                 |      |      |  |  |  |  |  |  |

|--------------------------------------------------------------|-----------------|------|------|--|--|--|--|--|--|

| Symbol                                                       | Dimensions (mm) |      |      |  |  |  |  |  |  |

|                                                              | Min.            | Nom. | Max. |  |  |  |  |  |  |

| A                                                            | -               | -    | 2.60 |  |  |  |  |  |  |

| A1                                                           | 0.30            | -    | -    |  |  |  |  |  |  |

| A2                                                           | -               | -    | 2.20 |  |  |  |  |  |  |

| A3                                                           | -               | -    | 1.80 |  |  |  |  |  |  |

| D                                                            | 31.00 BSC       |      |      |  |  |  |  |  |  |

| E                                                            | 31.00 BSC       |      |      |  |  |  |  |  |  |

| b                                                            | 0.50            | 0.60 | 0.70 |  |  |  |  |  |  |

| e                                                            | 1.00 BSC        |      |      |  |  |  |  |  |  |