Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | 903                                                       |

| Number of Logic Elements/Cells | 14448                                                     |

| Total RAM Bits                 | 239616                                                    |

| Number of I/O                  | 315                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 484-BGA                                                   |

| Supplier Device Package        | 484-FBGA (23x23)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c15af484c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Another special packing mode allows the register output to feed back into the LUT of the same LE so that the register is packed with its own fan-out LUT, providing another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

In addition to the three general routing outputs, the LEs within an LAB have register chain outputs. Register chain outputs allow registers within the same LAB to cascade together. The register chain output allows an LAB to use LUTs for a single combinational function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources. See "MultiTrack Interconnect" on page 2–10 for more information on register chain connections.

### **LE Operating Modes**

The Cyclone II LE operates in one of the following modes:

- Normal mode

- Arithmetic mode

Each mode uses LE resources differently. In each mode, six available inputs to the LE—the four data inputs from the LAB local interconnect, the LAB carry-in from the previous carry-chain LAB, and the register chain connection—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, synchronous clear, synchronous load, and clock enable control for the register. These LAB-wide signals are available in all LE modes.

The Quartus® II software, in conjunction with parameterized functions such as library of parameterized modules (LPM) functions, automatically chooses the appropriate mode for common functions such as counters, adders, subtractors, and arithmetic functions. If required, you can also create special-purpose functions that specify which LE operating mode to use for optimal performance.

### Normal Mode

The normal mode is suitable for general logic applications and combinational functions. In normal mode, four data inputs from the LAB local interconnect are inputs to a four-input LUT (see Figure 2–3). The Quartus II Compiler automatically selects the carry-in or the data3 signal as one of the inputs to the LUT. LEs in normal mode support packed registers and register feedback.

### **PLLs**

Cyclone II PLLs provide general-purpose clocking as well as support for the following features:

- Clock multiplication and division

- Phase shifting

- Programmable duty cycle

- Up to three internal clock outputs

- One dedicated external clock output

- Clock outputs for differential I/O support

- Manual clock switchover

- Gated lock signal

- Three different clock feedback modes

- Control signals

Cyclone II devices contain either two or four PLLs. Table 2–3 shows the PLLs available for each Cyclone II device.

| Table 2–3. Cyclone II Device PLL Availability |          |          |          |      |  |  |  |

|-----------------------------------------------|----------|----------|----------|------|--|--|--|

| Device                                        | PLL1     | PLL2     | PLL3     | PLL4 |  |  |  |

| EP2C5                                         | <b>✓</b> | <b>✓</b> |          |      |  |  |  |

| EP2C8                                         | ✓        | ✓        |          |      |  |  |  |

| EP2C15                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> | ✓    |  |  |  |

| EP2C20                                        | <b>✓</b> | ~        | ✓        | ~    |  |  |  |

| EP2C35                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> | ✓    |  |  |  |

| EP2C50                                        | <b>✓</b> | ~        | ✓        | ~    |  |  |  |

| EP2C70                                        | ✓        | ✓        | ✓        | ✓    |  |  |  |

| Table 2-20            | O. Cyclone II | MultiVolt I/ | O Support (  | Note (1) |              |              |              |          |

|-----------------------|---------------|--------------|--------------|----------|--------------|--------------|--------------|----------|

| v (v)                 |               | Input        | Signal       |          |              | Output       | Signal       |          |

| V <sub>CCIO</sub> (V) | 1.5 V         | 1.8 V        | 2.5 V        | 3.3 V    | 1.5 V        | 1.8 V        | 2.5 V        | 3.3 V    |

| 3.3                   |               |              | <b>√</b> (4) | <b>✓</b> | <b>√</b> (6) | <b>√</b> (6) | <b>√</b> (6) | <b>✓</b> |

#### Notes to Table 2-20:

- (1) The PCI clamping diode must be disabled to drive an input with voltages higher than V<sub>CCIO</sub>.

- (2) These input values overdrive the input buffer, so the pin leakage current is slightly higher than the default value. To drive inputs higher than V<sub>CCIO</sub> but less than 4.0 V, disable the PCI clamping diode and turn on Allow voltage overdrive for LVTTL/LVCMOS input pins option in Device setting option in the Quartus II software.

- (3) When  $V_{CCIO} = 1.8$ -V, a Cyclone II device can drive a 1.5-V device with 1.8-V tolerant inputs.

- (4) When  $V_{CCIO} = 3.3$ -V and a 2.5-V input signal feeds an input pin or when  $V_{CCIO} = 1.8$ -V and a 1.5-V input signal feeds an input pin, the  $V_{CCIO}$  supply current will be slightly larger than expected. The reason for this increase is that the input signal level does not drive to the  $V_{CCIO}$  rail, which causes the input buffer to not completely shut off.

- (5) When V<sub>CCIO</sub> = 2.5-V, a Cyclone II device can drive a 1.5-V or 1.8-V device with 2.5-V tolerant inputs.

- (6) When V<sub>CCIO</sub> = 3.3-V, a Cyclone II device can drive a 1.5-V, 1.8-V, or 2.5-V device with 3.3-V tolerant inputs.

| Table 5–3. DC Characteristics for User I/O, Dual-Purpose, and Dedicated Pins (Part 2 of 2) |                                                                                                      |                                                  |         |         |         |      |  |  |  |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------|---------|---------|------|--|--|--|

| Symbol                                                                                     | Parameter                                                                                            | Conditions                                       | Minimum | Typical | Maximum | Unit |  |  |  |

| R <sub>CONF</sub> (5) (6)                                                                  | Value of I/O pin                                                                                     | $V_{IN} = 0 \text{ V}; V_{CCIO} = 3.3 \text{ V}$ | 10      | 25      | 50      | kΩ   |  |  |  |

|                                                                                            | pull-up resistor<br>before and during<br>configuration                                               | V <sub>IN</sub> = 0 V; V <sub>CCIO</sub> = 2.5 V | 15      | 35      | 70      | kΩ   |  |  |  |

|                                                                                            |                                                                                                      | V <sub>IN</sub> = 0 V; V <sub>CCIO</sub> = 1.8 V | 30      | 50      | 100     | kΩ   |  |  |  |

|                                                                                            |                                                                                                      | V <sub>IN</sub> = 0 V; V <sub>CCIO</sub> = 1.5 V | 40      | 75      | 150     | kΩ   |  |  |  |

|                                                                                            |                                                                                                      | V <sub>IN</sub> = 0 V; V <sub>CCIO</sub> = 1.2 V | 50      | 90      | 170     | kΩ   |  |  |  |

|                                                                                            | Recommended<br>value of I/O pin<br>external pull-down<br>resistor before and<br>during configuration | (7)                                              | _       | 1       | 2       | kΩ   |  |  |  |

#### Notes to Table 5-3:

- All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (2) The minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to the voltages shown in Table 5-4, based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

- (3) This value is specified for normal device operation. The value may vary during power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, and 1.5 V).

- (4) Maximum values depend on the actual T<sub>J</sub> and design utilization. See the Excel-based PowerPlay Early Power Estimator (www.altera.com) or the Quartus II PowerPlay Power Analyzer feature for maximum values. Refer to "Power Consumption" on page 5–13 for more information.

- (5)  $R_{CONF}$  values are based on characterization.  $R_{CONF} = V_{CCIO}/I_{RCONF}$  values may be different if  $V_{IN}$  value is not 0 V. Pin pull-up resistance values will be lower if an external source drives the pin higher than  $V_{CCIO}$ .

- (6) Minimum condition at -40°C and high V<sub>CC</sub>, typical condition at 25°C and nominal V<sub>CC</sub> and maximum condition at 125°C and low V<sub>CC</sub> for R<sub>CONF</sub> values.

- (7) These values apply to all V<sub>CCIO</sub> settings.

Table 5–4 shows the maximum  $V_{\rm IN}$  overshoot voltage and the dependency on the duty cycle of the input signal. Refer to Table 5–3 for more information.

| Table 5–4. V <sub>IN</sub> Overshoot Voltage for All Input Buffers |                         |  |  |  |  |  |

|--------------------------------------------------------------------|-------------------------|--|--|--|--|--|

| Maximum V <sub>IN</sub> (V)                                        | Input Signal Duty Cycle |  |  |  |  |  |

| 4.0                                                                | 100% (DC)               |  |  |  |  |  |

| 4.1                                                                | 90%                     |  |  |  |  |  |

| 4.2                                                                | 50%                     |  |  |  |  |  |

| 4.3                                                                | 30%                     |  |  |  |  |  |

| 4.4                                                                | 17%                     |  |  |  |  |  |

| 4.5                                                                | 10%                     |  |  |  |  |  |

Table 5–38. Default Loading of Different I/O Standards for Cyclone II Device (Part 2 of 2)

| I/O Standard                    | Capacitive Load | Unit |

|---------------------------------|-----------------|------|

| SSTL_18_CLASS_II                | 0               | pF   |

| 1.5V_HSTL_CLASS_I               | 0               | pF   |

| 1.5V_HSTL_CLASS_II              | 0               | pF   |

| 1.8V_HSTL_CLASS_I               | 0               | pF   |

| 1.8V_HSTL_CLASS_II              | 0               | pF   |

| DIFFERENTIAL_SSTL_2_CLASS_I     | 0               | pF   |

| DIFFERENTIAL_SSTL_2_CLASS_II    | 0               | pF   |

| DIFFERENTIAL_SSTL_18_CLASS_I    | 0               | pF   |

| DIFFERENTIAL_SSTL_18_CLASS_II   | 0               | pF   |

| 1.5V_DIFFERENTIAL_HSTL_CLASS_I  | 0               | pF   |

| 1.5V_DIFFERENTIAL_HSTL_CLASS_II | 0               | pF   |

| 1.8V_DIFFERENTIAL_HSTL_CLASS_I  | 0               | pF   |

| 1.8V_DIFFERENTIAL_HSTL_CLASS_II | 0               | pF   |

| LVDS                            | 0               | pF   |

| 1.2V_HSTL                       | 0               | pF   |

| 1.2V_DIFFERENTIAL_HSTL          | 0               | pF   |

## I/O Delays

Refer to Tables 5–39 through 5–43 for I/O delays.

| Table 5–39. I/O Delay Parameters |                                              |  |  |  |  |

|----------------------------------|----------------------------------------------|--|--|--|--|

| Symbol                           | Parameter                                    |  |  |  |  |

| t <sub>DIP</sub>                 | Delay from I/O datain to output pad          |  |  |  |  |

| t <sub>OP</sub>                  | Delay from I/O output register to output pad |  |  |  |  |

| t <sub>PCOUT</sub>               | Delay from input pad to I/O dataout to core  |  |  |  |  |

| t <sub>P1</sub>                  | Delay from input pad to I/O input register   |  |  |  |  |

| Table 5–40. Cyclone II I/O Input Delay for Column Pins (Part 1 of 3) |                    |                           |                 |                |                |                       |                |      |

|----------------------------------------------------------------------|--------------------|---------------------------|-----------------|----------------|----------------|-----------------------|----------------|------|

|                                                                      |                    | Fast Co                   | -6              | _7             | -7             | -8                    |                |      |

| I/O Standard                                                         | Parameter          | Industrial/<br>Automotive | Commer<br>-cial | Speed<br>Grade | Speed<br>Grade | Speed<br>Grade<br>(2) | Speed<br>Grade | Unit |

| LVTTL                                                                | t <sub>P1</sub>    | 581                       | 609             | 1222           | 1228           | 1282                  | 1282           | ps   |

|                                                                      | t <sub>PCOUT</sub> | 367                       | 385             | 760            | 783            | 854                   | 854            | ps   |

| 2.5V                                                                 | t <sub>P1</sub>    | 624                       | 654             | 1192           | 1238           | 1283                  | 1283           | ps   |

|                                                                      | t <sub>PCOUT</sub> | 410                       | 430             | 730            | 793            | 855                   | 855            | ps   |

| 1.8V                                                                 | t <sub>P1</sub>    | 725                       | 760             | 1372           | 1428           | 1484                  | 1484           | ps   |

|                                                                      | t <sub>PCOUT</sub> | 511                       | 536             | 910            | 983            | 1056                  | 1056           | ps   |

| 1.5V                                                                 | t <sub>P1</sub>    | 790                       | 828             | 1439           | 1497           | 1556                  | 1556           | ps   |

|                                                                      | t <sub>PCOUT</sub> | 576                       | 604             | 977            | 1052           | 1128                  | 1128           | ps   |

| LVCMOS                                                               | t <sub>P1</sub>    | 581                       | 609             | 1222           | 1228           | 1282                  | 1282           | ps   |

|                                                                      | t <sub>PCOUT</sub> | 367                       | 385             | 760            | 783            | 854                   | 854            | ps   |

| SSTL_2_CLASS_I                                                       | t <sub>P1</sub>    | 533                       | 558             | 990            | 1015           | 1040                  | 1040           | ps   |

|                                                                      | t <sub>PCOUT</sub> | 319                       | 334             | 528            | 570            | 612                   | 612            | ps   |

| SSTL_2_CLASS_II                                                      | t <sub>P1</sub>    | 533                       | 558             | 990            | 1015           | 1040                  | 1040           | ps   |

|                                                                      | t <sub>PCOUT</sub> | 319                       | 334             | 528            | 570            | 612                   | 612            | ps   |

| SSTL_18_CLASS_I                                                      | t <sub>P1</sub>    | 577                       | 605             | 1027           | 1035           | 1045                  | 1045           | ps   |

|                                                                      | t <sub>PCOUT</sub> | 363                       | 381             | 565            | 590            | 617                   | 617            | ps   |

| SSTL_18_CLASS_II                                                     | t <sub>P1</sub>    | 577                       | 605             | 1027           | 1035           | 1045                  | 1045           | ps   |

|                                                                      | t <sub>PCOUT</sub> | 363                       | 381             | 565            | 590            | 617                   | 617            | ps   |

| Table 5–45. Maximum Output Clock Toggle Rate on Cyclone II Devices (Part 4 of 4) |                                                              |                      |                      |                      |                      |                      |                      |                      |                      |                      |

|----------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

|                                                                                  | Maximum Output Clock Toggle Rate on Cyclone II Devices (MHz) |                      |                      |                      |                      |                      |                      |                      |                      |                      |

| I/O Standard                                                                     | Drive                                                        | Colun                | ın I/O Pi            | ns (1)               | Row                  | I/O Pin              | s (1)                |                      | icated C<br>Outputs  |                      |

| ·                                                                                | Strength                                                     | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade |

| 1.5V_                                                                            | 8 mA                                                         | 210                  | 170                  | 140                  | 210                  | 170                  | 140                  | 210                  | 170                  | 140                  |

| DIFFERENTIAL_HSTL<br>_CLASS_I                                                    | 10 mA                                                        | 220                  | 180                  | 150                  | _                    | _                    | _                    | _                    | _                    | _                    |

| _02/00_1                                                                         | 12 mA                                                        | 230                  | 190                  | 160                  | _                    | _                    | _                    | _                    | _                    | _                    |

| 1.5V_<br>DIFFERENTIAL_HSTL<br>_CLASS_II                                          | 16 mA                                                        | 210                  | 170                  | 140                  | _                    | _                    | _                    | _                    | _                    | _                    |

| LVDS                                                                             | _                                                            | 400                  | 340                  | 280                  | 400                  | 340                  | 280                  | 400                  | 340                  | 280                  |

| RSDS                                                                             | _                                                            | 400                  | 340                  | 280                  | 400                  | 340                  | 280                  | 400                  | 340                  | 280                  |

| MINI_LVDS                                                                        | _                                                            | 400                  | 340                  | 280                  | 400                  | 340                  | 280                  | 400                  | 340                  | 280                  |

| SIMPLE_RSDS                                                                      | _                                                            | 380                  | 320                  | 260                  | 380                  | 320                  | 260                  | 380                  | 320                  | 260                  |

| 1.2V_HSTL                                                                        | _                                                            | 80                   | 80                   | 80                   | _                    | _                    | _                    | _                    | _                    | _                    |

| 1.2V_<br>DIFFERENTIAL_HSTL                                                       | _                                                            | 80                   | 80                   | 80                   | _                    | _                    | _                    | _                    | _                    | _                    |

| PCI                                                                              | _                                                            | _                    | _                    | _                    | 350                  | 315                  | 280                  | 350                  | 315                  | 280                  |

| PCI-X                                                                            | _                                                            | _                    | _                    | _                    | 350                  | 315                  | 280                  | 350                  | 315                  | 280                  |

| LVTTL                                                                            | OCT_25_<br>OHMS                                              | 360                  | 300                  | 250                  | 360                  | 300                  | 250                  | 360                  | 300                  | 250                  |

| LVCMOS                                                                           | OCT_25_<br>OHMS                                              | 360                  | 300                  | 250                  | 360                  | 300                  | 250                  | 360                  | 300                  | 250                  |

| 2.5V                                                                             | OCT_50_<br>OHMS                                              | 240                  | 200                  | 160                  | 240                  | 200                  | 160                  | 240                  | 200                  | 160                  |

| 1.8V                                                                             | OCT_50_<br>OHMS                                              | 290                  | 240                  | 200                  | 290                  | 240                  | 200                  | 290                  | 240                  | 200                  |

| SSTL_2_CLASS_I                                                                   | OCT_50_<br>OHMS                                              | 240                  | 200                  | 160                  | 240                  | 200                  | 160                  | _                    | _                    | _                    |

| SSTL_18_CLASS_I                                                                  | OCT_50_<br>OHMS                                              | 290                  | 240                  | 200                  | 290                  | 240                  | 200                  | _                    | _                    | _                    |

Note to Table 5–45:

(1) This is based on single data rate I/Os.

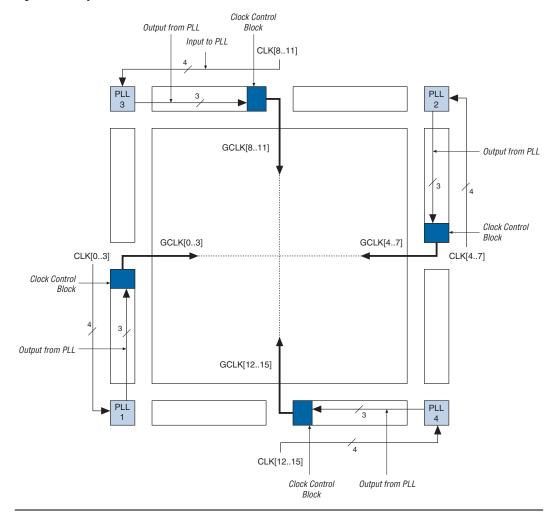

Figure 7-12. Cyclone II Clock Control Blocks Placement

The inputs to the four clock control blocks on each side are chosen from among the following clock sources:

- Four clock input pins

- Three PLL counter outputs

- Two DPCLK pins and two CDPCLK pins from both the left and right sides and four DPCLK pins and two CDPCLK pins from both the top and bottom

- Four signals from internal logic

From the clock sources listed above, only two clock input pins, two PLL clock outputs, one DPCLK or CDPCLK pin, and one source from internal logic can drive into any given clock control blocks, as shown in Figure 7–11. Out of these six inputs to any clock control block, the two clock input pins and two PLL outputs can be dynamic selected to feed a global clock network. The clock control block supports static selection of the DPCLK or CDPCLK pin and the signal from internal logic.

Figure 7–13 shows the simplified version of the four clock control blocks on each side of the Cyclone II device periphery. The Cyclone II devices support up to 16 of these clock control blocks and this allows for up to a maximum of 16 global clocks in Cyclone II devices.

Clock Input Pins

PLL Outputs

3

Clock

Control

Block

Internal Logic

Four Clock Control

Blocks on Each Side

of the Device

Figure 7-13. Clock Control Blocks on Each Side of the Cyclone II Device

Note to Figure 7-13:

The left and right sides of the device have two DPCLK pins, and the top and bottom

of the device have four DPCLK pins.

### Global Clock Network Power Down

The Cyclone II global clock network can be disabled (powered down) by both static and dynamic approaches. When a clock network is powered down, all the logic fed by the clock network is in an off-state, thereby reducing the overall power consumption of the device.

The global clock networks that are not used are automatically powered down through configuration bit settings in the configuration file generated by the Quartus II software.

The dynamic clock enable or disable feature allows internal logic to synchronously control power up or down on the global clock networks in the Cyclone II device. This function is independent of the PLL and is applied directly on the clock network, as shown in Figure 7–11. The input

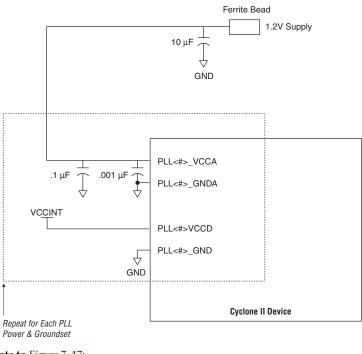

Figure 7–17. PLL Power Schematic for Cyclone II PLLs

Note to Figure 7–17:

(1) Applies to PLLs 1 through 4.

### **VCCD & GND**

The digital power and ground pins are labeled VCCD\_ PLL</br/>

PLL (PLL number) and GND\_PLL</br/>

PLL (PLL number). The VCCD pin supplies the power for the digital circuitry in the PLL. Connect these VCCD pins to the quietest digital supply on the board. In most systems, this is the digital 1.2-V supply supplied to the device's  $V_{CCINT}$  pins. Connect the VCCD pins to a power supply even if you do not use the PLL. When connecting the  $V_{CCD}$  pins to  $V_{CCINT}$ , you do not need any filtering or isolation. You can connect the GND pins directly to the same ground plane as the device's digital ground. See Figure 7–17.

## Conclusion

Cyclone II device PLLs provide you with complete control of device clocks and system timing. These PLLs support clock multiplication/division, phase shift, and programmable duty cycle for your cost-sensitive clock synthesis applications.

case writing is controlled only by the write enable signals. There is no clear port to the byte enable registers. M4K blocks support byte enables when the write port has a data width of 1, 2, 4, 8, 9, 16, 18, 32, or 36 bits. When using data widths of 1, 2, 4, 8, and 9 bits, the byte enable behaves as a redundant write enable because the data width is less than or equal to a single byte. Table 8–3 summarizes the byte selection.

| Table 8–3. Byte Enable for Cyclone II M4K Blocks Note (1) |              |                |              |              |              |               |               |               |               |  |

|-----------------------------------------------------------|--------------|----------------|--------------|--------------|--------------|---------------|---------------|---------------|---------------|--|

|                                                           |              | Affected Bytes |              |              |              |               |               |               |               |  |

| byteena[30]                                               | datain<br>×1 | datain<br>×2   | datain<br>×4 | datain<br>×8 | datain<br>×9 | datain<br>×16 | datain<br>×18 | datain<br>×32 | datain<br>×36 |  |

| [0] = 1                                                   | [0]          | [10]           | [30]         | [70]         | [80]         | [70]          | [80]          | [70]          | [80]          |  |

| [1] = 1                                                   | -            | -              | -            | -            | -            | [158]         | [179]         | [158]         | [179]         |  |

| [2] = 1                                                   | -            | -              | -            | -            | -            | -             | -             | [2316]        | [2618]        |  |

| [3] = 1                                                   | =            | =              | =            | -            | -            | -             | -             | [3124]        | [3527]        |  |

Note to Table 8-3:

Table 8–4 shows the byte enable port control for true dual-port mode.

| Table 8–4. Byte Enable Port Control for True Dual-Port Mode |            |  |  |  |  |

|-------------------------------------------------------------|------------|--|--|--|--|

| byteena [3:0] Affected Port                                 |            |  |  |  |  |

| [1:0]                                                       | Port A (1) |  |  |  |  |

| [3:2]                                                       | Port B (1) |  |  |  |  |

Note to Table 8-4:

Figure 8–2 shows how the wren and byteena signals control the operations of the RAM.

When a byte enable bit is de-asserted during a write cycle, the corresponding data byte output appears as a "don't care" or unknown value. When a byte enable bit is asserted during a write cycle, the corresponding data byte output is the newly written data.

<sup>(1)</sup> Any combination of byte enables is possible.

<sup>(1)</sup> For any data width up to  $\times 18$  for each port.

## Single-Clock Mode

Cyclone II memory blocks support single-clock mode for true dual-port, simple dual-port, and single-port memory. In this mode, a single clock, together with a clock enable, controls all registers of the memory block. This mode does not support asynchronous clear signals for the registers. Figures 8–18 through 8–20 show the memory block in single-clock mode for true dual-port, simple dual-port, and single-port modes, respectively.

# 9. External Memory Interfaces

CII51009-3.1

### Introduction

Improving data bandwidth is an important design consideration when trying to enhance system performance without complicating board design. Traditionally, doubling the data bandwidth of a system required either doubling the system frequency or doubling the number of data I/O pins. Both methods are undesirable because they complicate the overall system design and increase the number of I/O pins. Using double data rate (DDR) I/O pins to transmit and receive data doubles the data bandwidth while keeping I/O counts low. The DDR architecture uses both edges of a clock to transmit data, which facilitates data transmission at twice the rate of a single data rate (SDR) architecture using the same clock speed while maintaining the same number of I/O pins. DDR transmission should be used where fast data transmission is required for a broad range of applications such as networking, communications, storage, and image processing.

Cyclone<sup>®</sup> II devices support a broad range of external memory interfaces, such as SDR SDRAM, DDR SDRAM, DDR2 SDRAM, and QDRII SRAM. Dedicated clock delay control circuitry allows Cyclone II devices to interface with an external memory device at clock speeds up to 167 MHz/333 Mbps for DDR and DDR2 SDRAM devices and 167 MHz/667 Mbps for QDRII SRAM devices. Although Cyclone II devices also support SDR SDRAM, this chapter focuses on the implementations of a double data rate I/O interface using the hardware features available in Cyclone II devices and explains briefly how each memory standard uses the Cyclone II features.

The easiest way to interface to external memory devices is by using one of the Altera® external memory IP cores listed below.

- DDR2 SDRAM Controller MegaCore® Function

- DDR SDRAM Controller MegaCore Function

- QDRII SRAM Controller MegaCore Function

OpenCore<sup>®</sup> Plus evaluations of these cores are available for free to Quartus<sup>®</sup> II Web Edition software users. In addition, Altera software subscription customers now receive full licenses to these MegaCore functions as part of the IP-BASE suite.

## I/O Termination

The majority of the Cyclone II I/O standards are single-ended, non-voltage-referenced I/O standards and, as such, the following I/O standards do not specify a recommended termination scheme:

- 3.3-V LVTTL and LVCMOS

- 2.5-V LVTTL and LVCMOS

- 1.8-V LVTTL and LVCMOS

- 1.5-V LVCMOS

- 3.3-V PCI and PCI-X

### **Voltage-Referenced I/O Standard Termination**

Voltage-referenced I/O standards require both an input reference voltage,  $V_{REF}$ , and a termination voltage,  $V_{TT}$ . The reference voltage of the receiving device tracks the termination voltage of the transmitting device.

For more information on termination for voltage-referenced I/O standards, refer to "Supported I/O Standards" on page 10–1.

### Differential I/O Standard Termination

Differential I/O standards typically require a termination resistor between the two signals at the receiver. The termination resistor must match the differential load impedance of the bus.

Cyclone II devices support differential I/O standards LVDS, RSDS, and mini-LVDS, and differential LVPECL.

For more information on termination for differential I/O standards, refer to "Supported I/O Standards" on page 10–1.

# Referenced Documents

This chapter references the following documents:

- Altera Reliability Report

- AN 75: High-Speed Board Designs

- Cyclone II Architecture chapter in volume 1 of the Cyclone II Device Handbook

- Cyclone II Device Family Data Sheet, section 1 of the Cyclone II Device Handbook

- DC Characteristics and Timing Specifications chapter in volume 1 of the Cyclone II Device Handbook

- External Memory Interfaces chapter in volume 1 of the Cyclone II Device Handbook

- High Speed Differential Interfaces in Cyclone II Devices chapter in volume 1 of the Cyclone II Device Handbook

- Hot Socketing & Power-On Reset chapter in volume 1 of the Cyclone II Device Handbook

- I/O Management chapter in volume 2 of the Quartus II Handbook

# Document Revision History

Table 10–13 shows the revision history for this document.

| Table 10-13. D                  | ocument Revision History                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                 | Summary of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| February 2008<br>v2.4           | <ul> <li>Added "Referenced Documents" section.</li> <li>Updated "Differential Pad Placement<br/>Guidelines" section.</li> </ul>                                                                                                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| February 2007<br>v2.3           | <ul> <li>Added document revision history.</li> <li>Updated "Introduction" and its feetpara note.</li> <li>Updated Note (2) in Table 10–4.</li> <li>Updated "Differential LVPECL" section.</li> <li>Updated "Differential Pad Placement Guidelines" section.</li> <li>Updated "Output Pads" section.</li> <li>Added new section "5.0-V Device Compatibility" with two new figures.</li> </ul> | <ul> <li>Added reference detail for ESD specifications.</li> <li>Added information about differential placement restrictions applying only to pins in the same bank.</li> <li>Added information that Cyclone II device supports LVDS on clock inputs at 3.3V V<sub>CCIO</sub>.</li> <li>Added more information on DC placement guidelines.</li> <li>Added information stating SSTL and HSTL outputs can be closer than 2 pads from V<sub>REF</sub>.</li> <li>Added 5.0 Device tolerence solution.</li> </ul> |

### Configuration Stage

After the Cyclone II device's nSTATUS pin transitions high, the MAX II device should send the configuration data on the DATAO pin one bit at a time. If you are using configuration data in RBF, HEX, or TTF format, send the least significant bit (LSB) of each data byte first. For example, if the RBF contains the byte sequence 02 1B EE 01 FA, you should transmit the serial bitstream 0100-0000 1101-1000 0111-0111 1000-0000 0101-1111 to the device first.

The Cyclone II device receives configuration data on its DATAO pin and the clock on the DCLK pin. Data is latched into the FPGA on the rising edge of DCLK. Data is continuously clocked into the target device until the CONF\_DONE pin transitions high. After the Cyclone II device receives all the configuration data successfully, it releases the open-drain CONF\_DONE pin, which is pulled high by an external  $10\text{-k}\Omega$  pull-up resistor. A low-to-high transition on CONF\_DONE indicates configuration is complete and initialization of the device can begin. The CONF\_DONE pin must have an external  $10\text{-k}\Omega$  pull-up resistor in order for the device to initialize.

The configuration clock (DCLK) speed must be below the specified system frequency (see Table 13–7) to ensure correct configuration. No maximum DCLK period exists, which means you can pause configuration by halting DCLK for an indefinite amount of time.

### Initialization Stage

In Cyclone II devices, the initialization clock source is either the Cyclone II internal oscillator (typically 10 MHz) or the optional CLKUSR pin. The internal oscillator is the default clock source for initialization. If you use the internal oscillator, the Cyclone II device makes sure to provide enough clock cycles for proper initialization. Therefore, if the internal oscillator is the initialization clock source, sending the entire configuration file to the device is sufficient to configure and initialize the device. You do not need to provide additional clock cycles externally during the initialization stage. Driving DCLK back to the device after configuration is complete does not affect device operation. Additionally, if you use the internal oscillator as the clock source, you can use the CLKUSR pin as a user I/O pin.

If you want to delay the initialization of the device, you can use the CLKUSR pin. Using the CLKUSR pin allows you to control when your device enters user mode. You can delay the device from entering user mode for an indefinite amount of time.

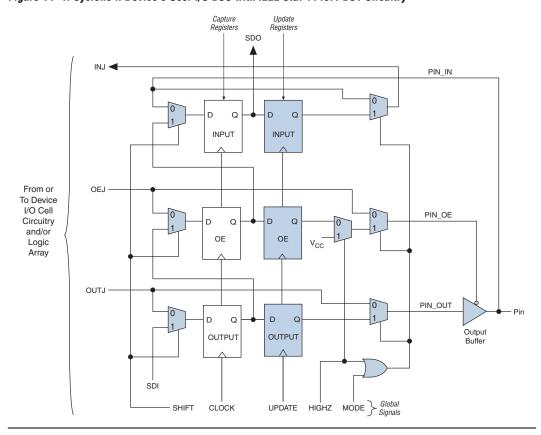

to external device data via the PIN\_IN signal, while the update registers connect to external data through the PIN\_OUT and PIN\_OE signals. The global control signals for the IEEE Std. 1149.1 BST registers (for example, shift, clock, and update) are generated internally by the TAP controller. The MODE signal is generated by a decode of the instruction register. The data signal path for the boundary-scan register runs from the serial data in (SDI) signal to the serial data out (SDO) signal. The scan register begins at the TDI pin and ends at the TDO pin of the device.

Figure 14–4 shows the Cyclone II device's user I/O boundary-scan cell.

Figure 14-4. Cyclone II Device's User I/O BSC with IEEE Std. 1149.1 BST Circuitry

During the capture phase, multiplexers preceding the capture registers select the active device data signals. This data is then clocked into the capture registers. The multiplexers at the outputs of the update registers also select active device data to prevent functional interruptions to the device. During the shift phase, the boundary-scan shift register is formed by clocking data through capture registers around the device periphery, then out of the TDO pin. The device can simultaneously shift new test data into TDI and replace the contents of the capture registers. During the update phase, data in the capture registers is transferred to the update registers. This data can then be used in the  ${\tt EXTEST}$  instruction mode. See "EXTEST Instruction Mode" on page 14–11 for more information.

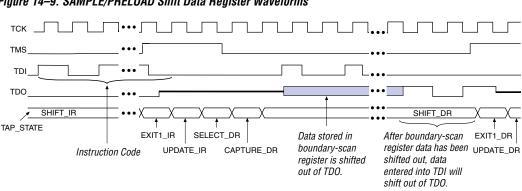

Figure 14–9 shows the SAMPLE/PRELOAD waveforms. The SAMPLE/PRELOAD instruction code is shifted in through the TDI pin. The TAP controller advances to the CAPTURE DR state, then to the SHIFT DR state, where it remains if TMS is held low. The data that was present in the capture registers after the capture phase is shifted out of the TDO pin. New test data shifted into the TDI pin appears at the TDO pin after being clocked through the entire boundary-scan register. Figure 14–9 shows that the instruction code at TDI does not appear at the TDO pin until after the capture register data is shifted out. If TMS is held high on two consecutive TCK clock cycles, the TAP controller advances to the UPDATE DR state for the update phase.

Figure 14-9. SAMPLE/PRELOAD Shift Data Register Waveforms

### **EXTEST Instruction Mode**

The EXTEST instruction mode is used to check external pin connections between devices. Unlike the SAMPLE/PRELOAD mode, EXTEST allows test data to be forced onto the pin signals. By forcing known logic high and low levels on output pins, opens and shorts can be detected at pins of any device in the scan chain.

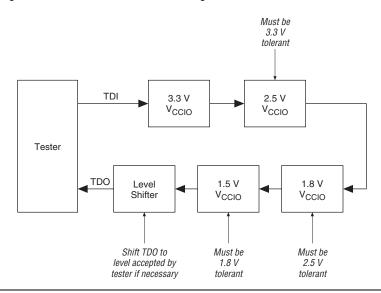

Figure 14–13. JTAG Chain of Mixed Voltages

# Using IEEE Std. 1149.1 BST Circuitry

Cyclone II devices have dedicated JTAG pins, and the IEEE Std. 1149.1 BST circuitry is enabled upon device power-up. You can perform BST on Cyclone II FPGAs not only before and after configuration, but also during configuration. Cyclone II FPGAs support the BYPASS, IDCODE, and SAMPLE instructions during configuration without interrupting configuration. To send all other JTAG instructions, you must interrupt configuration using the CONFIG IO instruction.

The CONFIG\_IO instruction allows you to configure I/O buffers via the JTAG port, and when issued, interrupts configuration. This instruction allows you to perform board-level testing prior to configuring the Cyclone II FPGA or waiting for a configuration device to complete configuration. Once configuration has been interrupted and JTAG BST is complete, the part must be reconfigured via JTAG (PULSE\_CONFIG instruction) or by pulsing nCONFIG low.

When you perform JTAG boundary-scan testing before configuration, the nCONFIG pin must be held low.

The device-wide reset (DEV\_CLRn) and device-wide output enable (DEV\_OE) pins on Cyclone II devices do not affect JTAG boundary-scan or configuration operations. Toggling these pins does not disrupt BST operation any more than usual.