Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | 903                                                       |

| Number of Logic Elements/Cells | 14448                                                     |

| Total RAM Bits                 | 239616                                                    |

| Number of I/O                  | 315                                                       |

| Number of Gates                |                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 484-BGA                                                   |

| Supplier Device Package        | 484-FBGA (23x23)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c15af484c8n |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Embedded multipliers can operate at up to 250 MHz (for the fastest speed grade) for  $18 \times 18$  and  $9 \times 9$  multiplications when using both input and output registers.

Each Cyclone II device has one to three columns of embedded multipliers that efficiently implement multiplication functions. An embedded multiplier spans the height of one LAB row. Table 2–10 shows the number of embedded multipliers in each Cyclone II device and the multipliers that can be implemented.

| Table 2–10. Numbe | r of Embedded Multipli         | ers in Cyclone II Devi  | ces Note (1)      |                     |

|-------------------|--------------------------------|-------------------------|-------------------|---------------------|

| Device            | Embedded<br>Multiplier Columns | Embedded<br>Multipliers | 9 × 9 Multipliers | 18 × 18 Multipliers |

| EP2C5             | 1                              | 13                      | 26                | 13                  |

| EP2C8             | 1                              | 18                      | 36                | 18                  |

| EP2C15            | 1                              | 26                      | 52                | 26                  |

| EP2C20            | 1                              | 26                      | 52                | 26                  |

| EP2C35            | 1                              | 35                      | 70                | 35                  |

| EP2C50            | 2                              | 86                      | 172               | 86                  |

| EP2C70            | 3                              | 150                     | 300               | 150                 |

#### Note to Table 2–10:

(1) Each device has either the number of  $9 \times 9$ -, or  $18 \times 18$ -bit multipliers shown. The total number of multipliers for each device is not the sum of all the multipliers.

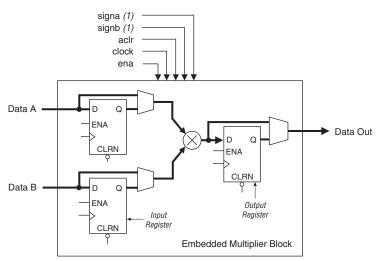

The embedded multiplier consists of the following elements:

- Multiplier block

- Input and output registers

- Input and output interfaces

Figure 2–18 shows the multiplier block architecture.

| Table 5–21. EP       | 2C5/A Column              | n Pins Global ( | Clock Timing P | arameters (P | art 2 of 2)  |          |      |

|----------------------|---------------------------|-----------------|----------------|--------------|--------------|----------|------|

|                      | Fast (                    | Corner          | –6 Speed       | –7 Speed     | –7 Speed     | –8 Speed |      |

| Parameter            | Industrial/<br>Automotive | Commercial      | Grade          | Grade<br>(1) | Grade<br>(2) | Grade    | Unit |

| t <sub>pllcout</sub> | -0.174                    | -0.186          | 0.11           | 0.07         | 0.071        | 0.081    | ns   |

*Notes to Table 5–21:*

(1) These numbers are for commercial devices.

(2) These numbers are for automotive devices.

| Table 5–22. El       | P2C5/A Row Pi             | ins Global Cloc | k Timing Para | ameters      |              |          |      |

|----------------------|---------------------------|-----------------|---------------|--------------|--------------|----------|------|

|                      | Fast (                    | Corner          | –6 Speed      | –7 Speed     | –7 Speed     | –8 Speed |      |

| Parameter            | Industrial/<br>Automotive | Commercial      | Grade         | Grade<br>(1) | Grade<br>(2) | Grade    | Unit |

| t <sub>CIN</sub>     | 1.212                     | 1.267           | 2.210         | 2.351        | 2.54         | 2.540    | ns   |

| t <sub>COUT</sub>    | 1.214                     | 1.269           | 2.226         | 2.364        | 2.548        | 2.548    | ns   |

| t <sub>PLLCIN</sub>  | -0.259                    | -0.277          | -0.043        | -0.095       | -0.106       | -0.096   | ns   |

| t <sub>pllcout</sub> | -0.257                    | -0.275          | -0.027        | -0.082       | -0.098       | -0.088   | ns   |

### *Notes to Table 5–22:*

(1) These numbers are for commercial devices.

(2) These numbers are for automotive devices.

### EP2C8/A Clock Timing Parameters

Tables 5–23 and 5–24 show the clock timing parameters for EP2C8/A devices.

| Table 5–23. EF      | 2C8/A Column              | n Pins Global ( | Clock Timing F | Parameters (P | art 1 of 2)  |                   |      |

|---------------------|---------------------------|-----------------|----------------|---------------|--------------|-------------------|------|

|                     | Fast (                    | Corner          | –6 Speed       | –7 Speed      | –7 Speed     | _8 Snood          |      |

| Parameter           | Industrial/<br>Automotive | Commercial      | Grade          | Grade<br>(1)  | Grade<br>(2) | –8 Speed<br>Grade | Unit |

| t <sub>CIN</sub>    | 1.339                     | 1.404           | 2.405          | 2.565         | 2.764        | 2.774             | ns   |

| t <sub>COUT</sub>   | 1.353                     | 1.419           | 2.439          | 2.597         | 2.793        | 2.803             | ns   |

| t <sub>PLLCIN</sub> | -0.193                    | -0.204          | 0.055          | 0.015         | 0.016        | 0.026             | ns   |

| Table 5–45. Maximum Output Clock Toggle Rate on Cyclone II Devices (Part 4 of 4) |                 |                                                              |                      |                      |                      |                      |                      |                      |                      |                      |

|----------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

|                                                                                  |                 | Maximum Output Clock Toggle Rate on Cyclone II Devices (MHz) |                      |                      |                      |                      |                      |                      |                      |                      |

| I/O Standard                                                                     | Drive           | Colun                                                        | ın I/O Pi            | ns (1)               | Row                  | / I/O Pin            | s (1)                | Ded                  | icated C<br>Outputs  |                      |

|                                                                                  | Strength        | –6<br>Speed<br>Grade                                         | –7<br>Speed<br>Grade | –8<br>Speed<br>Grade | –6<br>Speed<br>Grade | –7<br>Speed<br>Grade | –8<br>Speed<br>Grade | –6<br>Speed<br>Grade | –7<br>Speed<br>Grade | –8<br>Speed<br>Grade |

| 1.5V_                                                                            | 8 mA            | 210                                                          | 170                  | 140                  | 210                  | 170                  | 140                  | 210                  | 170                  | 140                  |

| DIFFERENTIAL_HSTL<br>CLASS I                                                     | 10 mA           | 220                                                          | 180                  | 150                  | —                    | —                    | —                    | _                    |                      | -                    |

| _02/00_1                                                                         | 12 mA           | 230                                                          | 190                  | 160                  | —                    | _                    | —                    | _                    | —                    | —                    |

| 1.5V_<br>DIFFERENTIAL_HSTL<br>_CLASS_II                                          | 16 mA           | 210                                                          | 170                  | 140                  | _                    | _                    | _                    | _                    |                      |                      |

| LVDS                                                                             | —               | 400                                                          | 340                  | 280                  | 400                  | 340                  | 280                  | 400                  | 340                  | 280                  |

| RSDS                                                                             | —               | 400                                                          | 340                  | 280                  | 400                  | 340                  | 280                  | 400                  | 340                  | 280                  |

| MINI_LVDS                                                                        | —               | 400                                                          | 340                  | 280                  | 400                  | 340                  | 280                  | 400                  | 340                  | 280                  |

| SIMPLE_RSDS                                                                      | —               | 380                                                          | 320                  | 260                  | 380                  | 320                  | 260                  | 380                  | 320                  | 260                  |

| 1.2V_HSTL                                                                        | —               | 80                                                           | 80                   | 80                   | —                    | _                    | —                    |                      | —                    | —                    |

| 1.2V_<br>DIFFERENTIAL_HSTL                                                       | —               | 80                                                           | 80                   | 80                   | —                    | —                    | —                    | -                    |                      | _                    |

| PCI                                                                              | —               |                                                              | —                    | _                    | 350                  | 315                  | 280                  | 350                  | 315                  | 280                  |

| PCI-X                                                                            | —               |                                                              | —                    | —                    | 350                  | 315                  | 280                  | 350                  | 315                  | 280                  |

| LVTTL                                                                            | OCT_25_<br>OHMS | 360                                                          | 300                  | 250                  | 360                  | 300                  | 250                  | 360                  | 300                  | 250                  |

| LVCMOS                                                                           | OCT_25_<br>OHMS | 360                                                          | 300                  | 250                  | 360                  | 300                  | 250                  | 360                  | 300                  | 250                  |

| 2.5V                                                                             | OCT_50_<br>OHMS | 240                                                          | 200                  | 160                  | 240                  | 200                  | 160                  | 240                  | 200                  | 160                  |

| 1.8V                                                                             | OCT_50_<br>OHMS | 290                                                          | 240                  | 200                  | 290                  | 240                  | 200                  | 290                  | 240                  | 200                  |

| SSTL_2_CLASS_I                                                                   | OCT_50_<br>OHMS | 240                                                          | 200                  | 160                  | 240                  | 200                  | 160                  | _                    | _                    | _                    |

| SSTL_18_CLASS_I                                                                  | OCT_50_<br>OHMS | 290                                                          | 240                  | 200                  | 290                  | 240                  | 200                  | _                    |                      | _                    |

Note to Table 5–45:

(1) This is based on single data rate I/Os.

|                |          | Ma                   | aximum               | Output (             | Clock To             | ggle Ra              | te Derat             | ing Fact             | ors (ps/p            | oF)                  |

|----------------|----------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| I/O Standard   | Drive    | Colu                 | umn I/O              | Pins                 | Ro                   | ow I/O Pi            | ins                  | Ded                  | icated C<br>Outputs  |                      |

|                | Strength | –6<br>Speed<br>Grade | –7<br>Speed<br>Grade | –8<br>Speed<br>Grade | –6<br>Speed<br>Grade | –7<br>Speed<br>Grade | –8<br>Speed<br>Grade | –6<br>Speed<br>Grade | –7<br>Speed<br>Grade | –8<br>Speed<br>Grade |

| LVTTL          | 4 mA     | 438                  | 439                  | 439                  | 338                  | 362                  | 387                  | 338                  | 362                  | 387                  |

|                | 8 mA     | 306                  | 321                  | 336                  | 267                  | 283                  | 299                  | 267                  | 283                  | 299                  |

|                | 12 mA    | 139                  | 179                  | 220                  | 193                  | 198                  | 202                  | 193                  | 198                  | 202                  |

|                | 16 mA    | 145                  | 158                  | 172                  | 139                  | 147                  | 156                  | 139                  | 147                  | 156                  |

|                | 20 mA    | 65                   | 77                   | 90                   | 74                   | 79                   | 84                   | 74                   | 79                   | 84                   |

|                | 24 mA    | 19                   | 20                   | 21                   | 14                   | 18                   | 22                   | 14                   | 18                   | 22                   |

| LVCMOS         | 4 mA     | 298                  | 305                  | 313                  | 197                  | 205                  | 214                  | 197                  | 205                  | 214                  |

|                | 8 mA     | 190                  | 205                  | 219                  | 112                  | 118                  | 125                  | 112                  | 118                  | 125                  |

|                | 12 mA    | 43                   | 72                   | 101                  | 27                   | 31                   | 35                   | 27                   | 31                   | 35                   |

|                | 16 mA    | 87                   | 99                   | 110                  | —                    | —                    | —                    | —                    | —                    | _                    |

|                | 20 mA    | 36                   | 46                   | 56                   | —                    | —                    | —                    | —                    | —                    | _                    |

|                | 24 mA    | 24                   | 25                   | 27                   | _                    | _                    | _                    | _                    | _                    | _                    |

| 2.5V           | 4 mA     | 228                  | 233                  | 237                  | 270                  | 306                  | 343                  | 270                  | 306                  | 343                  |

|                | 8 mA     | 173                  | 177                  | 180                  | 191                  | 199                  | 208                  | 191                  | 199                  | 208                  |

|                | 12 mA    | 119                  | 121                  | 123                  | —                    | —                    | —                    | —                    | —                    | —                    |

|                | 16 mA    | 64                   | 65                   | 66                   | —                    | —                    | —                    | —                    | —                    | —                    |

| 1.8V           | 2 mA     | 452                  | 457                  | 461                  | 332                  | 367                  | 403                  | 332                  | 367                  | 403                  |

|                | 4 mA     | 321                  | 347                  | 373                  | 244                  | 291                  | 337                  | 244                  | 291                  | 337                  |

|                | 6 mA     | 227                  | 255                  | 283                  | 178                  | 222                  | 266                  | 178                  | 222                  | 266                  |

|                | 8 mA     | 37                   | 118                  | 199                  | 58                   | 133                  | 207                  | 58                   | 133                  | 207                  |

|                | 10 mA    | 41                   | 72                   | 103                  | 46                   | 85                   | 123                  | 46                   | 85                   | 123                  |

|                | 12 mA    | 7                    | 8                    | 10                   | 13                   | 28                   | 44                   | 13                   | 28                   | 44                   |

| 1.5V           | 2 mA     | 738                  | 764                  | 789                  | 540                  | 604                  | 669                  | 540                  | 604                  | 669                  |

|                | 4 mA     | 499                  | 518                  | 536                  | 300                  | 354                  | 408                  | 300                  | 354                  | 408                  |

|                | 6 mA     | 261                  | 271                  | 282                  | 60                   | 103                  | 146                  | 60                   | 103                  | 146                  |

|                | 8 mA     | 22                   | 25                   | 29                   |                      |                      |                      |                      | —                    | —                    |

| SSTL_2_CLASS_I | 8 mA     | 46                   | 47                   | 49                   | 25                   | 40                   | 56                   | 25                   | 40                   | 56                   |

|                | 12 mA    | 67                   | 69                   | 70                   | 23                   | 42                   | 60                   | 23                   | 42                   | 60                   |

(T/2 - D1) / T (the low percentage boundary)

(T/2 + D2) / T (the high percentage boundary)

## **DCD Measurement Techniques**

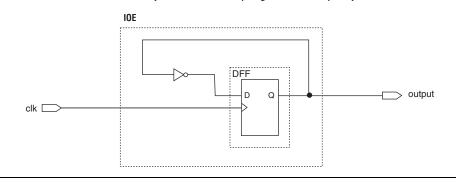

DCD is measured at an FPGA output pin driven by registers inside the corresponding I/O element (IOE) block. When the output is a single data rate signal (non-DDIO), only one edge of the register input clock (positive or negative) triggers output transitions (Figure 5–9). Therefore, any DCD present on the input clock signal, or caused by the clock input buffer, or different input I/O standard, does not transfer to the output signal.

Figure 5–9. DCD Measurement Technique for Non-DDIO (Single-Data Rate) Outputs

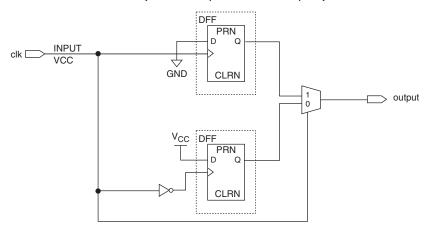

However, when the output is a double data rate input/output (DDIO) signal, both edges of the input clock signal (positive and negative) trigger output transitions (Figure 5–10). Therefore, any distortion on the input clock and the input clock buffer affect the output DCD.

Figure 5–10. DCD Measurement Technique for DDIO (Double-Data Rate) Outputs

When an FPGA PLL generates the internal clock, the PLL output clocks the IOE block. As the PLL only monitors the positive edge of the reference clock input and internally re-creates the output clock signal, any DCD present on the reference clock is filtered out. Therefore, the DCD for a DDIO output with PLL in the clock path is better than the DCD for a DDIO output without PLL in the clock path.

Tables 5–55 through 5–58 give the maximum DCD in absolution derivation for different I/O standards on Cyclone II devices. Examples are also provided that show how to calculate DCD as a percentage.

| Table 5–55. Maximum DCD for Single Data Outputs (SDR) on Row I/O         Pins       Notes (1), (2)       (Part 1 of 2) |     |     | I/O |      |

|------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Row I/O Output Standard                                                                                                | C6  | C7  | C8  | Unit |

| LVCMOS                                                                                                                 | 165 | 230 | 230 | ps   |

| LVTTL                                                                                                                  | 195 | 255 | 255 | ps   |

| 2.5-V                                                                                                                  | 120 | 120 | 135 | ps   |

| 1.8-V                                                                                                                  | 115 | 115 | 175 | ps   |

| 1.5-V                                                                                                                  | 130 | 130 | 135 | ps   |

| SSTL-2 Class I                                                                                                         | 60  | 90  | 90  | ps   |

| SSTL-2 Class II                                                                                                        | 65  | 75  | 75  | ps   |

| SSTL-18 Class I                                                                                                        | 90  | 165 | 165 | ps   |

| HSTL-15 Class I                                                                                                        | 145 | 145 | 205 | ps   |

| HSTL-18 Class I                                                                                                        | 85  | 155 | 155 | ps   |

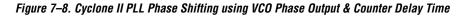

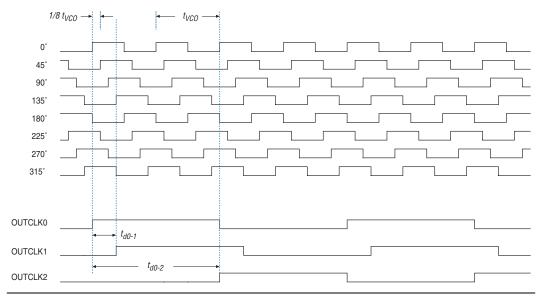

$\Delta t_{FINE}$  periods. OUTCLK2 is based off the 0° phase from the VCO but has the S value for the counter set to 3. This creates a delay of two  $\Delta t_{COARSE}$  periods.

## **Control Signals**

The four control signals in Cyclone II PLLs (pllena, areset, pfdena, and locked) control PLL operation.

### pllena

The PLL enable signal, pllena, enables and disables the PLL. You can either enable/disable a single PLL (by connecting pllena port independently) or multiple PLLs (by connecting pllena ports together). The pllena signal is an active-high signal. When pllena is low, the PLL clock output ports are driven by GND and the PLL loses lock. All PLL counters, including gated lock counter return to default state. When pllena transitions high, the PLL relocks and resynchronizes to the input clock. In Cyclone II devices, the pllena port can be fed by an LE output or any general-purpose I/O pin. There is no dedicated pllena pin. This increases flexibility since each PLL can have its own pllena control circuitry or all PLLs can share the same pllena circuitry. The pllena signal is optional. When it is not enabled in the Quartus II software, the port is internally tied to V<sub>CC</sub>.

| Table 8–2. Number o | Table 8–2. Number of M4K Blocks in Cyclone II Devices (Part 2 of 2) |                |  |  |  |

|---------------------|---------------------------------------------------------------------|----------------|--|--|--|

| Device              | M4K Blocks                                                          | Total RAM Bits |  |  |  |

| EP2C50              | 129                                                                 | 594,432        |  |  |  |

| EP2C70              | 250                                                                 | 1,152,000      |  |  |  |

# **Control Signals**

Figure 8–1 shows how the register clocks, clears, and control signals are implemented in the Cyclone II memory block.

The clock enable control signal controls the clock entering the entire memory block, not just the input and output registers. The signal disables the clock so that the memory block does not see any clock edges and will not perform any operations.

Cyclone II devices do not support asynchronous clear signals to input registers. Only output registers support asynchronous clears. There are three ways to reset the registers in the M4K blocks: power up the device, use the aclr signal for output register only, or assert the device-wide reset signal using the DEV\_CLRn option.

When applied to output registers, the asynchronous clear signal clears the output registers and the effects are seen immediately.

# Cyclone II DDR Memory Support Overview

Table 9–1 shows the external memory interfaces supported in Cyclone II devices.

| Table 9–1. External | Memory Support in Cyclo | ne II Devices Not    | te (1)                                   |                                          |

|---------------------|-------------------------|----------------------|------------------------------------------|------------------------------------------|

| Memory Standard     | I/O Standard            | Maximum Bus<br>Width | Maximum Clock<br>Rate Supported<br>(MHz) | Maximum Data<br>Rate Supported<br>(Mbps) |

| DDR SDRAM           | SSTL-2 class I (2)      | 72                   | 167                                      | 333 (1)                                  |

|                     | SSTL-2 class II (2)     | 72                   | 133                                      | 267 (1)                                  |

| DDR2 SDRAM          | SSTL-18 class I (2)     | 72                   | 167                                      | 333 (1)                                  |

|                     | SSTL-18 class II (3)    | 72                   | 125                                      | 250 (1)                                  |

| QDRII SRAM (4)      | 1.8-V HSTL class I (2)  | 36                   | 167                                      | 667 (1)                                  |

|                     | 1.8-V HSTL class II (3) | 36                   | 100                                      | 400 (1)                                  |

Notes to Table 9–1:

(1) The data rate is for designs using the clock delay control circuitry.

(2) These I/O standards are supported on all the I/O banks of the Cyclone II device.

(3) These I/O standards are supported only on the I/O banks on the top and bottom of the Cyclone II device.

(4) For maximum performance, Altera recommends using the 1.8-V HSTL I/O standard because of higher I/O drive strength. QDRII SRAM devices also support the 1.5-V HSTL I/O standard.

Cyclone II devices support the data strobe or read clock signal (DQS) used in DDR SDRAM with the clock delay control circuitry that can shift the incoming DQS signals to center them within the data window. To achieve DDR operation, the DDR input and output registers are implemented using the internal logic element (LE) registers. You should use the altdqs and altdq megafunctions in the Quartus II software to implement the DDR registers used for DQS and DQ signals, respectively.

# Document Revision History

Table 9–4 shows the revision history for this document.

|                               | Iment Revision History                                                                                                                                                                                                                   |                                                                                                      |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Date &<br>Document<br>Version | Changes Made                                                                                                                                                                                                                             | Summary of Changes                                                                                   |

| February 2007<br>v3.1         | <ul> <li>Added document revision history.</li> <li>Added handpara note in "Data &amp; Data Strobe Pins" section.</li> <li>Updated "DDR Output Registers" section.</li> </ul>                                                             | <ul> <li>Elaboration of DDR2 and<br/>QDRII interfaces supported<br/>by I/O bank included.</li> </ul> |

| November<br>2005, v2.1        | <ul> <li>Introduction</li> <li>Updated Table 9–2.</li> <li>Updated Figure 9–7.</li> </ul>                                                                                                                                                |                                                                                                      |

| July 2005, v2.0               | Updated Table 9–2.                                                                                                                                                                                                                       |                                                                                                      |

| November<br>2004, v1.1        | <ul> <li>Moved the "External Memory Interface Standards" section to follow the "Introduction" section.</li> <li>Updated the "Data &amp; Data Strobe Pins" section.</li> <li>Updated Figures 9–11, 9–12, 9–15, 9–16, and 9–17.</li> </ul> |                                                                                                      |

| June 2004, v1.0               | Added document to the Cyclone II Device Handbook.                                                                                                                                                                                        |                                                                                                      |

# I/O Driver Impedance Matching (R<sub>S</sub>) and Series Termination (R<sub>S</sub>)

Cyclone II devices support driver impedance matching to the impedance of the transmission line, typically 25 or 50  $\Omega$  When used with the output drivers, on-chip termination (OCT) sets the output driver impedance to 25 or 50  $\Omega$ by choosing the driver strength. Once matching impedance is selected, driver current can not be changed. Table 10–7 provides a list of output standards that support impedance matching. All I/O banks and I/O pins support impedance matching and series termination. Dedicated configuration pins and JTAG pins do not support impedance matching or series termination.

| I/O Standard     | Target R <sub>S</sub> (Ω) |

|------------------|---------------------------|

| 3.3-V LVTTL/CMOS | 25 (1)                    |

| 2.5-V LVTTL/CMOS | 50 (1)                    |

| 1.8-V LVTTL/CMOS | 50 (1)                    |

| SSTL-2 class I   | 50 (1)                    |

| SSTL-18 class I  | 50 (1)                    |

#### Note to Table 10–7:

(1) These RS values are nominal values. Actual impedance varies across process, voltage, and temperature conditions. Tolerance is specified in the DC Characteristics and Timing Specifications chapter in volume 1 of the Cyclone II Handbook.

# Pad Placement and DC Guidelines

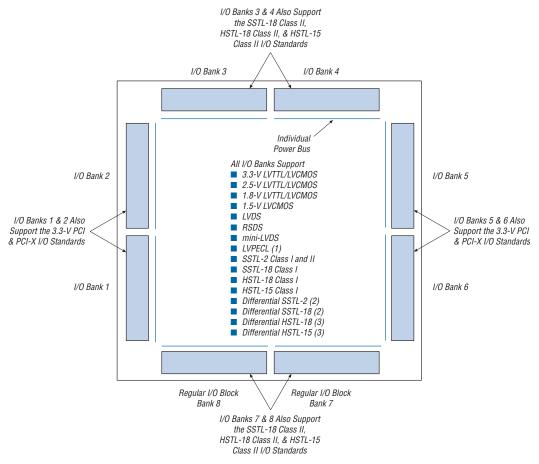

This section provides pad placement guidelines for the programmable I/O standards supported by Cyclone II devices and includes essential information for designing systems using the devices' selectable I/O capabilities. This section also discusses the DC limitations and guidelines.

Quartus II software provides user controlled restriction relaxation options for some placement constraints. When a default restriction is relaxed by a user, the Quartus II fitter generates warnings.

For more information about how Quartus II software checks I/O restrictions, refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook*.

Figure 11-2. I/O Banks in EP2C15, EP2C20, EP2C35, EP2C50 & EP2C70 Devices

#### Notes to Figure 11–2:

- (1) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (2) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (3) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

# Cyclone II High-Speed I/O Interface

Cyclone II devices provide a multi-protocol interface that allows communication between a variety of I/O standards, including LVDS, LVPECL, RSDS, mini-LVDS, differential HSTL, and differential SSTL. This feature makes the Cyclone II device family ideal for applications that require multiple I/O standards, such as protocol translation. See the *Cyclone II Memory Blocks* chapter in Volume 1 of the *Cyclone II Device Handbook* for more information on Cyclone II M4K memory blocks.

Refer to *AN 306: Techniques for Implementing Multipliers in FPGA Devices* for more information on soft multipliers.

# Architecture

Each embedded multiplier consists of the following elements:

- Multiplier stage

- Input and output registers

- Input and output interfaces

Figure 12–2 shows the multiplier block architecture.

Note to Figure 12-2:

(1) If necessary, you can send these signals through one register to match the data signal path.

## **Input Registers**

You can send each multiplier input signal into an input register or directly into the multiplier in 9- or 18-bit sections depending on the operational mode of the multiplier. You can send each multiplier input signal through a register independently of each other (e.g., you can send the multiplier's Cyclone II devices offer an optional INIT\_DONE pin which signals the end of initialization and the start of user mode with a low-to-high transition. The **Enable INIT\_DONE output** option is available in the Quartus II software from the **General** tab of the **Device & Pin Options** window. If you use the INIT\_DONE pin, an external 10-k $\Omega$  pull-up resistor is required to pull the signal high when nCONFIG is low and during the beginning of configuration. Once the optional bit to enable INIT\_DONE is programmed into the device (during the first frame of configuration data), the INIT\_DONE pin goes low. When initialization is complete, the INIT\_DONE pin is released and pulled high. This low-to-high transition signals that the FPGA has entered user mode. If you do not use the INIT\_DONE pin, the initialization period is complete after CONF\_DONE goes high and 299 clock cycles are sent to the CLKUSR pin or after the time t<sub>CF2UM</sub> (see Table 13–8) if the Cyclone II device uses the internal oscillator.

### User Mode

When initialization is complete, the FPGA enters user mode. In user mode, the user I/O pins no longer have weak pull-up resistors and function as assigned in your design.

When the Cyclone II device is in user mode, you can initiate reconfiguration by pulling the nCONFIG signal low. The nCONFIG signal should be low for at least 2 µs. When nCONFIG is pulled low, the Cyclone II device is reset and enters the reset stage. The Cyclone II device also pulls nSTATUS and CONF\_DONE low and all I/O pins are tri-stated. Once nCONFIG returns to a logic high level and nSTATUS is released by the Cyclone II device, reconfiguration begins.

## Error During Configuration

If an error occurs during configuration, the Cyclone II device drives the nSTATUS signal low to indicate a data frame error, and the CONF\_DONE signal stays low. If you enable the **Auto-restart configuration after error** option in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box, the Cyclone II device resets the serial configuration device by pulsing nCSO, releases nSTATUS after a reset time-out period (about 40 µs), and retries configuration. If the **Auto-restart configuration after error** option is turned off, the external system must monitor nSTATUS for errors and then pull nCONFIG low for at least 2 µs to restart configuration.

If you use the optional CLKUSR pin and the nCONFIG pin is pulled low to restart configuration during device initialization, ensure CLKUSR continues to toggle during the time nSTATUS is low (a maximum of 40 μs).

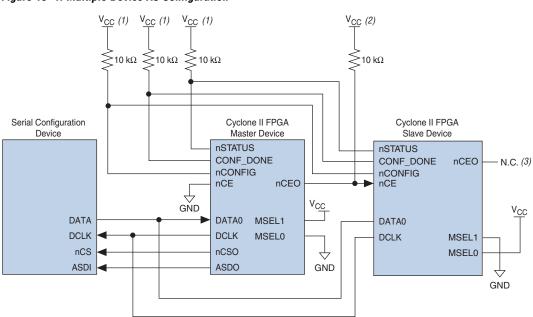

Figure 13–4. Multiple Device AS Configuration

#### Notes to Figure 13-4:

(1) Connect the pull-up resistors to a 3.3-V supply.

(2) Connect the pull-up resistor to the V<sub>CCIO</sub> supply voltage of I/O bank that the nCEO pin resides in.

(3) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed another device's nCE pin.

As shown in Figure 13–4, the nSTATUS and CONF\_DONE pins on all target FPGAs are connected together with external pull-up resistors. These pins are open-drain bidirectional pins on the FPGAs. When the first device asserts nCEO (after receiving all of its configuration data), it releases its CONF\_DONE pin. However, the subsequent devices in the chain keep the CONF\_DONE signal low until they receive their configuration data. When all the target FPGAs in the chain have received their configuration data and have released CONF\_DONE, the pull-up resistor pulls this signal high, and all devices simultaneously enter initialization mode.

<code>nCONFIG</code> low for at least 2 µs to restart configuration. The microprocessor or controller can only transition the <code>nCONFIG</code> pin low if the pin is under system control and not tied to  $V_{CC}$ .

The enhanced configuration devices support parallel configuration of up to eight devices. The *n*-bit (n = 1, 2, 4, or 8) PS configuration mode allows enhanced configuration devices to concurrently configure a chain of FPGAs. These devices do not have to be the same device family or density; they can be any combination of Altera FPGAs with different designs. An individual enhanced configuration device DATA pin is available for each targeted FPGA. Each DATA line can also feed a chain of FPGAs. Figure 13–15 shows how to concurrently configure multiple devices using an enhanced configuration device.

In addition, because the nSTATUS pins are connected, all the Cyclone II devices in the chain stop configuration if any device detects an error. If this happens, you must manually restart configuration in the Quartus II software.

Figure 13–20 shows how to configure multiple Cyclone II devices with a download cable.

| Pin Name | User<br>Mode | Configuration<br>Scheme | Pin Type                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|--------------|-------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nSTATUS  | N/A          | All                     | Bidirectional open-drain | The Cyclone II device drives nSTATUS low immediately after power-up and releases it after the POR time.                                                                                                                                                                                                                                                                                                                                                         |

|          |              |                         |                          | This pin provides a status output and input for the<br>Cyclone II device. If the Cyclone II device detects an<br>error during configuration, it drives the nSTATUS pin<br>low to stop configuration. If an external source (for<br>example, another Cyclone II device) drives the<br>nSTATUS pin low during configuration or<br>initialization, the target device enters an error state.<br>Driving nSTATUS low after configuration and                         |

|          |              |                         |                          | initialization does not affect the configured device. If<br>your design uses a configuration device, driving<br>nSTATUS low causes the configuration device to<br>attempt to configure the FPGA, but since the FPGA<br>ignores transitions on nSTATUS in user mode, the<br>FPGA does not reconfigure. To initiate a<br>reconfiguration, pull the nCONFIG pin low.                                                                                               |

|          |              |                         |                          | The enhanced configuration devices' and EPC2 devices' OE and nCS pins are connected to the Cyclone II device's nSTATUS and CONF_DONE pins, respectively, and have optional internal programmable pull-up resistors. If you use these internal pull-up resistors on the enhanced configuration device, do not use external 10-k $\Omega$ pull-up resistors on these pins. When using EPC2 devices, you should only use external 10-k $\Omega$ pull-up resistors. |

|          |              |                         |                          | The input buffer on this pin supports hysteresis using Schmitt trigger circuitry.                                                                                                                                                                                                                                                                                                                                                                               |

| Table 13–11. Dedicated Configuration Pins on the Cyclone II Device (Part 3 of 5) |              |                         |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|----------------------------------------------------------------------------------|--------------|-------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                                         | User<br>Mode | Configuration<br>Scheme | Pin Type                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| CONF_DONE                                                                        | N/A          | All                     | Bidirectional<br>open-drain | This pin is a status output and input.<br>The target Cyclone II device drives the CONF_DONE<br>pin low before and during configuration. Once the<br>Cyclone II device receives all the configuration data<br>without error and the initialization cycle starts, it<br>releases CONF_DONE. Driving CONF_DONE low<br>during user mode does not affect the configured<br>device. Do not drive CONF_DONE low before the<br>device enters user mode.<br>After the Cyclone II device receives all the data, the<br>CONF_DONE pin transitions high, and the device<br>initializes and enters user mode. The CONF_DONE<br>pin must have an external 10-k $\Omega$ pull-up resistor in<br>order for the device to initialize.<br>Driving CONF_DONE low after configured device.<br>The enhanced configuration devices' and EPC2<br>devices' OE and nCS pins are connected to the<br>Cyclone II device's nSTATUS and CONF_DONE pins,<br>respectively, and have optional internal<br>programmable pull-up resistors. If internal pull-up<br>resistors on the enhanced configuration device are<br>used, external 10-k $\Omega$ pull-up resistors should not be<br>used on these pins. When using EPC2 devices, you<br>should only use external 10-k $\Omega$ pull-up resistors.<br>The input buffer on this pin supports hysteresis using<br>Schmitt trigger circuitry. |  |  |

| nCE                                                                              | N/A          | All                     | Input                       | This pin is an active-low chip enable. The nCE pin<br>activates the device with a low signal to allow<br>configuration. The nCE pin must be held low during<br>configuration, initialization, and user mode. In single<br>device configuration, it should be tied low. In multiple<br>device configuration, nCE of the first device is tied low<br>while its nCEO pin is connected to nCE of the next<br>device in the chain.<br>The nCE pin must also be held low for successful<br>JTAG programming of the FPGA.<br>The input buffer on this pin supports hysteresis using<br>Schmitt trigger circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

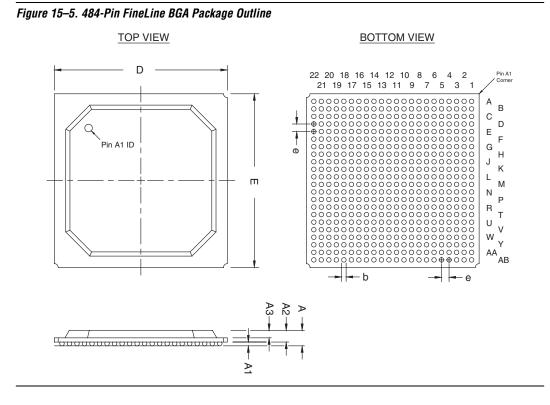

Figure 15–5 shows a 484-pin FineLine BGA package outline.