Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 1172                                                    |

| Number of Logic Elements/Cells | 18752                                                   |

| Total RAM Bits                 | 239616                                                  |

| Number of I/O                  | 152                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 256-LBGA                                                |

| Supplier Device Package        | 256-FBGA (17x17)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c20f256c7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

A LAB-wide asynchronous load signal to control the logic for the register's preset signal is not available. The register preset is achieved by using a NOT gate push-back technique. Cyclone II devices can only support either a preset or asynchronous clear signal.

In addition to the clear port, Cyclone II devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals.

## MultiTrack Interconnect

In the Cyclone II architecture, connections between LEs, M4K memory blocks, embedded multipliers, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive™ technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement within the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

The MultiTrack interconnect consists of row (direct link, R4, and R24) and column (register chain, C4, and C16) interconnects that span fixed distances. A routing structure with fixed-length resources for all devices allows predictable and repeatable performance when migrating through different device densities.

#### Row Interconnects

Dedicated row interconnects route signals to and from LABs, PLLs, M4K memory blocks, and embedded multipliers within the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks

- R4 interconnects traversing four blocks to the right or left

- R24 interconnects for high-speed access across the length of the device

### **Memory Modes**

Table 2–7 summarizes the different memory modes supported by the M4K memory blocks.

| Table 2–7. M4K Memory Modes       |                                                                                                                                                                                                 |  |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Memory Mode                       | Description                                                                                                                                                                                     |  |  |  |

| Single-port memory                | M4K blocks support single-port mode, used when simultaneous reads and writes are not required. Single-port memory supports non-simultaneous reads and writes.                                   |  |  |  |

| Simple dual-port memory           | Simple dual-port memory supports a simultaneous read and write.                                                                                                                                 |  |  |  |

| Simple dual-port with mixed width | Simple dual-port memory mode with different read and write port widths.                                                                                                                         |  |  |  |

| True dual-port memory             | True dual-port mode supports any combination of two-port operations: two reads, two writes, or one read and one write at two different clock frequencies.                                       |  |  |  |

| True dual-port with mixed width   | True dual-port mode with different read and write port widths.                                                                                                                                  |  |  |  |

| Embedded shift register           | M4K memory blocks are used to implement shift registers. Data is written into each address location at the falling edge of the clock and read from the address at the rising edge of the clock. |  |  |  |

| ROM                               | The M4K memory blocks support ROM mode. A MIF initializes the ROM contents of these blocks.                                                                                                     |  |  |  |

| FIFO buffers                      | A single clock or dual clock FIFO may be implemented in the M4K blocks. Simultaneous read and write from an empty FIFO buffer is not supported.                                                 |  |  |  |

Embedded Memory can be inferred in your HDL code or directly instantiated in the Quartus II software using the MegaWizard® Plug-in Manager Memory Compiler feature.

There are five dynamic control input signals that feed the embedded multiplier: signa, signb, clk, clkena, and aclr. signa and signb can be registered to match the data signal input path. The same clk, clkena, and aclr signals feed all registers within a single embedded multiplier.

For more information on Cyclone II embedded multipliers, see the *Embedded Multipliers in Cyclone II Devices* chapter.

# I/O Structure & Features

IOEs support many features, including:

- Differential and single-ended I/O standards

- 3.3-V, 64- and 32-bit, 66- and 33-MHz PCI compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- Output drive strength control

- Weak pull-up resistors during configuration

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors in user mode

- Programmable input and output delays

- Open-drain outputs

- DQ and DQS I/O pins

- V<sub>REF</sub> pins

Cyclone II device IOEs contain a bidirectional I/O buffer and three registers for complete embedded bidirectional single data rate transfer. Figure 2–20 shows the Cyclone II IOE structure. The IOE contains one input register, one output register, and one output enable register. You can use the input registers for fast setup times and output registers for fast clock-to-output times. Additionally, you can use the output enable (OE) register for fast clock-to-output enable timing. The Quartus II software automatically duplicates a single OE register that controls multiple output or bidirectional pins. You can use IOEs as input, output, or bidirectional pins.

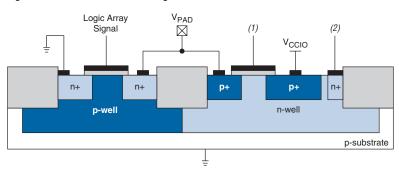

Figure 4–2. Transistor Level Diagram of FPGA Device I/O Buffers

*Notes to Figure 4–2:*

- (1) This is the logic array signal or the larger of either the  $V_{CCIO}$  or  $V_{PAD}$  signal.

- (2) This is the larger of either the  $V_{CCIO}$  or  $V_{PAD}$  signal.

# Power-On Reset Circuitry

Cyclone II devices contain POR circuitry to keep the device in a reset state until the power supply voltage levels have stabilized during power-up. The POR circuit monitors the  $V_{\rm CCINT}$  voltage levels and tri-states all user I/O pins until the  $V_{\rm CC}$  reaches the recommended operating levels. In addition, the POR circuitry also monitors the  $V_{\rm CCIO}$  level of the two I/O banks that contains configuration pins (I/O banks 1 and 3 for EP2C5 and EP2C8, I/O banks 2 and 6 for EP2C15A, EP2C20, EP2C35, EP2C50, and EP2C70) and tri-states all user I/O pins until the  $V_{\rm CC}$  reaches the recommended operating levels.

After the Cyclone II device enters user mode, the POR circuit continues to monitor the  $V_{CCINT}$  voltage level so that a brown-out condition during user mode can be detected. If the  $V_{CCINT}$  voltage sags below the POR trip point during user mode, the POR circuit resets the device. If the  $V_{CCIO}$  voltage sags during user mode, the POR circuit does not reset the device.

### "Wake-up" Time for Cyclone II Devices

In some applications, it may be necessary for a device to wake up very quickly in order to begin operation. The Cyclone II device family offers the Fast-On feature to support fast wake-up time applications. Devices that support the Fast-On feature are designated with an "A" in the ordering code and have stricter power up requirements compared to non-A devices.

| Table 5–3. DC Characteristics for User I/O, Dual-Purpose, and Dedicated Pins (Part 2 of 2) |                                                                                                      |                                                  |         |         |         |      |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------|---------|---------|------|

| Symbol                                                                                     | Parameter                                                                                            | Conditions                                       | Minimum | Typical | Maximum | Unit |

| R <sub>CONF</sub> (5) (6)                                                                  | Value of I/O pin                                                                                     | $V_{IN} = 0 \text{ V}; V_{CCIO} = 3.3 \text{ V}$ | 10      | 25      | 50      | kΩ   |

| pull-up resistor<br>before and during                                                      | V <sub>IN</sub> = 0 V; V <sub>CCIO</sub> = 2.5 V                                                     | 15                                               | 35      | 70      | kΩ      |      |

|                                                                                            | configuration                                                                                        | V <sub>IN</sub> = 0 V; V <sub>CCIO</sub> = 1.8 V | 30      | 50      | 100     | kΩ   |

|                                                                                            |                                                                                                      | V <sub>IN</sub> = 0 V; V <sub>CCIO</sub> = 1.5 V | 40      | 75      | 150     | kΩ   |

|                                                                                            |                                                                                                      | V <sub>IN</sub> = 0 V; V <sub>CCIO</sub> = 1.2 V | 50      | 90      | 170     | kΩ   |

|                                                                                            | Recommended<br>value of I/O pin<br>external pull-down<br>resistor before and<br>during configuration | (7)                                              | _       | 1       | 2       | kΩ   |

#### Notes to Table 5-3:

- All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (2) The minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to the voltages shown in Table 5-4, based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

- (3) This value is specified for normal device operation. The value may vary during power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, and 1.5 V).

- (4) Maximum values depend on the actual T<sub>J</sub> and design utilization. See the Excel-based PowerPlay Early Power Estimator (www.altera.com) or the Quartus II PowerPlay Power Analyzer feature for maximum values. Refer to "Power Consumption" on page 5–13 for more information.

- (5)  $R_{CONF}$  values are based on characterization.  $R_{CONF} = V_{CCIO}/I_{RCONF}$  values may be different if  $V_{IN}$  value is not 0 V. Pin pull-up resistance values will be lower if an external source drives the pin higher than  $V_{CCIO}$ .

- (6) Minimum condition at -40°C and high V<sub>CC</sub>, typical condition at 25°C and nominal V<sub>CC</sub> and maximum condition at 125°C and low V<sub>CC</sub> for R<sub>CONF</sub> values.

- (7) These values apply to all V<sub>CCIO</sub> settings.

Table 5–4 shows the maximum  $V_{\rm IN}$  overshoot voltage and the dependency on the duty cycle of the input signal. Refer to Table 5–3 for more information.

| Table 5–4. V <sub>IN</sub> Overshoot Voltage for All Input Buffers |           |  |  |  |

|--------------------------------------------------------------------|-----------|--|--|--|

| Maximum V <sub>IN</sub> (V) Input Signal Duty Cycle                |           |  |  |  |

| 4.0                                                                | 100% (DC) |  |  |  |

| 4.1                                                                | 90%       |  |  |  |

| 4.2                                                                | 50%       |  |  |  |

| 4.3                                                                | 30%       |  |  |  |

| 4.4                                                                | 17%       |  |  |  |

| 4.5                                                                | 10%       |  |  |  |

**Table 5–6. Recommended Operating Conditions for User I/O Pins Using Single-Ended I/O Standards**Note (1) (Part 2 of 2)

| I/O Standard           | V <sub>CCIO</sub> (V) |     | V <sub>REF</sub> (V) |       |      | V <sub>IL</sub> (V) | V <sub>IH</sub> (V)                                           |                                                               |

|------------------------|-----------------------|-----|----------------------|-------|------|---------------------|---------------------------------------------------------------|---------------------------------------------------------------|

| i/O Stallualu          | Min                   | Тур | Max                  | Min   | Тур  | Max                 | Max                                                           | Min                                                           |

| SSTL-18 class II       | 1.7                   | 1.8 | 1.9                  | 0.833 | 0.9  | 0.969               | V <sub>REF</sub> - 0.125 (DC)<br>V <sub>REF</sub> - 0.25 (AC) | V <sub>REF</sub> + 0.125 (DC)<br>V <sub>REF</sub> + 0.25 (AC) |

| 1.8-V HSTL<br>class I  | 1.71                  | 1.8 | 1.89                 | 0.85  | 0.9  | 0.95                | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

| 1.8-V HSTL<br>class II | 1.71                  | 1.8 | 1.89                 | 0.85  | 0.9  | 0.95                | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

| 1.5-V HSTL<br>class I  | 1.425                 | 1.5 | 1.575                | 0.71  | 0.75 | 0.79                | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

| 1.5-V HSTL<br>class II | 1.425                 | 1.5 | 1.575                | 0.71  | 0.75 | 0.79                | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

*Note to Table 5–6:*

<sup>(1)</sup> Nominal values (Nom) are for  $T_A$  = 25° C,  $V_{CCINT}$  = 1.2 V, and  $V_{CCIO}$  = 1.5, 1.8, 2.5, and 3.3 V.

| Table 5–7. DC Characteristics of User I/O Pins Using Single-Ended Standards Notes (1), (2) (Part 1 of 2) |                      |                      |                             |                             |  |  |

|----------------------------------------------------------------------------------------------------------|----------------------|----------------------|-----------------------------|-----------------------------|--|--|

| 1/0 0444                                                                                                 | Test Co              | nditions             | Voltage Thresholds          |                             |  |  |

| I/O Standard                                                                                             | I <sub>OL</sub> (mA) | I <sub>OH</sub> (mA) | Maximum V <sub>OL</sub> (V) | Minimum V <sub>OH</sub> (V) |  |  |

| 3.3-V LVTTL                                                                                              | 4                    | -4                   | 0.45                        | 2.4                         |  |  |

| 3.3-V LVCMOS                                                                                             | 0.1                  | -0.1                 | 0.2                         | V <sub>CCIO</sub> - 0.2     |  |  |

| 2.5-V LVTTL and LVCMOS                                                                                   | 1                    | -1                   | 0.4                         | 2.0                         |  |  |

| 1.8-V LVTTL and LVCMOS                                                                                   | 2                    | -2                   | 0.45                        | V <sub>CCIO</sub> - 0.45    |  |  |

| 1.5-V LVTTL and LVCMOS                                                                                   | 2                    | -2                   | 0.25 × V <sub>CCIO</sub>    | 0.75 × V <sub>CCIO</sub>    |  |  |

| PCI and PCI-X                                                                                            | 1.5                  | -0.5                 | 0.1 × V <sub>CCIO</sub>     | 0.9 × V <sub>CCIO</sub>     |  |  |

| SSTL-2 class I                                                                                           | 8.1                  | -8.1                 | V <sub>TT</sub> – 0.57      | V <sub>TT</sub> + 0.57      |  |  |

| SSTL-2 class II                                                                                          | 16.4                 | -16.4                | V <sub>TT</sub> – 0.76      | V <sub>TT</sub> + 0.76      |  |  |

| SSTL-18 class I                                                                                          | 6.7                  | -6.7                 | V <sub>TT</sub> – 0.475     | V <sub>TT</sub> + 0.475     |  |  |

| SSTL-18 class II                                                                                         | 13.4                 | -13.4                | 0.28                        | V <sub>CCIO</sub> - 0.28    |  |  |

| 1.8-V HSTL class I                                                                                       | 8                    | -8                   | 0.4                         | V <sub>CCIO</sub> - 0.4     |  |  |

| 1.8-V HSTL class II                                                                                      | 16                   | -16                  | 0.4                         | V <sub>CCIO</sub> - 0.4     |  |  |

You should select power supplies and regulators that can supply the amount of current required when designing with Cyclone II devices.

Altera recommends using the Cyclone II PowerPlay Early Power Estimator to estimate the user-mode  $I_{CCINT}$  consumption and then select power supplies or regulators based on the values obtained.

# Timing Specifications

The DirectDrive<sup>TM</sup> technology and MultiTrack<sup>TM</sup> interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Cyclone II device densities and speed grades. This section describes and specifies the performance, internal, external, high-speed I/O, JTAG, and PLL timing specifications.

This section shows the timing models for Cyclone II devices. Commercial devices meet this timing over the commercial temperature range. Industrial devices meet this timing over the industrial temperature range. Automotive devices meet this timing over the automotive temperature range. Extended devices meet this timing over the extended temperature range. All specifications are representative of worst-case supply voltage and junction temperature conditions.

#### Preliminary and Final Timing Specifications

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 5–14 shows the status of the Cyclone II device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

| Table 7–5. PLL | Table 7–5. PLL Output signals                                                                                                                                                                                       |                         |                                                |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------|--|--|--|

| Port           | Description                                                                                                                                                                                                         | Source                  | Destination                                    |  |  |  |

| c[20]          | PLL clock outputs driving the internal global clock network or external clock output pin (PLL<#>_OUT)                                                                                                               | PLL post-scale counter  | Global clock<br>network or<br>external I/O pin |  |  |  |

| Locked         | Gives the status of the PLL lock. When the PLL is locked, this port drives $V_{\text{CC}}$ . When the PLL is out of lock, this port drives GND. The locked port may pulse high and low during the PLL lock process. | PLL lock detect circuit | Logic array or output pin                      |  |  |  |

Table 7–6 shows a list of I/O standards supported in Cyclone II device PLLs.

| I/O Standard                                            | Input    | Output   |              |

|---------------------------------------------------------|----------|----------|--------------|

| I/O Standard                                            | inclk    | lock     | pll_out      |

| LVTTL (3.3, 2.5, and 1.8 V)                             | <b>✓</b> | <b>✓</b> | <b>✓</b>     |

| LVCMOS (3.3, 2.5, 1.8, and 1.5 V)                       | <b>✓</b> | ✓        | ~            |

| 3.3-V PCI                                               | ✓        | ✓        | <b>✓</b>     |

| 3.3-V PCI-X (1)                                         | <b>✓</b> | ✓        | <b>✓</b>     |

| LVPECL                                                  | ✓        |          |              |

| LVDS                                                    | <b>✓</b> | <b>✓</b> | <b>✓</b>     |

| 1.5 and 1.8 V differential<br>HSTL class I and class II | <b>✓</b> |          | <b>√</b> (2) |

| 1.8 and 2.5 V differential<br>SSTL class I and class II | <b>✓</b> |          | <b>√</b> (2) |

| 1.5-V HSTL class I                                      | ✓        | ✓        | <b>✓</b>     |

| 1.5-V HSTL class II (3)                                 | <b>✓</b> | <b>✓</b> | <b>✓</b>     |

| 1.8-V HSTL class I                                      | ✓        | ✓        | <b>✓</b>     |

| 1.8-V HSTL class II (3)                                 | <b>✓</b> | <b>✓</b> | <b>✓</b>     |

| SSTL-18 class I                                         | <b>✓</b> | <b>✓</b> | <b>✓</b>     |

| SSTL-18 class II (3)                                    | ✓        | ✓        | <b>✓</b>     |

| SSTL-25 class I                                         | <b>✓</b> | <b>✓</b> | <b>✓</b>     |

clock sources and the clkena signals for the global clock network multiplexers can be set through the Quartus II software using the altclkctrl megafunction.

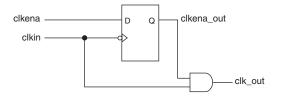

#### clkena signals

In Cyclone II devices, the clkena signals are supported at the clock network level. Figure 7–14 shows how the clkena is implemented. This allows you to gate off the clock even when a PLL is not being used. Upon re-enabling the output clock, the PLL does not need a resynchronization or relock period because the clock is gated off at the clock network level. Also, the PLL can remain locked independent of the clkena signals since the loop-related counters are not affected.

Figure 7-14. clkena Implementation

Figure 7–15 shows the waveform example for a clock output enable. clkena is synchronous to the falling edge of the clock (clkin).

This feature is useful for applications that require a low power or sleep mode. The exact amount of power saved when using this feature is pending device characterization. outputs, respectively. When the output registers are bypassed, the new data is available on the rising edge of the same clock cycle on which it was written. See "Read-During-Write Operation at the Same Address" on page 8–28 for waveforms and information on mixed-port read-during-write mode.

Potential write contentions must be resolved external to the RAM because writing to the same address location at both ports results in unknown data storage at that location.

For the maximum synchronous write cycle time, refer to the *Cyclone II Device Family Data Sheet* in volume 1 of the *Cyclone II Device Handbook*.

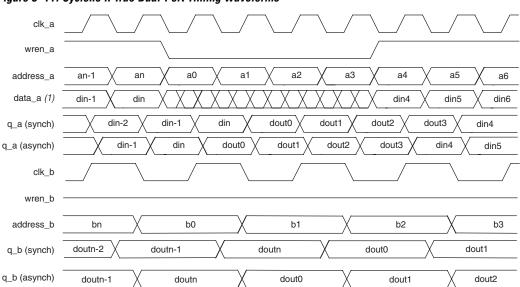

Figure 8–11 shows true dual-port timing waveforms for the write operation at port A and the read operation at port B.

Figure 8–11. Cyclone II True Dual-Port Timing Waveforms

*Note to Figure 8–11:*

The crosses in the data\_a waveform during write indicate "don't care."

### Shift Register Mode

Cyclone II memory blocks can implement shift registers for digital signal processing (DSP) applications, such as finite impulse response (FIR) filters, pseudo-random number generators, multi-channel filtering, and auto-correlation and cross-correlation functions. These and other DSP

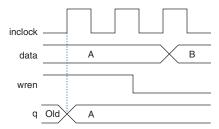

Figure 8–22. Cyclone II Same-Port Read-During-Write Functionality Note (1)

Note to Figure 8-22:

(1) Outputs are not registered.

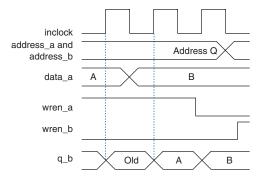

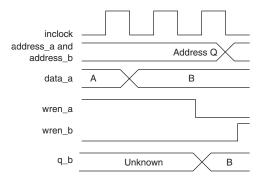

#### **Mixed-Port Read-During-Write Mode**

This mode applies to a RAM in simple or true dual-port mode, which has one port reading and the other port writing to the same address location with the same clock.

In this mode, you also have two output choices: old data or don't care. In Old Data Mode, a read-during-write operation to different ports causes the RAM outputs to reflect the old data at that address location. In Don't Care Mode, the same operation results in a "don't care" or unknown value on the RAM outputs.

Figure 8–23. Cyclone II Mixed-Port Read-During-Write: Old Data Mode Note (1)

Note to Figure 8-23:

(1) Outputs are not registered.

Figure 8–24. Cyclone II Mixed-Port Read-During-Write: Don't Care Mode Note (1)

Note to Figure 8-24:

(1) Outputs are not registered.

Mixed-port read-during-write is not supported when two different clocks are used in a dual-port RAM. The output value is unknown during a mixed-port read-during-write operation.

#### Conclusion

The M4K memory structure of Cyclone II devices provides a flexible memory architecture with high memory bandwidth. It addresses the needs of different memory applications in FPGA designs with features such as different memory modes, byte enables, parity bit storage, address clock enables, mixed clock mode, shift register mode, mixed-port width support, and true dual-port mode.

## Referenced Documents

This chapter references the following documents:

- Cyclone II Device Family Data Sheet in volume 1 of the Cyclone II Device Handbook

- Single- and Dual-Clock FIFO Megafunction User Guide

- Using Parity to Detect Errors White Paper

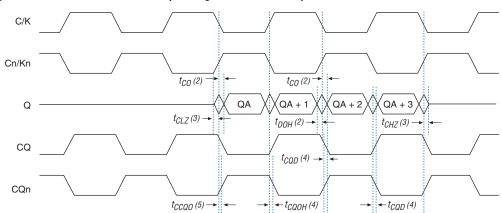

Figure 9-5. Data & Clock Relationship During a QDRII SRAM Report

#### *Notes to Figure 9–5:*

- (1) The timing parameter nomenclature is based on the Cypress QDRII SRAM data sheet for CY7C1313V18.

- (2)  $t_{CO}$  is the data clock-to-out time and  $t_{DOH}$  is the data output hold time between burst.

- (3)  $t_{\rm CLZ}$  and  $t_{\rm CHZ}$  are bus turn-on and turn-off times, respectively.

- (4) t<sub>COD</sub> is the skew between CQn and data edges.

- (5)  $t_{CCQO}$  and  $t_{CQOH}$  are skew measurements between the C or C# clocks (or the K or K# clocks in single-clock mode) and the CQ or CQn clocks.

When writing to QDRII SRAM devices, the write clock generates the data while the K clock is 90° shifted from the write clock, creating a centeraligned arrangement.

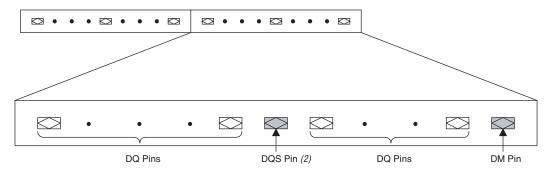

# DDR Memory Interface Pins

Cyclone II devices use data (DQ), data strobe (DQS), and clock pins to interface with external memory. Figure 9–6 shows the DQ and DQS pins in the  $\times 8/\times 9$  mode.

Figure 9–6. Cyclone II Device DQ & DQS Groups in ×8/×9 Mode Notes (1), (3)

#### Notes to Figure 9–6:

- (1) Each DQ group consists of a DQS pin, a DM pin, and up to nine DQ pins.

- (2) For the QDRII memory interface, other DQS pins implement the CQn pins. These pins are denoted by DQS/CQ# in the pin table.

- (3) This is an idealized pin layout. For the actual pin layout, refer to the pin tables in the PCB Layout Guidelines section of the Cyclone II Device Handbook, Volume 1.

#### **Data & Data Strobe Pins**

Cyclone II data pins for the DDR memory interfaces are called DQ pins. Cyclone II devices can use either bidirectional data strobes or unidirectional read clocks. Depending on the external memory interface, either the memory device's read data strobes or read clocks feed the DQS pins.

In Cyclone II devices, all the I/O banks support DDR and DDR2 SDRAM and QDRII SRAM memory at up to 167 MHz. All the I/O banks support DQS signals with the DQ bus modes of  $\times 8/\times 9$  and  $\times 16/\times 18$ . Cyclone II devices can support either bidirectional data strobes or unidirectional read clocks.

DDR2 and QDRII interfaces with class II I/O standard can only be implemented on the top and bottom I/O banks of the Cyclone II device.

The DQS pins are listed in the Cyclone II pin tables as DQS[1..0]T, DQS[1..0]B, DQS[1..0]B, DQS[1..0]B, and DQS[1..0]B for the EP2C5 and EP2C8 devices and DQS[5..0]T, DQS[5..0]B, DQS[3..0]L, and DQS[3..0]B for the larger devices. The T denotes pins on the top of the device, the B denotes pins on the bottom of the device, the L denotes pins on the left of the device, and the R denotes pins on the right of the device. The corresponding DQ pins are marked as DQ[5..0]T[8..0], where [5..0] indicates which DQS group the pins belong to.

In the Cyclone II pinouts, the DQ groups with 9 DQ pins are also used in the  $\times 8$  mode with the corresponding DQS pins, leaving the unused DQ pin available as a regular I/O pin. The DQ groups that have 18 DQ pins are also used in the  $\times 16$  mode with the corresponding DQS pins, leaving the two unused DQ pins available as regular I/O pins. For example, DQ1T[8..0] can be used in the  $\times 8$  mode, provided it is used with DQS1T. The remaining unused DQ pin, DQ1T8, is available as a regular I/O pin.

When not used as DQ or DQS pins, these pins are available as regular I/O pins. Table 9–3 shows the number of DQS pins supported in each I/O bank in each Cyclone II device density.

| Table 9–3. Available                         | DQS Pins in Each I/O | Note (1)        |               |                |

|----------------------------------------------|----------------------|-----------------|---------------|----------------|

| Device                                       | Top I/O Bank         | Bottom I/O Bank | Left I/O Bank | Right I/O Bank |

| EP2C5, EP2C8                                 | DQS[10]T             | DQS[10]B        | DQS[10]L      | DQS[10]R       |

| EP2C15, EP2C20,<br>EP2C35, EP2C50,<br>EP2C70 | DQS[50]B             | DQS[50]T        | DQS[30]L      | DQS[30]R       |

Note to Table 9-3:

(1) Numbers are preliminary.

The DQ pin numbering is based on ×8/×9 mode. There are up to 8 DQS/DQ groups in ×8 mode or 4 DQS/DQ groups in ×9 mode in I/O banks for EP2C5 and EP2C8. For the larger devices, there are up to 20 DQS/DQ groups in ×8 mode or 8 DQS/DQ groups in ×9 mode. Although there are up to 20 DQS/DQ groups in the ×8 mode available in the larger Cyclone II devices, but because of the available clock resources in the Cyclone II devices, only 16 DQS/DQ groups can be utilized for the external memory interface. There is a total of 16 global clock buses available for routing DQS signals but 2 of them are needed for routing the –90° write clock and the system clock to the external memory devices. This reduces the global clock resources to 14 global clock buses for routing DQS signals. Incoming DQS signals are all routed to the clock control block, and are then routed to the global clock bus to clock the DDR LE registers. For EP2C5 and EP2C8 devices, the DQS signals are routed

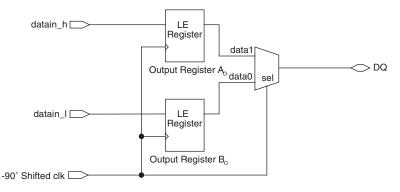

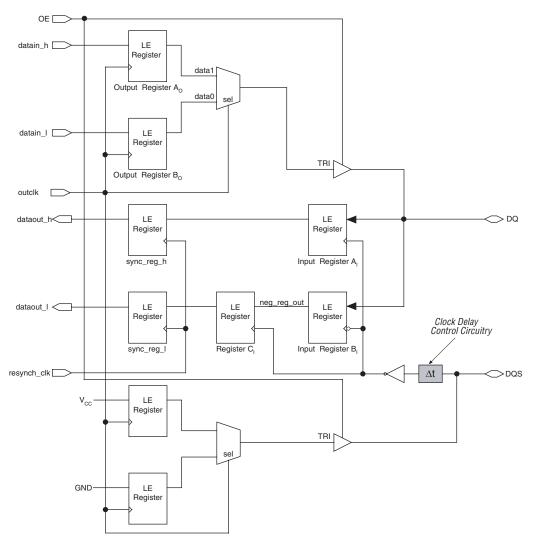

#### **DDR Output Registers**

Figure 9–14 shows a schematic representation of DDR output implemented in a Cyclone II device. The DDR output logic is implemented using LEs in the LAB adjacent to the output pin. Two registers synchronize two serial data streams. The registered outputs are then multiplexed by the common clock to drive the DDR output pin at two times the data rate.

Figure 9–14. DDR Output Implementation for DDR Memory Interfaces

While the clock signal is logic-high, the output from output register  $A_{\circ}$  is driven onto the DDR output pin. While the clock signal is logic-low, the output from output register  $B_{\circ}$  is driven onto the DDR output pin. The DDR output pin can be any available user I/O pin. Altera recommends the use of altdq and altdqs megafunctions to implement this output logic. This automatically provides the required tight placement and routing constraints on the LE registers and the output multiplexer.

Figure 9–15 shows examples of functional waveforms from a DDR output implementation.

Figure 9–16. Bidirectional DDR Implementation for DDR Memory Interfaces Note (1)

Note to Figure 9-16:

(1) You can use the altdq and altdqs megafunctions to generate the DQ and DQS signals.

Figure 9–17 shows example waveforms from a bidirectional DDR implementation.

#### 1.8-V LVCMOS (EIA/JEDEC Standard EIA/JESD8-7)

The 1.8-V I/O standard is used for 1.8-V LVCMOS applications. This standard defines the DC interface parameters for high-speed, low-voltage, non-terminated digital circuits driving or being driven by other 1.8-V parts.

The 1.8-V standard does not require input reference voltages or board terminations. Cyclone II devices support input and output levels for 1.8-V LVCMOS.

#### SSTL-18 Class I and II

The 1.8-V SSTL-18 standard is formulated under JEDEC Standard, JESD815: Stub Series Terminated Logic for 1.8V (SSTL-18).

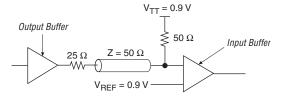

The SSTL-18 I/O standard is a 1.8-V memory bus standard used for applications such as high-speed DDR2 SDRAM interfaces. This standard is similar to SSTL-2 and defines input and output specifications for devices that are designed to operate in the SSTL-18 logic switching range 0.0 to 1.8 V. SSTL-18 requires a 0.9-V  $\rm V_{REF}$  and a 0.9-V  $\rm V_{TT}$ , with the termination resistors connected to both. There are no class definitions for the SSTL-18 standard in the JEDEC specification. The specification of this I/O standard is based on an environment that consists of both series and parallel terminating resistors. Altera provides solutions to two derived applications in JEDEC specification and names them class I and class II to be consistent with other SSTL standards. Figures 10–5 and 10–6 show SSTL-18 class I and II termination, respectively. Cyclone II devices support both input and output levels.

Figure 10-5. 1.8-V SSTL Class I Termination

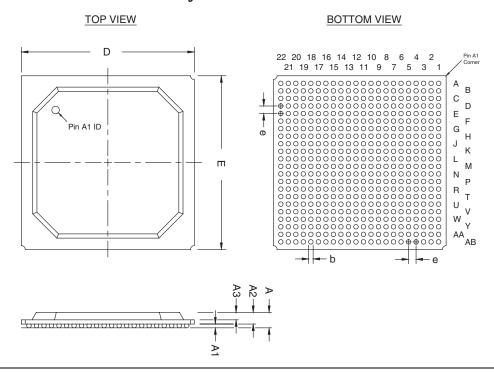

# 15. Package Information for Cyclone II Devices

CII51015-2.3

### Introduction

This chapter provides package information for Altera® Cyclone® II devices, including:

- Device and package cross reference

- Thermal resistance values

- Package outlines

Table 15–1 shows Cyclone II device package options.

| Table 15-1. | Table 15–1. Cyclone II Device Package Options |      |  |  |  |

|-------------|-----------------------------------------------|------|--|--|--|

| Device      | Package                                       | Pins |  |  |  |

| EP2C5       | Plastic Thin Quad Flat Pack (TQFP) – Wirebond | 144  |  |  |  |

|             | Plastic Quad Flat Pack (PQFP) - Wirebond      | 208  |  |  |  |

|             | Low profile FineLine BGA® – Wirebond          | 256  |  |  |  |

| EP2C8       | TQFP – Wirebond                               | 144  |  |  |  |

|             | PQFP – Wirebond                               | 208  |  |  |  |

|             | Low profile FineLine BGA – Wirebond           | 256  |  |  |  |

| EP2C15      | Low profile FineLine BGA, Option 2 – Wirebond | 256  |  |  |  |

|             | FineLine BGA, Option 3– Wirebond              | 484  |  |  |  |

| EP2C20      | PQFP – Wirebond                               | 240  |  |  |  |

|             | Low profile FineLine BGA, Option 2 – Wirebond | 256  |  |  |  |

|             | FineLine BGA, Option 3– Wirebond              | 484  |  |  |  |

| EP2C35      | FineLine BGA, Option 3 – Wirebond             | 484  |  |  |  |

|             | Ultra FineLine BGA – Wirebond                 | 484  |  |  |  |

|             | FineLine BGA, Option 3 – Wirebond             | 672  |  |  |  |

| EP2C50      | FineLine BGA, Option 3 – Wirebond             | 484  |  |  |  |

|             | Ultra FineLine BGA – Wirebond                 | 484  |  |  |  |

|             | FineLine BGA, Option 3 – Wirebond             | 672  |  |  |  |

| EP2C70      | FineLine BGA, Option 3 – Wirebond             | 672  |  |  |  |

|             | FineLine BGA – Wirebond                       | 896  |  |  |  |

Figure 15–5 shows a 484-pin FineLine BGA package outline.

Figure 15-5. 484-Pin FineLine BGA Package Outline