Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 1172                                                     |

| Number of Logic Elements/Cells | 18752                                                    |

| Total RAM Bits                 | 239616                                                   |

| Number of I/O                  | 152                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 256-LBGA                                                 |

| Supplier Device Package        | 256-FBGA (17x17)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c20f256c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

R24 row interconnects span 24 LABs and provide the fastest resource for long row connections between non-adjacent LABs, M4K memory blocks, dedicated multipliers, and row IOEs. R24 row interconnects drive to other row or column interconnects at every fourth LAB. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects and do not drive directly to LAB local interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

#### **Column Interconnects**

The column interconnect operates similar to the row interconnect. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs, M4K memory blocks, embedded multipliers, and row and column IOEs. These column resources include:

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four blocks in an up and down direction

- C16 interconnects for high-speed vertical routing through the device

Cyclone II devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using register chain connections. The register chain connection allows the register output of one LE to connect directly to the register input of the next LE in the LAB for fast shift registers. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–9 shows the register chain interconnects.

#### **PLLs**

Cyclone II PLLs provide general-purpose clocking as well as support for the following features:

- Clock multiplication and division

- Phase shifting

- Programmable duty cycle

- Up to three internal clock outputs

- One dedicated external clock output

- Clock outputs for differential I/O support

- Manual clock switchover

- Gated lock signal

- Three different clock feedback modes

- Control signals

Cyclone II devices contain either two or four PLLs. Table 2–3 shows the PLLs available for each Cyclone II device.

| Table 2–3. Cy | Table 2–3. Cyclone II Device PLL Availability |          |          |      |  |  |  |  |  |  |

|---------------|-----------------------------------------------|----------|----------|------|--|--|--|--|--|--|

| Device        | PLL1                                          | PLL2     | PLL3     | PLL4 |  |  |  |  |  |  |

| EP2C5         | <b>✓</b>                                      | <b>✓</b> |          |      |  |  |  |  |  |  |

| EP2C8         | ✓                                             | ✓        |          |      |  |  |  |  |  |  |

| EP2C15        | <b>✓</b>                                      | <b>✓</b> | <b>✓</b> | ✓    |  |  |  |  |  |  |

| EP2C20        | <b>✓</b>                                      | ~        | ✓        | ~    |  |  |  |  |  |  |

| EP2C35        | <b>✓</b>                                      | <b>✓</b> | <b>✓</b> | ✓    |  |  |  |  |  |  |

| EP2C50        | <b>✓</b>                                      | ~        | ✓        | ~    |  |  |  |  |  |  |

| EP2C70        | ✓                                             | ✓        | ✓        | ✓    |  |  |  |  |  |  |

| Table 5–7. DC Characteristics of User I/O Pins Using Single-Ended Standards       Notes (1), (2) (Part 2 of 2) |                                           |          |                             |                             |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------|-----------------------------|-----------------------------|--|--|--|--|--|

| I/O Ctondoud                                                                                                   | Test Co                                   | nditions | Voltage Thresholds          |                             |  |  |  |  |  |

| I/O Standard                                                                                                   | I <sub>OL</sub> (mA) I <sub>OH</sub> (mA) |          | Maximum V <sub>OL</sub> (V) | Minimum V <sub>OH</sub> (V) |  |  |  |  |  |

| 1.5-V HSTL class I                                                                                             | 8                                         | -8       | 0.4                         | V <sub>CCIO</sub> - 0.4     |  |  |  |  |  |

| 1.5V HSTL class II                                                                                             | 16                                        | -16      | 0.4                         | V <sub>CCIO</sub> - 0.4     |  |  |  |  |  |

#### Notes to Table 5-7:

- (1) The values in this table are based on the conditions listed in Tables 5–2 and 5–6.

- (2) This specification is supported across all the programmable drive settings available as shown in the Cyclone II Architecture chapter of the Cyclone II Device Handbook.

#### Differential I/O Standards

The RSDS and mini-LVDS I/O standards are only supported on output pins. The LVDS I/O standard is supported on both receiver input pins and transmitter output pins.

For more information on how these differential I/O standards are implemented, refer to the *High-Speed Differential Interfaces in Cyclone II Devices* chapter of the *Cyclone II Device Handbook*.

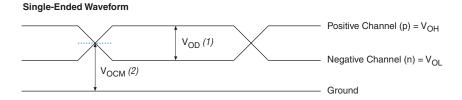

Figure 5–1 shows the receiver input waveforms for all differential I/O standards (LVDS, LVPECL, differential 1.5-V HSTL class I and II, differential 1.8-V HSTL class I and II, differential SSTL-2 class I and II, and differential SSTL-18 class I and II).

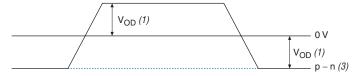

Figure 5–2 shows the transmitter output waveforms for all supported differential output standards (LVDS, mini-LVDS, RSDS, differential 1.5-V HSTL class I and II, differential 1.8-V HSTL class I and II, differential SSTL-2 class I and II, and differential SSTL-18 class I and II).

Figure 5–2. Transmitter Output Waveforms for Differential I/O Standards

#### Differential Waveform (Mathematical Function of Positive and Negative Channel)

#### Notes to Figure 5-2:

- (1)  $V_{OD}$  is the output differential voltage.  $V_{OD} = |p n|$ .

- (2)  $V_{OCM}$  is the output common mode voltage.  $V_{OCM} = (p + n)/2$ .

- (3) The p n waveform is a function of the positive channel (p) and the negative channel (n).

Table 5–9 shows the DC characteristics for user I/O pins with differential I/O standards.

| Table 5–9. DC Cl                                 | Table 5–9. DC Characteristics for User I/O Pins Using Differential I/O Standards Note (1) (Part 1 of 2) |     |     |                       |     |                      |      |       |                            |     |                     |     |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|-----|-----------------------|-----|----------------------|------|-------|----------------------------|-----|---------------------|-----|

| I/O Standard                                     | V <sub>OD</sub> (mV)                                                                                    |     |     | ∆V <sub>OD</sub> (mV) |     | V <sub>OCM</sub> (V) |      |       | V <sub>OH</sub> (V)        |     | V <sub>OL</sub> (V) |     |

| I/O Standard                                     | Min                                                                                                     | Тур | Max | Min                   | Max | Min                  | Тур  | Max   | Min                        | Max | Min                 | Max |

| LVDS                                             | 250                                                                                                     | _   | 600 | _                     | 50  | 1.125                | 1.25 | 1.375 | _                          | _   | _                   | _   |

| mini-LVDS (2)                                    | 300                                                                                                     | _   | 600 | _                     | 50  | 1.125                | 1.25 | 1.375 | _                          | _   | _                   | -   |

| RSDS (2)                                         | 100                                                                                                     | _   | 600 | _                     | _   | 1.125                | 1.25 | 1.375 | _                          | _   | _                   | _   |

| Differential 1.5-V<br>HSTL class I<br>and II (3) | _                                                                                                       | _   |     | _                     | _   | _                    | _    | _     | V <sub>CCIO</sub><br>- 0.4 | _   | _                   | 0.4 |

| Table 5–42. Cyclon | e II I/O Outp     | ut Delay for t   | Column Pins               | (Part 3 of      | 6)             |                       |                       |                |      |

|--------------------|-------------------|------------------|---------------------------|-----------------|----------------|-----------------------|-----------------------|----------------|------|

|                    |                   |                  | Fast Co                   | rner            | -6             | -7                    | -7                    | -8             |      |

| I/O Standard       | Drive<br>Strength | Parameter        | Industrial/<br>Automotive | Commer<br>-cial | Speed<br>Grade | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | Speed<br>Grade | Unit |

| SSTL_2_            | 8 mA              | t <sub>OP</sub>  | 1196                      | 1254            | 2388           | 2516                  | 2638                  | 2645           | ps   |

| CLASS_I            |                   | t <sub>DIP</sub> | 1328                      | 1393            | 2558           | 2710                  | 2864                  | 2864           | ps   |

|                    | 12 mA             | t <sub>OP</sub>  | 1174                      | 1231            | 2277           | 2401                  | 2518                  | 2525           | ps   |

|                    | (1)               | t <sub>DIP</sub> | 1306                      | 1370            | 2447           | 2595                  | 2744                  | 2744           | ps   |

| SSTL_2_            | 16 mA             | t <sub>OP</sub>  | 1158                      | 1214            | 2245           | 2365                  | 2479                  | 2486           | ps   |

| CLASS_II           |                   | t <sub>DIP</sub> | 1290                      | 1353            | 2415           | 2559                  | 2705                  | 2705           | ps   |

|                    | 20 mA             | t <sub>OP</sub>  | 1152                      | 1208            | 2231           | 2351                  | 2464                  | 2471           | ps   |

|                    |                   | t <sub>DIP</sub> | 1284                      | 1347            | 2401           | 2545                  | 2690                  | 2690           | ps   |

|                    | 24 mA             | t <sub>OP</sub>  | 1152                      | 1208            | 2225           | 2345                  | 2458                  | 2465           | ps   |

|                    | (1)               | t <sub>DIP</sub> | 1284                      | 1347            | 2395           | 2539                  | 2684                  | 2684           | ps   |

| SSTL_18_           | 6 mA              | t <sub>OP</sub>  | 1472                      | 1544            | 3140           | 3345                  | 3542                  | 3549           | ps   |

| CLASS_I            |                   | t <sub>DIP</sub> | 1604                      | 1683            | 3310           | 3539                  | 3768                  | 3768           | ps   |

|                    | 8 mA              | t <sub>OP</sub>  | 1469                      | 1541            | 3086           | 3287                  | 3482                  | 3489           | ps   |

|                    |                   | t <sub>DIP</sub> | 1601                      | 1680            | 3256           | 3481                  | 3708                  | 3708           | ps   |

|                    | 10 mA             | t <sub>OP</sub>  | 1466                      | 1538            | 2980           | 3171                  | 3354                  | 3361           | ps   |

|                    |                   | t <sub>DIP</sub> | 1598                      | 1677            | 3150           | 3365                  | 3580                  | 3580           | ps   |

|                    | 12 mA             | t <sub>OP</sub>  | 1466                      | 1538            | 2980           | 3171                  | 3354                  | 3361           | ps   |

|                    | (1)               | t <sub>DIP</sub> | 1598                      | 1677            | 3150           | 3365                  | 3580                  | 3580           | ps   |

| SSTL_18_           | 16 mA             | t <sub>OP</sub>  | 1454                      | 1525            | 2905           | 3088                  | 3263                  | 3270           | ps   |

| CLASS_II           |                   | t <sub>DIP</sub> | 1586                      | 1664            | 3075           | 3282                  | 3489                  | 3489           | ps   |

|                    | 18 mA             | t <sub>OP</sub>  | 1453                      | 1524            | 2900           | 3082                  | 3257                  | 3264           | ps   |

|                    | (1)               | t <sub>DIP</sub> | 1585                      | 1663            | 3070           | 3276                  | 3483                  | 3483           | ps   |

| 1.8V_HSTL_         | 8 mA              | t <sub>OP</sub>  | 1460                      | 1531            | 3222           | 3424                  | 3618                  | 3625           | ps   |

| CLASS_I            |                   | t <sub>DIP</sub> | 1592                      | 1670            | 3392           | 3618                  | 3844                  | 3844           | ps   |

|                    | 10 mA             | t <sub>OP</sub>  | 1462                      | 1534            | 3090           | 3279                  | 3462                  | 3469           | ps   |

|                    |                   | t <sub>DIP</sub> | 1594                      | 1673            | 3260           | 3473                  | 3688                  | 3688           | ps   |

|                    | 12 mA             | t <sub>OP</sub>  | 1462                      | 1534            | 3090           | 3279                  | 3462                  | 3469           | ps   |

|                    | (1)               | t <sub>DIP</sub> | 1594                      | 1673            | 3260           | 3473                  | 3688                  | 3688           | ps   |

| Table 5–46. Maximum 0                   | utput Clock     | Toggle               | Rate De                                                   | rating F             | actors (             | Part 3 o             | f 4)                 |                            |                      |                      |  |  |

|-----------------------------------------|-----------------|----------------------|-----------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------------|----------------------|----------------------|--|--|

|                                         |                 | Ma                   | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |                      |                      |                      |                      |                            |                      |                      |  |  |

| I/O Standard                            | Drive           | Colu                 | umn I/O                                                   | Pins                 | Row I/O Pins         |                      |                      | Dedicated Clock<br>Outputs |                      |                      |  |  |

|                                         | Strength        | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade                                      | -8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | -6<br>Speed<br>Grade       | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade |  |  |

| DIFFERENTIAL_SSTL_                      | 16 mA           | 30                   | 33                                                        | 36                   | _                    | _                    | _                    | _                          | _                    | _                    |  |  |

| 18_CLASS_II                             | 18 mA           | 29                   | 29                                                        | 29                   | _                    | _                    | _                    | _                          | _                    | _                    |  |  |

| 1.8V_                                   | 8 mA            | 26                   | 28                                                        | 29                   | 59                   | 61                   | 63                   | 59                         | 61                   | 63                   |  |  |

| DIFFERENTIAL_HSTL_                      | 10 mA           | 46                   | 47                                                        | 48                   | 65                   | 66                   | 68                   | 65                         | 66                   | 68                   |  |  |

| CLASS_I                                 | 12 mA           | 67                   | 67                                                        | 67                   | 71                   | 71                   | 72                   | 71                         | 71                   | 72                   |  |  |

| 1.8V_                                   | 16 mA           | 62                   | 65                                                        | 68                   |                      | _                    | _                    | _                          |                      | _                    |  |  |

| DIFFERENTIAL_HSTL_<br>CLASS_II          | 18 mA           | 59                   | 62                                                        | 65                   | _                    | _                    | _                    | _                          | _                    | _                    |  |  |

| CLASS_II                                | 20 mA           | 57                   | 59                                                        | 62                   | _                    | _                    | _                    | _                          | _                    | _                    |  |  |

| 1.5V_                                   | 8 mA            | 40                   | 40                                                        | 41                   | 28                   | 32                   | 36                   | 28                         | 32                   | 36                   |  |  |

| DIFFERENTIAL_HSTL_<br>CLASS_I           | 10 mA           | 41                   | 42                                                        | 42                   | _                    | _                    | _                    | _                          | _                    | _                    |  |  |

| CLASS_I                                 | 12 mA           | 43                   | 43                                                        | 43                   | _                    | _                    | _                    | _                          | _                    | _                    |  |  |

| 1.5V_<br>DIFFERENTIAL_HSTL_<br>CLASS_II | 16 mA           | 18                   | 20                                                        | 21                   | _                    | _                    | _                    | _                          | _                    | _                    |  |  |

| LVDS                                    | _               | 11                   | 13                                                        | 16                   | 11                   | 13                   | 15                   | 11                         | 13                   | 15                   |  |  |

| RSDS                                    | _               | 11                   | 13                                                        | 16                   | 11                   | 13                   | 15                   | 11                         | 13                   | 15                   |  |  |

| MINI_LVDS                               | _               | 11                   | 13                                                        | 16                   | 11                   | 13                   | 15                   | 11                         | 13                   | 15                   |  |  |

| SIMPLE_RSDS                             | _               | 15                   | 19                                                        | 23                   | 15                   | 19                   | 23                   | 15                         | 19                   | 23                   |  |  |

| 1.2V_HSTL                               | _               | 130                  | 132                                                       | 133                  | _                    | _                    | _                    | _                          | _                    | _                    |  |  |

| 1.2V_<br>DIFFERENTIAL_HSTL              | _               | 130                  | 132                                                       | 133                  | _                    | _                    | _                    | _                          | _                    | _                    |  |  |

| PCI                                     | _               | _                    | _                                                         | _                    | 99                   | 120                  | 142                  | 99                         | 120                  | 142                  |  |  |

| PCI-X                                   |                 | _                    | _                                                         | _                    | 99                   | 121                  | 143                  | 99                         | 121                  | 143                  |  |  |

| LVTTL                                   | OCT_25<br>_OHMS | 13                   | 14                                                        | 14                   | 21                   | 27                   | 33                   | 21                         | 27                   | 33                   |  |  |

| LVCMOS                                  | OCT_25<br>_OHMS | 13                   | 14                                                        | 14                   | 21                   | 27                   | 33                   | 21                         | 27                   | 33                   |  |  |

| 2.5V                                    | OCT_50<br>_OHMS | 346                  | 369                                                       | 392                  | 324                  | 326                  | 327                  | 324                        | 326                  | 327                  |  |  |

| 1.8V                                    | OCT_50<br>_OHMS | 198                  | 203                                                       | 209                  | 202                  | 203                  | 204                  | 202                        | 203                  | 204                  |  |  |

Note to Figure 5–4:

(1) The equation for the high-speed I/O timing budget is: period = TCCS + RSKM + SW + RSKM.

Table 5–48 shows the RSDS timing budget for Cyclone II devices at 311 Mbps. RSDS is supported for transmitting from Cyclone II devices. Cyclone II devices cannot receive RSDS data because the devices are intended for applications where they will be driving display drivers. Cyclone II devices support a maximum RSDS data rate of 311 Mbps using DDIO registers. Cyclone II devices support RSDS only in the commercial temperature range.

| Table 5-48         | Table 5–48. RSDS Transmitter Timing Specification (Part 1 of 2) |      |                |        |     |                |        |     |                |        |      |  |  |

|--------------------|-----------------------------------------------------------------|------|----------------|--------|-----|----------------|--------|-----|----------------|--------|------|--|--|

| O. mb al           | Conditions                                                      | -6 8 | -6 Speed Grade |        |     | -7 Speed Grade |        |     | –8 Speed Grade |        |      |  |  |

| Symbol             |                                                                 | Min  | Тур            | Max(1) | Min | Тур            | Max(1) | Min | Тур            | Max(1) | Unit |  |  |

| f <sub>HSCLK</sub> | ×10                                                             | 10   | _              | 155.5  | 10  | _              | 155.5  | 10  | _              | 155.5  | MHz  |  |  |

| (input<br>clock    | ×8                                                              | 10   | _              | 155.5  | 10  | _              | 155.5  | 10  | _              | 155.5  | MHz  |  |  |

| frequency)         | ×7                                                              | 10   | _              | 155.5  | 10  | _              | 155.5  | 10  | _              | 155.5  | MHz  |  |  |

|                    | ×4                                                              | 10   | _              | 155.5  | 10  | _              | 155.5  | 10  | _              | 155.5  | MHz  |  |  |

|                    | ×2                                                              | 10   | _              | 155.5  | 10  | _              | 155.5  | 10  | _              | 155.5  | MHz  |  |  |

|                    | ×1                                                              | 10   | _              | 311    | 10  | _              | 311    | 10  | _              | 311    | MHz  |  |  |

| Device             | ×10                                                             | 100  | _              | 311    | 100 | _              | 311    | 100 | _              | 311    | Mbps |  |  |

| operation in Mbps  | ×8                                                              | 80   | _              | 311    | 80  | _              | 311    | 80  | _              | 311    | Mbps |  |  |

| iii wbps           | ×7                                                              | 70   | _              | 311    | 70  | _              | 311    | 70  | _              | 311    | Mbps |  |  |

|                    | ×4                                                              | 40   | _              | 311    | 40  | _              | 311    | 40  | _              | 311    | Mbps |  |  |

|                    | ×2                                                              | 20   | _              | 311    | 20  | _              | 311    | 20  | _              | 311    | Mbps |  |  |

|                    | ×1                                                              | 10   | _              | 311    | 10  | _              | 311    | 10  | _              | 311    | Mbps |  |  |

| t <sub>DUTY</sub>  | _                                                               | 45   | _              | 55     | 45  | _              | 55     | 45  | _              | 55     | %    |  |  |

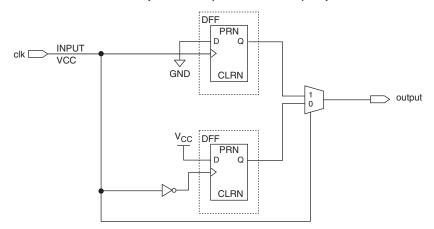

Figure 5-10. DCD Measurement Technique for DDIO (Double-Data Rate) Outputs

When an FPGA PLL generates the internal clock, the PLL output clocks the IOE block. As the PLL only monitors the positive edge of the reference clock input and internally re-creates the output clock signal, any DCD present on the reference clock is filtered out. Therefore, the DCD for a DDIO output with PLL in the clock path is better than the DCD for a DDIO output without PLL in the clock path.

Tables 5–55 through 5–58 give the maximum DCD in absolution derivation for different I/O standards on Cyclone II devices. Examples are also provided that show how to calculate DCD as a percentage.

| Table 5–55. Maximum DCD for Single Data Outputs (SDR) on Row I/O<br>Pins Notes (1), (2) (Part 1 of 2) |     |            |     |      |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|-----|------------|-----|------|--|--|--|--|--|

| Row I/O Output Standard                                                                               | C6  | <b>C</b> 7 | C8  | Unit |  |  |  |  |  |

| LVCMOS                                                                                                | 165 | 230        | 230 | ps   |  |  |  |  |  |

| LVTTL                                                                                                 | 195 | 255        | 255 | ps   |  |  |  |  |  |

| 2.5-V                                                                                                 | 120 | 120        | 135 | ps   |  |  |  |  |  |

| 1.8-V                                                                                                 | 115 | 115        | 175 | ps   |  |  |  |  |  |

| 1.5-V                                                                                                 | 130 | 130        | 135 | ps   |  |  |  |  |  |

| SSTL-2 Class I                                                                                        | 60  | 90         | 90  | ps   |  |  |  |  |  |

| SSTL-2 Class II                                                                                       | 65  | 75         | 75  | ps   |  |  |  |  |  |

| SSTL-18 Class I                                                                                       | 90  | 165        | 165 | ps   |  |  |  |  |  |

| HSTL-15 Class I                                                                                       | 145 | 145        | 205 | ps   |  |  |  |  |  |

| HSTL-18 Class I                                                                                       | 85  | 155        | 155 | ps   |  |  |  |  |  |

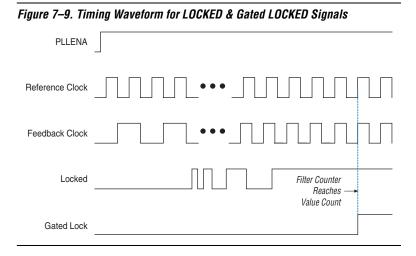

#### locked

When the locked port output is a logic high level, this indicates a stable PLL clock output in phase with the PLL reference input clock. The locked port may toggle as the PLL begins tracking the reference clock. The locked port of the PLL can feed any general-purpose I/O pin or LEs. The locked signal is optional, but is useful in monitoring the PLL lock process.

The locked output indicates that the PLL has locked onto the reference clock. You may need to gate the locked signal for use as a system-control signal. Either a gated locked signal or an ungated locked signal from the locked port can drive the logic array or an output pin. Cyclone II PLLs include a programmable counter that holds the locked signal low for a user-selected number of input clock transitions. This allows the PLL to lock before transitioning the locked signal high. You can use the Quartus II software to set the 20-bit counter value. The device resets and enables both the counter and the PLL simultaneously upon power-up and/or the assertion of the pllenable signal. To ensure correct lock circuit operation, and to ensure that the output clocks have the correct phase relationship with respect to the input clock, Altera recommends that the input clock be running before the Cyclone II device is configured.

Figure 7–9 shows the timing waveform for LOCKED and gated LOCKED signals.

#### Manual Clock Switchover

The Cyclone II PLLs support manual switchover of the reference clock through internal logic. This enables you to switch between two reference input clocks. Use this feature for a dual clock domain application such as in a system that turns on the redundant clock if the primary clock stops running.

Figure 7–10 shows how the PLL input clock ( $f_{\rm IN}$ ) is generated from one of four possible clock sources. The first stage multiplexing consists of two dedicated multiplexers that generate two single-ended or two differential clocks from four dedicated clock pins. These clock signals are then multiplexed to generate  $f_{\rm IN}$  by using another dedicated 2-to-1 multiplexer. The first stage multiplexers are controlled by configuration bit settings in the configuration file generated by the Quartus II software, while the second stage multiplexer is either controlled by the configuration bit settings or logic array signal to allow the  $f_{\rm IN}$  to be controlled dynamically. This allows the implementation of a manual clock switchover circuit where the PLL reference clock can be switched during user mode for applications that requires clock redundancy.

$\begin{array}{c} \text{CLK}[n+3] \\ \text{CLK}[n+2] \\ \text{CLK}[n+1] \\ \text{CLK}[n] \end{array}$

Figure 7-10. Cyclone II PLL Input Clock Generation

Notes to Figure 7-10:

- (1) This select line is set through the configuration file.

- (2) This select line can either be set through the configuration file or it can be dynamically set in user mode when using the manual switchover feature.

| Table 7–8. Global Clock Network Connections (Part 3 of 3) |   |                        |   |   |   |   |   |                                    |   |   |    |    |    |    |    |          |

|-----------------------------------------------------------|---|------------------------|---|---|---|---|---|------------------------------------|---|---|----|----|----|----|----|----------|

| Global Clock                                              |   | Global Clock Networks  |   |   |   |   |   |                                    |   |   |    |    |    |    |    |          |

| Network Clock                                             |   | All Cyclone II Devices |   |   |   |   |   | EP2C15 through EP2C70 Devices Only |   |   |    |    |    |    |    |          |

| Sources                                                   | 0 | 1                      | 2 | 3 | 4 | 5 | 6 | 7                                  | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15       |

| DPCLK3 (1)                                                |   |                        |   |   |   |   |   |                                    |   |   |    |    |    |    |    | <b>✓</b> |

Notes to Table 7-8:

- See the Cyclone II Architecture chapter in Volume 1 of the Cyclone II Device Handbook for more information on DPCLK pins.

- (2) This pin only applies to EP2C5 and EP2C8 devices.

- (3) These pins only apply to EP2C15 devices and larger. Only one of the two CDPCLK pins can feed the clock control block. The other pin can be used as a regular I/O pin.

If the dedicated clock pins are not used to feed the global clock networks, they can be used as general-purpose input pins to feed the logic array using the MultiTrack interconnect. However, if they are used as general-purpose input pins, they do not have support for an I/O register and must use LE-based registers in place of an I/O register.

#### **Clock Control Block**

Every global clock network is driven by a clock control block residing either on the top, bottom, left, or right side of the Cyclone II device. The global clock network has been optimized for minimum clock skew and delay.

Table 7–9 lists the sources that can feed the clock control block, which in turn feeds the global clock networks.

| Table 7–9. Clock Control Block Inputs (Part 1 of 2) |                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Input                                               | Description                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Dedicated clock inputs                              | Dedicated clock input pins can drive clocks or global signals, such as asynchronous clears, presets, or clock enables onto a given global clock network.                                                                |  |  |  |  |  |  |  |

| Dual-purpose clock (DPCLK and CDPCLK) I/O inputs    | DPCLK and CDPCLK I/O pins are bidirectional dual function pins that can be used for high fanout control signals, such as protocol signals, TRDY and IRDY signals for PCI, or DQS for DDR, via the global clock network. |  |  |  |  |  |  |  |

## External Memory Interface Standards

The following sections describe how to use Cyclone II device external memory interfacing features.

#### DDR & DDR2 SDRAM

DDR SDRAM is a memory architecture that transmits and receives data at twice the clock speed. These devices transfer data on both the rising and falling edge of the clock signal. DDR2 SDRAM is the second generation memory based on the DDR SDRAM architecture and is capable of data transfer rates of up to 533 Mbps. Cyclone II devices support DDR and DDR2 SDRAM at up to 333 Mbps.

#### Interface Pins

DDR and DDR2 SDRAM devices use interface pins such as data (DQ), data strobe (DQS), clock, command, and address pins to communicate with the memory controller. Data is sent and captured at twice the system clock rate by transferring data on the positive and negative edge of the clock. The commands and addresses use only one active (positive) edge of a clock.

DDR SDRAM uses single-ended data strobe DQS, while DDR2 SDRAM has the option to use differential data strobes DQS and DQS#. Cyclone II devices do not use the optional differential data strobes for DDR2 SDRAM interfaces. You can leave the DDR2 SDRAM memory DQS# pin unconnected, because only the shifted DQS signal from the clock delay control circuitry captures data. DDR and DDR2 SDRAM ×16 devices use two DQS pins, and each DQS pin is associated with eight DQ pins. However, this is not the same as the ×16/×18 mode in Cyclone II devices. You need to configure the Cyclone II devices to use two sets of pins in ×8 mode. Similarly, if your ×72 memory module uses nine DQS pins where each DQS pin is associated with eight DQ pins, configure the Cyclone II device to use nine sets of DQS/DQ groups in ×8 mode.

Connect the memory device's DQ and DQS pins to the Cyclone II DQ and DQS pins, respectively, as listed in the Cyclone II pin tables. DDR and DDR2 SDRAM also use active-high data mask (DM) pins for writes. DM pins are pre-assigned in pin outs for Cyclone II devices, and these are the preferred pins. However, you may connect the memory device's DM pins to any of the Cyclone II I/O pins in the same bank as the DQ pins of the FPGA. There is one DM pin per DQS/DQ group. If the DDR or DDR2 SDRAM device supports ECC, the design uses an extra DQS/DQ group for the ECC pins.

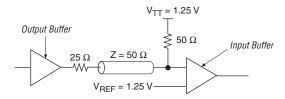

Figure 10-1. SSTL-2 Class I Termination

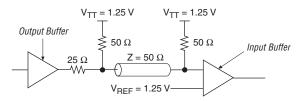

Figure 10-2. SSTL-2 Class II Termination

Cyclone II devices support both input and output SSTL-2 class I and II levels.

#### Pseudo-Differential SSTL-2

The differential SSTL-2 I/O standard (EIA/JEDEC standard JESD8-9A) is a 2.5-V standard used for applications such as high-speed DDR SDRAM clock interfaces. This standard supports differential signals in systems using the SSTL-2 standard and supplements the SSTL-2 standard for differential clocks. The differential SSTL-2 standard specifies an input voltage range of – 0.3 V  $\leq$ V $_{\rm I}$   $\leq$ V $_{\rm CCIO}$  + 0.3 V. The differential SSTL-2 standard does not require an input reference voltage. Refer to Figures 10–3 and 10–4 for details on differential SSTL-2 terminations.

Cyclone II devices do not support true differential SSTL-2 standards. Cyclone II devices support pseudo-differential SSTL-2 outputs for PLL\_OUT pins and pseudo-differential SSTL-2 inputs for clock pins. Pseudo-differential inputs require an input reference voltage as opposed to the true differential inputs. Refer to Table 10–1 on page 10–2 for information about pseudo-differential SSTL.

### Configuration File Format

Table 13–3 shows the approximate uncompressed configuration file sizes for Cyclone II devices. To calculate the amount of storage space required for multiple device configurations, add the file size of each device together.

| Table 13–3. Cyclone II F | Table 13–3. Cyclone II Raw Binary File (.rbf) Sizes Note (1) |                   |  |  |  |  |  |  |  |  |

|--------------------------|--------------------------------------------------------------|-------------------|--|--|--|--|--|--|--|--|

| Device                   | Data Size (Bits)                                             | Data Size (Bytes) |  |  |  |  |  |  |  |  |

| EP2C5                    | 1,265,792                                                    | 152,998           |  |  |  |  |  |  |  |  |

| EP2C8                    | 1,983,536                                                    | 247,974           |  |  |  |  |  |  |  |  |

| EP2C15                   | 3,892,496                                                    | 486,562           |  |  |  |  |  |  |  |  |

| EP2C20                   | 3,892,496                                                    | 486,562           |  |  |  |  |  |  |  |  |

| EP2C35                   | 6,858,656                                                    | 857,332           |  |  |  |  |  |  |  |  |

| EP2C50                   | 9,963,392                                                    | 1,245,424         |  |  |  |  |  |  |  |  |

| EP2C70                   | 14,319,216                                                   | 1,789,902         |  |  |  |  |  |  |  |  |

*Note to Table 13–3:*

These values are preliminary.

Use the data in Table 13–3 only to estimate the file size before design compilation. Different configuration file formats, such as a Hexadecimal (.hex) or Tabular Text File (.ttf) format, have different file sizes. However, for any specific version of the Quartus® II software, any design targeted for the same device has the same uncompressed configuration file size. If compression is used, the file size can vary after each compilation since the compression ratio is dependent on the design.

# Configuration Data Compression

Cyclone II devices support configuration data decompression, which saves configuration memory space and time. This feature allows you to store compressed configuration data in configuration devices or other memory and transmit this compressed bitstream to Cyclone II devices. During configuration, the Cyclone II device decompresses the bitstream in real time and programs its SRAM cells.

Preliminary data indicates that compression reduces configuration bitstream size by 35 to 55%.

Cyclone II devices support decompression in the AS and PS configuration schemes. Decompression is not supported in JTAG-based configuration.

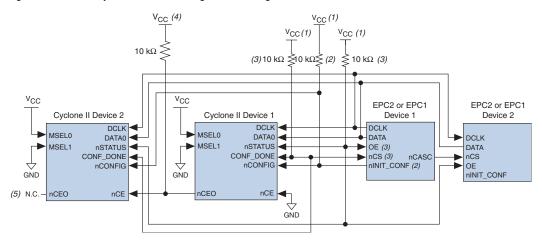

Figure 13-17. Multiple Device PS Configuration Using Cascaded EPC2 or EPC1 Devices

#### *Notes to Figure 13–17:*

- (1) The pull-up resistor should be connected to the same supply voltage as the configuration device.

- (2) The ninit\_conf pin (available on enhanced configuration devices and EPC2 devices only) has an internal pull-up resistor that is always active, meaning an external pull-up resistor should not be used on the ninit\_conf to nconfig line. The ninit\_conf pin does not need to be connected if its functionality is not used. If ninit\_conf is not used or not available (e.g., on EPC1 devices), nconfig must be pulled to V<sub>CC</sub> either directly or through a resistor (if reconfiguration is required, a resistor is necessary).

- (3) The enhanced configuration devices' and EPC2 devices' OE and nCS pins have internal programmable pull-up resistors. If internal pull-up resistors are used, external pull-up resistors should not be used on these pins. The internal pull-up resistors are used by default in the Quartus II software. To turn off the internal pull-up resistors, check the Disable nCS and OE pull-ups on configuration device option when generating programming files.

- (4) Use an external 10-kΩ pull-up resistor to pull the nCEO pin high to the I/O bank V<sub>CCIO</sub> level to help the internal weak pull-up when it feeds next device's nCE pin.

- (5) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

When using enhanced configuration devices or EPC2 devices, you can connect the Cyclone II device's <code>nCONFIG</code> pin to the configuration device's <code>nINIT\_CONF</code> pin, which allows the <code>INIT\_CONF</code> JTAG instruction to initiate FPGA configuration. You do not need to connect the <code>nINIT\_CONF</code> pin if it is not used. If the <code>nINIT\_CONF</code> pin is not used or not available (for example, on EPC1 devices), pull the <code>nCONFIG</code> pin to  $V_{CC}$  levels either directly or through a resistor (if reconfiguration is required, a resistor is necessary). An internal pull-up resistor on the <code>nINIT\_CONF</code> pin is always active in the enhanced configuration devices and the EPC2 devices. Therefore, do not use an external pull-up resistor if you connect the <code>nCONFIG</code> pin to <code>nINIT\_CONF</code>. If you use multiple EPC2 devices to configure a Cyclone II device(s), only connect the first EPC2 device's <code>nINIT\_CONF</code> pin to the device's <code>nCONFIG</code> pin.

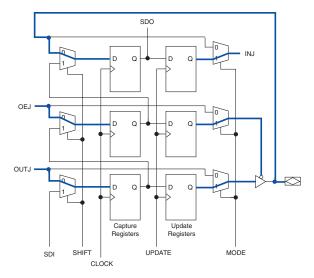

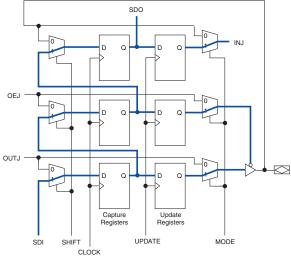

Figure 14–10 shows the capture, shift, and update phases of the EXTEST mode.

Figure 14-10. IEEE Std. 1149.1 BST EXTEST Mode

#### **Capture Phase**

In the capture phase, the signals at the pin, OEJ and OUTJ, are loaded into the capture registers. The CLOCK signals are supplied by the TAP controller's CLOCKDR output. Previously retained data in the update registers drive the PIN\_IN, INJ, and allows the I/O pin to tri-state or drive a signal out.

A "1" in the OEJ update register tri-states the output buffer.

#### **Shift & Update Phases**

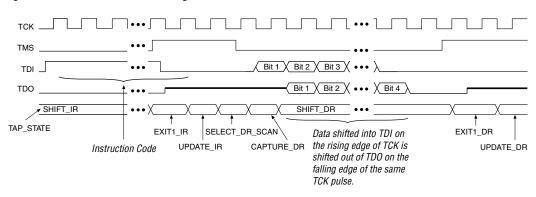

In the shift phase, the previously captured signals at the pin, OEJ and OUTJ, are shifted out of the boundary-scan register via the TDO pin using CLOCK. As data is shifted out, the patterns for the next test can be shifted in via the TDI pin.

In the update phase, data is transferred from the capture registers to the update registers using the UPDATE clock. The update registers then drive the PIN\_IN, INJ, and allow the I/O pin to tristate or drive a signal out.

Figure 14-12. BYPASS Shift Data Register Waveforms

#### **IDCODE Instruction Mode**

The IDCODE instruction mode is used to identify the devices in an IEEE Std. 1149.1 chain. When IDCODE is selected, the device identification register is loaded with the 32-bit vendor-defined identification code. The device ID register is connected between the TDI and TDO ports, and the device IDCODE is shifted out. The IDCODE for Cyclone II devices are listed in the Configuration & Testing chapter in Volume 1 of the Cyclone II Device Handbook.

#### **USERCODE Instruction Mode**

The USERCODE instruction mode is used to examine the user electronic signature (UES) within the devices along an IEEE Std. 1149.1 chain. When this instruction is selected, the device identification register is connected between the TDI and TDO ports. The user-defined UES is shifted into the device ID register in parallel from the 32-bit USERCODE register. The UES is then shifted out through the device ID register. The UES value is not user defined until after the device has been configured. Before configuration, the UES value is set to the default value.

#### **CLAMP Instruction Mode**

The CLAMP instruction mode is used to allow the boundary-scan register to determine the state of the signals driven from the pins. In CLAMP instruction mode, the bypass register is selected as the serial path between the TDI and TDO ports.

# Thermal Resistance

Thermal resistance values for Cyclone II devices are provided for a board meeting JEDEC specifications and for a typical board. The values provided are as follows:

- θ<sub>JA</sub> (°C/W) Still Air—Junction-to-ambient thermal resistance with no airflow when a heat sink is not being used.

- $\theta_{JA}$  (° C/W) 100 ft./minute—Junction-to-ambient thermal resistance with 100 ft./minute airflow when a heat sink is not being used.

- $\theta_{JA}$  (° C/W) 200 ft./minute—Junction-to-ambient thermal resistance with 200 ft./minute airflow when a heat sink is not being used.

- $\theta_{JA}$  (° C/W) 400 ft./minute—Junction-to-ambient thermal resistance with 400 ft./minute airflow when a heat sink is not being used.

- $\theta_{IC}$  (°C/W)—Junction-to-case thermal resistance for device.

- $\theta_{JB}$  (° C/W)—Junction-to-board thermal resistance for specific board being used.

Table 15–2 provides  $\theta_{JA}$  (junction-to-ambient thermal resistance) values and  $\theta_{JC}$  (junction-to-case thermal resistance) values for Cyclone II devices on a board meeting JEDEC specifications for thermal resistance calculation. The JEDEC board specifications require two signal and two power/ground planes and are available at **www.jedec.org**.

| Table 15- | -2. Theri    | mal Resistance of Cyc | lone II Devices i                    | or Board Meet                           | ting JEDEC Sp | ecifications (                          | (Part 1 of 2)              |

|-----------|--------------|-----------------------|--------------------------------------|-----------------------------------------|---------------|-----------------------------------------|----------------------------|

| Device    | Pin<br>Count | Package               | θ <sub>JA</sub> (° C/W)<br>Still Air | θ <sub>JA</sub> (° C/W)<br>100 ft./min. | • ,           | θ <sub>JA</sub> (° C/W)<br>400 ft./min. | θ <sub>JC</sub><br>(° C/W) |

| EP2C5     | 144          | TQFP                  | 31                                   | 29.3                                    | 27.9          | 25.5                                    | 10                         |

|           | 208          | PQFP                  | 30.4                                 | 29.2                                    | 27.3          | 22.3                                    | 5.5                        |

|           | 256          | FineLine BGA          | 30.2                                 | 26.1                                    | 23.6          | 21.7                                    | 8.7                        |

| EP2C8     | 144          | TQFP                  | 29.8                                 | 28.3                                    | 26.9          | 24.9                                    | 9.9                        |

|           | 208          | PQFP                  | 30.2                                 | 28.8                                    | 26.9          | 21.7                                    | 5.4                        |

|           | 256          | FineLine BGA          | 27                                   | 23                                      | 20.5          | 18.5                                    | 7.1                        |

| EP2C15    | 256          | FineLine BGA          | 24.2                                 | 20                                      | 17.8          | 16                                      | 5.5                        |

|           | 484          | FineLine BGA          | 21                                   | 17                                      | 14.8          | 13.1                                    | 4.2                        |

| EP2C20    | 240          | PQFP                  | 26.6                                 | 24                                      | 21.4          | 17.4                                    | 4.2                        |

|           | 256          | FineLine BGA          | 24.2                                 | 20                                      | 17.8          | 16                                      | 5.5                        |

|           | 484          | FineLine BGA          | 21                                   | 17                                      | 14.8          | 13.1                                    | 4.2                        |

| EP2C35    | 484          | FineLine BGA          | 19.4                                 | 15.4                                    | 13.3          | 11.7                                    | 3.3                        |

|           | 484          | Ultra FineLine BGA    | 20.6                                 | 16.6                                    | 14.5          | 12.8                                    | 5                          |

|           | 672          | FineLine BGA          | 18.6                                 | 14.6                                    | 12.6          | 11.1                                    | 3.1                        |

Tables 15–5 and 15–6 show the package information and package outline figure references, respectively, for the 144-pin TQFP package.

| Table 15–5. 144-Pin TQFP Package Information |                                                |  |

|----------------------------------------------|------------------------------------------------|--|

| Description                                  | Specification                                  |  |

| Ordering code reference                      | Т                                              |  |

| Package acronym                              | TQFP                                           |  |

| Lead frame material                          | Copper                                         |  |

| Lead finish (plating)                        | Regular: 85Sn:15Pb (Typ.)<br>Pb-free: Matte Sn |  |

| JEDEC Outline Reference                      | MS-026 Variation: BFB                          |  |

| Maximum lead coplanarity                     | 0.003 inches (0.08mm)                          |  |

| Weight                                       | 1.3 g                                          |  |

| Moisture sensitivity level                   | Printed on moisture barrier bag                |  |

| Table 15–6. 144-Pin TQFP Package Outline Dimensions |            |      |            |

|-----------------------------------------------------|------------|------|------------|

| Symbol -                                            | Millimeter |      |            |

|                                                     | Min.       | Nom. | Max.       |

| Α                                                   | _          | _    | 1.60       |

| A1                                                  | 0.05       | -    | 0.15       |

| A2                                                  | 1.35       | 1.40 | 1.45       |

| D                                                   | 22.00 BSC  |      |            |

| D1                                                  | 20.00 BSC  |      |            |

| E                                                   | 22.00 BSC  |      |            |

| E1                                                  | 20.00 BSC  |      |            |

| L                                                   | 0.45       | 0.60 | 0.75       |

| L1                                                  | 1.00 REF   |      |            |

| S                                                   | 0.20       | _    | _          |

| b                                                   | 0.17       | 0.22 | 0.27       |

| С                                                   | 0.09       | _    | 0.20       |

| е                                                   | 0.50 BSC   |      |            |

| θ                                                   | 0°         | 3.5° | <b>7</b> ° |