### Intel - EP2C20F256I8N Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 1172                                                     |

| Number of Logic Elements/Cells | 18752                                                    |

| Total RAM Bits                 | 239616                                                   |

| Number of I/O                  | 152                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 256-LBGA                                                 |

| Supplier Device Package        | 256-FBGA (17x17)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c20f256i8n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| clkena signals | 29 |

|----------------|----|

| Board Layout   | 30 |

| VCCA & GNDA    |    |

| VCCD & GND     |    |

| Conclusion     |    |

# Section III. Memory

| <b>Revision History</b> |  | 7- | 1 |

|-------------------------|--|----|---|

|-------------------------|--|----|---|

## **Chapter 8. Cyclone II Memory Blocks**

| Introduction                                     | -1 |

|--------------------------------------------------|----|

| Overview                                         | -1 |

| Control Signals                                  | -3 |

| Parity Bit Support                               | -4 |

| Byte Enable Support                              | -4 |

| Packed Mode Support 8-                           | -6 |

| Address Clock Enable                             | -6 |

| Memory Modes                                     | -8 |

| Single-Port Mode                                 | -9 |

| Simple Dual-Port Mode                            | 10 |

| True Dual-Port Mode                              | 12 |

| Shift Register Mode                              | 14 |

| ROM Mode                                         | 16 |

| FIFO Buffer Mode 8-1                             | 16 |

| Clock Modes                                      | 16 |

| Independent Clock Mode                           | 17 |

| Input/Output Clock Mode                          | 19 |

| Read/Write Clock Mode                            | 22 |

| Single-Clock Mode                                | 24 |

| Power-Up Conditions & Memory Initialization 8-2  | 27 |

| Read-During- Write Operation at the Same Address | 28 |

| Same-Port Read-During-Write Mode 8-2             | 28 |

| Mixed-Port Read-During-Write Mode 8-2            | 29 |

| Conclusion                                       | 30 |

| Referenced Documents                             | 30 |

## **Chapter 9. External Memory Interfaces**

| Introduction                           | 9–1  |

|----------------------------------------|------|

| External Memory Interface Standards    | 9–2  |

| DDR & DDR2 SDRAM                       | 9–2  |

| QDRII SRAM                             |      |

| Cyclone II DDR Memory Support Overview | 9–9  |

| Data & Data Strobe Pins                |      |

| Clock, Command & Address Pins          | 9–14 |

| Parity, DM & ECC Pins                  | 9–14 |

|                                        |      |

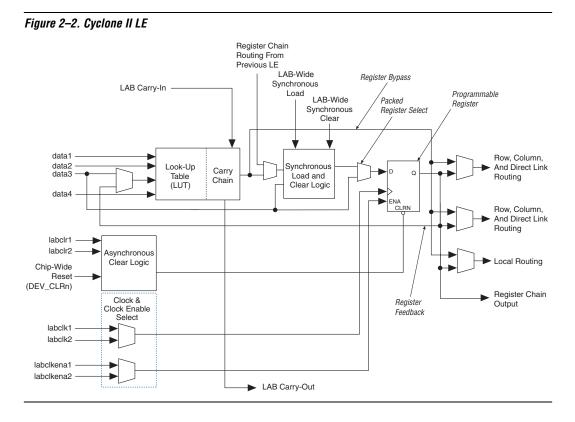

Figure 2–2 shows a Cyclone II LE.

Each LE's programmable register can be configured for D, T, JK, or SR operation. Each register has data, clock, clock enable, and clear inputs. Signals that use the global clock network, general-purpose I/O pins, or any internal logic can drive the register's clock and clear control signals. Either general-purpose I/O pins or internal logic can drive the clock enable. For combinational functions, the LUT output bypasses the register and drives directly to the LE outputs.

Each LE has three outputs that drive the local, row, and column routing resources. The LUT or register output can drive these three outputs independently. Two LE outputs drive column or row and direct link routing connections and one drives local interconnect resources, allowing the LUT to drive one output while the register drives another output. This feature, register packing, improves device utilization because the device can use the register and the LUT for unrelated functions. When using register packing, the LAB-wide synchronous load control signal is not available. See "LAB Control Signals" on page 2–8 for more information.

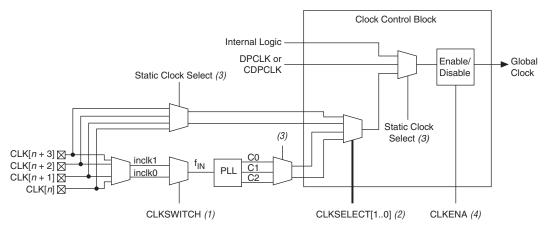

Of the sources listed, only two clock pins, two PLL clock outputs, one DPCLK pin, and one internally-generated signal are chosen to drive into a clock control block. Figure 2–13 shows a more detailed diagram of the clock control block. Out of these six inputs, the two clock input pins and two PLL outputs can be dynamic selected to feed a global clock network. The clock control block supports static selection of DPCLK and the signal from internal logic.

Figure 2–13. Clock Control Block

#### Notes to Figure 2–13:

- The CLKSWITCH signal can either be set through the configuration file or it can be dynamically set when using the manual PLL switchover feature. The output of the multiplexer is the input reference clock (f<sub>IN</sub>) for the PLL.

- (2) The CLKSELECT[1..0] signals are fed by internal logic and can be used to dynamically select the clock source for the global clock network when the device is in user mode.

- (3) The static clock select signals are set in the configuration file and cannot be dynamically controlled when the device is in user mode.

- (4) Internal logic can be used to enabled or disabled the global clock network in user mode.

# 3. Configuration & Testing

CII51003-2.2

## IEEE Std. 1149.1 (JTAG) Boundary Scan Support

All Cyclone<sup>®</sup> II devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1. JTAG boundary-scan testing can be performed either before or after, but not during configuration. Cyclone II devices can also use the JTAG port for configuration with the Quartus<sup>®</sup> II software or hardware using either Jam Files (.**jam**) or Jam Byte-Code Files (.**jbc**).

Cyclone II devices support IOE I/O standard reconfiguration through the JTAG BST chain. The JTAG chain can update the I/O standard for all input and output pins any time before or during user mode through the CONFIG\_IO instruction. You can use this capability for JTAG testing before configuration when some of the Cyclone II pins drive or receive from other devices on the board using voltage-referenced standards. Since the Cyclone II device might not be configured before JTAG testing, the I/O pins may not be configured for appropriate electrical standards for chip-to-chip communication. Programming the I/O standards via JTAG allows you to fully test I/O connections to other devices.

For information on I/O reconfiguration, refer to the *MorphIO: An I/O Reconfiguration Solution for Altera Devices White Paper.*

A device operating in JTAG mode uses four required pins: TDI, TDO, TMS, and TCK. The TCK pin has an internal weak pull-down resister, while the TDI and TMS pins have weak internal pull-up resistors. The TDO output pin and all JTAG input pin voltage is determined by the  $V_{\rm CCIO}$  of the bank where it resides. The bank  $V_{\rm CCIO}$  selects whether the JTAG inputs are 1.5-, 1.8-, 2.5-, or 3.3-V compatible.

Stratix<sup>®</sup> II, Stratix, Cyclone II and Cyclone devices must be within the first 8 devices in a JTAG chain. All of these devices have the same JTAG controller. If any of the Stratix II, Stratix, Cyclone II or Cyclone devices are in the 9th of further position, they fail configuration. This does not affect Signal Tap II. Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| Device   | Speed Grade           | Preliminary  | Final        |

|----------|-----------------------|--------------|--------------|

| EP2C5/A  | Commercial/Industrial | —            | $\checkmark$ |

|          | Automotive            | $\checkmark$ | —            |

| EP2C8/A  | Commercial/Industrial | —            | $\checkmark$ |

|          | Automotive            | $\checkmark$ | _            |

| EP2C15A  | Commercial/Industrial | —            | $\checkmark$ |

|          | Automotive            | $\checkmark$ | _            |

| EP2C20/A | Commercial/Industrial | —            | $\checkmark$ |

|          | Automotive            | $\checkmark$ | _            |

| EP2C35   | Commercial/Industrial | —            | $\checkmark$ |

| EP2C50   | Commercial/Industrial | —            | $\checkmark$ |

| EP2C70   | Commercial/Industrial | —            | $\checkmark$ |

### Performance

Table 5–15 shows Cyclone II performance for some common designs. All performance values were obtained with Quartus II software compilation of LPM, or MegaCore functions for the FIR and FFT designs.

| Table 5–15. Cyclone II Performance (Part 1 of 4) |                         |     |                         |               |                      |                             |                             |                      |  |  |  |  |

|--------------------------------------------------|-------------------------|-----|-------------------------|---------------|----------------------|-----------------------------|-----------------------------|----------------------|--|--|--|--|

|                                                  |                         | R   | esources U              | lsed          | Performance (MHz)    |                             |                             |                      |  |  |  |  |

| Applications                                     |                         | LEs | M4K<br>Memory<br>Blocks | DSP<br>Blocks | –6<br>Speed<br>Grade | -7<br>Speed<br>Grade<br>(6) | -7<br>Speed<br>Grade<br>(7) | –8<br>Speed<br>Grade |  |  |  |  |

| LE                                               | 16-to-1 multiplexer (1) | 21  | 0                       | 0             | 385.35               | 313.97                      | 270.85                      | 286.04               |  |  |  |  |

|                                                  | 32-to-1 multiplexer (1) | 38  | 0                       | 0             | 294.2                | 260.75                      | 228.78                      | 191.02               |  |  |  |  |

|                                                  | 16-bit counter          | 16  | 0                       | 0             | 401.6                | 349.4                       | 310.65                      | 310.65               |  |  |  |  |

|                                                  | 64-bit counter          | 64  | 0                       | 0             | 157.15               | 137.98                      | 126.08                      | 126.27               |  |  |  |  |

| Table 5–17. IOE Internal Timing Microparameters (Part 2 of 2) |          |           |          |           |          |      |      |  |  |  |

|---------------------------------------------------------------|----------|-----------|----------|-----------|----------|------|------|--|--|--|

| Parameter                                                     | –6 Speed | Grade (1) | –7 Speed | Grade (2) | –8 Speed |      |      |  |  |  |

|                                                               | Min      | Мах       | Min      | Мах       | Min      | Мах  | Unit |  |  |  |

| TCOMBIN2PIN_C                                                 | 1418     | 2622      | 1352     | 2831      | 1352     | 3041 | ps   |  |  |  |

|                                                               | _        | —         | 1418     | —         | 1418     | —    | ps   |  |  |  |

| TCLR                                                          | 137      | —         | 165      | —         | 165      | —    | ps   |  |  |  |

|                                                               | —        | —         | 151      | —         | 165      | —    | ps   |  |  |  |

| TPRE                                                          | 192      | —         | 233      | —         | 233      | —    | ps   |  |  |  |

|                                                               | —        | —         | 212      | —         | 233      | —    | ps   |  |  |  |

| TCLKL                                                         | 1000     | —         | 1242     | —         | 1242     | —    | ps   |  |  |  |

|                                                               | —        | —         | 1111     | —         | 1242     | —    | ps   |  |  |  |

| TCLKH                                                         | 1000     | —         | 1242     | —         | 1242     | —    | ps   |  |  |  |

|                                                               | —        | —         | 1111     | —         | 1242     | —    | ps   |  |  |  |

#### Notes to Table 5–17:

(1) For the -6 speed grades, the minimum timing is for the commercial temperature grade. The -7 speed grade devices offer the automotive temperature grade. The -8 speed grade devices offer the industrial temperature grade.

(2) For each parameter of the -7 speed grade columns, the value in the first row represents the minimum timing parameter for automotive devices. The second row represents the minimum timing parameter for commercial devices.

(3) For each parameter of the -8 speed grade columns, the value in the first row represents the minimum timing parameter for industrial devices. The second row represents the minimum timing parameter for commercial devices.

| Table 5–18. DSP Block Internal Timing Microparameters (Part 1 of 2) |          |           |          |             |          |      |      |  |  |  |  |

|---------------------------------------------------------------------|----------|-----------|----------|-------------|----------|------|------|--|--|--|--|

| Parameter                                                           | –6 Speed | Grade (1) | –7 Speed | l Grade (2) | –8 Speed | 11   |      |  |  |  |  |

|                                                                     | Min      | Max       | Min      | Max         | Min      | Max  | Unit |  |  |  |  |

| TSU                                                                 | 47       | —         | 62       | —           | 62       | —    | ps   |  |  |  |  |

|                                                                     | —        | —         | 54       | —           | 62       | —    | ps   |  |  |  |  |

| тн                                                                  | 110      | _         | 113      | —           | 113      | —    | ps   |  |  |  |  |

|                                                                     | —        | —         | 111      | —           | 113      | —    | ps   |  |  |  |  |

| тсо                                                                 | 0        | 0         | 0        | 0           | 0        | 0    | ps   |  |  |  |  |

|                                                                     | —        | —         | 0        | —           | 0        | _    | ps   |  |  |  |  |

| TINREG2PIPE9                                                        | 652      | 1379      | 621      | 1872        | 621      | 2441 | ps   |  |  |  |  |

|                                                                     | —        | —         | 652      | —           | 652      | —    | ps   |  |  |  |  |

| TINREG2PIPE18                                                       | 652      | 1379      | 621      | 1872        | 621      | 2441 | ps   |  |  |  |  |

|                                                                     | —        | _         | 652      | —           | 652      | —    | ps   |  |  |  |  |

| Table 5–47. High-Speed I/O Timing Definitions (Part 2 of 2) |                   |                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|-------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Parameter                                                   | Symbol            | Description                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

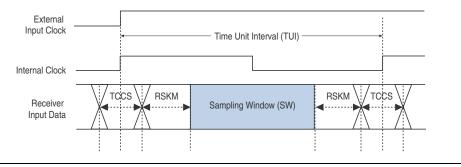

| Sampling window                                             | SW                | The period of time during which the data must be valid in order for you to capture it correctly. Sampling window is the sum of the setup time, hold time, and jitter. The window of $t_{SU} + t_H$ is expected to be centered in the sampling window.<br>SW = TUI – TCCS – (2 × RSKM) |  |  |  |  |  |  |  |

| Receiver input skew margin                                  | RSKM              | RSKM is defined by the total margin left after accounting for the sampling window and TCCS.<br>RSKM = (TUI – SW – TCCS) / 2                                                                                                                                                           |  |  |  |  |  |  |  |

| Input jitter (peak to peak)                                 | —                 | Peak-to-peak input jitter on high-speed PLLs.                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Output jitter (peak to peak)                                | —                 | Peak-to-peak output jitter on high-speed PLLs.                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Signal rise time                                            | t <sub>RISE</sub> | Low-to-high transmission time.                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Signal fall time                                            | t <sub>FALL</sub> | High-to-low transmission time.                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Lock time                                                   | t <sub>LOCK</sub> | Lock time for high-speed transmitter and receiver PLLs.                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

Figure 5–3. High-Speed I/O Timing Diagram

Figure 5–4 shows the high-speed I/O timing budget.

Table 7–2 provides an overview of the Cyclone II PLL features.

| Table 7–2. Cyclone II PLL Features     |                                                |

|----------------------------------------|------------------------------------------------|

| Feature                                | Description                                    |

| Clock multiplication and division      | $m / (n \times \text{post-scale counter})$ (1) |

| Phase shift                            | Down to 125-ps increments (2), (3)             |

| Programmable duty cycle                | $\checkmark$                                   |

| Number of internal clock outputs       | Up to three per PLL (4)                        |

| Number of external clock outputs       | One per PLL (4)                                |

| Locked port can feed logic array       | $\checkmark$                                   |

| PLL clock outputs can feed logic array | $\checkmark$                                   |

| Manual clock switchover                | $\checkmark$                                   |

| Gated lock                             | $\checkmark$                                   |

#### Notes to Table 7–2:

- (1) *m* and post-scale counter values range from 1 to 32. *n* ranges from 1 to 4.

- (2) The smallest phase shift is determined by the voltage control oscillator (VCO) period divided by 8.

- (3) For degree increments, Cyclone II devices can shift output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the VCO frequency.

- (4) The Cyclone II PLL has three output counters that drive the global clock network. One of these output counters (c2) can also drive a dedicated external I/O pin (single ended or differential). This counter output can also drive the external clock output (PLL<#>\_OUT) and internal global clock network at the same time.

## Cyclone II PLL Hardware Overview

Cyclone II devices contain up to four PLLs that are arranged in the four corners of the Cyclone II device as shown in Figure 7–1, which shows a top-level diagram of the Cyclone II device and the PLL locations.

Table 7–8 shows the clock sources connectivity to the global clock networks.

| Global Clock    |                        |              |              |              |              | (            | Globa        | l Cloc       | ck Net       | work                               | S            |              |              |              |              |              |

|-----------------|------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Network Clock   | All Cyclone II Devices |              |              |              |              |              |              |              |              | EP2C15 through EP2C70 Devices Only |              |              |              |              |              |              |

| Sources         | 0                      | 1            | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9                                  | 10           | 11           | 12           | 13           | 14           | 15           |

| CLK0/LVDSCLK0p  | $\checkmark$           |              | $\checkmark$ |              |              |              |              |              |              |                                    |              |              |              |              |              |              |

| CLK1/LVDSCLK0n  |                        | $\checkmark$ | $\checkmark$ |              |              |              |              |              |              |                                    |              |              |              |              |              |              |

| CLK2/LVDSCLK1p  | $\checkmark$           |              |              | $\checkmark$ |              |              |              |              |              |                                    |              |              |              |              |              |              |

| CLK3/LVDSCLK1n  |                        | $\checkmark$ |              | >            |              |              |              |              |              |                                    |              |              |              |              |              |              |

| CLK4/LVDSCLK2p  |                        |              |              |              | $\checkmark$ |              | >            |              |              |                                    |              |              |              |              |              |              |

| CLK5/LVDSCLK2n  |                        |              |              |              |              | $\checkmark$ | >            |              |              |                                    |              |              |              |              |              |              |

| CLK6/LVDSCLK3p  |                        |              |              |              | $\checkmark$ |              |              | >            |              |                                    |              |              |              |              |              |              |

| CLK7/LVDSCLK3n  |                        |              |              |              |              | $\checkmark$ |              | $\checkmark$ |              |                                    |              |              |              |              |              |              |

| CLK8/LVDSCLK4n  |                        |              |              |              |              |              |              |              | $\checkmark$ |                                    | $\checkmark$ |              |              |              |              |              |

| CLK9/LVDSCLK4p  |                        |              |              |              |              |              |              |              |              | $\checkmark$                       | $\checkmark$ |              |              |              |              |              |

| CLK10/LVDSCLK5n |                        |              |              |              |              |              |              |              | $\checkmark$ |                                    |              | $\checkmark$ |              |              |              |              |

| CLK11/LVDSCLK5p |                        |              |              |              |              |              |              |              |              | $\checkmark$                       |              | $\checkmark$ |              |              |              |              |

| CLK12/LVDSCLK6n |                        |              |              |              |              |              |              |              |              |                                    |              |              | $\checkmark$ |              | $\checkmark$ |              |

| CLK13/LVDSCLK6p |                        |              |              |              |              |              |              |              |              |                                    |              |              |              | $\checkmark$ | $\checkmark$ |              |

| CLK14/LVDSCLK7n |                        |              |              |              |              |              |              |              |              |                                    |              |              | $\checkmark$ |              |              | $\checkmark$ |

| CLK15/LVDSCLK7p |                        |              |              |              |              |              |              |              |              |                                    |              |              |              | $\checkmark$ |              | $\checkmark$ |

| PLL1_c0         | $\checkmark$           | $\checkmark$ |              | $\checkmark$ |              |              |              |              |              |                                    |              |              |              |              |              |              |

| PLL1_c1         | $\checkmark$           |              | $\checkmark$ | $\checkmark$ |              |              |              |              |              |                                    |              |              |              |              |              |              |

| PLL1_c2         |                        | $\checkmark$ | $\checkmark$ |              |              |              |              |              |              |                                    |              |              |              |              |              |              |

| PLL2_c0         |                        |              |              |              | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |              |                                    |              |              |              |              |              |              |

| PLL2_c1         |                        |              |              |              | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |              |                                    |              |              |              |              |              |              |

| PLL2_c2         |                        |              |              |              |              | $\checkmark$ | $\checkmark$ |              |              |                                    |              |              |              |              |              |              |

| PLL3_c0         |                        |              |              |              |              |              |              |              | $\checkmark$ | $\checkmark$                       |              | $\checkmark$ |              |              |              |              |

| PLL3_c1         |                        |              |              |              |              |              |              |              | $\checkmark$ |                                    | $\checkmark$ | $\checkmark$ |              |              |              |              |

| PLL3_c2         |                        |              |              |              |              |              |              |              |              | $\checkmark$                       | $\checkmark$ |              |              |              |              |              |

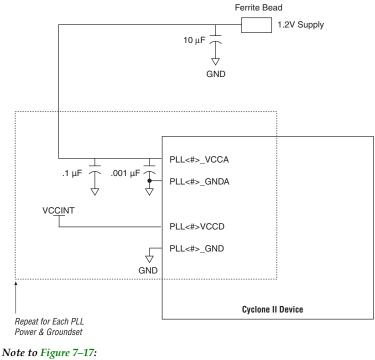

Figure 7–17. PLL Power Schematic for Cyclone II PLLs

(1) Applies to PLLs 1 through 4.

## VCCD & GND

The digital power and ground pins are labeled VCCD\_PLL<*PLL number>* and GND\_PLL<*PLL number>*. The VCCD pin supplies the power for the digital circuitry in the PLL. Connect these VCCD pins to the quietest digital supply on the board. In most systems, this is the digital 1.2-V supply supplied to the device's V<sub>CCINT</sub> pins. Connect the VCCD pins to a power supply even if you do not use the PLL. When connecting the V<sub>CCD</sub> pins to V<sub>CCINT</sub>, you do not need any filtering or isolation. You can connect the GND pins directly to the same ground plane as the device's digital ground. See Figure 7–17.

## Conclusion

Cyclone II device PLLs provide you with complete control of device clocks and system timing. These PLLs support clock multiplication/division, phase shift, and programmable duty cycle for your cost-sensitive clock synthesis applications.

M4K memory blocks do not support asynchronous memory (unregistered inputs).

The M4K memory blocks support the following modes:

- Single-port

- Simple dual-port

- True dual-port (bidirectional dual-port)

- Shift register

- ROM

- FIFO buffers

- Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

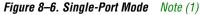

## **Single-Port Mode**

Single-port mode supports non-simultaneous read and write operations. Figure 8–6 shows the single-port memory configuration for Cyclone II memory blocks.

#### Note to Figure 8–6:

(1) Two single-port memory blocks can be implemented in a single M4K block in packed mode.

In single-port mode, the outputs are in read-during-write mode, which means that during the write operation, data written to the RAM flows through to the RAM outputs. When the output registers are bypassed, the new data is available on the rising edge of the same clock cycle on which it was written.

•••

See "Read-During- Write Operation at the Same Address" on page 8–28 for more information about read-during-write mode.

The port width configurations for M4K blocks in single-port mode are as follows:

You can use any of the user I/O pins for commands and addresses. Because of the symmetrical setup and hold time for the command and address pins at the memory device, you may need to generate these signals from the negative edge of the system clock.

The clocks to the SDRAM device are called CK and CK#. Use any of the user I/O pins via the DDR registers to generate the CK and CK# signals to meet the  $t_{DQSS}$  requirements of the DDR SDRAM or DDR2 SDRAM device. The memory device's  $t_{DQSS}$  requires the positive edge of the write DQS signal to be within 25% of the positive edge of the DDR SDRAM and DDR2 SDRAM clock input. Because of strict skew requirements between CK and CK# signals, use adjacent pins to generate the clock pair. Surround the pair with buffer pins tied to  $V_{CC}$  and pins tied to ground for better noise immunity from other signals.

### Read & Write Operation

When reading from the memory, DDR and DDR2 SDRAM devices send the data edge-aligned relative to the data strobe. To properly read the data, the data strobe must be center-aligned relative to the data inside the FPGA. Cyclone II devices feature clock delay control circuitry to shift the data strobe to the middle of the data window. Figure 9–1 shows an example of how the memory sends out the data and data strobe for a burst-of-two operation. Additionally, each Cyclone II I/O bank has its own VCCIO pins. Any single I/O bank can only support one V<sub>CCIO</sub> setting from among 1.5, 1.8, 2.5 or 3.3 V. Although there can only be one V<sub>CCIO</sub> voltage per I/O bank, Cyclone II devices permit additional input signaling capabilities, as shown in Table 10–4.

| Donk V (V)                 | Acceptable Input Levels (V) |                         |              |                       |  |

|----------------------------|-----------------------------|-------------------------|--------------|-----------------------|--|

| Bank V <sub>ccio</sub> (V) | 3.3                         | 2.5                     | 1.8          | 1.5                   |  |

| 3.3                        | $\checkmark$                | 🗸 (1)                   |              |                       |  |

| 2.5                        | $\checkmark$                | $\checkmark$            |              |                       |  |

| 1.8                        | <ul> <li>(2)</li> </ul>     | <ul><li>✓ (2)</li></ul> | $\checkmark$ | <ul><li>(1)</li></ul> |  |

| 1.5                        | <ul> <li>(2)</li> </ul>     | <ul> <li>(2)</li> </ul> | $\checkmark$ | $\checkmark$          |  |

Notes to Table 10–4:

- Because the input level does not drive to the rail, the input buffer does not completely shut off, and the I/O current is slightly higher than the default value.

- (2) These input values overdrive the input buffer, so the pin leakage current is slightly higher than the default value. To drive inputs higher than V<sub>CCIO</sub> but less than 4.0 V, disable the PCI clamping diode and turn on Allow voltage overdrive for LVTTL/LVCMOS input pins in Settings > Device > Device and Pin Options > Pin Placement tab. This setting allows input pins with LVTTL or LVCMOS I/O standards to be placed by the Quartus II software in an I/O bank with a lower V<sub>CCIO</sub> voltage than the voltage specified by the pins.

Any number of supported single-ended or differential standards can be simultaneously supported in a single I/O bank as long as they use compatible  $V_{CCIO}$  levels for input and output pins. For example, an I/O bank with a 2.5-V  $V_{CCIO}$  setting can support 2.5-V LVTTL inputs and outputs, 2.5-V LVDS-compatible inputs and outputs, and 3.3-V LVCMOS inputs only.

Voltage-referenced standards can be supported in an I/O bank using any number of single-ended or differential standards as long as they use the same V<sub>REF</sub> and a compatible V<sub>CCIO</sub> value. For example, if you choose to implement both SSTL-2 and SSTL-18 in your Cyclone II device, I/O pins using these standards—because they require different V<sub>REF</sub> values—must be in different banks from each other. However, the same I/O bank can support SSTL-2 and 2.5-V LVCMOS with the V<sub>CCIO</sub> set to 2.5 V and the V<sub>REF</sub> set to 1.25 V.

Refer to "Pad Placement and DC Guidelines" on page 10–27 for more information.

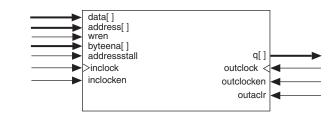

Figure 11–17. Cyclone II High-Speed I/O Timing Budget Note (1)

### Note to Figure 11–17:

(1) The equation for the high-speed I/O timing budget is: Period = 0.5/TCCS + RSKM + SW + RSKM + 0.5/TCCS.

## Design Guidelines

This section provides guidelines for designing with Cyclone II devices.

## **Differential Pad Placement Guidelines**

To maintain an acceptable noise level on the  $\rm V_{\rm CCIO}$  supply, there are restrictions on placement of single-ended I/O pins in relation to differential pads.

See the guidelines in the *Selectable I/O Standards in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook* for placing single-ended pads with respect to differential pads in Cyclone II devices.

## **Board Design Considerations**

This section explains how to get the optimal performance from the Cyclone II I/O interface and ensure first-time success in implementing a functional design with optimal signal quality. The critical issues of controlled impedance of traces and connectors, differential routing, and termination techniques must be considered to get the best performance from the IC. The Cyclone II device generates signals that travel over the media at frequencies as high as 805 Mbps. Use the following general guidelines for improved signal quality:

Base board designs on controlled differential impedance. Calculate and compare all parameters such as trace width, trace thickness, and the distance between two differential traces.

13 - 28

You must connect all other configuration pins (nCONFIG, nSTATUS, DCLK, DATAO, and CONF DONE) to every Cyclone II device in the chain. The configuration signals may require buffering to ensure signal integrity and prevent clock skew problems. You should buffer the DCLK and DATA lines for every fourth device. Because all device CONF DONE pins are tied together, all devices initialize and enter user mode at the same time.

Since all nSTATUS and CONF DONE pins are connected, if any Cyclone II device detects an error, configuration stops for the entire chain and the entire chain must be reconfigured. For example, if the first Cyclone II detects an error, it resets the chain by pulling its nSTATUS pin low. This behavior is similar to a single Cyclone II device detecting an error.

If the Auto-restart configuration after error option is turned on, the Cyclone II devices release their nSTATUS pins after a reset time-out period (maximum of 40 µs). After all nSTATUS pins are released and pulled high, the MAX II device reconfigures the chain without pulsing nCONFIG low. If the Auto-restart configuration after error option is turned off, the MAX II device must generate a low-to-high transition (with a low pulse of at least 2 µs) on nCONFIG to restart the configuration process.

If you want to delay the initialization of the devices in the chain, you can use the CLKUSR pin option. The CLKUSR pin allows you to control when your device enters user mode. This feature also allows you to control the order of when each device enters user mode by feeding a separate clock to each device's CLKUSR pin. By using the CLKUSR pins, you can choose any device in the multiple device chain to enter user mode first and have the other devices enter user mode at a later time.

Different device families may require a different number of initialization clock cycles. Therefore, if your multiple device chain consists of devices from different families, the devices may enter user mode at a slightly different time due to the different number of initialization clock cycles required. However, if the number of initialization clock cycles is similar across different device families or if the devices are from the same family, then the devices enter user mode at the same time. See the respective device family handbook for more information about the number of initialization clock cycles required.

Table 13–12 describes the optional configuration pins. If these optional configuration pins are not enabled in the Quartus II software, they are available as general-purpose user I/O pins. Therefore during configuration, these pins function as user I/O pins and are tri-stated with weak pull-up resistors.

| Pin Name  | User Mode                                        | Pin Type              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|--------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKUSR    | N/A if option is<br>on. I/O if option<br>is off. | Input                 | This is an optional user-supplied clock input that<br>synchronizes the initialization of one or more devices. This<br>pin is enabled by turning on the <b>Enable user-supplied</b><br><b>start-up clock (CLKUSR)</b> option in the Quartus II software                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| INIT_DONE | N/A if option is<br>on. I/O if option<br>is off. | Output open-<br>drain | This is a status pin that can be used to indicate when the device has initialized and is in user mode. When nCONFIG is low and during the beginning of configuration, the INIT_DONE pin is tri-stated and pulled high due to an external 10-k $\Omega$ pull-up resistor. Once the option bit to enable INIT_DONE is programmed into the device (during the first frame of configuration data), the INIT_DONE pin goes low. When initialization is complete, the INIT_DONE pin is released and pulled high and the FPGA enters user mode. Thus, the monitoring circuitry must be able to detect a low-to-high transition. This pin is enabled by turning on the <b>Enable INIT_DONE output</b> option in the Quartus II software. |

| DEV_OE    | N/A if option is<br>on. I/O if option<br>is off. | Input                 | Optional pin that allows the user to override all tri-states on<br>the device. When this pin is driven low, all I/O pins are tri-<br>stated. When this pin is driven high, all I/O pins behave as<br>programmed. This pin is enabled by turning on the <b>Enable</b><br><b>device-wide output enable (DEV_OE)</b> option in the<br>Quartus II software.                                                                                                                                                                                                                                                                                                                                                                          |

| DEV_CLRn  | N/A if option is<br>on. I/O if option<br>is off. | Input                 | Optional pin that allows you to override all clears on all device registers. When this pin is driven low, all registers are cleared. When this pin is driven high, all registers behave as programmed. This pin is enabled by turning on the <b>Enable device-wide reset (DEV_CLRn)</b> option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                                       |

| Table 15–2. Thermal Resistance of Cyclone II Devices for Board Meeting JEDEC Specifications (Part 2 of 2) |              |                    |                                      |                                         |                                         |                                         |                            |

|-----------------------------------------------------------------------------------------------------------|--------------|--------------------|--------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------|

| Device                                                                                                    | Pin<br>Count | Package            | θ <sub>JA</sub> (° C/W)<br>Still Air | θ <sub>JA</sub> (° C/W)<br>100 ft./min. | θ <sub>JA</sub> (° C/W)<br>200 ft./min. | θ <sub>JA</sub> (° C/W)<br>400 ft./min. | θ <sub>JC</sub><br>(° C/W) |

| EP2C50                                                                                                    | 484          | FineLine BGA       | 18.4                                 | 14.4                                    | 12.4                                    | 10.9                                    | 2.8                        |

|                                                                                                           | 484          | Ultra FineLine BGA | 19.6                                 | 15.6                                    | 13.6                                    | 11.9                                    | 4.4                        |

|                                                                                                           | 672          | FineLine BGA       | 17.7                                 | 13.7                                    | 11.8                                    | 10.2                                    | 2.6                        |

| EP2C70                                                                                                    | 672          | FineLine BGA       | 16.9                                 | 13                                      | 11.1                                    | 9.7                                     | 2.2                        |

|                                                                                                           | 896          | FineLine BGA       | 16.3                                 | 11.9                                    | 10.5                                    | 9.1                                     | 2.1                        |

Table 15–3 provides board dimension information for each package.

| Table 15–3. PCB Dimensions Notes (1), (2) |                  |                        |                              |                            |  |

|-------------------------------------------|------------------|------------------------|------------------------------|----------------------------|--|

| 2.5 mm<br>Thick                           | Signal<br>Layers | Power/Ground<br>Layers | Package<br>Dimension<br>(mm) | Board<br>Dimension<br>(mm) |  |

| F896                                      | 10               | 10                     | 31                           | 91                         |  |

| F672                                      | 8                | 8                      | 27                           | 87                         |  |

| F672                                      | 7                | 7                      | 27                           | 87                         |  |

| F484                                      | 7                | 7                      | 23                           | 83                         |  |

| F484                                      | 6                | 6                      | 23                           | 83                         |  |

| U484                                      | 7                | 7                      | 19                           | 79                         |  |

| U484                                      | 6                | 6                      | 19                           | 79                         |  |

| F256                                      | 6                | 6                      | 17                           | 77                         |  |

Notes to Table 15–3:

(1) Power layer Cu thickness 35 um, Cu 90%

(2) Signal layer Cu thickness 17 um, Cu 15%

Tables 15–5 and 15–6 show the package information and package outline figure references, respectively, for the 144-pin TQFP package.

| Description                | Specification                                  |

|----------------------------|------------------------------------------------|

| Ordering code reference    | Т                                              |

| Package acronym            | TQFP                                           |

| Lead frame material        | Copper                                         |

| Lead finish (plating)      | Regular: 85Sn:15Pb (Typ.)<br>Pb-free: Matte Sn |

| JEDEC Outline Reference    | MS-026 Variation: BFB                          |

| Maximum lead coplanarity   | 0.003 inches (0.08mm)                          |

| Weight                     | 1.3 g                                          |

| Moisture sensitivity level | Printed on moisture barrier bag                |

| Table 15–6. 144-Pin TQFP Package Outline Dimensions |                |      |      |  |  |

|-----------------------------------------------------|----------------|------|------|--|--|

| Symbol                                              | Millimeter     |      |      |  |  |

| Symbol                                              | Min.           | Nom. | Max. |  |  |

| A                                                   | -              | -    | 1.60 |  |  |

| A1                                                  | 0.05           | -    | 0.15 |  |  |

| A2                                                  | 1.35           | 1.40 | 1.45 |  |  |

| D                                                   | 22.00 BSC      |      |      |  |  |

| D1                                                  | 20.00 BSC      |      |      |  |  |

| E                                                   | 22.00 BSC      |      |      |  |  |

| E1                                                  | 20.00 BSC      |      |      |  |  |

| L                                                   | 0.45 0.60 0.75 |      |      |  |  |

| L1                                                  | 1.00 REF       |      |      |  |  |

| S                                                   | 0.20 – –       |      |      |  |  |

| b                                                   | 0.17 0.22 0.2  |      | 0.27 |  |  |

| С                                                   | 0.09 – 0.20    |      |      |  |  |

| е                                                   | 0.50 BSC       |      |      |  |  |

| θ                                                   | 0° 3.5° 7°     |      |      |  |  |

## 672-Pin FineLine BGA Package, Option 3 - Wirebond

- All dimensions and tolerances conform to ASME Y14.5M 1994.

- Controlling dimension is in millimeters.

- Pin A1 may be indicated by an ID dot, or a special feature, in its proximity on the package surface.

Tables 15–17 and 15–18 show the package information and package outline figure references, respectively, for the 672-pin FineLine BGA package.

| Table 15–17. 672-Pin FineLine BGA Package Information |                                                           |  |  |  |

|-------------------------------------------------------|-----------------------------------------------------------|--|--|--|

| Description                                           | Specification                                             |  |  |  |

| Ordering code reference                               | F                                                         |  |  |  |

| Package acronym                                       | FineLine BGA                                              |  |  |  |

| Substrate material                                    | ВТ                                                        |  |  |  |

| Solder ball composition                               | Regular: 63Sn:37Pb (Typ.)<br>Pb-free: Sn:3Ag:0.5Cu (Typ.) |  |  |  |

| JEDEC Outline Reference                               | MS-034 Variation: AAL-1                                   |  |  |  |

| Maximum lead coplanarity                              | 0.008 inches (0.20 mm)                                    |  |  |  |

| Weight                                                | 7.7 g                                                     |  |  |  |

| Moisture sensitivity level                            | Printed on moisture barrier bag                           |  |  |  |

| Table 15–18. 672-Pin FineLine BGA Package Outline Dimensions |                 |      |      |  |

|--------------------------------------------------------------|-----------------|------|------|--|

| Symbol                                                       | Dimensions (mm) |      |      |  |

| Symbol                                                       | Min.            | Nom. | Max. |  |

| A                                                            | -               | -    | 2.60 |  |

| A1                                                           | 0.30            | -    | -    |  |

| A2                                                           | -               | -    | 2.20 |  |

| A3                                                           | -               | -    | 1.80 |  |

| D                                                            | 27.00 BSC       |      |      |  |

| E                                                            | 27.00 BSC       |      |      |  |

| b                                                            | 0.50            | 0.60 | 0.70 |  |

| e                                                            | 1.00 BSC        |      |      |  |