Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 1172                                                    |

| Number of Logic Elements/Cells | 18752                                                   |

| Total RAM Bits                 | 239616                                                  |

| Number of I/O                  | 315                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

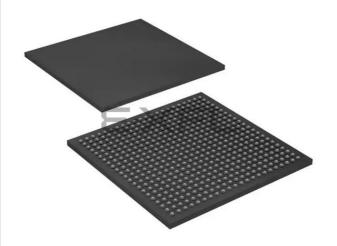

| Package / Case                 | 484-BGA                                                 |

| Supplier Device Package        | 484-FBGA (23x23)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c20f484c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

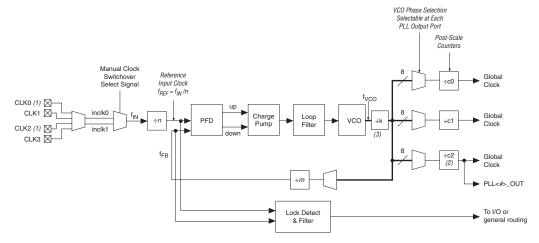

Figure 2–16 shows a block diagram of the Cyclone II PLL.

Figure 2–16. Cyclone II PLL Note (1)

#### Notes to Figure 2–16:

- (1) This input can be single-ended or differential. If you are using a differential I/O standard, then two CLK pins are used. LVDS input is supported via the secondary function of the dedicated CLK pins. For example, the CLK0 pin's secondary function is LVDSCLK1p and the CLK1 pin's secondary function is LVDSCLK1n. If a differential I/O standard is assigned to the PLL clock input pin, the corresponding CLK(n) pin is also completely used. The Figure 2–16 shows the possible clock input connections (CLK0/CLK1) to PLL1.

- (2) This counter output is shared between a dedicated external clock output I/O and the global clock network.

For more information on Cyclone II PLLs, see the PLLs in the *Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

## Embedded Memory

The Cyclone II embedded memory consists of columns of M4K memory blocks. The M4K memory blocks include input registers that synchronize writes and output registers to pipeline designs and improve system performance. The output registers can be bypassed, but input registers cannot.

Embedded multipliers can operate at up to 250 MHz (for the fastest speed grade) for  $18 \times 18$  and  $9 \times 9$  multiplications when using both input and output registers.

Each Cyclone II device has one to three columns of embedded multipliers that efficiently implement multiplication functions. An embedded multiplier spans the height of one LAB row. Table 2–10 shows the number of embedded multipliers in each Cyclone II device and the multipliers that can be implemented.

| Table 2–10. Number of Embedded Multipliers in Cyclone II Devices Note (1) |                                |                         |                   |                     |  |

|---------------------------------------------------------------------------|--------------------------------|-------------------------|-------------------|---------------------|--|

| Device                                                                    | Embedded<br>Multiplier Columns | Embedded<br>Multipliers | 9 × 9 Multipliers | 18 × 18 Multipliers |  |

| EP2C5                                                                     | 1                              | 13                      | 26                | 13                  |  |

| EP2C8                                                                     | 1                              | 18                      | 36                | 18                  |  |

| EP2C15                                                                    | 1                              | 26                      | 52                | 26                  |  |

| EP2C20                                                                    | 1                              | 26                      | 52                | 26                  |  |

| EP2C35                                                                    | 1                              | 35                      | 70                | 35                  |  |

| EP2C50                                                                    | 2                              | 86                      | 172               | 86                  |  |

| EP2C70                                                                    | 3                              | 150                     | 300               | 150                 |  |

*Note to Table 2–10:*

The embedded multiplier consists of the following elements:

- Multiplier block

- Input and output registers

- Input and output interfaces

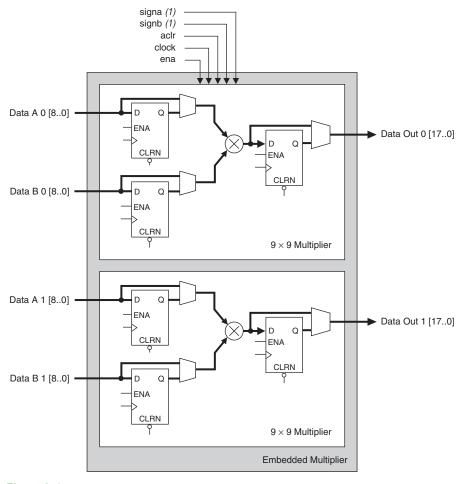

Figure 2–18 shows the multiplier block architecture.

<sup>(1)</sup> Each device has either the number of  $9 \times 9$ -, or  $18 \times 18$ -bit multipliers shown. The total number of multipliers for each device is not the sum of all the multipliers.

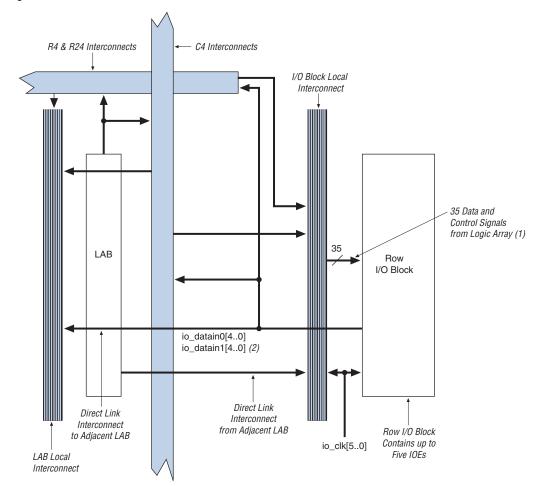

Figure 2-21. Row I/O Block Connection to the Interconnect

#### Notes to Figure 2-21:

- (1) The 35 data and control signals consist of five data out lines, io\_dataout [4..0], five output enables, io\_coe [4..0], five input clock enables, io\_cce\_in [4..0], five output clock enables, io\_cce\_out [4..0], five clocks, io\_cclk [4..0], five asynchronous clear signals, io\_caclr [4..0], and five synchronous clear signals, io\_csclr [4..0].

- (2) Each of the five IOEs in the row I/O block can have two io datain (combinational or registered) inputs.

## 7. PLLs in Cyclone II Devices

CII51007-3.1

#### Introduction

Cyclone<sup>®</sup> II devices have up to four phase-locked loops (PLLs) that provide robust clock management and synthesis for device clock management, external system clock management, and I/O interfaces. Cyclone II PLLs are versatile and can be used as a zero delay buffer, a jitter attenuator, a low skew fan out buffer, or a frequency synthesizer.

Each Cyclone II device has up to four PLLs, supporting advanced capabilities such as clock switchover and programmable switchover. These PLLs offer clock multiplication and division, phase shifting, and programmable duty cycle and can be used to minimize clock delay and clock skew, and to reduce or adjust clock-to-out ( $t_{CO}$ ) and set-up ( $t_{SU}$ ) times.

Cyclone II devices also support a power-down mode where unused clock networks can be turned off. The Altera<sup>®</sup> Quartus<sup>®</sup> II software enables the PLLs and their features without requiring any external devices.

Cyclone II PLLs have been characterized to operate in the commercial junction temperature range (0° to 85° C), the industrial junction temperature range (-40° to 100° C) and the extended temperature range (-40° to 125° C).

Table 7–1 shows the PLLs available in each Cyclone II device.

| Table 7–1. Cyclone II Device PLL Availability |          |          |          |          |  |  |

|-----------------------------------------------|----------|----------|----------|----------|--|--|

| Device                                        | PLL1     | PLL2     | PLL3     | PLL4     |  |  |

| EP2C5                                         | <b>✓</b> | <b>✓</b> |          |          |  |  |

| EP2C8                                         | <b>✓</b> | <b>✓</b> |          |          |  |  |

| EP2C15                                        | ✓        | <b>✓</b> | <b>✓</b> | ✓        |  |  |

| EP2C20                                        | ✓        | <b>✓</b> | <b>✓</b> | ✓        |  |  |

| EP2C35                                        | ✓        | <b>✓</b> | ✓        | ✓        |  |  |

| EP2C50                                        | ✓        | <b>✓</b> | <b>✓</b> | ✓        |  |  |

| EP2C70                                        | ✓        | ✓        | ✓        | <b>✓</b> |  |  |

The VCO frequency is a critical parameter that must be between 300 and 1,000 MHz to ensure proper operation of the PLL. The Quartus II software automatically sets the VCO frequency within the recommended range based on the clock output and phase-shift requirements in your design.

#### **PLL Reference Clock Generation**

In Cyclone II devices, up to four clock pins can drive the PLL, as shown in Figure 7–11 on page 7–26. The multiplexer output feeds the PLL reference clock input. The PLL has internal delay elements that compensate for the clock delay from the input pin to the clock input port of the PLL.

Table 7–3 shows the clock input pin connections to the PLLs in the Cyclone II device.

| Table 7–3. PLL Clock Input Pin Connections |              |              |              |              |          |                |                |                |

|--------------------------------------------|--------------|--------------|--------------|--------------|----------|----------------|----------------|----------------|

|                                            | PLL 1        |              | PLL 2        |              | PLL 3    |                | PLL 4          |                |

| Device                                     | CLK0<br>CLK1 | CLK2<br>CLK3 | CLK4<br>CLK5 | CLK6<br>CLK7 | CLK8     | CLK10<br>CLK11 | CLK12<br>CLK13 | CLK14<br>CLK15 |

| EP2C5                                      | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     |          |                |                |                |

| EP2C8                                      | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     |          |                |                |                |

| EP2C15                                     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b> | <b>✓</b>       | <b>✓</b>       | <b>✓</b>       |

| EP2C20                                     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b> | <b>✓</b>       | <b>✓</b>       | <b>✓</b>       |

| EP2C35                                     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b> | <b>✓</b>       | <b>✓</b>       | <b>✓</b>       |

| EP2C50                                     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b> | <b>✓</b>       | <b>✓</b>       | <b>✓</b>       |

| EP2C70                                     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b> | <b>✓</b>       | <b>✓</b>       | <b>✓</b>       |

Each PLL can be fed by one of four single-ended or two differential clock input pins. For example, PLL 1 can be fed by CLK[3..0] when using a single-ended I/O standard. When your design uses a differential I/O standard, these same clock pins have a secondary function as  $\begin{tabular}{l} $LVDSCLK[2..1]p$ and $LVDSCLK[2..1]n$ pins. When using differential clocks, the CLK0 pin's secondary function is $LVDSCLK1p$, the CLK1 pin's secondary function is $LVDSCLK1p$, etc.$

## Software Overview

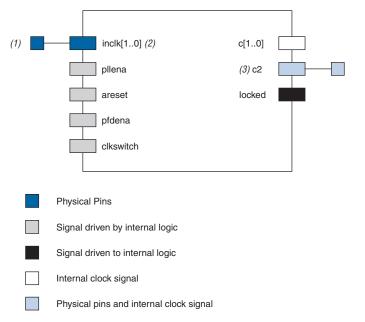

You can use the altpll megafunction in the Quartus II software to enable Cyclone II PLLs. Figure 7–3 shows the available ports in Cyclone II PLLs and their sources and destinations. The c0 and c1 counters feed the internal global clock networks and the c2 counter can feed the global clock network and a dedicated external clock output pin (PLL<#>\_OUT) at the same time.

Figure 7-3. Cyclone II PLL Signals

#### Notes to Figure 7-3:

- (1) These signals can be assigned to either a single-ended or differential I/O standard.

- (2) The inclk must be driven by one of two dedicated clock input pins.

- (3) This counter output can drive both a dedicated external clock output (PLL<#> OUT) and the global clock network.

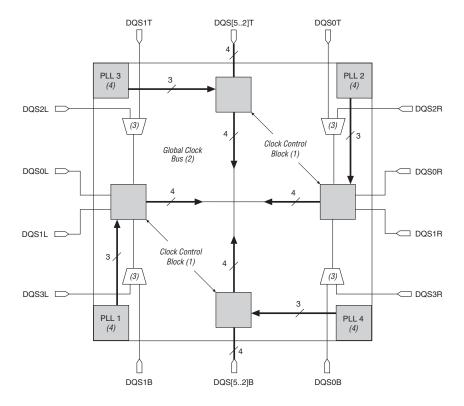

directly to the clock control block. For the larger Cyclone II devices, the corner DQS signals are multiplexed before they are routed to the clock control block. When you use the corner DQS pins for DDR implementation, there is a degradation in the performance of the memory interface. The clock control block is used to select from a number of input clock sources, in this case either PLL clock outputs or DQS pins, to drive onto the global clock bus. Figure 9–7 shows the corner DQS signal mappings for EP2C15 through EP2C70 devices.

Figure 9-7. Corner DQS Signal Mapping for EP2C15-EP2C70 Devices

#### *Notes to Figure 9–7:*

- (1) There are four control blocks on each side.

- (2) There are a total of 16 global clocks available.

- (3) Only one of the corner DQS pins in each corner can feed the clock control block at a time. The other DQS pins can be used as general purpose I/O pins.

- (4) PLL resource can be lost if all DQS pins from one side are used at the same time.

- (5) Top/bottom and side IOE have different timing.

## **Conclusion**

Cyclone II devices support SDR SDRAM, DDR SDRAM, DDR2 SDRAM, and QDRII SRAM external memories. Cyclone II devices feature high-speed interfaces that transfer data between external memory devices at up to 167 MHz/333 Mbps for DDR and DDR2 SDRAM devices and 167 MHz/667 Mbps for QDRII SRAM devices. The clock delay control circuitry allows you to fine tune the phase shift for the input clocks or strobes to properly align clock edges as needed to capture data.

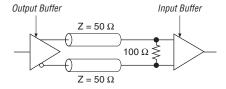

transistor-to-transistor logic (TTL), and positive (or pseudo) emitter coupled logic (PECL). This low EMI makes LVDS ideal for applications with low EMI requirements or noise immunity requirements. The LVDS standard does not require an input reference voltage. However, it does require a termination resistor of 90 to 110  $\Omega$ between the two signals at the input buffer. Cyclone II devices support true differential LVDS inputs and outputs.

LVDS outputs on Cyclone II need external resistor network to work properly. Refer to the *High Speed Differential Interfaces in Cyclone II Devices* chapter in volume 1 of the *Cyclone II Device Handbook* for more information.

For reduced swing differential signaling (RSDS),  $V_{OD}$  ranges from 100 to 600 mV. For mini-LVDS,  $V_{OD}$  ranges from 300 to 600 mV. The differential termination resistor value ranges from 95 to 105  $\Omega$  for both RSDS and mini-LVDS. Cyclone II devices support RSDS/mini-LVDS outputs only.

#### **Differential LVPECL**

The low voltage positive (or pseudo) emitter coupled logic (LVPECL) standard is a differential interface standard recommending  $V_{\rm CCIO}$  of 3.3 V. The LVPECL standard also supports  $V_{\rm CCIO}$  of 2.5 V, 1.8 V and 1.5 V. The standard is used in applications involving video graphics, telecommunications, data communications, and clock distribution. The high-speed, low-voltage swing LVPECL I/O standard uses a positive power supply and is similar to LVDS. However, LVPECL has a larger differential output voltage swing than LVDS. The LVPECL standard does not require an input reference voltage, but it does require an external  $100\text{-}\Omega$  termination resistor between the two signals at the input buffer. Figures 10--17 and 10--18 show two alternate termination schemes for LVPECL. LVPECL input standard is supported at the clock input pins on Cyclone II devices. LVPECL output standard is not supported.

Figure 10–17. LVPECL DC Coupled Termination

# Referenced Documents

This chapter references the following documents:

- Altera Reliability Report

- AN 75: High-Speed Board Designs

- Cyclone II Architecture chapter in volume 1 of the Cyclone II Device Handbook

- Cyclone II Device Family Data Sheet, section 1 of the Cyclone II Device Handbook

- DC Characteristics and Timing Specifications chapter in volume 1 of the Cyclone II Device Handbook

- External Memory Interfaces chapter in volume 1 of the Cyclone II Device Handbook

- High Speed Differential Interfaces in Cyclone II Devices chapter in volume 1 of the Cyclone II Device Handbook

- Hot Socketing & Power-On Reset chapter in volume 1 of the Cyclone II Device Handbook

- I/O Management chapter in volume 2 of the Quartus II Handbook

## Document Revision History

Table 10–13 shows the revision history for this document.

| Table 10–13. Document Revision History |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date and<br>Document<br>Version        | Changes Made                                                                                                                                                                                                                                                                                                                                                                                 | Summary of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| February 2008<br>v2.4                  | <ul> <li>Added "Referenced Documents" section.</li> <li>Updated "Differential Pad Placement<br/>Guidelines" section.</li> </ul>                                                                                                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| February 2007<br>v2.3                  | <ul> <li>Added document revision history.</li> <li>Updated "Introduction" and its feetpara note.</li> <li>Updated Note (2) in Table 10–4.</li> <li>Updated "Differential LVPECL" section.</li> <li>Updated "Differential Pad Placement Guidelines" section.</li> <li>Updated "Output Pads" section.</li> <li>Added new section "5.0-V Device Compatibility" with two new figures.</li> </ul> | <ul> <li>Added reference detail for ESD specifications.</li> <li>Added information about differential placement restrictions applying only to pins in the same bank.</li> <li>Added information that Cyclone II device supports LVDS on clock inputs at 3.3V V<sub>CCIO</sub>.</li> <li>Added more information on DC placement guidelines.</li> <li>Added information stating SSTL and HSTL outputs can be closer than 2 pads from V<sub>REF</sub>.</li> <li>Added 5.0 Device tolerence solution.</li> </ul> |  |  |  |

Figure 12–4. 9-Bit Multiplier Mode

Note to Figure 12-4:

(1) If necessary, you can send these signals through one register to match the data signal path.

All 9-bit multiplier inputs and results can be independently sent through registers. The multiplier inputs can accept signed integers, unsigned integers, or a combination of both. Each embedded multiplier only has one signa signal to control the sign representation of both data A inputs (one for each  $9 \times 9$  multiplier) and one signb signal to control the sign representation of both data B inputs. Therefore, all of the data A inputs feeding the same embedded multiplier must have the same sign representation. Similarly, all of the data B inputs feeding the same embedded multiplier must have the same sign representation.

## 13. Configuring Cyclone II Devices

CII51013-3.1

#### Introduction

Cyclone<sup>®</sup> II devices use SRAM cells to store configuration data. Since SRAM memory is volatile, configuration data must be downloaded to Cyclone II devices each time the device powers up. You can use the active serial (AS) configuration scheme, which can operate at a DCLK frequency up to 40 MHz, to configure Cyclone II devices. You can also use the passive serial (PS) and Joint Test Action Group (JTAG)-based configuration schemes to configure Cyclone II devices. Additionally, Cyclone II devices can receive a compressed configuration bitstream and decompress this data on-the-fly, reducing storage requirements and configuration time.

This chapter explains the Cyclone II configuration features and describes how to configure Cyclone II devices using the supported configuration schemes. This chapter also includes configuration pin descriptions and the Cyclone II configuration file format.

For more information on setting device configuration options or creating configuration files, see the *Software Settings* chapter in the *Configuration Handbook*.

## Cyclone II Configuration Overview

You can use the AS, PS, and JTAG configuration schemes to configure Cyclone II devices. You can select which configuration scheme to use by driving the Cyclone II device  ${\tt MSEL}$  pins either high or low as shown in Table 13–1. The  ${\tt MSEL}$  pins are powered by the  $V_{CCIO}$  power supply of the bank they reside in. The  ${\tt MSEL}$  [1 . . 0] pins have 9-k $\Omega$  internal pull-down resistors that are always active. During power-on reset (POR) and reconfiguration, the  ${\tt MSEL}$  pins have to be at LVTTL  $V_{IL}$  or  $V_{IH}$  levels to be considered a logic low or logic high, respectively. Therefore, to avoid any problems with detecting an incorrect configuration scheme, you should connect the  ${\tt MSEL}$  [] pins to the  $V_{CCIO}$  of the I/O bank they reside in and GND without any pull-up or pull-down resistors. The  ${\tt MSEL}$  [] pins should not be driven by a microprocessor or another device.

#### **Programming Serial Configuration Devices**

Serial configuration devices are non-volatile, flash-memory-based devices. You can program these devices in-system using the USB-Blaster<sup>TM</sup> or ByteBlaster<sup>TM</sup> II download cable. Alternatively, you can program them using the Altera Programming Unit (APU), supported third-party programmers, or a microprocessor with the SRunner software driver.

You can use the AS programming interface to program serial configuration devices in-system. During in-system programming, the download cable disables FPGA access to the AS interface by driving the nCE pin high. Cyclone II devices are also held in reset by pulling the nCONFIG signal low. After programming is complete, the download cable releases the nCE and nCONFIG signals, allowing the pull-down and pull-up resistor to drive GND and  $V_{CC}$ , respectively. Figure 13–7 shows the download cable connections to the serial configuration device.

For more information on the USB-Blaster download cable, see the *USB-Blaster USB Port Download Cable Data Sheet*. For more information on the ByteBlaster II cable, see the *ByteBlaster II Download Cable Data Sheet*.

All information in the "Single Device PS Configuration Using a MAX II Device as an External Host" on page 13–22 section is also applicable when using a microprocessor as an external host. Refer to that section for all configuration information.

The MicroBlaster™ software driver allows you to configure Altera FPGAs, including Cyclone II devices, through the ByteBlaster II or ByteBlasterMV cable in PS mode. The MicroBlaster software driver supports a RBF programming input file and is targeted for embedded PS configuration. The source code is developed for the Windows NT operating system, although you can customize it to run on other operating systems.

Since the Cyclone II device can decompress the compressed configuration data on-the-fly during PS configuration, the MicroBlaster software can accept a compressed RBF file as its input file.

For more information on the MicroBlaster software driver, see the *Configuring the MicroBlaster Passive Serial Software Driver White Paper* and source files on the Altera web site at **www.altera.com**.

If you turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Quartus II software, the Cyclone II devices does not enter user mode after the MicroBlaster has transmitted all the configuration data in the RBF file. You need to supply enough initialization clock cycles to CLKUSR pin to enter user mode.

### Single Device PS Configuration Using a Configuration Device

You can use an Altera configuration device (for example, an EPC2, EPC1, or enhanced configuration device) to configure Cyclone II devices using a serial configuration bitstream. Configuration data is stored in the configuration device. Figure 13–13 shows the configuration interface connections between the Cyclone II device and a configuration device.

The figures in this chapter only show the configuration-related pins and the configuration pin connections between the configuration device and the FPGA.

the five common signals (nCONFIG, nSTATUS, DCLK, DATA0, and CONF\_DONE) between the cable and the configuration device. You can also remove the configuration device from the board when configuring the FPGA with the cable. Figure 13–21 shows a combination of a configuration device and a download cable to configure an FPGA.

USB Blaster, ByteBlaster II, V<sub>CC</sub> (1) MasterBlaster, or ByteBlasterMV 10-Pin Male Header Vcc 10 kO (Passive Serial Mode) **≲**10 kΩ Cyclone II FPGA Pin 1 (5) CONF DONE  $V_{CC}$ 10  $k\Omega$ MSEL0 nSTATUS **DCLK** MSEL1 마 nCEO -N.C. (6) nCE GND (3) (3) (3)DATA0 nCONFIG GŇD Configuration Device \((3) DCI K DATA OE (5) nCS (5) nINIT\_CONF (4)

Figure 13-21. PS Configuration with a Download Cable & Configuration Device Circuit

#### *Notes to Figure 13–21:*

- (1) The pull-up resistor should be connected to the same supply voltage as the configuration device.

- (2) Pin 6 of the header is a V<sub>IO</sub> reference voltage for the MasterBlaster output driver. V<sub>IO</sub> should match the device's V<sub>CCIO</sub>. Refer to the MasterBlaster Serial/USB Communications Cable Data Sheet for this value. In the ByteBlasterMV, this pin is a no connect. In the USB-Blaster and ByteBlaster II, this pin is connected to nCE when it is used for AS programming, otherwise it is a no connect.

- (3) You should not attempt configuration with a download cable while a configuration device is connected to a Cyclone II device. Instead, you should either remove the configuration device from its socket when using the download cable or place a switch on the five common signals between the download cable and the configuration device.

- (4) The ninit\_conf pin (available on enhanced configuration devices and EPC2 devices only) has an internal pull-up resistor that is always active. This means an external pull-up resistor should not be used on the ninit\_conf to nconfig line. The ninit\_conf pin does not need to be connected if its functionality is not used. If ninit\_conf is not used or not available (e.g., on EPC1 devices), nconfig must be pulled to V<sub>CC</sub> either directly or through a resistor (if reconfiguration is required, a resistor is necessary).

- (5) The enhanced configuration devices' OE and nCS pins have internal programmable pull-up resistors. If internal pull-up resistors are used, external pull-up resistors should not be used on these pins. The internal pull-up resistors are used by default in the Quartus II software. To turn off the internal pull-up resistors, check the **Disable nCS and OE pull-ups on configuration device** option when generating programming files.

- (6) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

During the capture phase, multiplexers preceding the capture registers select the active device data signals. This data is then clocked into the capture registers. The multiplexers at the outputs of the update registers also select active device data to prevent functional interruptions to the device. During the shift phase, the boundary-scan shift register is formed by clocking data through capture registers around the device periphery, then out of the TDO pin. The device can simultaneously shift new test data into TDI and replace the contents of the capture registers. During the update phase, data in the capture registers is transferred to the update registers. This data can then be used in the  ${\tt EXTEST}$  instruction mode. See "EXTEST Instruction Mode" on page 14–11 for more information.

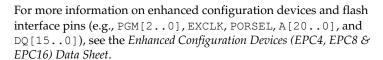

Figure 14–9 shows the SAMPLE/PRELOAD waveforms. The SAMPLE/PRELOAD instruction code is shifted in through the TDI pin. The TAP controller advances to the CAPTURE DR state, then to the SHIFT DR state, where it remains if TMS is held low. The data that was present in the capture registers after the capture phase is shifted out of the TDO pin. New test data shifted into the TDI pin appears at the TDO pin after being clocked through the entire boundary-scan register. Figure 14–9 shows that the instruction code at TDI does not appear at the TDO pin until after the capture register data is shifted out. If TMS is held high on two consecutive TCK clock cycles, the TAP controller advances to the UPDATE DR state for the update phase.

Figure 14-9. SAMPLE/PRELOAD Shift Data Register Waveforms

#### **EXTEST Instruction Mode**

The EXTEST instruction mode is used to check external pin connections between devices. Unlike the SAMPLE/PRELOAD mode, EXTEST allows test data to be forced onto the pin signals. By forcing known logic high and low levels on output pins, opens and shorts can be detected at pins of any device in the scan chain.

When designing a board for JTAG configuration of Cyclone II devices, the connections for the dedicated configuration pins need to be considered.

For more information on using the IEEE Std.1149.1 circuitry for device configuration, see the *Configuring Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

## BST for Configured Devices

For a configured device, the input buffers are turned off by default for I/O pins that are set as output only in the design file. Nevertheless, executing the SAMPLE instruction will turn on the input buffers for the output pins. You can set the Quartus II software to always enable the input buffers on a configured device so it behaves the same as an unconfigured device for boundary-scan testing, allowing sample function on output pins in the design. This aspect can cause slight increase in standby current because the unused input buffer is always on. In the Quartus II software, do the following:

- 1. Choose **Settings** (Assignment menu).

- 2. Click Assembler.

- 3. Turn on Always Enable Input Buffers.

- 4. If you use the default setting with input disabled, you need to convert the default BSDL file to the design-specific BSDL file using the BSDLCustomizer script. For more information regarding BSDL file, refer to "Boundary-Scan Description Language (BSDL) Support".

| Table 15–8. 208-Pin PQFP Package Outline Dimensions (Part 2 of 2) |            |      |      |  |  |

|-------------------------------------------------------------------|------------|------|------|--|--|

| Cumbal                                                            | Millimeter |      |      |  |  |

| Symbol                                                            | Min.       | Nom. | Max. |  |  |

| е                                                                 | 0.50 BSC   |      |      |  |  |

| q                                                                 | 0° 3.5° 8° |      |      |  |  |

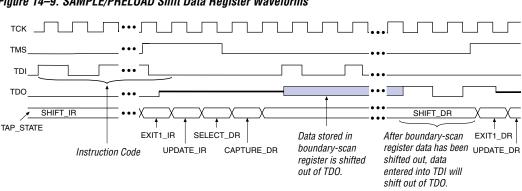

Figure 15–2 shows a 208-pin PQFP package outline.

Pin 1 ID

Pin 52

Figure 15-2. 208-pin PQFP Package Outline

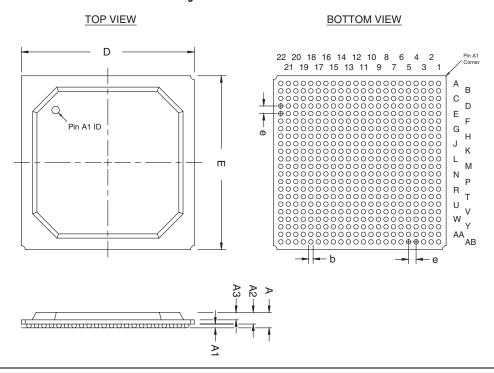

Figure 15–4 shows a 256-pin FineLine BGA package outline.

Figure 15-4. 256-Pin FineLine BGA Package Outline

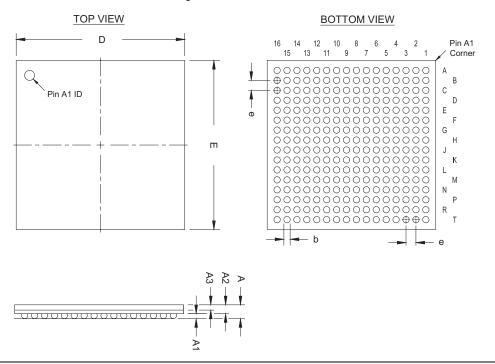

Figure 15–5 shows a 484-pin FineLine BGA package outline.

Figure 15-5. 484-Pin FineLine BGA Package Outline