#### Intel - EP2C20F484C7N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 1172                                                     |

| Number of Logic Elements/Cells | 18752                                                    |

| Total RAM Bits                 | 239616                                                   |

| Number of I/O                  | 315                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 484-BGA                                                  |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c20f484c7n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Copyright © 2008 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

| Guidelines for IEEE Std. 1149.1 Boundary-Scan Testing | 14 - 18 |

|-------------------------------------------------------|---------|

| Boundary-Scan Description Language (BSDL) Support     | 14–19   |

| Conclusion                                            | 14–19   |

| References                                            | 14–19   |

| Document Revision History                             | 14–20   |

# Section VII. PCB Layout Guidelines

| Revision History |  | 14- | -1 |  |

|------------------|--|-----|----|--|

|------------------|--|-----|----|--|

## Chapter 15. Package Information for Cyclone II Devices

| Introduction                                          |       |

|-------------------------------------------------------|-------|

| Thermal Resistance                                    |       |

| Package Outlines                                      |       |

| 144-Pin Plastic Thin Quad Flat Pack (TQFP) – Wirebond |       |

| 208-Pin Plastic Quad Flat Pack (PQFP) – Wirebond      |       |

| 240-Pin Plastic Quad Flat Pack (PQFP)                 |       |

| 256-Pin FineLine Ball-Grid Array, Option 2 – Wirebond | 15–11 |

| 484-Pin FineLine BGA, Option 3 – Wirebond             | 15–13 |

| 484-Pin Ultra FineLine BGA – Wirebond                 | 15–15 |

| 672-Pin FineLine BGA Package, Option 3 – Wirebond     |       |

| 896-Pin FineLine BGA Package – Ŵirebond               | 15–19 |

|                                                       |       |

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, M4K memory blocks, embedded multipliers, and IOEs. C16 column interconnects drive to other row and column interconnects at every fourth LAB. C16 column interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly. C16 interconnects can drive R24, R4, C16, and C4 interconnects.

## **Device Routing**

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (for example, M4K memory, embedded multiplier, or PLL) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB.

Table 2–1 shows the Cyclone II device's routing scheme.

| Table 2–1. Cy               | clone II       | one II Device Routing Scheme (Part 1 of 2) |                          |                 |                  |                 |                  |    |               |                     |     |            |         |

|-----------------------------|----------------|--------------------------------------------|--------------------------|-----------------|------------------|-----------------|------------------|----|---------------|---------------------|-----|------------|---------|

|                             |                | Destination                                |                          |                 |                  |                 |                  |    |               |                     |     |            |         |

| Source                      | Register Chain | Local Interconnect                         | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | 31 | M4K RAM Block | Embedded Multiplier | ٦٦d | Column IOE | Row IOE |

| Register<br>Chain           |                |                                            |                          |                 |                  |                 |                  | ~  |               |                     |     |            |         |

| Local<br>Interconnect       |                |                                            |                          |                 |                  |                 |                  | ~  | ~             | ~                   | ~   | ~          | ~       |

| Direct Link<br>Interconnect |                | ~                                          |                          |                 |                  |                 |                  |    |               |                     |     |            |         |

| R4<br>Interconnect          |                | ~                                          |                          | ~               | ~                | ~               | ~                |    |               |                     |     |            |         |

| R24<br>Interconnect         |                |                                            |                          | ~               | ~                | ~               | ~                |    |               |                     |     |            |         |

| C4<br>Interconnect          |                | ~                                          |                          | ~               | ~                | ~               | ~                |    |               |                     |     |            |         |

| C16<br>Interconnect         |                |                                            |                          | ~               | ~                | ~               | ~                |    |               |                     |     |            |         |

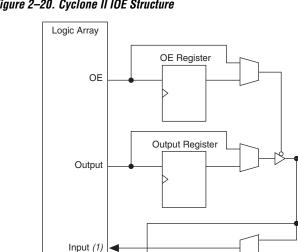

Figure 2–20. Cyclone II IOE Structure

#### Note to Figure 2-20:

(1)There are two paths available for combinational or registered inputs to the logic array. Each path contains a unique programmable delay chain.

Input Register

The IOEs are located in I/O blocks around the periphery of the Cyclone II device. There are up to five IOEs per row I/O block and up to four IOEs per column I/O block (column I/O blocks span two columns). The row I/O blocks drive row, column (only C4 interconnects), or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–21 shows how a row I/O block connects to the logic array. Figure 2–22 shows how a column I/O block connects to the logic array.

$\bigcirc$

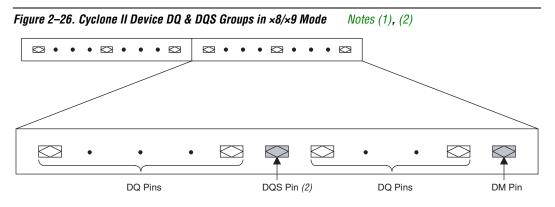

#### Notes to Figure 2–26:

- (1) Each DQ group consists of a DQS pin, DM pin, and up to nine DQ pins.

- (2) This is an idealized pin layout. For actual pin layout, refer to the pin table.

Cyclone II devices support the data strobe or read clock signal (DQS) used in DDR and DDR2 SDRAM. Cyclone II devices can use either bidirectional data strobes or unidirectional read clocks. The dedicated external memory interface in Cyclone II devices also includes programmable delay circuitry that can shift the incoming DQS signals to center align the DQS signals within the data window.

The DQS signal is usually associated with a group of data (DQ) pins. The phase-shifted DQS signals drive the global clock network, which is used to clock the DQ signals on internal LE registers.

Table 2–15 shows the number of DQ pin groups per device.

| Table 2–15. | Cyclone II DQS & DQ Bus | Mode Support (P        | Part 1 of 2) No                 | te (1)                  |                                  |

|-------------|-------------------------|------------------------|---------------------------------|-------------------------|----------------------------------|

| Device      | Package                 | Number of ×8<br>Groups | Number of ×9<br>Groups (5), (6) | Number of ×16<br>Groups | Number of ×18<br>Groups (5), (6) |

| EP2C5       | 144-pin TQFP (2)        | 3                      | 3                               | 0                       | 0                                |

|             | 208-pin PQFP            | 7 (3)                  | 4                               | 3                       | 3                                |

| EP2C8       | 144-pin TQFP (2)        | 3                      | 3                               | 0                       | 0                                |

|             | 208-pin PQFP            | 7 (3)                  | 4                               | 3                       | 3                                |

|             | 256-pin FineLine BGA®   | 8 (3)                  | 4                               | 4                       | 4                                |

| EP2C15      | 256-pin FineLine BGA    | 8                      | 4                               | 4                       | 4                                |

|             | 484-pin FineLine BGA    | 16 (4)                 | 8                               | 8                       | 8                                |

| EP2C20      | 256-pin FineLine BGA    | 8                      | 4                               | 4                       | 4                                |

|             | 484-pin FineLine BGA    | 16 (4)                 | 8                               | 8                       | 8                                |

## **Slew Rate Control**

Slew rate control is performed by using programmable output drive strength.

## **Bus Hold**

Each Cyclone II device user I/O pin provides an optional bus-hold feature. The bus-hold circuitry can hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not necessary to hold a signal level when the bus is tri-stated.

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. You can select this feature individually for each I/O pin. The bus-hold output drives no higher than  $V_{\rm CCIO}$  to prevent overdriving signals.

If the bus-hold feature is enabled, the device cannot use the programmable pull-up option. Disable the bus-hold feature when the I/O pin is configured for differential signals. Bus hold circuitry is not available on the dedicated clock pins.

The bus-hold circuitry is only active after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

The bus-hold circuitry uses a resistor with a nominal resistance ( $R_{BH}$ ) of approximately 7 k $\Omega$  to pull the signal level to the last-driven state. Refer to the *DC Characteristics & Timing Specifications* chapter in Volume 1 of the *Cyclone II Device Handbook* for the specific sustaining current for each  $V_{CCIO}$  voltage level driven through the resistor and overdrive current used to identify the next driven input level.

## Programmable Pull-Up Resistor

Each Cyclone II device I/O pin provides an optional programmable pull-up resistor during user mode. If you enable this feature for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) holds the output to the V<sub>CCIO</sub> level of the output pin's bank.

If the programmable pull-up is enabled, the device cannot use the bus-hold feature. The programmable pull-up resistors are not supported on the dedicated configuration, JTAG, and dedicated clock pins.

| Table 2–17. Cyclone II Supp  | Table 2–17. Cyclone II Supported I/O Standards & Constraints (Part 2 of 2) |                                     |        |                          |                  |               |                       |                  |

|------------------------------|----------------------------------------------------------------------------|-------------------------------------|--------|--------------------------|------------------|---------------|-----------------------|------------------|

| I/O Standard                 | Tuno                                                                       | ACCIO LEAGI                         |        | Top & Bottom<br>I/O Pins |                  | Side I/O Pins |                       |                  |

| i/O Stanuaru                 | Туре                                                                       | Input                               | Output | CLK,<br>DQS              | User I/O<br>Pins | CLK,<br>DQS   | PLL_OUT               | User I/O<br>Pins |

| Differential HSTL-15 class I | Pseudo                                                                     | (5)                                 | 1.5 V  |                          |                  |               | ✓ (7)                 |                  |

| or class II                  | differential (4)                                                           | 1.5 V                               | (5)    | ✓<br>(6)                 |                  | ✓<br>(6)      |                       |                  |

| Differential HSTL-18 class I | Pseudo                                                                     | (5)                                 | 1.8 V  |                          |                  |               | <ul><li>(7)</li></ul> |                  |

| or class II                  | differential (4)                                                           | 1.8 V                               | (5)    | ✓<br>(6)                 |                  | ✓<br>(6)      |                       |                  |

| LVDS                         | Differential                                                               | 2.5 V                               | 2.5 V  | $\checkmark$             | $\checkmark$     | $\checkmark$  | ~                     | $\checkmark$     |

| RSDS and mini-LVDS (8)       | Differential                                                               | (5)                                 | 2.5 V  |                          | $\checkmark$     |               | ~                     | $\checkmark$     |

| LVPECL (9)                   | Differential                                                               | 3.3 V/<br>2.5 V/<br>1.8 V/<br>1.5 V | (5)    | >                        |                  | ~             |                       |                  |

Notes to Table 2–17:

- To drive inputs higher than V<sub>CCIO</sub> but less than 4.0 V, disable the PCI clamping diode and turn on the Allow LVTTL and LVCMOS input levels to overdrive input buffer option in the Quartus II software.

- (2) These pins support SSTL-18 class II and 1.8- and 1.5-V HSTL class II inputs.

- (3) PCI-X does not meet the IV curve requirement at the linear region. PCI-clamp diode is not available on top and bottom I/O pins.

- (4) Pseudo-differential HSTL and SSTL outputs use two single-ended outputs with the second output programmed as inverted. Pseudo-differential HSTL and SSTL inputs treat differential inputs as two single-ended HSTL and SSTL inputs and only decode one of them.

- (5) This I/O standard is not supported on these I/O pins.

- (6) This I/O standard is only supported on the dedicated clock pins.

- (7) PLL\_OUT does not support differential SSTL-18 class II and differential 1.8 and 1.5-V HSTL class II.

- (8) mini-LVDS and RSDS are only supported on output pins.

- (9) LVPECL is only supported on clock inputs.

For more information on Cyclone II supported I/O standards, see the *Selectable I/O Standards in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

## **High-Speed Differential Interfaces**

Cyclone II devices can transmit and receive data through LVDS signals at a data rate of up to 640 Mbps and 805 Mbps, respectively. For the LVDS transmitter and receiver, the Cyclone II device's input and output pins support serialization and deserialization through internal logic.

|                          | SRAM configuration elements allow Cyclone II devices to be<br>reconfigured in-circuit by loading new configuration data into the device.<br>With real-time reconfiguration, the device is forced into command mode<br>with the nCONFIG pin. The configuration process loads different<br>configuration data, reinitializes the device, and resumes user-mode<br>operation. You can perform in-field upgrades by distributing new<br>configuration files within the system or remotely. |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | A built-in weak pull-up resistor pulls all user I/O pins to $V_{\mbox{CCIO}}$ before and during device configuration.                                                                                                                                                                                                                                                                                                                                                                  |

|                          | The configuration pins support 1.5-V/1.8-V or 2.5-V/3.3-V I/O standards. The voltage level of the configuration output pins is determined by the $V_{CCIO}$ of the bank where the pins reside. The bank $V_{CCIO}$ selects whether the configuration inputs are 1.5-V, 1.8-V, 2.5-V, or 3.3-V compatible.                                                                                                                                                                              |

| Configuration<br>Schemes | You can load the configuration data for a Cyclone II device with one of<br>three configuration schemes (see Table 3–4), chosen on the basis of the<br>target application. You can use a configuration device, intelligent<br>controller, or the JTAG port to configure a Cyclone II device. A low-cost<br>configuration device can automatically configure a Cyclone II device at<br>system power-up.                                                                                  |

|                          | Multiple Cyclone II devices can be configured in any of the three configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.                                                                                                                                                                                                                                                                                       |

| Table 3–4. Data Sources for Configuration |                                                                                                                                          |  |  |  |  |  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Configuration<br>Scheme                   | Data Source                                                                                                                              |  |  |  |  |  |

| Active serial (AS)                        | ow-cost serial configuration device                                                                                                      |  |  |  |  |  |

| Passive serial (PS)                       | Enhanced or EPC2 configuration device, MasterBlaster, ByteBlasterMV, ByteBlaster II or USB Blaster download cable, or serial data source |  |  |  |  |  |

| JTAG                                      | MasterBlaster, ByteBlasterMV, ByteBlaster II or USB Blaster download cable or a microprocessor with a Jam or JBC file                    |  |  |  |  |  |

For more information on configuration, see the *Configuring Cyclone II Devices* chapter of the *Cyclone II Handbook, Volume 2*.

|              | Deiter            | Parameter        | Fast Co                   | -6              | 7              | -7                    | -8                    |                |      |

|--------------|-------------------|------------------|---------------------------|-----------------|----------------|-----------------------|-----------------------|----------------|------|

| I/O Standard | Drive<br>Strength |                  | Industrial/<br>Automotive | Commer<br>-cial | Speed<br>Grade | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | Speed<br>Grade | Unit |

| 2.5V         | 4 mA              | t <sub>OP</sub>  | 1208                      | 1267            | 2478           | 2614                  | 2743                  | 2750           | ps   |

|              |                   | t <sub>DIP</sub> | 1340                      | 1406            | 2648           | 2808                  | 2969                  | 2969           | ps   |

|              | 8 mA              | t <sub>OP</sub>  | 1190                      | 1248            | 2307           | 2434                  | 2554                  | 2561           | ps   |

|              |                   | t <sub>DIP</sub> | 1322                      | 1387            | 2477           | 2628                  | 2780                  | 2780           | ps   |

|              | 12 mA             | t <sub>OP</sub>  | 1154                      | 1210            | 2192           | 2314                  | 2430                  | 2437           | ps   |

|              |                   | t <sub>DIP</sub> | 1286                      | 1349            | 2362           | 2508                  | 2656                  | 2656           | ps   |

|              | 16 mA             | t <sub>OP</sub>  | 1140                      | 1195            | 2152           | 2263                  | 2375                  | 2382           | ps   |

|              | (1)               | t <sub>DIP</sub> | 1272                      | 1334            | 2322           | 2457                  | 2601                  | 2601           | ps   |

| 1.8V         | 2 mA              | t <sub>OP</sub>  | 1682                      | 1765            | 3988           | 4279                  | 4563                  | 4570           | ps   |

|              |                   | t <sub>DIP</sub> | 1814                      | 1904            | 4158           | 4473                  | 4789                  | 4789           | ps   |

|              | 4 mA              | t <sub>OP</sub>  | 1567                      | 1644            | 3301           | 3538                  | 3768                  | 3775           | ps   |

|              | 6 mA              | t <sub>DIP</sub> | 1699                      | 1783            | 3471           | 3732                  | 3994                  | 3994           | ps   |

|              |                   | t <sub>OP</sub>  | 1475                      | 1547            | 2993           | 3195                  | 3391                  | 3398           | ps   |

|              |                   | t <sub>DIP</sub> | 1607                      | 1686            | 3163           | 3389                  | 3617                  | 3617           | ps   |

|              | 8 mA              | t <sub>OP</sub>  | 1451                      | 1522            | 2882           | 3074                  | 3259                  | 3266           | ps   |

|              |                   | t <sub>DIP</sub> | 1583                      | 1661            | 3052           | 3268                  | 3485                  | 3485           | ps   |

|              | 10 mA             | t <sub>OP</sub>  | 1438                      | 1508            | 2853           | 3041                  | 3223                  | 3230           | ps   |

|              |                   | t <sub>DIP</sub> | 1570                      | 1647            | 3023           | 3235                  | 3449                  | 3449           | ps   |

|              | 12 mA             | t <sub>OP</sub>  | 1438                      | 1508            | 2853           | 3041                  | 3223                  | 3230           | ps   |

|              | (1)               | t <sub>DIP</sub> | 1570                      | 1647            | 3023           | 3235                  | 3449                  | 3449           | ps   |

| 1.5V         | 2 mA              | t <sub>OP</sub>  | 2083                      | 2186            | 4477           | 4870                  | 5256                  | 5263           | ps   |

|              |                   | t <sub>DIP</sub> | 2215                      | 2325            | 4647           | 5064                  | 5482                  | 5482           | ps   |

|              | 4 mA              | t <sub>OP</sub>  | 1793                      | 1881            | 3649           | 3965                  | 4274                  | 4281           | ps   |

|              |                   | t <sub>DIP</sub> | 1925                      | 2020            | 3819           | 4159                  | 4500                  | 4500           | ps   |

|              | 6 mA              | t <sub>OP</sub>  | 1770                      | 1857            | 3527           | 3823                  | 4112                  | 4119           | ps   |

|              |                   | t <sub>DIP</sub> | 1902                      | 1996            | 3697           | 4017                  | 4338                  | 4338           | ps   |

|              | 8 mA              | t <sub>OP</sub>  | 1703                      | 1787            | 3537           | 3827                  | 4111                  | 4118           | ps   |

|              | (1)               | t <sub>DIP</sub> | 1835                      | 1926            | 3707           | 4021                  | 4337                  | 4337           | ps   |

5–38

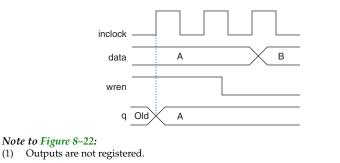

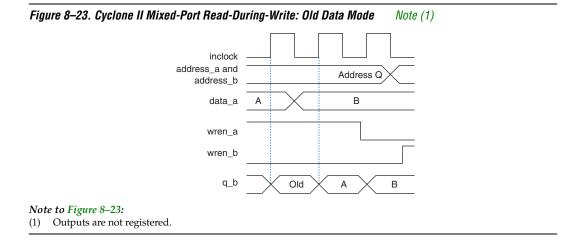

#### Mixed-Port Read-During-Write Mode

This mode applies to a RAM in simple or true dual-port mode, which has one port reading and the other port writing to the same address location with the same clock.

In this mode, you also have two output choices: old data or don't care. In Old Data Mode, a read-during-write operation to different ports causes the RAM outputs to reflect the old data at that address location. In Don't Care Mode, the same operation results in a "don't care" or unknown value on the RAM outputs.

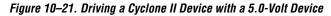

If  $V_{CCIO}$  is between 3.0 V and 3.6 V and the PCI clamping diode is enabled, the voltage at point B in Figure 10–21 is 4.3 V or less. To limit large current draw from the 5.0-V device,  $R_2$  should be small enough for a fast signal rise time and large enough so that it does not violate the high-level output current ( $I_{OH}$ ) specifications of the devices driving the trace. The PCI clamping diode in the Cyclone II device can support 25 mA of current.

To compute the required value of  $R_2$ , first calculate the model of the pull-up transistors on the 5.0-V device. This output resistor ( $R_1$ ) can be modeled by dividing the 5.0-V device supply voltage ( $V_{CC}$ ) by the  $I_{OH}$ :  $R_1 = V_{CC}/I_{OH}$ .

Figure 10–22 shows an example of typical output drive characteristics of a 5.0-V device.

| November 2005<br>v2.1 | <ul> <li>Updated Tables 10–2 and 10–3.</li> <li>Added PCI Express information.</li> <li>Updated Table 10–6.</li> </ul> | _ |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|---|

| July 2005 v2.0        | Updated Table 10–1.                                                                                                    | — |

| November 2004<br>v1.1 | Updated Table 10–7.                                                                                                    | _ |

| June 2004 v1.0        | Added document to the Cyclone II Device Handbook.                                                                      | _ |

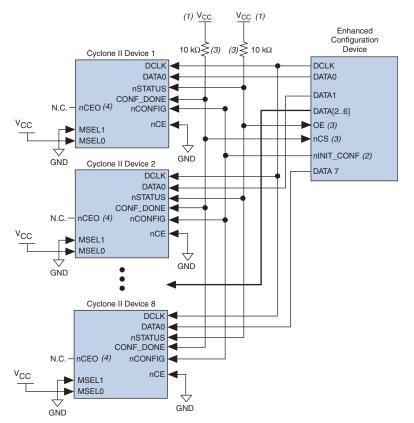

Figure 13–15. Concurrent PS Configuration of Multiple Devices Using an Enhanced Configuration Device

#### Notes to Table 13–15:

- (1) The pull-up resistor should be connected to the same supply voltage as the configuration device.

- (2) The nINIT\_CONF pin is available on enhanced configuration devices and has an internal pull-up resistor that is always active, meaning an external pull-up resistor should not be used on the nINIT\_CONF to nCONFIG line. The nINIT\_CONF pin does not need to be connected if its functionality is not used. If nINIT\_CONF is not used, nCONFIG must be pulled to V<sub>CC</sub> either directly or through a resistor (if reconfiguration is required, a resistor is necessary).

- (3) The enhanced configuration devices' OE and nCS pins have internal programmable pull-up resistors. If internal pull-up resistors are used, external pull-up resistors should not be used on these pins. The internal pull-up resistors are used by default in the Quartus II software. To turn off the internal pull-up resistors, check the Disable nCS and OE pull-ups on configuration device option when generating programming files.

- (4) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

The Quartus II software only allows you to set *n* to 1, 2, 4, or 8. However, you can use these modes to configure any number of devices from 1 to 8. For example, if you configure three FPGAs, you would use the 4-bit PS mode. For the DATA0, DATA1, and DATA2 lines, the corresponding SOF data is transmitted from the configuration device to the FPGA. For

feature. To use this feature successfully, set the MSEL[1..0] pins of the master Cyclone II device to select the AS configuration scheme or fast AS configuration scheme (see Table 13–1).

The Quartus II software version 4.1 and higher supports serial configuration device ISP through an FPGA JTAG interface using a JIC file.

The serial configuration device in-system programming through the Cyclone II JTAG interface has three stages, which are described in the following sections.

#### Loading the Serial Flash Loader Design

The serial flash loader design is a design inside the Cyclone II device that bridges the JTAG interface and AS interface inside the Cyclone II device using glue logic.

The intelligent host uses the JTAG interface to configure the master Cyclone II device with a serial flash loader design. The serial flash loader design allows the master Cyclone II device to control the access of four serial configuration device pins, also known as the Active Serial Memory Interface (ASMI) pins, through the JTAG interface. The ASMI pins are the serial clock input (DCLK), serial data output (DATA), AS data input (ASDI), and an active-low chip select (nCS) pins.

If you configure a master Cyclone II device with a serial flash loader design, the master Cyclone II device can enter user mode even though the slave devices in the multiple device chain are not being configured. The master Cyclone II device can enter user mode with a serial flash loader design even though the CONF\_DONE signal is externally held low by the other slave devices in chain. Figure 13–25 shows the JTAG configuration of a single Cyclone II device with a serial flash loader design.

Table 13–12 describes the optional configuration pins. If these optional configuration pins are not enabled in the Quartus II software, they are available as general-purpose user I/O pins. Therefore during configuration, these pins function as user I/O pins and are tri-stated with weak pull-up resistors.

| Pin Name  | User Mode                                        | Pin Type              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|--------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKUSR    | N/A if option is<br>on. I/O if option<br>is off. | Input                 | This is an optional user-supplied clock input that<br>synchronizes the initialization of one or more devices. This<br>pin is enabled by turning on the <b>Enable user-supplied</b><br><b>start-up clock (CLKUSR)</b> option in the Quartus II software                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| INIT_DONE | N/A if option is<br>on. I/O if option<br>is off. | Output open-<br>drain | This is a status pin that can be used to indicate when the device has initialized and is in user mode. When nCONFIG is low and during the beginning of configuration, the INIT_DONE pin is tri-stated and pulled high due to an external 10-k $\Omega$ pull-up resistor. Once the option bit to enable INIT_DONE is programmed into the device (during the first frame of configuration data), the INIT_DONE pin goes low. When initialization is complete, the INIT_DONE pin is released and pulled high and the FPGA enters user mode. Thus, the monitoring circuitry must be able to detect a low-to-high transition. This pin is enabled by turning on the <b>Enable INIT_DONE output</b> option in the Quartus II software. |

| DEV_OE    | N/A if option is<br>on. I/O if option<br>is off. | Input                 | Optional pin that allows the user to override all tri-states on<br>the device. When this pin is driven low, all I/O pins are tri-<br>stated. When this pin is driven high, all I/O pins behave as<br>programmed. This pin is enabled by turning on the <b>Enable</b><br><b>device-wide output enable (DEV_OE)</b> option in the<br>Quartus II software.                                                                                                                                                                                                                                                                                                                                                                          |

| DEV_CLRn  | N/A if option is<br>on. I/O if option<br>is off. | Input                 | Optional pin that allows you to override all clears on all device registers. When this pin is driven low, all registers are cleared. When this pin is driven high, all registers behave as programmed. This pin is enabled by turning on the <b>Enable device-wide reset (DEV_CLRn)</b> option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 13–13 describes the dedicated JTAG pins. JTAG pins must be kept stable before and during configuration to prevent accidental loading of JTAG instructions. The TCK pin has a weak internal pull-down resistor and the TDI and TMS JTAG input pins have weak internal pull-up resistors.

| Pin Name | User Mode | Pin Type | Description                                                                                                                                                                                                                                                                                 |

|----------|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDI      | N/A       | Input    | Serial input pin for instructions as well as test and programming data. Data is shifted in on the rising edge of TCK.                                                                                                                                                                       |

|          |           |          | If the JTAG interface is not required on the board, the JTAG circuitry can be disabled by connecting this pin to $V_{\rm CC}.$                                                                                                                                                              |

|          |           |          | The input buffer on this pin supports hysteresis using Schmitt trigger circuitry.                                                                                                                                                                                                           |

| TDO      | N/A       | Output   | Serial data output pin for instructions as well as test and<br>programming data. Data is shifted out on the falling edge of<br>TCK. The pin is tri-stated if data is not being shifted out of the<br>device.                                                                                |

|          |           |          | If the JTAG interface is not required on the board, the JTAG circuitry can be disabled by leaving this pin unconnected.                                                                                                                                                                     |

| TMS      | N/A       | Input    | Input pin that provides the control signal to determine the transitions of the TAP controller state machine. Transitions within the state machine occur on the rising edge of TCK. Therefore, TMS must be set up before the rising edge of TCK. TMS is evaluated on the rising edge of TCK. |

|          |           |          | If the JTAG interface is not required on the board, the JTAG circuitry can be disabled by connecting this pin to $V_{\rm CC}.$                                                                                                                                                              |

|          |           |          | The input buffer on this pin supports hysteresis using Schmitt trigger circuitry.                                                                                                                                                                                                           |

| TCK      | N/A       | Input    | The clock input to the BST circuitry. Some operations occur at the rising edge, while others occur at the falling edge.                                                                                                                                                                     |

|          |           |          | If the JTAG interface is not required on the board, the JTAG circuitry can be disabled by connecting this pin to GND.                                                                                                                                                                       |

|          |           |          | The input buffer on this pin supports hysteresis using Schmitt trigger circuitry.                                                                                                                                                                                                           |

## Conclusion

Cyclone II devices can be configured in AS, PS or JTAG configuration schemes to fit your system's need. The AS configuration scheme supported by Cyclone II devices can now operate at a higher DCLK

This chapter discusses how to use the IEEE Std. 1149.1 BST circuitry in Cyclone<sup>™</sup> II devices, including:

- IEEE Std. 1149.1 BST architecture

- IEEE Std. 1149.1 boundary-scan register

- IEEE Std. 1149.1 BST operation control

- I/O voltage support in JTAG chain

- Using IEEE Std. 1149.1 BST circuitry

- Disabling IEEE Std. 1149.1 BST circuitry

- Guidelines for IEEE Std. 1149.1 boundary-scan testing

- Boundary-Scan Description Language (BSDL) support

In addition to BST, you can use the IEEE Std. 1149.1 controller for Cyclone II device in-circuit reconfiguration (ICR). However, this chapter only discusses the BST feature of the IEEE Std. 1149.1 circuitry.

For information on configuring Cyclone II devices via the IEEE Std. 1149.1 circuitry, see the *Configuring Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

# IEEE Std. 1149.1 BST Architecture

A Cyclone II device operating in IEEE Std. 1149.1 BST mode uses four required pins, TDI, TDO, TMS and TCK. The optional TRST pin is not available in Cyclone II devices. TDI and TMS pins have weak internal pull-up resistors while TCK has weak internal pull-down resistors. All user I/O pins are tri-stated during JTAG configuration. Table 14–1 summarizes the functions of each of these pins.

| Pin | Description      | Function                                                                                                                                                                                                                                                                                                                                                     |

|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDI | Test data input  | Serial input pin for instructions as well as test and programming data. Signal applied to $\texttt{TDI}$ is expected to change state at the falling edge of $\texttt{TCK}$ . Data is shifted in on the rising edge of $\texttt{TCK}$ .                                                                                                                       |

| TDO | Test data output | Serial data output pin for instructions as well as test and programming data. Data is shifted out on the falling edge of $TCK$ . The pin is tri-stated if data is not being shifted out of the device.                                                                                                                                                       |

| TMS | Test mode select | Input pin that provides the control signal to determine the transitions of the TAP controller state machine. Transitions within the state machine occur at the rising edge of TCK. Therefore, TMS must be set up before the rising edge of TCK. TMS is evaluated on the rising edge of TCK. During non-JTAG operation, TMS is recommended to be driven high. |

| TCK | Test clock input | The clock input to the BST circuitry. Some operations occur at the rising edge, while others occur at the falling edge. The clock input waveform should have a 50% duty cycle.                                                                                                                                                                               |

EXTEST selects data differently than SAMPLE/PRELOAD. EXTEST chooses data from the update registers as the source of the output and output enable signals. Once the EXTEST instruction code is entered, the multiplexers select the update register data. Thus, data stored in these registers from a previous EXTEST or SAMPLE/PRELOAD test cycle can be forced onto the pin signals. In the capture phase, the results of this test data are stored in the capture registers, then shifted out of TDO during the shift phase. New test data can then be stored in the update registers during the update phase.

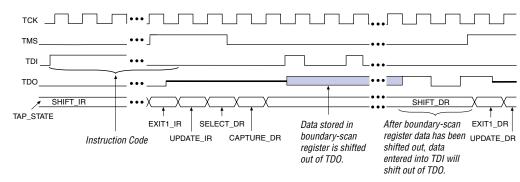

The EXTEST waveform diagram in Figure 14–11 resembles the SAMPLE/PRELOAD waveform diagram, except for the instruction code. The data shifted out of TDO consists of the data that was present in the capture registers after the capture phase. New test data shifted into the TDI pin appears at the TDO pin after being clocked through the entire boundary-scan register.

Figure 14–11. EXTEST Shift Data Register Waveforms

### **BYPASS Instruction Mode**

The BYPASS mode is activated when an instruction code of all 1's is loaded in the instruction register. The waveforms in Figure 14–12 show how scan data passes through a device once the TAP controller is in the SHIFT\_DR state. In this state, data signals are clocked into the bypass register from TDI on the rising edge of TCK and out of TDO on the falling edge of the same clock pulse.

# Section VII. PCB Layout Guidelines

This section provides information for board layout designers to successfully layout their boards for Cyclone<sup>®</sup> II devices. The chapters in this section contain the required PCB layout guidelines and package specifications.

This section includes the following chapters:

Chapter 15, Package Information for Cyclone II Devices

## **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.