Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 1172                                                    |

| Number of Logic Elements/Cells | 18752                                                   |

| Total RAM Bits                 | 239616                                                  |

| Number of I/O                  | 315                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 484-BGA                                                 |

| Supplier Device Package        | 484-FBGA (23x23)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c20f484c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Internal Timing                                                                                                                                                                                                                                                                                                                                                                                                         | 5–18                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Cyclone II Clock Timing Parameters                                                                                                                                                                                                                                                                                                                                                                                      |                                                 |

| Clock Network Skew Adders                                                                                                                                                                                                                                                                                                                                                                                               |                                                 |

| IOE Programmable Delay                                                                                                                                                                                                                                                                                                                                                                                                  | 5–30                                            |

| Default Capacitive Loading of Different I/O Standards                                                                                                                                                                                                                                                                                                                                                                   | 5–31                                            |

| I/O Delays                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

| Maximum Input and Output Clock Rate                                                                                                                                                                                                                                                                                                                                                                                     |                                                 |

| High Speed I/O Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |

| External Memory Interface Specifications                                                                                                                                                                                                                                                                                                                                                                                | 5–63                                            |

| JTAG Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

| PLL Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                               | 5–66                                            |

| Duty Cycle Distortion                                                                                                                                                                                                                                                                                                                                                                                                   |                                                 |

| DCD Measurement Techniques                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

| Referenced Documents                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                               |                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |

| Chapter 6. Reference & Ordering Information                                                                                                                                                                                                                                                                                                                                                                             |                                                 |

| Software                                                                                                                                                                                                                                                                                                                                                                                                                | 6–1                                             |

| Device Pin-Outs                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |

| Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                               |                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |

| Section II Clack Management                                                                                                                                                                                                                                                                                                                                                                                             |                                                 |

| Section II. Clock Management Revision History                                                                                                                                                                                                                                                                                                                                                                           | 6–1                                             |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 6–1                                             |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 6–1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices                                                                                                                                                                                                                                                                                                                                                                 |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction                                                                                                                                                                                                                                                                                                                                                   | 7–1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction  Cyclone II PLL Hardware Overview                                                                                                                                                                                                                                                                                                                 | 7–1<br>7–2                                      |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 7–1<br>7–2<br>7–6                               |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 7–1<br>7–2<br>7–6                               |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        |                                                 |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 7–1<br>7–2<br>7–10<br>7–10<br>7–10<br>7–11      |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode                                                                                                                                                                                                       | 7–17–27–67–107–117–12                           |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        |                                                 |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction  Cyclone II PLL Hardware Overview  PLL Reference Clock Generation  Clock Feedback Modes  Normal Mode  Zero Delay Buffer Mode  No Compensation Mode  Source-Synchronous Mode  Hardware Features  Clock Multiplication & Division                                                                                                                   |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle                                                                                                     |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation                                                                       |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals                                                       | 7-1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover                               | 7-1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover Clocking                      | 7-1 7-2 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover Clocking Global Clock Network | 7-1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover Clocking                      | 7-1 7-2 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 |

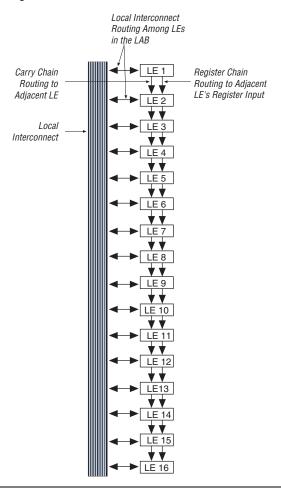

Figure 2-9. Register Chain Interconnects

The C4 interconnects span four LABs, M4K blocks, or embedded multipliers up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–10 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including PLLs, M4K memory blocks, embedded multiplier blocks, and column and row IOEs. For LAB interconnection, a primary LAB or its LAB neighbor (see Figure 2–10) can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

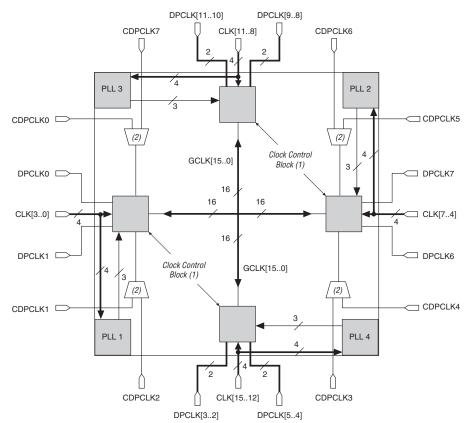

Figure 2-12. EP2C15 & Larger PLL, CLK[], DPCLK[] & Clock Control Block Locations

#### Notes to Figure 2–12:

- (1) There are four clock control blocks on each side.

- (2) Only one of the corner CDPCLK pins in each corner can feed the clock control block at a time. The other CDPCLK pins can be used as general-purpose I/O pins.

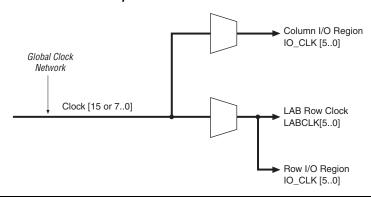

#### **Global Clock Network Distribution**

Cyclone II devices contains 16 global clock networks. The device uses multiplexers with these clocks to form six-bit buses to drive column IOE clocks, LAB row clocks, or row IOE clocks (see Figure 2–14). Another multiplexer at the LAB level selects two of the six LAB row clocks to feed the LE registers within the LAB.

Figure 2-14. Global Clock Network Multiplexers

LAB row clocks can feed LEs, M4K memory blocks, and embedded multipliers. The LAB row clocks also extend to the row I/O clock regions.

IOE clocks are associated with row or column block regions. Only six global clock resources feed to these row and column regions. Figure 2–15 shows the I/O clock regions.

Cyclone II devices also use the JTAG port to monitor the logic operation of the device with the SignalTap $^{\$}$  II embedded logic analyzer. Cyclone II devices support the JTAG instructions shown in Table 3–1.

| Table 3–1. Cyclone | II JTAG Instructions | (Part 1 of 2)                                                                                                                                                                                                                                                                   |

|--------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Instruction   | Instruction Code     | Description                                                                                                                                                                                                                                                                     |

| SAMPLE/PRELOAD     | 00 0000 0101         | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap II embedded logic analyzer.                                         |

| EXTEST (1)         | 00 0000 1111         | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                                                             |

| BYPASS             | 11 1111 1111         | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                                                     |

| USERCODE           | 00 0000 0111         | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                       |

| IDCODE             | 00 0000 0110         | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                                                           |

| HIGHZ (1)          | 00 0000 1011         | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                              |

| CLAMP (1)          | 00 0000 1010         | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register. |

| ICR instructions   |                      | Used when configuring a Cyclone II device via the JTAG port with a USB Blaster <sup>™</sup> , ByteBlaster <sup>™</sup> II, MasterBlaster <sup>™</sup> or ByteBlasterMV <sup>™</sup> download cable, or when using a Jam File or JBC File via an embedded processor.             |

| PULSE_NCONFIG      | 00 0000 0001         | Emulates pulsing the nCONFIG pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                     |

the power supply can provide current to the device's  $V_{CC}$  and ground planes. This condition can lead to latch-up and cause a low-impedance path from  $V_{CC}$  to ground within the device. As a result, the device extends a large amount of current, possibly causing electrical damage.

Altera has ensured by design of the I/O buffers and hot-socketing circuitry, that Cyclone II devices are immune to latch-up during hot socketing.

# Hot-Socketing Feature Implementation in Cyclone II Devices

The hot-socketing feature turns off the output buffer during power up (either  $V_{\rm CCINT}$  or  $V_{\rm CCIO}$  supplies) or power down. The hot-socket circuit generates an internal HOTSCKT signal when either  $V_{\rm CCINT}$  or  $V_{\rm CCIO}$  is below the threshold voltage. Designs cannot use the HOTSCKT signal for other purposes. The HOTSCKT signal cuts off the output buffer to ensure that no DC current (except for weak pull-up leakage current) leaks through the pin. When  $V_{\rm CC}$  ramps up slowly,  $V_{\rm CC}$  is still relatively low even after the internal POR signal (not available to the FPGA fabric used by customer designs) is released and the configuration is finished. The CONF\_DONE, nCEO, and nSTATUS pins fail to respond, as the output buffer cannot drive out because the hot-socketing circuitry keeps the I/O pins tristated at this low  $V_{\rm CC}$  voltage. Therefore, the hot-socketing circuit has been removed on these configuration output or bidirectional pins to ensure that they are able to operate during configuration. These pins are expected to drive out during power-up and power-down sequences.

Each I/O pin has the circuitry shown in Figure 4–1.

| Table 5–3. DC Characteristics for User I/O, Dual-Purpose, and Dedicated Pins (Part 1 of 2) |                                    |                                                                      |                                 |         |          |                   |       |     |   |

|--------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------|---------------------------------|---------|----------|-------------------|-------|-----|---|

| Symbol                                                                                     | Parameter                          | Cond                                                                 | itions                          | Minimum | Typical  | Maximum           | Unit  |     |   |

| V <sub>IN</sub>                                                                            | Input voltage                      | (1)                                                                  | , (2)                           | -0.5    | _        | 4.0               | V     |     |   |

| l <sub>i</sub>                                                                             | Input pin leakage current          | $V_{IN} = V_{CCIOmax} t$                                             | o 0 V (3)                       | -10     | _        | 10                | μΑ    |     |   |

| V <sub>OUT</sub>                                                                           | Output voltage                     | -                                                                    | _                               | 0       | _        | V <sub>CCIO</sub> | V     |     |   |

| l <sub>oz</sub>                                                                            | Tri-stated I/O pin leakage current | $V_{OUT} = V_{CCIOmax}$                                              | to 0 V (3)                      | -10     | _        | 10                | μΑ    |     |   |

| I <sub>CCINTO</sub>                                                                        | V <sub>CCINT</sub> supply          | V <sub>IN</sub> = ground,                                            | EP2C5/A                         | _       | 0.010    | (4)               | Α     |     |   |

|                                                                                            | current (standby)                  | no load, no toggling inputs $T_J = 25^{\circ} C$ Nominal $V_{CCINT}$ | EP2C8/A                         | _       | 0.017    | (4)               | Α     |     |   |

|                                                                                            |                                    |                                                                      | $T_J = 25^{\circ} C$<br>Nominal | EP2C15A | _        | 0.037             | (4)   | Α   |   |

|                                                                                            |                                    |                                                                      |                                 |         | EP2C20/A | _                 | 0.037 | (4) | Α |

|                                                                                            |                                    |                                                                      |                                 | EP2C35  | _        | 0.066             | (4)   | Α   |   |

|                                                                                            |                                    |                                                                      | EP2C50                          | _       | 0.101    | (4)               | Α     |     |   |

|                                                                                            |                                    |                                                                      | EP2C70                          | _       | 0.141    | (4)               | Α     |     |   |

| I <sub>CCIO0</sub>                                                                         | V <sub>CCIO</sub> supply current   | V <sub>IN</sub> = ground,                                            | EP2C5/A                         | _       | 0.7      | (4)               | mA    |     |   |

|                                                                                            | (standby)                          | no load, no toggling inputs                                          | EP2C8/A                         | _       | 0.8      | (4)               | mA    |     |   |

|                                                                                            |                                    | $T_{.1} = 25^{\circ} \text{ C}$                                      | EP2C15A                         | _       | 0.9      | (4)               | mA    |     |   |

|                                                                                            |                                    | $V_{CCIO} = 2.5 \text{ V}$                                           | EP2C20/A                        | _       | 0.9      | (4)               | mA    |     |   |

|                                                                                            |                                    |                                                                      | EP2C35                          | _       | 1.3      | (4)               | mA    |     |   |

|                                                                                            |                                    |                                                                      | EP2C50                          | _       | 1.3      | (4)               | mA    |     |   |

|                                                                                            |                                    |                                                                      | EP2C70                          | _       | 1.7      | (4)               | mA    |     |   |

**Table 5–6. Recommended Operating Conditions for User I/O Pins Using Single-Ended I/O Standards**Note (1) (Part 2 of 2)

| I/O Standard           | V <sub>CCIO</sub> (V) |     |       | V <sub>REF</sub> (V) |      |       | V <sub>IL</sub> (V)                                           | V <sub>IH</sub> (V)                                           |

|------------------------|-----------------------|-----|-------|----------------------|------|-------|---------------------------------------------------------------|---------------------------------------------------------------|

| i/O Stallualu          | Min                   | Тур | Max   | Min                  | Тур  | Max   | Max                                                           | Min                                                           |

| SSTL-18 class II       | 1.7                   | 1.8 | 1.9   | 0.833                | 0.9  | 0.969 | V <sub>REF</sub> - 0.125 (DC)<br>V <sub>REF</sub> - 0.25 (AC) | V <sub>REF</sub> + 0.125 (DC)<br>V <sub>REF</sub> + 0.25 (AC) |

| 1.8-V HSTL<br>class I  | 1.71                  | 1.8 | 1.89  | 0.85                 | 0.9  | 0.95  | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

| 1.8-V HSTL<br>class II | 1.71                  | 1.8 | 1.89  | 0.85                 | 0.9  | 0.95  | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

| 1.5-V HSTL<br>class I  | 1.425                 | 1.5 | 1.575 | 0.71                 | 0.75 | 0.79  | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

| 1.5-V HSTL<br>class II | 1.425                 | 1.5 | 1.575 | 0.71                 | 0.75 | 0.79  | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

*Note to Table 5–6:*

<sup>(1)</sup> Nominal values (Nom) are for  $T_A$  = 25° C,  $V_{CCINT}$  = 1.2 V, and  $V_{CCIO}$  = 1.5, 1.8, 2.5, and 3.3 V.

| Table 5–7. DC Characteristics of User I/O Pins Using Single-Ended Standards Notes (1), (2) (Part 1 of 2) |                      |                      |                             |                             |  |  |

|----------------------------------------------------------------------------------------------------------|----------------------|----------------------|-----------------------------|-----------------------------|--|--|

| 1/0 0444                                                                                                 | Test Co              | nditions             | Voltage Thresholds          |                             |  |  |

| I/O Standard                                                                                             | I <sub>OL</sub> (mA) | I <sub>OH</sub> (mA) | Maximum V <sub>OL</sub> (V) | Minimum V <sub>OH</sub> (V) |  |  |

| 3.3-V LVTTL                                                                                              | 4                    | -4                   | 0.45                        | 2.4                         |  |  |

| 3.3-V LVCMOS                                                                                             | 0.1                  | -0.1                 | 0.2                         | V <sub>CCIO</sub> - 0.2     |  |  |

| 2.5-V LVTTL and LVCMOS                                                                                   | 1                    | -1                   | 0.4                         | 2.0                         |  |  |

| 1.8-V LVTTL and LVCMOS                                                                                   | 2                    | -2                   | 0.45                        | V <sub>CCIO</sub> - 0.45    |  |  |

| 1.5-V LVTTL and LVCMOS                                                                                   | 2                    | -2                   | 0.25 × V <sub>CCIO</sub>    | 0.75 × V <sub>CCIO</sub>    |  |  |

| PCI and PCI-X                                                                                            | 1.5                  | -0.5                 | 0.1 × V <sub>CCIO</sub>     | 0.9 × V <sub>CCIO</sub>     |  |  |

| SSTL-2 class I                                                                                           | 8.1                  | -8.1                 | V <sub>TT</sub> – 0.57      | V <sub>TT</sub> + 0.57      |  |  |

| SSTL-2 class II                                                                                          | 16.4                 | -16.4                | V <sub>TT</sub> – 0.76      | V <sub>TT</sub> + 0.76      |  |  |

| SSTL-18 class I                                                                                          | 6.7                  | -6.7                 | V <sub>TT</sub> – 0.475     | V <sub>TT</sub> + 0.475     |  |  |

| SSTL-18 class II                                                                                         | 13.4                 | -13.4                | 0.28                        | V <sub>CCIO</sub> - 0.28    |  |  |

| 1.8-V HSTL class I                                                                                       | 8                    | -8                   | 0.4                         | V <sub>CCIO</sub> - 0.4     |  |  |

| 1.8-V HSTL class II                                                                                      | 16                   | -16                  | 0.4                         | V <sub>CCIO</sub> - 0.4     |  |  |

| Table 5–43. Cycl                  | Table 5–43. Cyclone II I/O Output Delay for Row Pins (Part 3 of 4) |                  |                                |                 |                      |                       |                       |                      |      |

|-----------------------------------|--------------------------------------------------------------------|------------------|--------------------------------|-----------------|----------------------|-----------------------|-----------------------|----------------------|------|

|                                   |                                                                    |                  | Fast (                         | Corner          | _                    | -7                    | -7                    |                      |      |

| I/O Standard                      | Drive<br>Strength                                                  | Parameter        | Industrial<br>/Auto-<br>motive | Commer-<br>cial | -6<br>Speed<br>Grade | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | –8<br>Speed<br>Grade | Unit |

| 1.8V_HSTL_                        | 8 mA                                                               | t <sub>OP</sub>  | 1364                           | 1430            | 2853                 | 3017                  | 3178                  | 3184                 | ps   |

| CLASS_I                           |                                                                    | t <sub>DIP</sub> | 1488                           | 1562            | 3061                 | 3254                  | 3451                  | 3451                 | ps   |

|                                   | 10 mA                                                              | t <sub>OP</sub>  | 1332                           | 1396            | 2842                 | 3011                  | 3173                  | 3179                 | ps   |

|                                   |                                                                    | t <sub>DIP</sub> | 1456                           | 1528            | 3050                 | 3248                  | 3446                  | 3446                 | ps   |

|                                   | 12 mA                                                              | t <sub>OP</sub>  | 1332                           | 1396            | 2842                 | 3011                  | 3173                  | 3179                 | ps   |

|                                   | (1)                                                                | t <sub>DIP</sub> | 1456                           | 1528            | 3050                 | 3248                  | 3446                  | 3446                 | ps   |

| 1.5V_HSTL_                        | 8 mA                                                               | t <sub>OP</sub>  | 1657                           | 1738            | 3642                 | 3917                  | 4185                  | 4191                 | ps   |

| CLASS_I                           | (1)                                                                | t <sub>DIP</sub> | 1781                           | 1870            | 3850                 | 4154                  | 4458                  | 4458                 | ps   |

| DIFFERENTIAL_                     | 8 mA                                                               | t <sub>OP</sub>  | 1090                           | 1142            | 2152                 | 2268                  | 2376                  | 2382                 | ps   |

| SSTL_2_<br>CLASS I                |                                                                    | t <sub>DIP</sub> | 1214                           | 1274            | 2360                 | 2505                  | 2649                  | 2649                 | ps   |

| 02.00                             | 12 mA<br>(1)                                                       | t <sub>OP</sub>  | 1097                           | 1150            | 2131                 | 2246                  | 2354                  | 2360                 | ps   |

|                                   |                                                                    | t <sub>DIP</sub> | 1221                           | 1282            | 2339                 | 2483                  | 2627                  | 2627                 | ps   |

| DIFFERENTIAL_                     | 16 mA                                                              | t <sub>OP</sub>  | 1068                           | 1119            | 2067                 | 2177                  | 2281                  | 2287                 | ps   |

| SSTL_2_<br>CLASS_II               | (1)                                                                | t <sub>DIP</sub> | 1192                           | 1251            | 2275                 | 2414                  | 2554                  | 2554                 | ps   |

| DIFFERENTIAL_                     | 6 mA                                                               | t <sub>OP</sub>  | 1371                           | 1437            | 2828                 | 3018                  | 3200                  | 3206                 | ps   |

| SSTL_18_<br>CLASS I               |                                                                    | t <sub>DIP</sub> | 1495                           | 1569            | 3036                 | 3255                  | 3473                  | 3473                 | ps   |

| 02.00                             | 8 mA                                                               | t <sub>OP</sub>  | 1365                           | 1431            | 2832                 | 3024                  | 3209                  | 3215                 | ps   |

|                                   |                                                                    | t <sub>DIP</sub> | 1489                           | 1563            | 3040                 | 3261                  | 3482                  | 3482                 | ps   |

|                                   | 10 mA                                                              | t <sub>OP</sub>  | 1374                           | 1440            | 2806                 | 2990                  | 3167                  | 3173                 | ps   |

|                                   | (1)                                                                | t <sub>DIP</sub> | 1498                           | 1572            | 3014                 | 3227                  | 3440                  | 3440                 | ps   |

| 1.8V_                             | 8 mA                                                               | t <sub>OP</sub>  | 1364                           | 1430            | 2853                 | 3017                  | 3178                  | 3184                 | ps   |

| DIFFERENTIAL_<br>HSTL             |                                                                    | t <sub>DIP</sub> | 1488                           | 1562            | 3061                 | 3254                  | 3451                  | 3451                 | ps   |

| CLASS_I                           | 10 mA                                                              | t <sub>OP</sub>  | 1332                           | 1396            | 2842                 | 3011                  | 3173                  | 3179                 | ps   |

|                                   |                                                                    | t <sub>DIP</sub> | 1456                           | 1528            | 3050                 | 3248                  | 3446                  | 3446                 | ps   |

|                                   | 12 mA                                                              | t <sub>OP</sub>  | 1332                           | 1396            | 2842                 | 3011                  | 3173                  | 3179                 | ps   |

|                                   | (1)                                                                | t <sub>DIP</sub> | 1456                           | 1528            | 3050                 | 3248                  | 3446                  | 3446                 | ps   |

| 1.5V_                             | 8 mA                                                               | t <sub>OP</sub>  | 1657                           | 1738            | 3642                 | 3917                  | 4185                  | 4191                 | ps   |

| DIFFERENTIAL_<br>HSTL_<br>CLASS_I | (1)                                                                | t <sub>DIP</sub> | 1781                           | 1870            | 3850                 | 4154                  | 4458                  | 4458                 | ps   |

Note to Figure 5–4:

(1) The equation for the high-speed I/O timing budget is: period = TCCS + RSKM + SW + RSKM.

Table 5–48 shows the RSDS timing budget for Cyclone II devices at 311 Mbps. RSDS is supported for transmitting from Cyclone II devices. Cyclone II devices cannot receive RSDS data because the devices are intended for applications where they will be driving display drivers. Cyclone II devices support a maximum RSDS data rate of 311 Mbps using DDIO registers. Cyclone II devices support RSDS only in the commercial temperature range.

| Table 5–48. RSDS Transmitter Timing Specification (Part 1 of 2) |            |      |                |        |                |     |        |                |     |        |      |

|-----------------------------------------------------------------|------------|------|----------------|--------|----------------|-----|--------|----------------|-----|--------|------|

| O. mb al                                                        |            | -6 8 | -6 Speed Grade |        | -7 Speed Grade |     |        | -8 Speed Grade |     |        |      |

| Symbol                                                          | Conditions | Min  | Тур            | Max(1) | Min            | Тур | Max(1) | Min            | Тур | Max(1) | Unit |

| f <sub>HSCLK</sub>                                              | ×10        | 10   | _              | 155.5  | 10             | _   | 155.5  | 10             | _   | 155.5  | MHz  |

| (input<br>clock                                                 | ×8         | 10   | _              | 155.5  | 10             | _   | 155.5  | 10             | _   | 155.5  | MHz  |

| frequency)                                                      | ×7         | 10   | _              | 155.5  | 10             | _   | 155.5  | 10             | _   | 155.5  | MHz  |

|                                                                 | ×4         | 10   | _              | 155.5  | 10             | _   | 155.5  | 10             | _   | 155.5  | MHz  |

|                                                                 | ×2         | 10   | _              | 155.5  | 10             | _   | 155.5  | 10             | _   | 155.5  | MHz  |

|                                                                 | ×1         | 10   | _              | 311    | 10             | _   | 311    | 10             | _   | 311    | MHz  |

| Device                                                          | ×10        | 100  | _              | 311    | 100            | _   | 311    | 100            | _   | 311    | Mbps |

| operation in Mbps                                               | ×8         | 80   | _              | 311    | 80             | _   | 311    | 80             | _   | 311    | Mbps |

| iii wbps                                                        | ×7         | 70   | _              | 311    | 70             | _   | 311    | 70             | _   | 311    | Mbps |

|                                                                 | ×4         | 40   | _              | 311    | 40             | _   | 311    | 40             | _   | 311    | Mbps |

|                                                                 | ×2         | 20   | _              | 311    | 20             | _   | 311    | 20             | _   | 311    | Mbps |

|                                                                 | ×1         | 10   | _              | 311    | 10             | _   | 311    | 10             | _   | 311    | Mbps |

| t <sub>DUTY</sub>                                               | _          | 45   | _              | 55     | 45             | _   | 55     | 45             | _   | 55     | %    |

# 7. PLLs in Cyclone II Devices

CII51007-3.1

#### Introduction

Cyclone<sup>®</sup> II devices have up to four phase-locked loops (PLLs) that provide robust clock management and synthesis for device clock management, external system clock management, and I/O interfaces. Cyclone II PLLs are versatile and can be used as a zero delay buffer, a jitter attenuator, a low skew fan out buffer, or a frequency synthesizer.

Each Cyclone II device has up to four PLLs, supporting advanced capabilities such as clock switchover and programmable switchover. These PLLs offer clock multiplication and division, phase shifting, and programmable duty cycle and can be used to minimize clock delay and clock skew, and to reduce or adjust clock-to-out ( $t_{CO}$ ) and set-up ( $t_{SU}$ ) times.

Cyclone II devices also support a power-down mode where unused clock networks can be turned off. The Altera<sup>®</sup> Quartus<sup>®</sup> II software enables the PLLs and their features without requiring any external devices.

Cyclone II PLLs have been characterized to operate in the commercial junction temperature range (0° to 85° C), the industrial junction temperature range (-40° to 100° C) and the extended temperature range (-40° to 125° C).

Table 7–1 shows the PLLs available in each Cyclone II device.

| Table 7–1. Cyclone II Device PLL Availability |          |          |          |          |  |  |  |

|-----------------------------------------------|----------|----------|----------|----------|--|--|--|

| Device                                        | PLL1     | PLL2     | PLL3     | PLL4     |  |  |  |

| EP2C5                                         | <b>✓</b> | <b>✓</b> |          |          |  |  |  |

| EP2C8                                         | <b>✓</b> | <b>✓</b> |          |          |  |  |  |

| EP2C15                                        | ✓        | <b>✓</b> | <b>✓</b> | ✓        |  |  |  |

| EP2C20                                        | ✓        | <b>✓</b> | <b>✓</b> | ✓        |  |  |  |

| EP2C35                                        | ✓        | <b>✓</b> | ✓        | ✓        |  |  |  |

| EP2C50                                        | ✓        | ✓        | ✓        | ✓        |  |  |  |

| EP2C70                                        | ✓        | ✓        | ✓        | <b>✓</b> |  |  |  |

| Table 8–1. Summary of M4K Memory Features (Part 2 of 2) |                                           |  |  |  |  |

|---------------------------------------------------------|-------------------------------------------|--|--|--|--|

| Feature                                                 | M4K Blocks                                |  |  |  |  |

| Packed mode                                             | ✓                                         |  |  |  |  |

| Address clock enable                                    | ✓                                         |  |  |  |  |

| Single-port mode                                        | ✓                                         |  |  |  |  |

| Simple dual-port mode                                   | ✓                                         |  |  |  |  |

| True dual-port mode                                     | ✓                                         |  |  |  |  |

| Embedded shift register mode (2)                        | ✓                                         |  |  |  |  |

| ROM mode                                                | ✓                                         |  |  |  |  |

| FIFO buffer (2)                                         | ✓                                         |  |  |  |  |

| Simple dual-port mixed width support                    | ✓                                         |  |  |  |  |

| True dual-port mixed width support                      | ✓                                         |  |  |  |  |

| Memory Initialization File (.mif)                       | ✓                                         |  |  |  |  |

| Mixed-clock mode                                        | ✓                                         |  |  |  |  |

| Power-up condition                                      | Outputs cleared                           |  |  |  |  |

| Register clears                                         | Output registers only                     |  |  |  |  |

| Same-port read-during-write                             | New data available at positive clock edge |  |  |  |  |

| Mixed-port read-during-write                            | Old data available at positive clock edge |  |  |  |  |

#### Notes to Table 8-1:

- (1) Maximum performance information is preliminary until device characterization.

- (2) FIFO buffers and embedded shift registers require external logic elements (LEs) for implementing control logic.

Table 8–2 shows the capacity and distribution of the M4K memory blocks in each Cyclone II device family member.

| Table 8–2. Number of M4K Blocks in Cyclone II Devices (Part 1 of 2) |            |                |  |  |  |  |  |

|---------------------------------------------------------------------|------------|----------------|--|--|--|--|--|

| Device                                                              | M4K Blocks | Total RAM Bits |  |  |  |  |  |

| EP2C5                                                               | 26         | 119,808        |  |  |  |  |  |

| EP2C8                                                               | 36         | 165,888        |  |  |  |  |  |

| EP2C15                                                              | 52         | 239,616        |  |  |  |  |  |

| EP2C20                                                              | 52         | 239,616        |  |  |  |  |  |

| EP2C35                                                              | 105        | 483,840        |  |  |  |  |  |

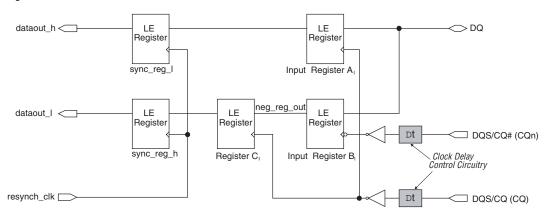

Figure 9-4. CQ & CQn Connection for QDRII SRAM Read

#### Read & Write Operation

Figure 9–5 shows the data and clock relationships in QDRII SRAM devices at the memory pins during reads. QDRII SRAM devices send data within  $t_{CO}$  time after each rising edge of the read clock C or C# in multiclock mode or the input clock K or K# in single clock mode. Data is valid until  $t_{\rm DOH}$  time after each rising edge of the read clock C or C# in multiclock mode or the input clock K or K# in single clock mode. The CQ and CQn clocks are edge-aligned with the read data signal. These clocks accompany the read data for data capture in Cyclone II devices.

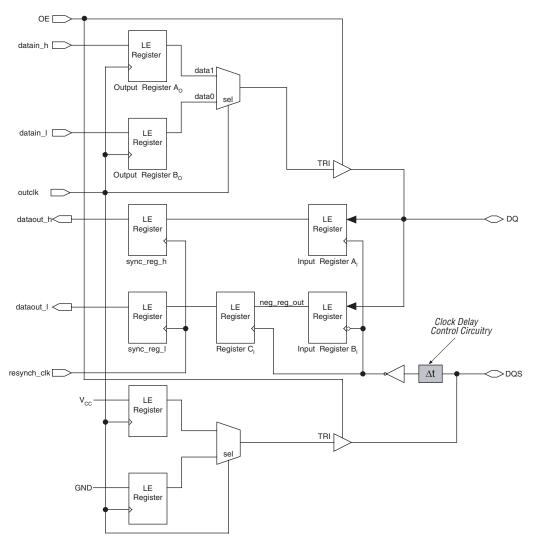

Figure 9–16. Bidirectional DDR Implementation for DDR Memory Interfaces Note (1)

Note to Figure 9-16:

(1) You can use the altdq and altdqs megafunctions to generate the DQ and DQS signals.

Figure 9–17 shows example waveforms from a bidirectional DDR implementation.

# 11. High-Speed Differential Interfaces in Cyclone II Devices

CII51011-2.2

#### Introduction

From high-speed backplane applications to high-end switch boxes, low-voltage differential signaling (LVDS) is the technology of choice. LVDS is a low-voltage differential signaling standard, allowing higher noise immunity than single-ended I/O technologies. Its low-voltage swing allows for high-speed data transfers, low power consumption, and reduced electromagnetic interference (EMI). LVDS I/O signaling is a data interface standard defined in the TIA/EIA-644 and IEEE Std. 1596.3 specifications.

The reduced swing differential signaling (RSDS) and mini-LVDS standards are derivatives of the LVDS standard. The RSDS and mini-LVDS I/O standards are similar in electrical characteristics to LVDS, but have a smaller voltage swing and therefore provide increased power benefits and reduced EMI. National Semiconductor Corporation and Texas Instruments introduced the RSDS and mini-LVDS specifications, respectively. Currently, many designers use these specifications for flat panel display links between the controller and the drivers that drive display column drivers. Cyclone® II devices support the RSDS and mini-LVDS I/O standards at speeds up to 311 megabits per second (Mbps) at the transmitter.

Altera® Cyclone II devices can transmit and receive data through LVDS signals at a data rate of up to 640 Mbps and 805 Mbps, respectively. For the LVDS transmitter and receiver, the Cyclone II device's input and output pins support serialization and deserialization through internal logic.

This chapter describes how to use Cyclone II I/O pins for differential signaling and contains the following topics:

- Cyclone II high-speed I/O banks

- Cyclone II high-speed I/O interface

- LVDS, RSDS, mini-LVDS, LVPECL, differential HSTL, and differential SSTL I/O standards support in Cyclone II devices

- High-speed I/O timing in Cyclone II devices

- Design guidelines

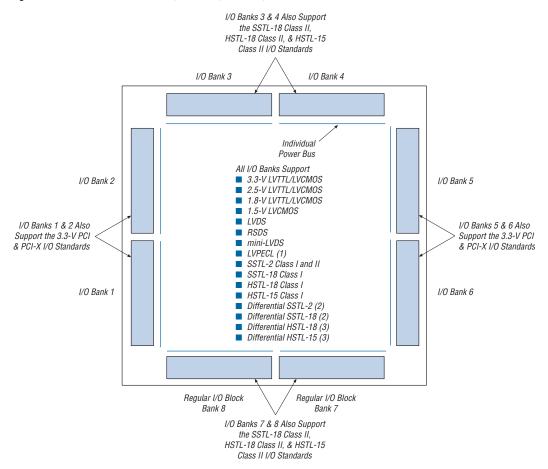

## Cyclone II High-Speed I/O Banks

Cyclone II device I/O banks are shown in Figures 11–1 and 11–2. The EP2C5 and EP2C8 devices offer four I/O banks and EP2C15, EP2C20, EP2C35, EP2C50, and EP2C70 devices offer eight I/O banks. A subset of

Figure 11–2. I/O Banks in EP2C15, EP2C20, EP2C35, EP2C50 & EP2C70 Devices

#### Notes to Figure 11-2:

- The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (2) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (3) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

### Cyclone II High-Speed I/O Interface

Cyclone II devices provide a multi-protocol interface that allows communication between a variety of I/O standards, including LVDS, LVPECL, RSDS, mini-LVDS, differential HSTL, and differential SSTL. This feature makes the Cyclone II device family ideal for applications that require multiple I/O standards, such as protocol translation.

Section VI-2 Altera Corporation

#### Configuration Stage

When the nSTATUS pin transitions high, the configuration device's OE pin also transitions high and the configuration device clocks data out serially to the FPGA using its internal oscillator. The Cyclone II device receives configuration data on its DATAO pin and the clock is received on the DCLK pin. Data is latched into the FPGA on the rising edge of DCLK.

After the FPGA has received all configuration data successfully, it releases the open-drain CONF\_DONE pin, which is pulled high by a pull-up resistor. Since the Cyclone II device's CONF\_DONE pin is tied to the configuration device's nCS pin, the configuration device is disabled when CONF\_DONE goes high. Enhanced configuration and EPC2 devices have an optional internal pull-up resistor on the nCS pin. You can turn this option on in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. If you do not use this internal pull-up resistor, you need to connect an external 10-k $\Omega$ pull-up resistor to the nCS and CONF\_DONE line. A low-to-high transition on CONF\_DONE indicates configuration is complete, and the device can begin initialization.

#### Initialization Stage

In Cyclone II devices, the default initialization clock source is the Cyclone II internal oscillator (typically 10 MHz). Cyclone II devices can also use the optional CLKUSR pin. If your design uses the internal oscillator, the Cyclone II device supplies itself with enough clock cycles for proper initialization. The advantage of using the internal oscillator is you do not need to use another device or source to send additional clock cycles to the CLKUSR pin during the initialization stage. Additionally, you can use of the CLKUSR pin as a user I/O pin, which means you have an additional user I/O pin.

If you want to delay the initialization of the device, you can use the CLKUSR pin. Using the CLKUSR pin allows you to control when the Cyclone II device enters user mode. You can delay the Cyclone II devices from entering user mode for an indefinite amount of time. You can turn on the Enable user-supplied start-up clock (CLKUSR) option in the Quartus II software from the General tab of the Device & Pin Options dialog box. Supplying a clock on CLKUSR does not affect the configuration process. After all configuration data is accepted and CONF\_DONE goes high, Cyclone II devices require 299 clock cycles to properly initialize and support a CLKUSR  $f_{\rm MAX}$  of 100 MHz.

An optional <code>INIT\_DONE</code> pin is available, which signals the end of initialization and the start of user mode with a low-to-high transition. The <code>Enable INIT\_DONE</code> output option is available in the Quartus II software from the <code>General</code> tab of the <code>Device & Pin Options</code> dialog box. If you use the <code>INIT\_DONE</code> pin, an external 10-k $\Omega$ pull-up resistor pulls it high when

| Table 13–11. Dedicated Configuration Pins on the Cyclone II Device (Part 4 of 5) |                                                          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|----------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                                                         | User<br>Mode                                             | Configuration<br>Scheme | Pin Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| nCEO                                                                             | N/A if option is on. I/O if option is off.               | All                     | Output   | This pin is an output that drives low when device configuration is complete. In single device configuration, you can leave this pin floating or use it as a user I/O pin after configuration. In multiple device configuration, this pin inputs the next device's $n\text{CE}$ pin. The $n\text{CEO}$ of the last device in the chain can be left floating or used as a user I/O pin after configuration. If you use the $n\text{CEO}$ pin to feed next device's $n\text{CE}$ pin, use an external 10-k $\Omega$ pull-up resistor to pull the $n\text{CEO}$ pin high to the $V_{\text{CCIO}}$ voltage of its I/O bank to help the internal weak pull-up resistor. |  |  |  |  |

|                                                                                  |                                                          |                         |          | Use the Quartus II software to make this pin a user I/O pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| ASDO                                                                             | N/A in<br>AS<br>mode<br>I/O in<br>PS and<br>JTAG<br>mode | AS                      | Output   | This pin sends a control signal from the Cyclone II device to the serial configuration device in AS mode and is used to read out configuration data.  In AS mode, ASDO has an internal pull-up that is always active.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| nCSO                                                                             | N/A in<br>AS<br>mode<br>I/O in<br>PS and<br>JTAG<br>mode | AS                      | Output   | This pin sends an output control signal from the Cyclone II device to the serial configuration device in AS mode that enables the configuration device.  In AS mode, nCSO has an internal pull-up resistor that is always active.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

Table 13–12 describes the optional configuration pins. If these optional configuration pins are not enabled in the Quartus II software, they are available as general-purpose user I/O pins. Therefore during configuration, these pins function as user I/O pins and are tri-stated with weak pull-up resistors.

| Table 13–12. Optional Configuration Pins |                                                  |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------|--------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                 | User Mode                                        | Pin Type              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CLKUSR                                   | N/A if option is<br>on. I/O if option<br>is off. | Input                 | This is an optional user-supplied clock input that synchronizes the initialization of one or more devices. This pin is enabled by turning on the <b>Enable user-supplied start-up clock (CLKUSR)</b> option in the Quartus II software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| INIT_DONE                                | N/A if option is<br>on. I/O if option<br>is off. | Output open-<br>drain | This is a status pin that can be used to indicate when the device has initialized and is in user mode. When $\texttt{nCONFIG}$ is low and during the beginning of configuration, the $\texttt{INIT\_DONE}$ pin is tri-stated and pulled high due to an external 10-k $\Omega$ pull-up resistor. Once the option bit to enable $\texttt{INIT\_DONE}$ is programmed into the device (during the first frame of configuration data), the $\texttt{INIT\_DONE}$ pin goes low. When initialization is complete, the $\texttt{INIT\_DONE}$ pin is released and pulled high and the FPGA enters user mode. Thus, the monitoring circuitry must be able to detect a low-to-high transition. This pin is enabled by turning on the <b>Enable INIT_DONE output</b> option in the Quartus II software. |