Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 2076                                                    |

| Number of Logic Elements/Cells | 33216                                                   |

| Total RAM Bits                 | 483840                                                  |

| Number of I/O                  | 322                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 484-BGA                                                 |

| Supplier Device Package        | 484-FBGA (23x23)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c35f484c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Section I. Cyclone II Device Family Data Sheet

This section provides information for board layout designers to successfully layout their boards for Cyclone<sup>®</sup> II devices. It contains the required PCB layout guidelines, device pin tables, and package specifications.

This section includes the following chapters:

- Chapter 1. Introduction

- Chapter 2. Cyclone II Architecture

- Chapter 3. Configuration & Testing

- Chapter 4. Hot Socketing & Power-On Reset

- Chapter 5. DC Characteristics and Timing Specifications

- Chapter 6. Reference & Ordering Information

# **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

Altera Corporation Section I–1

phase-align double data rate (DDR) signals) provide interface support for external memory devices such as DDR, DDR2, and single data rate (SDR) SDRAM, and QDRII SRAM devices at up to 167 MHz.

Figure 2–1 shows a diagram of the Cyclone II EP2C20 device.

PLL IOEs PLL Embedded Multipliers Logic Logic Logic Logic **IOEs IOEs** Array Array Array Array M4K Blocks M4K Blocks PLL **IOEs PLL**

Figure 2–1. Cyclone II EP2C20 Device Block Diagram

The number of M4K memory blocks, embedded multiplier blocks, PLLs, rows, and columns vary per device.

# **Logic Elements**

The smallest unit of logic in the Cyclone II architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE features:

- A four-input look-up table (LUT), which is a function generator that can implement any function of four variables

- A programmable register

- A carry chain connection

- A register chain connection

- The ability to drive all types of interconnects: local, row, column, register chain, and direct link interconnects

- Support for register packing

- Support for register feedback

Embedded multipliers can operate at up to 250 MHz (for the fastest speed grade) for  $18 \times 18$  and  $9 \times 9$  multiplications when using both input and output registers.

Each Cyclone II device has one to three columns of embedded multipliers that efficiently implement multiplication functions. An embedded multiplier spans the height of one LAB row. Table 2–10 shows the number of embedded multipliers in each Cyclone II device and the multipliers that can be implemented.

| Table 2–10. Number of Embedded Multipliers in Cyclone II Devices Note (1) |                                |                         |                   |                     |  |

|---------------------------------------------------------------------------|--------------------------------|-------------------------|-------------------|---------------------|--|

| Device                                                                    | Embedded<br>Multiplier Columns | Embedded<br>Multipliers | 9 × 9 Multipliers | 18 × 18 Multipliers |  |

| EP2C5                                                                     | 1                              | 13                      | 26                | 13                  |  |

| EP2C8                                                                     | 1                              | 18                      | 36                | 18                  |  |

| EP2C15                                                                    | 1                              | 26                      | 52                | 26                  |  |

| EP2C20                                                                    | 1                              | 26                      | 52                | 26                  |  |

| EP2C35                                                                    | 1                              | 35                      | 70                | 35                  |  |

| EP2C50                                                                    | 2                              | 86                      | 172               | 86                  |  |

| EP2C70                                                                    | 3                              | 150                     | 300               | 150                 |  |

*Note to Table 2–10:*

The embedded multiplier consists of the following elements:

- Multiplier block

- Input and output registers

- Input and output interfaces

Figure 2–18 shows the multiplier block architecture.

<sup>(1)</sup> Each device has either the number of  $9 \times 9$ -, or  $18 \times 18$ -bit multipliers shown. The total number of multipliers for each device is not the sum of all the multipliers.

There is only one signa and one signb signal for each dedicated multiplier. Therefore, all of the data A inputs feeding the same dedicated multiplier must have the same sign representation. Similarly, all of the data B inputs feeding the same dedicated multiplier must have the same sign representation. The signa and signb signals can be changed dynamically to modify the sign representation of the input operands at run time. The multiplier offers full precision regardless of the sign representation and can be registered using dedicated registers located at the input register stage.

### **Multiplier Modes**

Table 2–12 summarizes the different modes that the embedded multipliers can operate in.

| Table 2–12. Embedded Multiplier Modes |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Multiplier Mode                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 18-bit Multiplier                     | An embedded multiplier can be configured to support a single 18 × 18 multiplier for operand widths up to 18 bits. All 18-bit multiplier inputs and results can be registered independently. The multiplier operands can accept signed integers, unsigned integers, or a combination of both.                                                                                                                                                                                                                                           |  |  |  |

| 9-bit Multiplier                      | An embedded multiplier can be configured to support two 9 × 9 independent multipliers for operand widths up to 9-bits. Both 9-bit multiplier inputs and results can be registered independently. The multiplier operands can accept signed integers, unsigned integers or a combination of both.  There is only one signa signal to control the sign representation of both data A inputs and one signb signal to control the sign representation of both data B inputs of the 9-bit multipliers within the same dedicated multiplier. |  |  |  |

| Table 2–18. Cyclone II Device LVDS Channels (Part 2 of 2) |     |           |  |  |

|-----------------------------------------------------------|-----|-----------|--|--|

| Device Pin Count Number of LVDS Channels (1)              |     |           |  |  |

| EP2C70                                                    | 672 | 160 (168) |  |  |

|                                                           | 896 | 257 (265) |  |  |

Note to Table 2-18:

(1) The first number represents the number of bidirectional I/O pins which can be used as inputs or outputs. The number in parenthesis includes dedicated clock input pin pairs which can only be used as inputs.

You can use I/O pins and internal logic to implement a high-speed I/O receiver and transmitter in Cyclone II devices. Cyclone II devices do not contain dedicated serialization or deserialization circuitry. Therefore, shift registers, internal PLLs, and IOEs are used to perform serial-to-parallel conversions on incoming data and parallel-to-serial conversion on outgoing data.

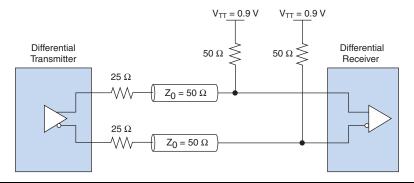

The maximum internal clock frequency for a receiver and for a transmitter is 402.5 MHz. The maximum input data rate of 805 Mbps and the maximum output data rate of 640 Mbps is only achieved when DDIO registers are used. The LVDS standard does not require an input reference voltage, but it does require a  $100\text{-}\Omega$  termination resistor between the two signals at the input buffer. An external resistor network is required on the transmitter side.

For more information on Cyclone II differential I/O interfaces, see the *High-Speed Differential Interfaces in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

## **Series On-Chip Termination**

On-chip termination helps to prevent reflections and maintain signal integrity. This also minimizes the need for external resistors in high pin count ball grid array (BGA) packages. Cyclone II devices provide I/O driver on-chip impedance matching and on-chip series termination for single-ended outputs and bidirectional pins.

| Table 5–42. Cyclone II I/O Output Delay for Column Pins (Part 2 of 6) |                   |                  |                           |                 |                |                       |                       |                |      |

|-----------------------------------------------------------------------|-------------------|------------------|---------------------------|-----------------|----------------|-----------------------|-----------------------|----------------|------|

|                                                                       |                   | Parameter        | Fast Corner               |                 | -6             | -7                    | -7                    | -8             |      |

| I/O Standard                                                          | Drive<br>Strength |                  | Industrial/<br>Automotive | Commer<br>-cial | Speed<br>Grade | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | Speed<br>Grade | Unit |

| 2.5V                                                                  | 4 mA              | t <sub>OP</sub>  | 1208                      | 1267            | 2478           | 2614                  | 2743                  | 2750           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1340                      | 1406            | 2648           | 2808                  | 2969                  | 2969           | ps   |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 1190                      | 1248            | 2307           | 2434                  | 2554                  | 2561           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1322                      | 1387            | 2477           | 2628                  | 2780                  | 2780           | ps   |

|                                                                       | 12 mA             | t <sub>OP</sub>  | 1154                      | 1210            | 2192           | 2314                  | 2430                  | 2437           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1286                      | 1349            | 2362           | 2508                  | 2656                  | 2656           | ps   |

|                                                                       | 16 mA             | t <sub>OP</sub>  | 1140                      | 1195            | 2152           | 2263                  | 2375                  | 2382           | ps   |

|                                                                       | (1)               | t <sub>DIP</sub> | 1272                      | 1334            | 2322           | 2457                  | 2601                  | 2601           | ps   |

| 1.8V                                                                  | 2 mA              | t <sub>OP</sub>  | 1682                      | 1765            | 3988           | 4279                  | 4563                  | 4570           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1814                      | 1904            | 4158           | 4473                  | 4789                  | 4789           | ps   |

|                                                                       | 4 mA              | t <sub>OP</sub>  | 1567                      | 1644            | 3301           | 3538                  | 3768                  | 3775           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1699                      | 1783            | 3471           | 3732                  | 3994                  | 3994           | ps   |

|                                                                       | 6 mA              | t <sub>OP</sub>  | 1475                      | 1547            | 2993           | 3195                  | 3391                  | 3398           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1607                      | 1686            | 3163           | 3389                  | 3617                  | 3617           | ps   |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 1451                      | 1522            | 2882           | 3074                  | 3259                  | 3266           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1583                      | 1661            | 3052           | 3268                  | 3485                  | 3485           | ps   |

|                                                                       | 10 mA             | t <sub>OP</sub>  | 1438                      | 1508            | 2853           | 3041                  | 3223                  | 3230           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1570                      | 1647            | 3023           | 3235                  | 3449                  | 3449           | ps   |

|                                                                       | 12 mA             | t <sub>OP</sub>  | 1438                      | 1508            | 2853           | 3041                  | 3223                  | 3230           | ps   |

|                                                                       | (1)               | t <sub>DIP</sub> | 1570                      | 1647            | 3023           | 3235                  | 3449                  | 3449           | ps   |

| 1.5V                                                                  | 2 mA              | t <sub>OP</sub>  | 2083                      | 2186            | 4477           | 4870                  | 5256                  | 5263           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 2215                      | 2325            | 4647           | 5064                  | 5482                  | 5482           | ps   |

|                                                                       | 4 mA              | t <sub>OP</sub>  | 1793                      | 1881            | 3649           | 3965                  | 4274                  | 4281           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1925                      | 2020            | 3819           | 4159                  | 4500                  | 4500           | ps   |

|                                                                       | 6 mA              | t <sub>OP</sub>  | 1770                      | 1857            | 3527           | 3823                  | 4112                  | 4119           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1902                      | 1996            | 3697           | 4017                  | 4338                  | 4338           | ps   |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 1703                      | 1787            | 3537           | 3827                  | 4111                  | 4118           | ps   |

|                                                                       | (1)               | t <sub>DIP</sub> | 1835                      | 1926            | 3707           | 4021                  | 4337                  | 4337           | ps   |

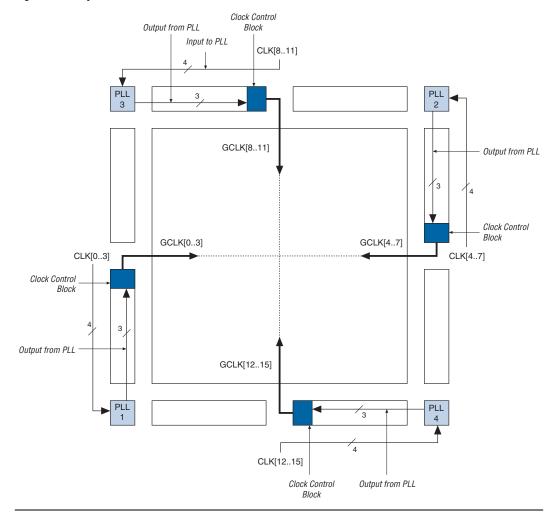

Figure 7-12. Cyclone II Clock Control Blocks Placement

The inputs to the four clock control blocks on each side are chosen from among the following clock sources:

- Four clock input pins

- Three PLL counter outputs

- Two DPCLK pins and two CDPCLK pins from both the left and right sides and four DPCLK pins and two CDPCLK pins from both the top and bottom

- Four signals from internal logic

QDRII SRAM devices use the following clock signals:

- Input clocks K and K#

- Optional output clocks C and C#

- Echo clocks CQ and CQn

Clocks C#, K#, and CQn are logical complements of clocks C, K, and CQ, respectively. Clocks C, C#, K, and K# are inputs to the QDRII SRAM, and clocks CQ and CQn are outputs from the QDRII SRAM. Cyclone II devices use single-clock mode for QDRII SRAM interfacing. The K and K# clocks are used for both read and write operations, and the C and C# clocks are unused.

You can generate C, C#, K, and K# clocks using any of the I/O registers via the DDR registers. Due to strict skew requirements between K and K# signals, use adjacent pins to generate the clock pair. Surround the pair with buffer pins tied to  $V_{CC}$  and pins tied to ground for better noise immunity from other signals.

In Cyclone II devices, another DQS pin implements the CQn pin in the QDRII SRAM memory interface. These pins are denoted by DQS/CQ# in the pin table. Connect CQ and CQn pins to the Cyclone II DQS/CQ and DQS/CQ# pins of the same DQ groups, respectively. You must configure the DQS/CQ and DQS/CQ# as bidirectional pins. However, because CQ and CQn pins are output-only pins from the memory device, the Cyclone II device's QDRII SRAM memory interface requires that you ground the DQS/CQ and DQS/CQ# output enable. To capture data presented by the memory device, connect the shifted CQ signal to register  $\mathtt{C}_\mathtt{I}$  and input register  $\mathtt{A}_\mathtt{I}$ . Connect the shifted CQn to input register  $\mathtt{B}_\mathtt{I}$ . Figure 9–4 shows the CQ and CQn connections for a QDRII SRAM read.

# Document Revision History

Table 9–4 shows the revision history for this document.

| Table 9–4. Document Revision History |                                                                                                                                                                                                                                          |                                                                                |  |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|

| Date &<br>Document<br>Version        | Changes Made                                                                                                                                                                                                                             | Summary of Changes                                                             |  |  |  |

| February 2007<br>v3.1                | <ul> <li>Added document revision history.</li> <li>Added handpara note in "Data &amp; Data Strobe Pins" section.</li> <li>Updated "DDR Output Registers" section.</li> </ul>                                                             | Elaboration of DDR2 and<br>QDRII interfaces supported<br>by I/O bank included. |  |  |  |

| November<br>2005, v2.1               | <ul><li>Introduction</li><li>Updated Table 9–2.</li><li>Updated Figure 9–7.</li></ul>                                                                                                                                                    |                                                                                |  |  |  |

| July 2005, v2.0                      | Updated Table 9–2.                                                                                                                                                                                                                       |                                                                                |  |  |  |

| November<br>2004, v1.1               | <ul> <li>Moved the "External Memory Interface Standards" section to follow the "Introduction" section.</li> <li>Updated the "Data &amp; Data Strobe Pins" section.</li> <li>Updated Figures 9–11, 9–12, 9–15, 9–16, and 9–17.</li> </ul> |                                                                                |  |  |  |

| June 2004, v1.0                      | Added document to the Cyclone II Device Handbook.                                                                                                                                                                                        |                                                                                |  |  |  |

# Pseudo-Differential SSTL-18 Class I and Differential SSTL-18 Class II

The 1.8-V differential SSTL-18 standard is formulated under JEDEC Standard, JESD8-15: Stub Series Terminated Logic for 1.8V (SSTL-18).

The differential SSTL-18 I/O standard is a 1.8-V standard used for applications such as high-speed DDR2 SDRAM interfaces. This standard supports differential signals in systems using the SSTL-18 standard and supplements the SSTL-18 standard for differential clocks. Refer to Figures 10–9 and 10–10 for details on differential SSTL-18 termination.

Cyclone II devices do not support true differential SSTL-18 standards. Cyclone II devices support pseudo-differential SSTL-18 outputs for PLL\_OUT pins and pseudo-differential SSTL-18 inputs for clock pins. Pseudo-differential inputs require an input reference voltage as opposed to the true differential inputs. Refer to Table 10–1 on page 10–2 for information about pseudo-differential SSTL.

Figure 10-9. Differential SSTL-18 Class I Termination

### I/O Driver Impedance Matching (R<sub>S</sub>) and Series Termination (R<sub>S</sub>)

Cyclone II devices support driver impedance matching to the impedance of the transmission line, typically 25 or 50  $\Omega$  When used with the output drivers, on-chip termination (OCT) sets the output driver impedance to 25 or 50  $\Omega$  by choosing the driver strength. Once matching impedance is selected, driver current can not be changed. Table 10–7 provides a list of output standards that support impedance matching. All I/O banks and I/O pins support impedance matching and series termination. Dedicated configuration pins and JTAG pins do not support impedance matching or series termination.

| Table 10–7. Selectable I/O Drivers with Impedance Matching and Series<br>Termination |        |  |  |  |

|--------------------------------------------------------------------------------------|--------|--|--|--|

| I/O Standard Target $R_S$ ( $\Omega$ )                                               |        |  |  |  |

| 3.3-V LVTTL/CMOS                                                                     | 25 (1) |  |  |  |

| 2.5-V LVTTL/CMOS                                                                     | 50 (1) |  |  |  |

| 1.8-V LVTTL/CMOS                                                                     | 50 (1) |  |  |  |

| SSTL-2 class I                                                                       | 50 (1) |  |  |  |

| SSTL-18 class I                                                                      | 50 (1) |  |  |  |

#### *Note to Table 10–7:*

(1) These RS values are nominal values. Actual impedance varies across process, voltage, and temperature conditions. Tolerance is specified in the DC Characteristics and Timing Specifications chapter in volume 1 of the Cyclone II Handbook.

# Pad Placement and DC Guidelines

This section provides pad placement guidelines for the programmable I/O standards supported by Cyclone II devices and includes essential information for designing systems using the devices' selectable I/O capabilities. This section also discusses the DC limitations and guidelines.

Quartus II software provides user controlled restriction relaxation options for some placement constraints. When a default restriction is relaxed by a user, the Quartus II fitter generates warnings.

For more information about how Quartus II software checks I/O restrictions, refer to the I/O Management chapter in volume 2 of the Quartus II Handbook.

pins in each  $\rm I/O$  bank (on both rows and columns) support the high-speed  $\rm I/O$  interface. Cyclone II pin tables list the pins that support the high-speed  $\rm I/O$  interface.

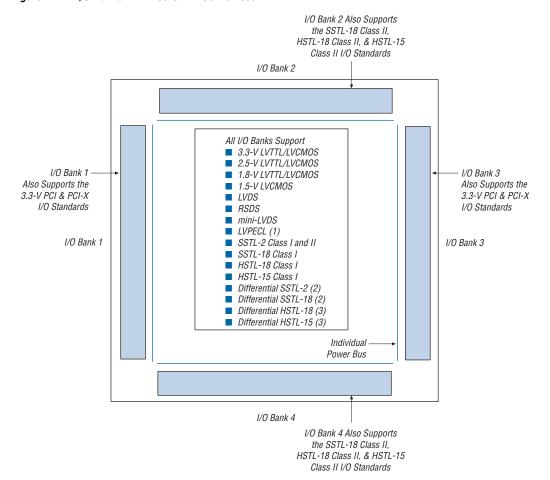

Figure 11-1. I/O Banks in EP2C5 & EP2C8 Devices

#### *Notes to Figure 11–1:*

- The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (2) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (3) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

Internal Clock Period

0.5 × TCCS RSKM SW RSKM 0.5 × TCCS

Figure 11–17. Cyclone II High-Speed I/O Timing Budget Note (1)

Note to Figure 11–17:

(1) The equation for the high-speed I/O timing budget is: Period = 0.5/TCCS + RSKM + SW + RSKM + 0.5/TCCS.

# Design Guidelines

This section provides guidelines for designing with Cyclone II devices.

#### **Differential Pad Placement Guidelines**

To maintain an acceptable noise level on the  $V_{\text{CCIO}}$  supply, there are restrictions on placement of single-ended I/O pins in relation to differential pads.

See the guidelines in the *Selectable I/O Standards in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook* for placing single-ended pads with respect to differential pads in Cyclone II devices.

## **Board Design Considerations**

This section explains how to get the optimal performance from the Cyclone II I/O interface and ensure first-time success in implementing a functional design with optimal signal quality. The critical issues of controlled impedance of traces and connectors, differential routing, and termination techniques must be considered to get the best performance from the IC. The Cyclone II device generates signals that travel over the media at frequencies as high as 805 Mbps. Use the following general guidelines for improved signal quality:

Base board designs on controlled differential impedance. Calculate and compare all parameters such as trace width, trace thickness, and the distance between two differential traces.

# Document Revision History

Table 11–6 shows the revision history for this document.

| Table 11–6. Document Revision History |                                                                                                                                                                                                                                                                                                                   |                                                                                                                                           |  |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date &<br>Document<br>Version         | Changes Made                                                                                                                                                                                                                                                                                                      | Summary of Changes                                                                                                                        |  |  |  |

| February 2007<br>v2.2                 | <ul> <li>Added document revision history.</li> <li>Added Note (1) to Table 11-1.</li> <li>Updated Figure 11-5 and added Note (1)</li> <li>Added Note (1) to Table 11-2.</li> <li>Updated Figure 11-6 and added Note (1)</li> <li>Added Note (1) to Table 11-3.</li> <li>Added Note (1) to Figure 11-9.</li> </ul> | Added information stating<br>LVDS/RSDS/mini-LVDS<br>I/O standards<br>specifications apply at the<br>external resistors network<br>output. |  |  |  |

| November 2005<br>v2.1                 | <ul> <li>Updated Table 11–2.</li> <li>Updated Figures 11–7 through 11–9.</li> <li>Added Resistor Network Solution for RSDS.</li> <li>Updated note for mini-LVDS Resistor Network table.</li> </ul>                                                                                                                |                                                                                                                                           |  |  |  |

| July 2005 v2.0                        | <ul> <li>Updated "I/O Standards Support" section.</li> <li>Updated Tables 11–1 through 11–3.</li> </ul>                                                                                                                                                                                                           |                                                                                                                                           |  |  |  |

| November 2004<br>v1.1                 | <ul> <li>Updated Table 11–1.</li> <li>Updated Figures 11–4, 11–5, 11–7, and 11–9.</li> </ul>                                                                                                                                                                                                                      |                                                                                                                                           |  |  |  |

| June 2004, v1.0                       | Added document to the Cyclone II Device Handbook.                                                                                                                                                                                                                                                                 |                                                                                                                                           |  |  |  |

the five common signals (nCONFIG, nSTATUS, DCLK, DATA0, and CONF\_DONE) between the cable and the configuration device. You can also remove the configuration device from the board when configuring the FPGA with the cable. Figure 13–21 shows a combination of a configuration device and a download cable to configure an FPGA.

USB Blaster, ByteBlaster II, V<sub>CC</sub> (1) MasterBlaster, or ByteBlasterMV 10-Pin Male Header Vcc 10 kO (Passive Serial Mode) **≲**10 kΩ Cyclone II FPGA Pin 1 (5) CONF DONE  $V_{CC}$ 10  $k\Omega$ MSEL0 nSTATUS **DCLK** MSEL1 마 nCEO -N.C. (6) nCE GND (3) (3) (3)DATA0 nCONFIG GŇD Configuration Device \((3) DCI K DATA OE (5) nCS (5) nINIT\_CONF (4)

Figure 13-21. PS Configuration with a Download Cable & Configuration Device Circuit

#### *Notes to Figure 13–21:*

- (1) The pull-up resistor should be connected to the same supply voltage as the configuration device.

- (2) Pin 6 of the header is a V<sub>IO</sub> reference voltage for the MasterBlaster output driver. V<sub>IO</sub> should match the device's V<sub>CCIO</sub>. Refer to the MasterBlaster Serial/USB Communications Cable Data Sheet for this value. In the ByteBlasterMV, this pin is a no connect. In the USB-Blaster and ByteBlaster II, this pin is connected to nCE when it is used for AS programming, otherwise it is a no connect.

- (3) You should not attempt configuration with a download cable while a configuration device is connected to a Cyclone II device. Instead, you should either remove the configuration device from its socket when using the download cable or place a switch on the five common signals between the download cable and the configuration device.

- (4) The ninit\_conf pin (available on enhanced configuration devices and EPC2 devices only) has an internal pull-up resistor that is always active. This means an external pull-up resistor should not be used on the ninit\_conf to nconfig line. The ninit\_conf pin does not need to be connected if its functionality is not used. If ninit\_conf is not used or not available (e.g., on EPC1 devices), nconfig must be pulled to V<sub>CC</sub> either directly or through a resistor (if reconfiguration is required, a resistor is necessary).

- (5) The enhanced configuration devices' OE and nCS pins have internal programmable pull-up resistors. If internal pull-up resistors are used, external pull-up resistors should not be used on these pins. The internal pull-up resistors are used by default in the Quartus II software. To turn off the internal pull-up resistors, check the **Disable nCS and OE pull-ups on configuration device** option when generating programming files.

- (6) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

frequency (up to 40 MHz), which reduces your configuration time. In addition, Cyclone II devices can receive a compressed configuration bitstream and decompress this data on-the-fly in the AS or PS configuration scheme, which further reduces storage requirements and configuration time.

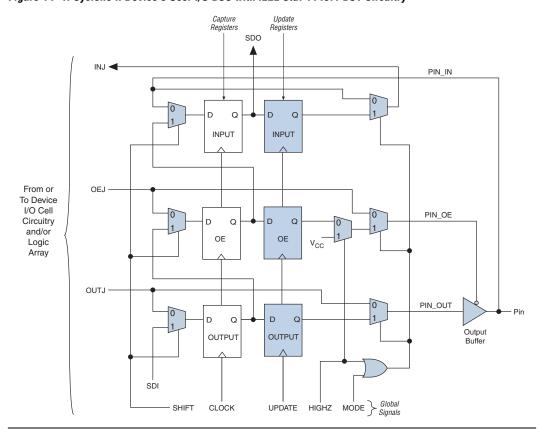

to external device data via the PIN\_IN signal, while the update registers connect to external data through the PIN\_OUT and PIN\_OE signals. The global control signals for the IEEE Std. 1149.1 BST registers (for example, shift, clock, and update) are generated internally by the TAP controller. The MODE signal is generated by a decode of the instruction register. The data signal path for the boundary-scan register runs from the serial data in (SDI) signal to the serial data out (SDO) signal. The scan register begins at the TDI pin and ends at the TDO pin of the device.

Figure 14–4 shows the Cyclone II device's user I/O boundary-scan cell.

Figure 14-4. Cyclone II Device's User I/O BSC with IEEE Std. 1149.1 BST Circuitry

EXTEST selects data differently than SAMPLE/PRELOAD. EXTEST chooses data from the update registers as the source of the output and output enable signals. Once the EXTEST instruction code is entered, the multiplexers select the update register data. Thus, data stored in these registers from a previous EXTEST or SAMPLE/PRELOAD test cycle can be forced onto the pin signals. In the capture phase, the results of this test data are stored in the capture registers, then shifted out of TDO during the shift phase. New test data can then be stored in the update registers during the update phase.

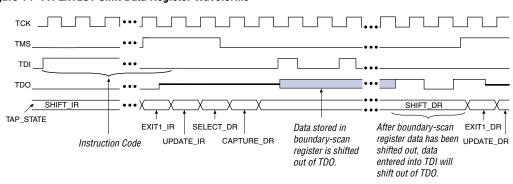

The EXTEST waveform diagram in Figure 14–11 resembles the SAMPLE/PRELOAD waveform diagram, except for the instruction code. The data shifted out of TDO consists of the data that was present in the capture registers after the capture phase. New test data shifted into the TDI pin appears at the TDO pin after being clocked through the entire boundary-scan register.

Figure 14-11. EXTEST Shift Data Register Waveforms

#### **BYPASS Instruction Mode**

The BYPASS mode is activated when an instruction code of all 1's is loaded in the instruction register. The waveforms in Figure 14–12 show how scan data passes through a device once the TAP controller is in the SHIFT\_DR state. In this state, data signals are clocked into the bypass register from TDI on the rising edge of TCK and out of TDO on the falling edge of the same clock pulse.

Tables 15–5 and 15–6 show the package information and package outline figure references, respectively, for the 144-pin TQFP package.

| Table 15–5. 144-Pin TQFP Package Information |                                                |  |  |

|----------------------------------------------|------------------------------------------------|--|--|

| Description Specification                    |                                                |  |  |

| Ordering code reference                      | Т                                              |  |  |

| Package acronym                              | TQFP                                           |  |  |

| Lead frame material                          | Copper                                         |  |  |

| Lead finish (plating)                        | Regular: 85Sn:15Pb (Typ.)<br>Pb-free: Matte Sn |  |  |

| JEDEC Outline Reference                      | MS-026 Variation: BFB                          |  |  |

| Maximum lead coplanarity                     | 0.003 inches (0.08mm)                          |  |  |

| Weight                                       | 1.3 g                                          |  |  |

| Moisture sensitivity level                   | Printed on moisture barrier bag                |  |  |

| Table 15–6. 144-Pin TQFP Package Outline Dimensions |                |           |      |  |  |

|-----------------------------------------------------|----------------|-----------|------|--|--|

| Country of                                          | Millimeter     |           |      |  |  |

| Symbol                                              | Min.           | Nom.      | Max. |  |  |

| Α                                                   | _              | _         | 1.60 |  |  |

| A1                                                  | 0.05           | -         | 0.15 |  |  |

| A2                                                  | 1.35           | 1.40      | 1.45 |  |  |

| D                                                   |                | 22.00 BSC |      |  |  |

| D1                                                  | 20.00 BSC      |           |      |  |  |

| E                                                   | 22.00 BSC      |           |      |  |  |

| E1                                                  |                | 20.00 BSC |      |  |  |

| L                                                   | 0.45 0.60 0.75 |           |      |  |  |

| L1                                                  | 1.00 REF       |           |      |  |  |

| S                                                   | 0.20 – –       |           |      |  |  |

| b                                                   | 0.17 0.22 0.27 |           |      |  |  |

| С                                                   | 0.09 – 0.20    |           |      |  |  |

| е                                                   | 0.50 BSC       |           |      |  |  |

| θ                                                   | 0° 3.5° 7°     |           |      |  |  |

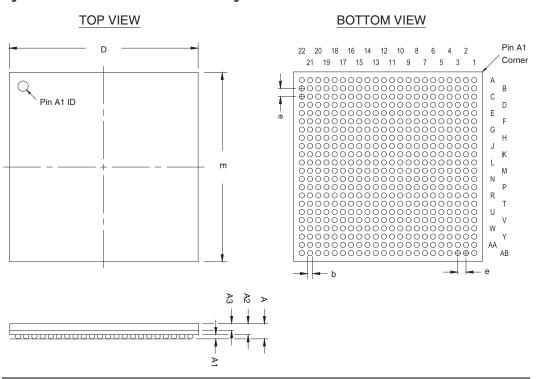

Figure 15–6 shows a 484-pin Ultra FineLine BGA package outline.

Figure 15-6. 484-Pin Ultra FineLine BGA Package Outline