Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 2076                                                     |

| Number of Logic Elements/Cells | 33216                                                    |

| Total RAM Bits                 | 483840                                                   |

| Number of I/O                  | 322                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 484-BGA                                                  |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c35f484c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

R24 row interconnects span 24 LABs and provide the fastest resource for long row connections between non-adjacent LABs, M4K memory blocks, dedicated multipliers, and row IOEs. R24 row interconnects drive to other row or column interconnects at every fourth LAB. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects and do not drive directly to LAB local interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

#### **Column Interconnects**

The column interconnect operates similar to the row interconnect. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs, M4K memory blocks, embedded multipliers, and row and column IOEs. These column resources include:

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four blocks in an up and down direction

- C16 interconnects for high-speed vertical routing through the device

Cyclone II devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using register chain connections. The register chain connection allows the register output of one LE to connect directly to the register input of the next LE in the LAB for fast shift registers. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–9 shows the register chain interconnects.

Each M4K block can implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and first-in first-out (FIFO) buffers. The M4K blocks support the following features:

- 4,608 RAM bits

- 250-MHz performance

- True dual-port memory

- Simple dual-port memory

- Single-port memory

- Byte enable

- Parity bits

- Shift register

- FIFO buffer

- ROM

- Various clock modes

- Address clock enable

Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

Table 2–5 shows the capacity and distribution of the M4K memory blocks in each Cyclone II device.

| Table 2–5. M4K Memory Capacity & Distribution in Cyclone II Devices |             |            |                |  |  |  |  |

|---------------------------------------------------------------------|-------------|------------|----------------|--|--|--|--|

| Device                                                              | M4K Columns | M4K Blocks | Total RAM Bits |  |  |  |  |

| EP2C5                                                               | 2           | 26         | 119,808        |  |  |  |  |

| EP2C8                                                               | 2           | 36         | 165,888        |  |  |  |  |

| EP2C15                                                              | 2           | 52         | 239,616        |  |  |  |  |

| EP2C20                                                              | 2           | 52         | 239,616        |  |  |  |  |

| EP2C35                                                              | 3           | 105        | 483,840        |  |  |  |  |

| EP2C50                                                              | 3           | 129        | 594,432        |  |  |  |  |

| EP2C70                                                              | 5           | 250        | 1,152,000      |  |  |  |  |

For Cyclone II devices, wake-up time consists of power-up, POR, configuration, and initialization. The device must properly go through all four stages to configure correctly and begin operation. You can calculate wake-up time using the following equation:

$Wake-Up\ Time = V_{CC}\ Ramp\ Time + POR\ Time + Configuration\ Time + Initialization\ Time$

Figure 4–3 illustrates the components of wake up time.

V<sub>CC</sub> Minimum

V<sub>CC</sub> Ramp

POR Time

Configuration Time

Initialization

Time

Mode

Figure 4-3. Cyclone II Wake-Up Time

*Note to Figure 4–3:*

(1)  $V_{CC}$  ramp must be monotonic.

The  $V_{CC}$  ramp time and POR time will depend on the device characteristics and the power supply used in your system. The fast-on devices require a maximum  $V_{CC}$  ramp time of 2 ms and have a maximum POR time of 12 ms.

Configuration time will depend on the configuration mode chosen and the configuration file size. You can calculate configuration time by multiplying the number of bits in the configuration file with the period of the configuration clock. For fast configuration times, you should use Passive Serial (PS) configuration mode with maximum DCLK frequency of 100 MHz. In addition, you can use compression to reduce the configuration file size and speed up the configuration time. The  $t_{\text{CD2UM}}$  or  $t_{\text{CD2UMC}}$  parameters will determine the initialization time.

For more information on the t<sub>CD2UM</sub> or t<sub>CD2UMC</sub> parameters, refer to the *Configuring Cyclone II Devices* chapter in the *Cyclone II Device Handbook*.

| I/O Standard    |                 | Ma                   | aximum               | Output (             | Clock To             | ggle Rat             | e Derati             | ing Facto                  | ors (ps/p            | ıF)                  |

|-----------------|-----------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------------|----------------------|----------------------|

|                 | Drive           | Column I/O Pins      |                      |                      | Row I/O Pins         |                      |                      | Dedicated Clock<br>Outputs |                      |                      |

|                 | Strength        | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade       | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade |

| SSTL_2_CLASS_I  | OCT_50<br>_OHMS | 67                   | 69                   | 70                   | 25                   | 42                   | 60                   | 25                         | 42                   | 60                   |

| SSTL_18_CLASS_I | OCT_50<br>OHMS  | 30                   | 33                   | 36                   | 47                   | 49                   | 51                   | 47                         | 49                   | 51                   |

#### **High Speed I/O Timing Specifications**

The timing analysis for LVDS, mini-LVDS, and RSDS is different compared to other I/O standards because the data communication is source-synchronous.

You should also consider board skew, cable skew, and clock jitter in your calculation. This section provides details on the timing parameters for high-speed I/O standards in Cyclone II devices.

Table 5–47 defines the parameters of the timing diagram shown in Figure 5–3.

| Table 5–47. High-Speed I/O Timing Definitions (Part 1 of 2) |                     |                                                                                                                                                                                                        |  |  |  |

|-------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter                                                   | Symbol              | Description                                                                                                                                                                                            |  |  |  |

| High-speed clock                                            | f <sub>HSCKLK</sub> | High-speed receiver and transmitter input and output clock frequency.                                                                                                                                  |  |  |  |

| Duty cycle                                                  | t <sub>DUTY</sub>   | Duty cycle on high-speed transmitter output clock.                                                                                                                                                     |  |  |  |

| High-speed I/O data rate                                    | HSIODR              | High-speed receiver and transmitter input and output data rate.                                                                                                                                        |  |  |  |

| Time unit interval                                          | TUI                 | TUI = 1/HSIODR.                                                                                                                                                                                        |  |  |  |

| Channel-to-channel skew                                     | TCCS                | The timing difference between the fastest and slowest output edges, including $t_{CO}$ variation and clock skew. The clock is included in the TCCS measurement.<br>TCCS = TUI – SW – $(2 \times RSKM)$ |  |  |  |

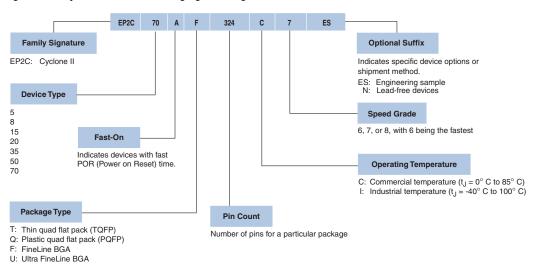

Figure 6-1. Cyclone II Device Packaging Ordering Information

## Document Revision History

Table 6–1 shows the revision history for this document.

| Table 6–1. Docu               | Table 6–1. Document Revision History                                              |                                                                                  |  |  |  |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|--|--|--|

| Date &<br>Document<br>Version | Changes Made                                                                      | Summary of Changes                                                               |  |  |  |  |  |  |

| February 2007<br>v1.5         | <ul> <li>Added document revision history.</li> <li>Updated Figure 6–1.</li> </ul> | Added Ultra FineLine BGA<br>detail in UBGA Package<br>information in Figure 6–1. |  |  |  |  |  |  |

| November 2005<br>v1.2         | Updated software introduction.                                                    |                                                                                  |  |  |  |  |  |  |

| November 2004<br>v1.1         | Updated Figure 6–1.                                                               |                                                                                  |  |  |  |  |  |  |

| June 2004 v1.0                | Added document to the Cyclone II Device Handbook.                                 |                                                                                  |  |  |  |  |  |  |

#### Input/Output Clock Mode

Cyclone II memory blocks can implement the input/output clock mode for true and simple dual-port memory. On each of the two ports, A and B, one clock controls all registers for the data, write enable, and address inputs into the memory block. The other clock controls the blocks' data output registers. Each memory block port also supports independent clock enables for input and output registers. Asynchronous clear signals for the registers are not supported.

Figures 8–14 through 8–16 show the memory block in input/output clock mode for true dual-port, simple dual-port, and single-port modes, respectively.

# Document Revision History

Table 8–8 shows the revision history for this document.

| Table 8–8. Document Revision History |                                                                                                                                                                                              |                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Date &<br>Document<br>Version        | Changes Made                                                                                                                                                                                 | Summary of Changes                                                                                                                                                                                                                    |  |  |  |  |  |  |

| February 2008<br>v2.4                | Corrected Figure 8–12.                                                                                                                                                                       | _                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| February 2007<br>v2.3                | <ul> <li>Added document revision history.</li> <li>Updated "Packed Mode Support" section.</li> <li>Updated "Mixed-Port Read-During-Write Mode" section and added new Figure 8–24.</li> </ul> | <ul> <li>In packed mode support,<br/>the maximum data width for<br/>each of the two memory<br/>block is 18 bits wide.</li> <li>Added don't care mode<br/>information to mixed-port<br/>read-during-write mode<br/>section.</li> </ul> |  |  |  |  |  |  |

| November 2005<br>v2.1                | Updated Figures 8–13 through 8–20.                                                                                                                                                           | _                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| July 2005 v2.0                       | Added Clear Signals section.                                                                                                                                                                 | _                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| February 2005<br>v1.1                | Added a note to Figures 8-13 through 8-20 regarding violating the setup and hold time on address registers.                                                                                  | _                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| June 2004 v1.0                       | Added document to the Cyclone II Device Handbook.                                                                                                                                            | _                                                                                                                                                                                                                                     |  |  |  |  |  |  |

#### **Conclusion**

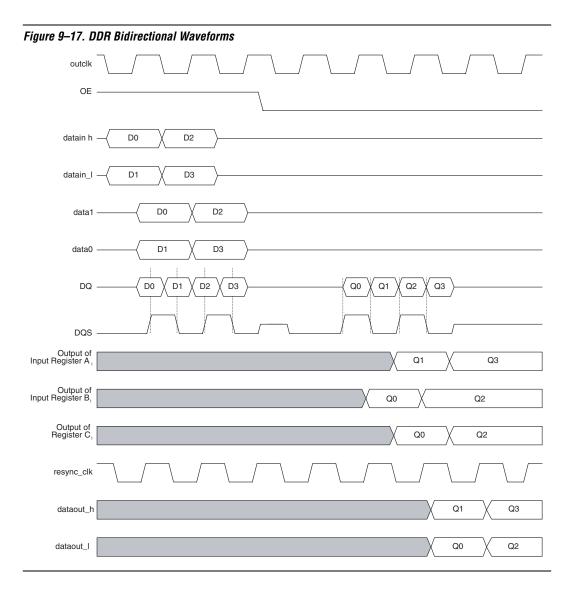

Cyclone II devices support SDR SDRAM, DDR SDRAM, DDR2 SDRAM, and QDRII SRAM external memories. Cyclone II devices feature high-speed interfaces that transfer data between external memory devices at up to 167 MHz/333 Mbps for DDR and DDR2 SDRAM devices and 167 MHz/667 Mbps for QDRII SRAM devices. The clock delay control circuitry allows you to fine tune the phase shift for the input clocks or strobes to properly align clock edges as needed to capture data.

For information about the I/O standards supported for external memory applications, refer to the *External Memory Interfaces* chapter in volume 1 of the *Cyclone II Device Handbook*.

| I/O Standard                   | Туре               | V <sub>CCIO</sub> Level |        | Top and<br>Bottom I/O<br>Pins |                  | Side I/O Pins |              |                  |

|--------------------------------|--------------------|-------------------------|--------|-------------------------------|------------------|---------------|--------------|------------------|

|                                |                    | Input                   | Output | CLK,<br>DQS                   | User I/O<br>Pins | CLK,<br>DQS   | PLL_OUT      | User I/O<br>Pins |

| 3.3-V LVTTL and LVCMOS         | Single ended       | 3.3 V/<br>2.5 V         | 3.3 V  | <b>✓</b>                      | ~                | <b>✓</b>      | <b>✓</b>     | <b>✓</b>         |

| 2.5-V LVTTL and LVCMOS         | Single ended       | 3.3 V/<br>2.5 V         | 2.5 V  | <b>✓</b>                      | ~                | <b>✓</b>      | <b>✓</b>     | <b>✓</b>         |

| 1.8-V LVTTL and LVCMOS         | Single ended       | 1.8 V/<br>1.5 V         | 1.8 V  | <b>✓</b>                      | ~                | <b>✓</b>      | <b>✓</b>     | <b>✓</b>         |

| 1.5-V LVCMOS                   | Single ended       | 1.8 V/<br>1.5 V         | 1.5 V  | <b>✓</b>                      | ~                | <b>✓</b>      | <b>✓</b>     | <b>✓</b>         |

| SSTL-2 class I                 | Voltage referenced | 2.5 V                   | 2.5 V  | <b>✓</b>                      | ~                | <b>✓</b>      | <b>✓</b>     | <b>✓</b>         |

| SSTL-2 class II                | Voltage referenced | 2.5 V                   | 2.5 V  | <b>✓</b>                      | ~                | <b>✓</b>      | <b>✓</b>     | <b>✓</b>         |

| SSTL-18 class I                | Voltage referenced | 1.8 V                   | 1.8 V  | ~                             | ~                | ~             | <b>✓</b>     | <b>✓</b>         |

| SSTL-18 class II               | Voltage referenced | 1.8 V                   | 1.8 V  | ~                             | ~                | (1)           | (1)          | (1)              |

| HSTL-18 class I                | Voltage referenced | 1.8 V                   | 1.8 V  | ~                             | ~                | ~             | <b>✓</b>     | <b>✓</b>         |

| HSTL-18 class II               | Voltage referenced | 1.8 V                   | 1.8 V  | ~                             | ~                | (1)           | (1)          | (1)              |

| HSTL-15 class I                | Voltage referenced | 1.5 V                   | 1.5 V  | <b>✓</b>                      | ~                | <b>✓</b>      | <b>✓</b>     | <b>✓</b>         |

| HSTL-15 class II               | Voltage referenced | 1.5 V                   | 1.5 V  | ~                             | ~                | (1)           | (1)          | (1)              |

| PCI and PCI-X (2)              | Single ended       | 3.3 V                   | 3.3 V  | _                             | _                | <b>✓</b>      | <b>✓</b>     | ~                |

| Differential SSTL-2 class I or | Pseudo             | (4)                     | 2.5 V  | _                             | _                | _             | <b>✓</b>     | _                |

| class II                       | differential (3)   | 2.5 V                   | (4)    | <b>(</b> 5)                   | _                | <b>(</b> 5)   | _            | _                |

| Differential SSTL-18 class I   | Pseudo             | (4)                     | 1.8 V  | _                             | _                |               | <b>√</b> (6) | _                |

| or class II                    | differential (3)   | 1.8 V                   | (4)    | <b>√</b> (5)                  | _                | <b>(</b> 5)   | _            | _                |

After applying the equation above, apply one of the equations in Table 10–11, depending on the package type.

| Table 10–11. Bidirectional Pad Limitation Formulas (Multiple $V_{REF}$ Inputs and Outputs) |                                                                                              |  |  |  |  |  |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|

| Package Type                                                                               | Formula                                                                                      |  |  |  |  |  |

| FineLine BGA                                                                               | (Total number of bidirectional pads) + (Total number of output pads) ≤9 (per VCCIO/GND pair) |  |  |  |  |  |

| QFP                                                                                        | Total number of bidirectional pads + Total number of output pads ≤5 (per VCCIO/GND pair)     |  |  |  |  |  |

Each I/O bank can only be set to a single  $V_{\rm CCIO}$  voltage level and a single  $V_{\rm REF}$  voltage level at a given time. Pins of different I/O standards can share the bank if they have compatible  $V_{\rm CCIO}$  values (refer to Table 10–4 for more details) and compatible  $V_{\rm REF}$  voltage levels.

#### DDR and QDR Pads

For dedicated DQ and DQS pads on a DDR interface, DQ pads have to be on the same power bank as DQS pads. With the DDR and DDR2 memory interfaces, a VCCIO and ground pair can have a maximum of five DQ pads.

For a QDR interface, D is the QDR output and Q is the QDR input. D pads and Q pads have to be on the same power bank as CQ. With the QDR and QDRII memory interfaces, a VCCIO and ground pair can have a maximum of five D and Q pads.

By default, the Quartus II software assigns D and Q pads as regular I/O pins. If you do not specify the function of a D or Q pad in the Quartus II software, the software sets them as regular I/O pins. If this occurs, Cyclone II QDR and QDRII performance is not guaranteed.

#### **DC** Guidelines

There is a current limit of 240 mA per eight consecutive output top and bottom pins per power pair, as shown by the following equation:

```

pin+7

\Sigma I<sub>PIN</sub> < 240mA per power pair

pin

```

There is a current limit of 240 mA per 12 consecutive output side (left and right) pins per power pair, as shown by the following equation:

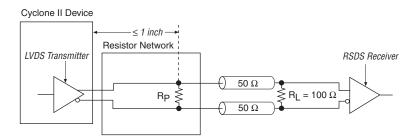

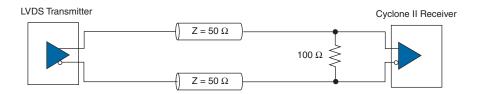

Figure 11–8. RSDS Single Resistor Network Note (1)

Note to Figure 11–8: (1)  $R_p = 100 \Omega$

#### RSDS Software Support

When designing for the RSDS I/O standard, assign the RSDS I/O standard to the I/O pins intended for RSDS in the Quartus® II software. Contact Altera Applications for reference designs.

#### mini-LVDS Standard Support in Cyclone II Devices

The mini-LVDS specification defines its use in chip-to-chip applications between the timing controller and the column drivers on display panels. Cyclone II devices meet the Texas Instruments mini-LVDS Interface Specification and support the mini-LVDS output standard. Table 11–3 shows the mini-LVDS electrical characteristics for Cyclone II devices.

| Table 11–3. mini-LVDS Electrical Characteristics for Cyclone II Devices         Note (1) |                             |                        |       |      |       |       |  |  |  |

|------------------------------------------------------------------------------------------|-----------------------------|------------------------|-------|------|-------|-------|--|--|--|

| Symbol                                                                                   | Parameters                  | Condition              | Min   | Тур  | Max   | Units |  |  |  |

| V <sub>CCIO</sub>                                                                        | Output supply voltage       |                        | 2.375 | 2.5  | 2.625 | V     |  |  |  |

| V <sub>OD</sub> (2)                                                                      | Differential output voltage | R <sub>L</sub> = 100 Ω | 300   |      | 600   | mV    |  |  |  |

| V <sub>OS</sub> (3)                                                                      | Output offset voltage       | $R_L = 100 \Omega$     | 1125  | 1250 | 1375  | mV    |  |  |  |

| T <sub>r</sub> / T <sub>f</sub>                                                          | Transition time             | 20% to 80%             |       |      | 500   | ps    |  |  |  |

*Notes to Table 11–3:*

- (1) The  $V_{OD}$  specifications apply at the resistor network output.

- $(2) V_{OD} = V_{OH} V_{OL}.$

- (3)  $V_{OS} = (V_{OH} + V_{OL}) / 2$ .

Figure 11-11. LVPECL I/O Interface

#### **Differential SSTL Support in Cyclone II Devices**

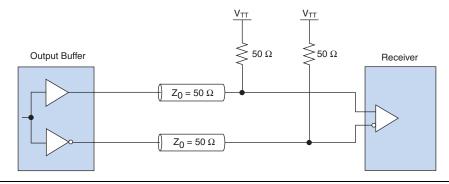

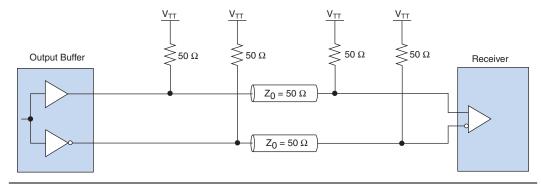

The differential SSTL I/O standard is a memory bus standard used for applications such as high-speed double data rate (DDR) SDRAM interfaces. The differential SSTL I/O standard is similar to voltage referenced SSTL and requires two differential inputs with an external termination voltage (V $_{\rm TT}$ ) of 0.5  $\times$  V $_{\rm CCIO}$  to which termination resistors are connected. A 2.5-V output source voltage is required for differential SSTL-2, while a 1.8-V output source voltage is required for differential SSTL-18. The differential SSTL output standard is only supported at PLLCLKOUT pins using two single-ended SSTL output buffers programmed to have opposite polarity.

The differential SSTL input standard is supported at the global clock (GCLK) pins only, treating differential inputs as two single-ended SSTL, and only decoding one of them.

For SSTL signaling characteristics, see the *DC Characteristics & Timing Specification* chapter and the *Selectable I/O Standards in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

Figures 11–12 and 11–13 show the differential SSTL class I and II interfaces, respectively.

Figures 11–14 and 11–15 show differential HSTL class I and II interfaces, respectively.

Figure 11-14. Differential HSTL Class I Interface

Figure 11-15. Differential HSTL Class II Interface

### High-Speed I/O Timing in Cyclone II Devices

This section discusses the timing budget, waveforms, and specifications for source-synchronous signaling in Cyclone II devices. LVDS, LVPECL, RSDS, and mini-LVDS I/O standards enable high-speed data transmission. Timing for these high-speed signals is based on skew between the data and the clock signals.

High-speed differential data transmission requires timing parameters provided by integrated circuit (IC) vendors and requires consideration of board skew, cable skew, and clock jitter. This section provides details on high-speed I/O standards timing parameters in Cyclone II devices.

Figure 13–1. Enabling Compression for Cyclone II Bitstreams in Compiler Settings

You can also use the following steps to enable compression when creating programming files from the Convert Programming Files window.

- 1. Click **Convert Programming Files** (File menu).

- 2. Select the Programming File type. Only Programmer Object Files (.pof), SRAM HEXOUT, RBF, or TTF files support compression.

- 3. For POFs, select a configuration device.

- 4. Select **Add File** and add a Cyclone II SRAM Object File(s) (.sof).

- 5. Select the name of the file you added to the SOF Data area and click on **Properties**.

- 6. Check the **Compression** check box.

You should put a buffer before the DATA and DCLK output from the master Cyclone II device to avoid signal strength and signal integrity issues. The buffer should not significantly change the DATA-to-DCLK relationships or delay them with respect to other AS signals (ASDI and nCS). Also, the buffer should only drive the slave Cyclone II devices, so that the timing between the master Cyclone II device and serial configuration device is unaffected.

This configuration method supports both compressed and uncompressed SOFs. Therefore, if the configuration bitstream size exceeds the capacity of a serial configuration device, you can enable the compression feature in the SOF file used or you can select a larger serial configuration device.

#### **Estimating AS Configuration Time**

The AS configuration time is the time it takes to transfer data from the serial configuration device to the Cyclone II device. The Cyclone II DCLK output (generated from an internal oscillator) clocks this serial interface. As listed in Table 13–5, if you are using the 40-MHz oscillator, the DCLK minimum frequency is 20 MHz (50 ns). Therefore, the maximum configuration time estimate for an EP2C5 device (1,223,980 bits of uncompressed data) is:

RBF size × (maximum DCLK period / 1 bit per DCLK cycle) = estimated maximum configuration time

$1,223,980 \text{ bits} \times (50 \text{ ns} / 1 \text{ bit}) = 61.2 \text{ ms}$

To estimate the typical configuration time, use the typical DCLK period listed in Table 13–5. With a typical DCLK period of 38.46 ns, the typical configuration time is 47.1 ms. Enabling compression reduces the amount of configuration data that is transmitted to the Cyclone II device, which also reduces configuration time. On average, compression reduces configuration time by 50%.

| Table 13–11. | Dedicated    | d Configuration         | Pins on the Cyc          | lone II Device (Part 3 of 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|--------------|-------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name     | User<br>Mode | Configuration<br>Scheme | Pin Type                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CONF_DONE    | N/A          | All                     | Bidirectional open-drain | This pin is a status output and input. The target Cyclone II device drives the <code>CONF_DONE</code> pin low before and during configuration. Once the Cyclone II device receives all the configuration data without error and the initialization cycle starts, it releases <code>CONF_DONE</code> . Driving <code>CONF_DONE</code> low during user mode does not affect the configured device. Do not drive <code>CONF_DONE</code> low before the device enters user mode.  After the Cyclone II device receives all the data, the <code>CONF_DONE</code> pin transitions high, and the device initializes and enters user mode. The <code>CONF_DONE</code> pin must have an external $10\text{-}k\Omega$ pull-up resistor in order for the device to initialize.  Driving <code>CONF_DONE</code> low after configuration and initialization does not affect the configured device.  The enhanced configuration devices' and <code>EPC2</code> devices' <code>OE</code> and <code>nCS</code> pins are connected to the Cyclone II device's <code>nSTATUS</code> and <code>CONF_DONE</code> pins, respectively, and have optional internal programmable pull-up resistors. If internal pull-up resistors on the enhanced configuration device are used, external $10\text{-}k\Omega$ pull-up resistors should not be used on these pins. When using <code>EPC2</code> devices, you should only use external $10\text{-}k\Omega$ pull-up resistors.  The input buffer on this pin supports hysteresis using <code>Schmitt</code> trigger circuitry. |

| nCE          | N/A          | All                     | Input                    | This pin is an active-low chip enable. The nCE pin activates the device with a low signal to allow configuration. The nCE pin must be held low during configuration, initialization, and user mode. In single device configuration, it should be tied low. In multiple device configuration, nCE of the first device is tied low while its nCEO pin is connected to nCE of the next device in the chain.  The nCE pin must also be held low for successful JTAG programming of the FPGA.  The input buffer on this pin supports hysteresis using Schmitt trigger circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 13–11. | Dedicated    | d Configuration         | Pins on the Cyd           | Table 13–11. Dedicated Configuration Pins on the Cyclone II Device (Part 5 of 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|--------------|--------------|-------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Pin Name     | User<br>Mode | Configuration<br>Scheme | Pin Type                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| DCLK         | N/A          | PS,<br>AS               | Input (PS)<br>Output (AS) | In PS configuration, DCLK is the clock input used to clock data from an external source into the target device. Data is latched into the Cyclone II device on the rising edge of DCLK.  In AS mode, DCLK is an output from the Cyclone II device that provides timing for the configuration interface. In AS mode, DCLK has an internal pull-up that is always active.  After configuration, this pin is tri-stated. If you are using a configuration device, it drives DCLK low after configuration is complete. If your design uses a control host, drive DCLK either high or low. Toggling this pin after configuration does not affect the configured device. |  |  |  |  |  |  |  |  |  |

|              |              |                         |                           | The input buffer on this pin supports hysteresis using Schmitt trigger circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| DATA0        | N/A          | All                     | Input                     | This is the data input pin. In serial configuration modes, bit-wide configuration data is presented to the target device on the DATAO pin.  In AS mode, DATAO has an internal pull-up resistor that is always active.  After configuration, EPC1 and EPC1441 devices tri-state this pin, while enhanced configuration and EPC2 devices drive this pin high.  The input buffer on this pin supports hysteresis using Schmitt trigger circuitry.                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

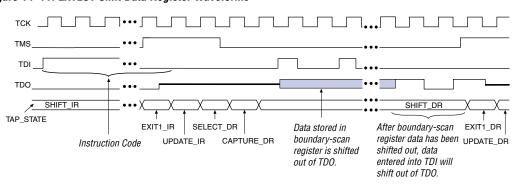

EXTEST selects data differently than SAMPLE/PRELOAD. EXTEST chooses data from the update registers as the source of the output and output enable signals. Once the EXTEST instruction code is entered, the multiplexers select the update register data. Thus, data stored in these registers from a previous EXTEST or SAMPLE/PRELOAD test cycle can be forced onto the pin signals. In the capture phase, the results of this test data are stored in the capture registers, then shifted out of TDO during the shift phase. New test data can then be stored in the update registers during the update phase.

The EXTEST waveform diagram in Figure 14–11 resembles the SAMPLE/PRELOAD waveform diagram, except for the instruction code. The data shifted out of TDO consists of the data that was present in the capture registers after the capture phase. New test data shifted into the TDI pin appears at the TDO pin after being clocked through the entire boundary-scan register.

Figure 14-11. EXTEST Shift Data Register Waveforms

#### **BYPASS Instruction Mode**

The BYPASS mode is activated when an instruction code of all 1's is loaded in the instruction register. The waveforms in Figure 14–12 show how scan data passes through a device once the TAP controller is in the SHIFT\_DR state. In this state, data signals are clocked into the bypass register from TDI on the rising edge of TCK and out of TDO on the falling edge of the same clock pulse.

## Thermal Resistance

Thermal resistance values for Cyclone II devices are provided for a board meeting JEDEC specifications and for a typical board. The values provided are as follows:

- θ<sub>JA</sub> (°C/W) Still Air—Junction-to-ambient thermal resistance with no airflow when a heat sink is not being used.

- $\theta_{JA}$  (° C/W) 100 ft./minute—Junction-to-ambient thermal resistance with 100 ft./minute airflow when a heat sink is not being used.

- $\theta_{JA}$  (° C/W) 200 ft./minute—Junction-to-ambient thermal resistance with 200 ft./minute airflow when a heat sink is not being used.

- $\theta_{JA}$  (° C/W) 400 ft./minute—Junction-to-ambient thermal resistance with 400 ft./minute airflow when a heat sink is not being used.

- $\theta_{IC}$  (°C/W)—Junction-to-case thermal resistance for device.

- $\theta_{JB}$  (° C/W)—Junction-to-board thermal resistance for specific board being used.

Table 15–2 provides  $\theta_{JA}$  (junction-to-ambient thermal resistance) values and  $\theta_{JC}$  (junction-to-case thermal resistance) values for Cyclone II devices on a board meeting JEDEC specifications for thermal resistance calculation. The JEDEC board specifications require two signal and two power/ground planes and are available at **www.jedec.org**.

| Table 15- | Table 15–2. Thermal Resistance of Cyclone II Devices for Board Meeting JEDEC Specifications (Part 1 of 2) |                    |                                      |                                         |      |                                         |                            |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------|-----------------------------------------|------|-----------------------------------------|----------------------------|--|--|--|--|

| Device    | Pin<br>Count                                                                                              | Package            | θ <sub>JA</sub> (° C/W)<br>Still Air | θ <sub>JA</sub> (° C/W)<br>100 ft./min. | • ,  | θ <sub>JA</sub> (° C/W)<br>400 ft./min. | θ <sub>JC</sub><br>(° C/W) |  |  |  |  |

| EP2C5     | 144                                                                                                       | TQFP               | 31                                   | 29.3                                    | 27.9 | 25.5                                    | 10                         |  |  |  |  |

|           | 208                                                                                                       | PQFP               | 30.4                                 | 29.2                                    | 27.3 | 22.3                                    | 5.5                        |  |  |  |  |

|           | 256                                                                                                       | FineLine BGA       | 30.2                                 | 26.1                                    | 23.6 | 21.7                                    | 8.7                        |  |  |  |  |

| EP2C8     | 144                                                                                                       | TQFP               | 29.8                                 | 28.3                                    | 26.9 | 24.9                                    | 9.9                        |  |  |  |  |

|           | 208                                                                                                       | PQFP               | 30.2                                 | 28.8                                    | 26.9 | 21.7                                    | 5.4                        |  |  |  |  |

|           | 256                                                                                                       | FineLine BGA       | 27                                   | 23                                      | 20.5 | 18.5                                    | 7.1                        |  |  |  |  |

| EP2C15    | 256                                                                                                       | FineLine BGA       | 24.2                                 | 20                                      | 17.8 | 16                                      | 5.5                        |  |  |  |  |

|           | 484                                                                                                       | FineLine BGA       | 21                                   | 17                                      | 14.8 | 13.1                                    | 4.2                        |  |  |  |  |

| EP2C20    | 240                                                                                                       | PQFP               | 26.6                                 | 24                                      | 21.4 | 17.4                                    | 4.2                        |  |  |  |  |

|           | 256                                                                                                       | FineLine BGA       | 24.2                                 | 20                                      | 17.8 | 16                                      | 5.5                        |  |  |  |  |

|           | 484                                                                                                       | FineLine BGA       | 21                                   | 17                                      | 14.8 | 13.1                                    | 4.2                        |  |  |  |  |

| EP2C35    | 484                                                                                                       | FineLine BGA       | 19.4                                 | 15.4                                    | 13.3 | 11.7                                    | 3.3                        |  |  |  |  |

|           | 484                                                                                                       | Ultra FineLine BGA | 20.6                                 | 16.6                                    | 14.5 | 12.8                                    | 5                          |  |  |  |  |

|           | 672                                                                                                       | FineLine BGA       | 18.6                                 | 14.6                                    | 12.6 | 11.1                                    | 3.1                        |  |  |  |  |

# Document Revision History

Table 15–21 shows the revision history for this document.

| Table 15–21. Document Revision History |                                                   |                    |

|----------------------------------------|---------------------------------------------------|--------------------|

| Date &<br>Document<br>Version          | Changes Made                                      | Summary of Changes |

| February 2007<br>v2.3                  | Added document revision history.                  |                    |

| November 2005<br>v2.1                  | Updated information throughout.                   |                    |

| July 2005 v2.0                         | Updated packaging information.                    |                    |

| November 2004<br>v1.0                  | Added document to the Cyclone II Device Handbook. |                    |