Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 2076                                                     |

| Number of Logic Elements/Cells | 33216                                                    |

| Total RAM Bits                 | 483840                                                   |

| Number of I/O                  | 322                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 484-BGA                                                  |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c35f484i8n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| clkena signals                                   | 7–29 |

|--------------------------------------------------|------|

| Board Layout                                     |      |

| VCCA & GNDA                                      | 7–31 |

| VCCD & GND                                       | 7–33 |

| Conclusion                                       | 7–33 |

|                                                  |      |

|                                                  |      |

| Section III. Memory                              |      |

| Revision History                                 | 7–1  |

| Chapter 8. Cyclone II Memory Blocks              |      |

| Introduction                                     | Q 1  |

| Overview                                         |      |

| Control Signals                                  |      |

| Parity Bit Support                               |      |

| Byte Enable Support                              |      |

| Packed Mode Support                              |      |

| Address Clock Enable                             |      |

| Memory Modes                                     |      |

| Single-Port Mode                                 |      |

| Simple Dual-Port Mode                            |      |

| True Dual-Port Mode                              | 8–12 |

| Shift Register Mode                              | 8–14 |

| ROM Mode                                         |      |

| FIFO Buffer Mode                                 | 8–16 |

| Clock Modes                                      |      |

| Independent Clock Mode                           |      |

| Input/Output Clock Mode                          |      |

| Read/Write Clock Mode                            |      |

| Single-Clock Mode                                |      |

| Power-Up Conditions & Memory Initialization      |      |

| Read-During- Write Operation at the Same Address |      |

| Same-Port Read-During-Write Mode                 |      |

| Mixed-Port Read-During-Write Mode                |      |

| Conclusion                                       |      |

| Referenced Documents                             | 8–30 |

| Chapter 9. External Memory Interfaces            |      |

| Introduction                                     |      |

| External Memory Interface Standards              | 9–2  |

| DDR & DDR2 SDRAM                                 | 9–2  |

| QDRII SRAM                                       |      |

| Cyclone II DDR Memory Support Overview           | 9–9  |

| Data & Data Strobe Pins                          |      |

| Clock, Command & Address Pins                    |      |

| Parity, DM & ECC Pins                            | 9–14 |

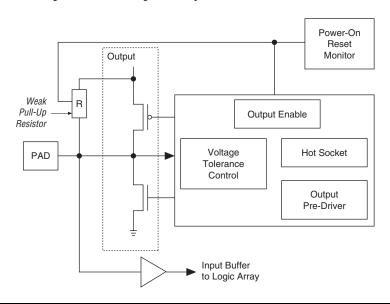

Figure 4–1. Hot-Socketing Circuit Block Diagram for Cyclone II Devices

The POR circuit monitors  $V_{CCINT}$  voltage level and keeps I/O pins tri-stated until the device is in user mode. The weak pull-up resistor (R) from the I/O pin to  $V_{CCIO}$  keeps the I/O pins from floating. The voltage tolerance control circuit permits the I/O pins to be driven by 3.3 V before  $V_{CCIO}$  and/or  $V_{CCINT}$  are powered, and it prevents the I/O pins from driving out when the device is not in user mode.

For more information, see the *DC Characteristics & Timing Specifications* chapter in Volume 1 of the *Cyclone II Device Handbook* for the value of the internal weak pull-up resistors.

Figure 4–2 shows a transistor level cross section of the Cyclone II device I/O buffers. This design ensures that the output buffers do not drive when  $V_{\text{CCIO}}$  is powered before  $V_{\text{CCINT}}$  or if the I/O pad voltage is higher than  $V_{\text{CCIO}}.$  This also applies for sudden voltage spikes during hot socketing. The  $V_{\text{PAD}}$  leakage current charges the voltage tolerance control circuit capacitance.

| Table 5–7. DC Characteristics of User I/O Pins Using Single-Ended Standards Notes (1), (2) (Part 2 of 2) |                      |                      |                             |                             |  |  |

|----------------------------------------------------------------------------------------------------------|----------------------|----------------------|-----------------------------|-----------------------------|--|--|

| I/O Ctondoud                                                                                             | Test Co              | nditions             | Voltage Thresholds          |                             |  |  |

| I/O Standard                                                                                             | I <sub>OL</sub> (mA) | I <sub>OH</sub> (mA) | Maximum V <sub>OL</sub> (V) | Minimum V <sub>OH</sub> (V) |  |  |

| 1.5-V HSTL class I                                                                                       | 8                    | -8                   | 0.4                         | V <sub>CCIO</sub> - 0.4     |  |  |

| 1.5V HSTL class II                                                                                       | 16                   | -16                  | 0.4                         | V <sub>CCIO</sub> - 0.4     |  |  |

#### Notes to Table 5-7:

- (1) The values in this table are based on the conditions listed in Tables 5–2 and 5–6.

- (2) This specification is supported across all the programmable drive settings available as shown in the Cyclone II Architecture chapter of the Cyclone II Device Handbook.

## Differential I/O Standards

The RSDS and mini-LVDS I/O standards are only supported on output pins. The LVDS I/O standard is supported on both receiver input pins and transmitter output pins.

For more information on how these differential I/O standards are implemented, refer to the *High-Speed Differential Interfaces in Cyclone II Devices* chapter of the *Cyclone II Device Handbook*.

Figure 5–1 shows the receiver input waveforms for all differential I/O standards (LVDS, LVPECL, differential 1.5-V HSTL class I and II, differential 1.8-V HSTL class I and II, differential SSTL-2 class I and II, and differential SSTL-18 class I and II).

Table 5–8 shows the recommended operating conditions for user I/O pins with differential I/O standards.

| Table 5–8.                                          | Table 5–8. Recommended Operating Conditions for User I/O Pins Using Differential Signal I/O Standards |         |            |      |                     |                         | ards                                |                            |                                     |     |                         |                            |      |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------|------------|------|---------------------|-------------------------|-------------------------------------|----------------------------|-------------------------------------|-----|-------------------------|----------------------------|------|

| I/O                                                 | V                                                                                                     | ccio (V | <b>'</b> ) | V    | I <sub>ID</sub> (V) | (1)                     |                                     | V <sub>ICM</sub> (V)       |                                     | VII | _ (V)                   | V <sub>IH</sub> (V)        |      |

| Standard                                            | Min                                                                                                   | Тур     | Max        | Min  | Тур                 | Max                     | Min                                 | Тур                        | Max                                 | Min | Max                     | Min                        | Max  |

| LVDS                                                | 2.375                                                                                                 | 2.5     | 2.625      | 0.1  | _                   | 0.65                    | 0.1                                 | _                          | 2.0                                 | _   | _                       | _                          | _    |

| Mini-LVDS                                           | 2.375                                                                                                 | 2.5     | 2.625      |      | _                   | _                       | _                                   | _                          | _                                   | _   | _                       | _                          | _    |

| RSDS (2)                                            | 2.375                                                                                                 | 2.5     | 2.625      |      | _                   | _                       | _                                   | _                          | _                                   | _   | _                       | _                          | _    |

| LVPECL (3) (6)                                      | 3.135                                                                                                 | 3.3     | 3.465      | 0.1  | 0.6                 | 0.95                    | _                                   | _                          | _                                   | 0   | 2.2                     | 2.1                        | 2.88 |

| Differential<br>1.5-V HSTL<br>class I<br>and II (4) | 1.425                                                                                                 | 1.5     | 1.575      | 0.2  |                     | V <sub>CCIO</sub> + 0.6 | 0.68                                | _                          | 0.9                                 | _   | V <sub>REF</sub> – 0.20 | V <sub>REF</sub><br>+ 0.20 |      |

| Differential<br>1.8-V HSTL<br>class I<br>and II (4) | 1.71                                                                                                  | 1.8     | 1.89       |      |                     | _                       | _                                   | _                          | _                                   |     | V <sub>REF</sub> – 0.20 | V <sub>REF</sub><br>+ 0.20 |      |

| Differential<br>SSTL-2<br>class I<br>and II (5)     | 2.375                                                                                                 | 2.5     | 2.625      | 0.36 | _                   | V <sub>CCIO</sub> + 0.6 | 0.5 ×<br>V <sub>CCIO</sub><br>- 0.2 | 0.5 ×<br>V <sub>CCIO</sub> | 0.5 ×<br>V <sub>CCIO</sub><br>+ 0.2 | _   | V <sub>REF</sub> – 0.35 | V <sub>REF</sub> + 0.35    |      |

| Differential<br>SSTL-18<br>class I<br>and II (5)    | 1.7                                                                                                   | 1.8     | 1.9        | 0.25 | _                   | V <sub>CCIO</sub> + 0.6 | 0.5 ×<br>V <sub>CCIO</sub><br>- 0.2 | 0.5 ×<br>V <sub>CCIO</sub> | 0.5 ×<br>V <sub>CCIO</sub><br>+ 0.2 | _   | V <sub>REF</sub> – 0.25 | V <sub>REF</sub><br>+ 0.25 | _    |

#### Notes to Table 5-8:

- Refer to the High-Speed Differential Interfaces in Cyclone II Devices chapter of the Cyclone II Device Handbook for measurement conditions on V<sub>ID</sub>.

- (2) The RSDS and mini-LVDS I/O standards are only supported on output pins.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock

- (5) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (6) The LVPECL clock inputs are powered by V<sub>CCINT</sub> and support all V<sub>CCIO</sub> settings. However, it is recommended to connect V<sub>CCIO</sub> to typical value of 3.3V.

Table 5–19. M4K Block Internal Timing Microparameters (Part 2 of 3) -6 Speed Grade (1) -7 Speed Grade (2) -8 Speed Grade (3) Parameter Unit Min Max Min Max Min Max TM4KBEH 234 267 267 ps 250 267 ps TM4KDATAASU 35 46 46 ps 40 46 ps TM4KDATAAH 234 267 267 ps 250 267 ps TM4KADDRASU 35 46 46 ps 40 46 ps TM4KADDRAH 234 267 267 ps 250 267 ps TM4KDATABSU 35 46 46 ps 40 46 ps TM4KDATABH 234 267 267 ps 250 267 ps TM4KRADDRBSU 46 35 46 ps 40 46 ps TM4KRADDRBH 234 267 267 ps 250 267 ps TM4KDATACO1 724 445 826 445 930 466 ps 466 466 ps 2345 TM4KDATACO2 3680 2234 4157 2234 4636 ps 2345 2345 ps TM4KCLKH 1923 2769 2769 ps 2307 2769 ps ps TM4KCLKL 1923 2769 2769 2307 2769 ps

| Table 5-37                       | Table 5–37. Cyclone II IOE Programmable Delay on Row Pins Notes (1), (2) (Part 2 of 2) |                |                 |               |                   |               |                              |               |                |               |      |

|----------------------------------|----------------------------------------------------------------------------------------|----------------|-----------------|---------------|-------------------|---------------|------------------------------|---------------|----------------|---------------|------|

| Parameter                        | . Paths                                                                                |                | Fast Corner (3) |               | –6 Speed<br>Grade |               | –7 Speed<br>Grade <i>(4)</i> |               | -8 Speed Grade |               | Unit |

| ratameter                        | Affected                                                                               | of<br>Settings | Min<br>Offset   | Max<br>Offset | Min<br>Offset     | Max<br>Offset | Min<br>Offset                | Max<br>Offset | Min<br>Offset  | Max<br>Offset | UIII |

| Input Delay                      | Pad ->                                                                                 | 8              | 0               | 2669          | 0                 | 4482          | 0                            | 4834          | 0              | 4859          | ps   |

| from Pin to<br>Input<br>Register | I/O input<br>register                                                                  |                | 0               | 2802          | _                 |               | 0                            | 4671          | _              | _             | ps   |

| Delay from                       | I/O                                                                                    | 2              | 0               | 308           | 0                 | 572           | 0                            | 648           | 0              | 682           | ps   |

| Output Register to Output Pin    | output<br>register -<br>> Pad                                                          |                | 0               | 324           | _                 | _             | 0                            | 626           | _              | _             | ps   |

#### Notes to Table 5–37:

- The incremental values for the settings are generally linear. For exact values of each setting, use the latest version

of the Quartus II software.

- (2) The minimum and maximum offset timing numbers are in reference to setting "0" as available in the Quartus II software.

- (3) The value in the first row represents the fast corner timing parameter for industrial and automotive devices. The second row represents the fast corner timing parameter for commercial devices.

- (4) The value in the first row is for automotive devices. The second row is for commercial devices.

## Default Capacitive Loading of Different I/O Standards

Refer to Table 5–38 for default capacitive loading of different I/O standards.

| Table 5–38. Default Loading of Different I/O Standards for Cyclone II Device (Part 1 of 2) |                 |      |  |  |  |

|--------------------------------------------------------------------------------------------|-----------------|------|--|--|--|

| I/O Standard                                                                               | Capacitive Load | Unit |  |  |  |

| LVTTL                                                                                      | 0               | pF   |  |  |  |

| LVCMOS                                                                                     | 0               | pF   |  |  |  |

| 2.5V                                                                                       | 0               | pF   |  |  |  |

| 1.8V                                                                                       | 0               | pF   |  |  |  |

| 1.5V                                                                                       | 0               | pF   |  |  |  |

| PCI                                                                                        | 10              | pF   |  |  |  |

| PCI-X                                                                                      | 10              | pF   |  |  |  |

| SSTL_2_CLASS_I                                                                             | 0               | pF   |  |  |  |

| SSTL_2_CLASS_II                                                                            | 0               | pF   |  |  |  |

| SSTL_18_CLASS_I                                                                            | 0               | pF   |  |  |  |

| IADIE 5-45. MAXIMUM | Table 5-45. Maximum Output Clock Toggle Rate on Cyclone II Devices (Part 3 of 4)  Maximum Output Clock Toggle Rate on Cyclone II Devices (MUS) |                                                                                 |                      |                      |                      |                      |                      |                      | M11=/                   |                      |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-------------------------|----------------------|--|

| I/O Standard        | Drive                                                                                                                                          | Maximum Output Clock Toggle Rate on Cyclo  Column I/O Pins (1) Row I/O Pins (1) |                      |                      |                      |                      |                      | l                    | Dedicated Clock Outputs |                      |  |

| ,                   | Strength                                                                                                                                       | -6<br>Speed<br>Grade                                                            | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade    | –8<br>Speed<br>Grade |  |

| SSTL_18_ CLASS_II   | 16 mA                                                                                                                                          | 260                                                                             | 220                  | 180                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

|                     | 18 mA                                                                                                                                          | 270                                                                             | 220                  | 180                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| 1.8V_HSTL_ CLASS_I  | 8 mA                                                                                                                                           | 260                                                                             | 220                  | 180                  | 260                  | 220                  | 180                  | 260                  | 220                     | 180                  |  |

|                     | 10 mA                                                                                                                                          | 300                                                                             | 250                  | 210                  | 300                  | 250                  | 210                  | 300                  | 250                     | 210                  |  |

|                     | 12 mA                                                                                                                                          | 320                                                                             | 270                  | 220                  | 320                  | 270                  | 220                  | 320                  | 270                     | 220                  |  |

| 1.8V_HSTL_ CLASS_II | 16 mA                                                                                                                                          | 230                                                                             | 190                  | 160                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

|                     | 18 mA                                                                                                                                          | 240                                                                             | 200                  | 160                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

|                     | 20 mA                                                                                                                                          | 250                                                                             | 210                  | 170                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| 1.5V_HSTL_ CLASS_I  | 8 mA                                                                                                                                           | 210                                                                             | 170                  | 140                  | 210                  | 170                  | 140                  | 210                  | 170                     | 140                  |  |

|                     | 10 mA                                                                                                                                          | 220                                                                             | 180                  | 150                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

|                     | 12 mA                                                                                                                                          | 230                                                                             | 190                  | 160                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| 1.5V_HSTL_ CLASS_II | 16 mA                                                                                                                                          | 210                                                                             | 170                  | 140                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| DIFFERENTIAL_       | 8 mA                                                                                                                                           | 400                                                                             | 340                  | 280                  | 400                  | 340                  | 280                  | 400                  | 340                     | 280                  |  |

| SSTL_2_CLASS_I      | 12 mA                                                                                                                                          | 400                                                                             | 340                  | 280                  | 400                  | 340                  | 280                  | 400                  | 340                     | 280                  |  |

| DIFFERENTIAL_       | 16 mA                                                                                                                                          | 350                                                                             | 290                  | 240                  | 350                  | 290                  | 240                  | 350                  | 290                     | 240                  |  |

| SSTL_2_CLASS_II     | 20 mA                                                                                                                                          | 400                                                                             | 340                  | 280                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

|                     | 24 mA                                                                                                                                          | 400                                                                             | 340                  | 280                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| DIFFERENTIAL_       | 6 mA                                                                                                                                           | 260                                                                             | 220                  | 180                  | 260                  | 220                  | 180                  | 260                  | 220                     | 180                  |  |

| SSTL_18_CLASS_I     | 8 mA                                                                                                                                           | 260                                                                             | 220                  | 180                  | 260                  | 220                  | 180                  | 260                  | 220                     | 180                  |  |

|                     | 10 mA                                                                                                                                          | 270                                                                             | 220                  | 180                  | 270                  | 220                  | 180                  | 270                  | 220                     | 180                  |  |

|                     | 12 mA                                                                                                                                          | 280                                                                             | 230                  | 190                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| DIFFERENTIAL_SSTL   | 16 mA                                                                                                                                          | 260                                                                             | 220                  | 180                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| _18_CLASS_II        | 18 mA                                                                                                                                          | 270                                                                             | 220                  | 180                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| 1.8V_               | 8 mA                                                                                                                                           | 260                                                                             | 220                  | 180                  | 260                  | 220                  | 180                  | 260                  | 220                     | 180                  |  |

| DIFFERENTIAL_HSTL   | 10 mA                                                                                                                                          | 300                                                                             | 250                  | 210                  | 300                  | 250                  | 210                  | 300                  | 250                     | 210                  |  |

| _CLASS_I            | 12 mA                                                                                                                                          | 320                                                                             | 270                  | 220                  | 320                  | 270                  | 220                  | 320                  | 270                     | 220                  |  |

| 1.8V_               | 16 mA                                                                                                                                          | 230                                                                             | 190                  | 160                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| DIFFERENTIAL_HSTL   | 18 mA                                                                                                                                          | 240                                                                             | 200                  | 160                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| _CLASS_II           | 20 mA                                                                                                                                          | 250                                                                             | 210                  | 170                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

Tables 7–4 and 7–5 describe the Cyclone II PLL input and output ports.

| Port      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Source                     | Destination        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------|

| inclk[10] | Primary and secondary clock inputs to the PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Dedicated clock input pins | n counter          |

| pllena    | pllena is an active high signal that acts as an enable and reset signal for the PLL. It can be used for enabling or disabling each PLL. When pllena transitions low, the PLL clock output ports are driven to GND and the PLL loses lock. Once pllena transitions high again, the lock process begins and the PLL re-synchronizes to its input reference clock. The pllena port can be driven by an LE output or any general-purpose I/O pin.                                                                                                                            | Logic array or input pin   | PLL control signal |

| areset    | areset is an active high signal that resets all PLL counters to their initial values. When this signal is driven high the PLL resets its counters, clears the PLL outputs and loses lock. Once this signal is driven low again, the lock process begins and the PLL re-synchronizes to its input reference clock. The areset port can be driven by an LE output or any general-purpose I/O pin.                                                                                                                                                                          | Logic array or input pin   | PLL control signal |

| pfdena    | pfdena is an active high signal that enables or disables the up/down output signals from the PFD. When pfdena is driven low, the PFD is disabled, while the VCO continues to operate. The PLL clock outputs continue to toggle regardless of the input clock, but may experience some long-term drift. Because the output clock frequency does not change for some time, you can use the pfdena port as a shutdown or cleanup function when a reliable input clock is no longer available. The pfdena port can be driven by an LE output or any general-purpose I/O pin. | Logic array or input pin   | PFD                |

| clkswitch | clkswitch is an active high switchover signal used to initiate manual clock switchover.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Logic array or input pin   | PLL control signal |

## **Phase-Shifting Implementation**

Cyclone II devices use fine or coarse phase shifts for clock delays because they are more efficient than delay elements and are independent of process, voltage, and temperature.

Phase shift is implemented by using a combination of the VCO phase output and the counter starting time. The VCO phase taps and counter starting time are independent of process, voltage, and temperature. The VCO phase taps allow you to phase shift the Cyclone II PLL output clocks with fine resolution. The counter starting time allows you to phase shift the Cyclone II PLL output clocks with coarse resolution.

Fine-resolution phase shifting is implemented using any of the eight VCO phases for the output counters (c[2..0]) or the feedback counter (m) reference clock. This provides the finest resolution for phase shift. The minimum delay time that may be inserted using this method is defined by the equation:

$$\Delta t_{\text{FINE}} = \frac{1}{8} t_{\text{VCO}} = \frac{1}{8 \times f_{\text{VCO}}} = \frac{n}{8 \times m \times f_{\text{IN}}}$$

f<sub>IN</sub> is input reference clock frequency.

For example, if  $f_{\rm IN}$  is 100 MHz, n is 1 and m is 8, then  $f_{\rm VCO}$  is 800 MHz and  $\Delta t$  is 156.25 ps. This delay time is defined by the PLL operating frequency which is governed by the reference clock and the counter settings.

The second way to implement phase shifts is by delaying the start of the m and post-scale counters for a predetermined number of counter clocks. This delay time may be expressed as:

$$\Delta t_{\text{COARSE}} = \frac{S-1}{f_{\text{VCO}}} = \frac{(S-1) \times n}{m \times f_{\text{IN}}}$$

where S is the value set for the counter starting time. The counter starting time is called the **Initial** setting in the PLL Usage section of the compilation report in the Quartus II software.

Figure 7–8 shows an example of delay insertion using these two methods. The eight phases from the VCO are shown and labeled for reference. For this example, <code>OUTCLKO</code> is based off the 0° phase from the VCO and has the S value for the counter set to 1. It is divided by 4 (two VCO clocks for high time and two VCO clocks for low time). <code>OUTCLK1</code> is based off the 135° phase tap from the VCO and also has the S value for the counter set to 1. It is also divided by 4. In this case, the two clocks are offset by three

The DQS pins are listed in the Cyclone II pin tables as DQS[1..0]T, DQS[1..0]B, DQS[1..0]B, DQS[1..0]B, and DQS[1..0]B for the EP2C5 and EP2C8 devices and DQS[5..0]T, DQS[5..0]B, DQS[3..0]L, and DQS[3..0]B for the larger devices. The T denotes pins on the top of the device, the B denotes pins on the bottom of the device, the L denotes pins on the left of the device, and the R denotes pins on the right of the device. The corresponding DQ pins are marked as DQ[5..0]T[8..0], where [5..0] indicates which DQS group the pins belong to.

In the Cyclone II pinouts, the DQ groups with 9 DQ pins are also used in the  $\times 8$  mode with the corresponding DQS pins, leaving the unused DQ pin available as a regular I/O pin. The DQ groups that have 18 DQ pins are also used in the  $\times 16$  mode with the corresponding DQS pins, leaving the two unused DQ pins available as regular I/O pins. For example, DQ1T[8..0] can be used in the  $\times 8$  mode, provided it is used with DQS1T. The remaining unused DQ pin, DQ1T8, is available as a regular I/O pin.

When not used as DQ or DQS pins, these pins are available as regular I/O pins. Table 9–3 shows the number of DQS pins supported in each I/O bank in each Cyclone II device density.

| Table 9–3. Available DQS Pins in Each I/O Bank & Each Device   Note (1) |              |                 |               |                |  |  |  |

|-------------------------------------------------------------------------|--------------|-----------------|---------------|----------------|--|--|--|

| Device                                                                  | Top I/O Bank | Bottom I/O Bank | Left I/O Bank | Right I/O Bank |  |  |  |

| EP2C5, EP2C8                                                            | DQS[10]T     | DQS[10]B        | DQS[10]L      | DQS[10]R       |  |  |  |

| EP2C15, EP2C20,<br>EP2C35, EP2C50,<br>EP2C70                            | DQS[50]B     | DQS[50]T        | DQS[30]L      | DQS[30]R       |  |  |  |

Note to Table 9-3:

(1) Numbers are preliminary.

The DQ pin numbering is based on ×8/×9 mode. There are up to 8 DQS/DQ groups in ×8 mode or 4 DQS/DQ groups in ×9 mode in I/O banks for EP2C5 and EP2C8. For the larger devices, there are up to 20 DQS/DQ groups in ×8 mode or 8 DQS/DQ groups in ×9 mode. Although there are up to 20 DQS/DQ groups in the ×8 mode available in the larger Cyclone II devices, but because of the available clock resources in the Cyclone II devices, only 16 DQS/DQ groups can be utilized for the external memory interface. There is a total of 16 global clock buses available for routing DQS signals but 2 of them are needed for routing the –90° write clock and the system clock to the external memory devices. This reduces the global clock resources to 14 global clock buses for routing DQS signals. Incoming DQS signals are all routed to the clock control block, and are then routed to the global clock bus to clock the DDR LE registers. For EP2C5 and EP2C8 devices, the DQS signals are routed

| Table 10–6. Programmable Drive Strength (Part 2 of 2) |                                                                |               |  |  |  |  |

|-------------------------------------------------------|----------------------------------------------------------------|---------------|--|--|--|--|

| I/O Standard                                          | I <sub>OH</sub> /I <sub>OL</sub> Current Strength Setting (mA) |               |  |  |  |  |

| I/O Standard                                          | Top and Bottom I/O Pins                                        | Side I/O Pins |  |  |  |  |

| SSTL-2 class I                                        | 8                                                              | 8             |  |  |  |  |

|                                                       | 12                                                             | 12            |  |  |  |  |

| SSTL-2 class II                                       | 16                                                             | 16            |  |  |  |  |

|                                                       | 20                                                             | _             |  |  |  |  |

|                                                       | 24                                                             | _             |  |  |  |  |

| SSTL-18 class I                                       | 6                                                              | 6             |  |  |  |  |

|                                                       | 8                                                              | 8             |  |  |  |  |

|                                                       | 10                                                             | 10            |  |  |  |  |

|                                                       | 12                                                             | _             |  |  |  |  |

| SSTL-18 class II                                      | 16                                                             | _             |  |  |  |  |

|                                                       | 18                                                             | _             |  |  |  |  |

| HSTL-18 class I                                       | 8                                                              | 8             |  |  |  |  |

|                                                       | 10                                                             | 10            |  |  |  |  |

|                                                       | 12                                                             | 12            |  |  |  |  |

| HSTL-18 class II                                      | 16                                                             | N/A           |  |  |  |  |

|                                                       | 18                                                             | _             |  |  |  |  |

|                                                       | 20                                                             | _             |  |  |  |  |

| HSTL-15 class I                                       | 8                                                              | 8             |  |  |  |  |

|                                                       | 10                                                             | _             |  |  |  |  |

|                                                       | 12                                                             | _             |  |  |  |  |

| HSTL-15 class II                                      | 16                                                             | N/A           |  |  |  |  |

These drive-strength settings are programmable on a per-pin basis using the Quartus II software.

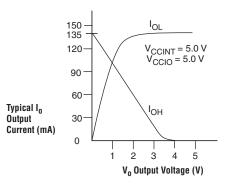

Figure 10–22. Output Drive Characteristics of a 5.0-V Device

As shown above,  $R_1 = 5.0$ -V/135 mA.

The values shown in data sheets usually reflect typical operating conditions. Subtract 20% from the data sheet value for guard band. This subtraction when applied in the example in Figure 10–22 gives  $R_{\rm 1}$  a value of 30  $\Omega$

$R_2$  should be selected so that it does not violate the driving device's  $I_{OH}$  specification. For example, if the device has a maximum  $I_{OH}$  of 8 mA, given that the PCI clamping diode,  $V_{IN} = V_{CCIO} + 0.7 - V = 3.7 - V$ , and the maximum supply load of a 5.0-V device ( $V_{CC}$ ) is 5.25-V, the value of  $R_2$  can be calculated as follows:

$$R_2 = \frac{(5.25 \text{ V} - 3.7 \text{ V}) - (8 \text{ mA} \times 30 \Omega)}{8 \text{ mA}} = 164 \Omega$$

This analysis assumes worst case conditions. If your system does not have a wide variation in voltage-supply levels, you can adjust these calculations accordingly.

Because 5.0-V device tolerance in Cyclone II devices requires use of the PCI clamp, and this clamp is activated during configuration, 5.0-V signals may not be driven into the device until it is configured.

## Conclusion

Cyclone II device I/O capabilities enable you to keep pace with increasing design complexity utilizing a low-cost FPGA device family. Support for I/O standards including SSTL and LVDS compatibility allow Cyclone II devices to fit into a wide variety of applications. The Quartus II

## Configuration Stage

After the Cyclone II device's nSTATUS pin transitions high, the MAX II device should send the configuration data on the DATAO pin one bit at a time. If you are using configuration data in RBF, HEX, or TTF format, send the least significant bit (LSB) of each data byte first. For example, if the RBF contains the byte sequence 02 1B EE 01 FA, you should transmit the serial bitstream 0100-0000 1101-1000 0111-0111 1000-0000 0101-1111 to the device first.

The Cyclone II device receives configuration data on its DATAO pin and the clock on the DCLK pin. Data is latched into the FPGA on the rising edge of DCLK. Data is continuously clocked into the target device until the CONF\_DONE pin transitions high. After the Cyclone II device receives all the configuration data successfully, it releases the open-drain CONF\_DONE pin, which is pulled high by an external  $10\text{-k}\Omega$  pull-up resistor. A low-to-high transition on CONF\_DONE indicates configuration is complete and initialization of the device can begin. The CONF\_DONE pin must have an external  $10\text{-k}\Omega$  pull-up resistor in order for the device to initialize.

The configuration clock (DCLK) speed must be below the specified system frequency (see Table 13–7) to ensure correct configuration. No maximum DCLK period exists, which means you can pause configuration by halting DCLK for an indefinite amount of time.

### Initialization Stage

In Cyclone II devices, the initialization clock source is either the Cyclone II internal oscillator (typically 10 MHz) or the optional CLKUSR pin. The internal oscillator is the default clock source for initialization. If you use the internal oscillator, the Cyclone II device makes sure to provide enough clock cycles for proper initialization. Therefore, if the internal oscillator is the initialization clock source, sending the entire configuration file to the device is sufficient to configure and initialize the device. You do not need to provide additional clock cycles externally during the initialization stage. Driving DCLK back to the device after configuration is complete does not affect device operation. Additionally, if you use the internal oscillator as the clock source, you can use the CLKUSR pin as a user I/O pin.

If you want to delay the initialization of the device, you can use the CLKUSR pin. Using the CLKUSR pin allows you to control when your device enters user mode. You can delay the device from entering user mode for an indefinite amount of time.

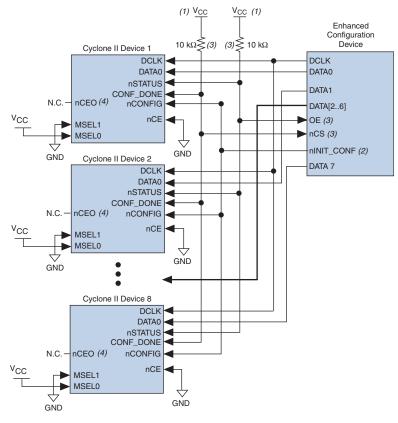

Figure 13–15. Concurrent PS Configuration of Multiple Devices Using an Enhanced Configuration Device

#### *Notes to Table 13–15:*

- (1) The pull-up resistor should be connected to the same supply voltage as the configuration device.

- (2) The ninit\_conf pin is available on enhanced configuration devices and has an internal pull-up resistor that is always active, meaning an external pull-up resistor should not be used on the ninit\_conf to nconfig line. The ninit\_conf pin does not need to be connected if its functionality is not used. If ninit\_conf is not used, nconfig must be pulled to V<sub>CC</sub> either directly or through a resistor (if reconfiguration is required, a resistor is necessary).

- (3) The enhanced configuration devices' OE and nCS pins have internal programmable pull-up resistors. If internal pull-up resistors are used, external pull-up resistors should not be used on these pins. The internal pull-up resistors are used by default in the Quartus II software. To turn off the internal pull-up resistors, check the **Disable nCS and OE pull-ups on configuration device** option when generating programming files.

- (4) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

The Quartus II software only allows you to set n to 1, 2, 4, or 8. However, you can use these modes to configure any number of devices from 1 to 8. For example, if you configure three FPGAs, you would use the 4-bit PS mode. For the DATA0, DATA1, and DATA2 lines, the corresponding SOF data is transmitted from the configuration device to the FPGA. For

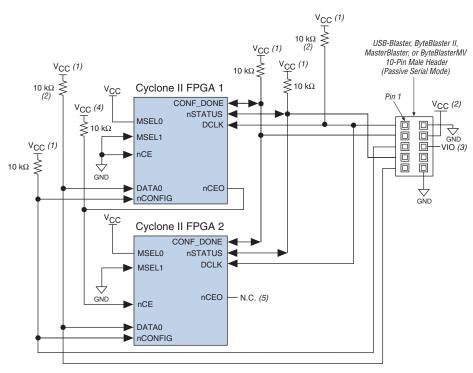

Quartus II programmer and a download cable. Figure 13–19 shows the PS configuration for Cyclone II devices using a USB-Blaster, MasterBlaster, ByteBlaster II or ByteBlasterMV cable.

10 kΩ V<sub>CC</sub> (1) **≤**10 kΩ ≤10 kΩ Cyclone II Device CONF DONE MSEL0 USB-Blaster, ByteBlaster II, MSEL1 MasterBlaster. nCEO - N.C. (4) nCE or ByteBlasterMV 10-Pin Male Header DCI K Pin 1 DATA0 **nCONFIG** VIO (3) 回

Figure 13-19. PS Configuration Using a USB-Blaster, MasterBlaster, ByteBlaster II or ByteBlasterMV Cable

#### Notes to Figure 13-19:

- (1) The pull-up resistor should be connected to the same supply voltage as the USB-Blaster, MasterBlaster (VIO pin), ByteBlaster II, or ByteBlasterMV cable.

- (2) The pull-up resistors on DATAO and DCLK are only needed if the download cable is the only configuration scheme used on your board. This is to ensure that DATAO and DCLK are not left floating after configuration. For example, if you are also using a configuration device, the pull-up resistors on DATAO and DCLK are not needed.

- (3) Pin 6 of the header is a V<sub>IO</sub> reference voltage for the MasterBlaster output driver. V<sub>IO</sub> should match the device's V<sub>CCIO</sub>. Refer to the MasterBlaster Serial/USB Communications Cable Data Sheet for this value. In the ByteBlasterMV, this pin is a no connect. In the USB-Blaster and ByteBlaster II, this pin is connected to nCE when it is used for AS programming, otherwise it is a no connect.

- (4) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

You can use a download cable to configure multiple Cyclone II devices by connecting each device's nCEO pin to the subsequent device's nCE pin. Connect the first Cyclone II device's nCE pin to GND and connect its nCEO pin to the nCE pin of the next device in the chain. Use an external 10-k $\Omega$  pull-up resistor to pull the nCEO pin high to  $V_{CCIO}$  when it feeds next device's nCE pin. Connect all other configuration pins (nCONFIG, nSTATUS, DCLK, DATAO, and CONF\_DONE) on every device in the chain together. Because all CONF\_DONE pins are connected, all devices in the chain initialize and enter user mode at the same time.

Shield GND

Figure 13–20. Multiple Device PS Configuration Using a USB-Blaster, MasterBlaster, ByteBlaster II or ByteBlasterMV Cable

#### *Notes to Figure 13–20:*

- (1) The pull-up resistor should be connected to the same supply voltage as the USB-Blaster, MasterBlaster (VIO pin), ByteBlaster II, or ByteBlasterMV cable.

- (2) The pull-up resistors on DATAO and DCLK are only needed if the download cable is the only configuration scheme used on your board. This is to ensure that DATAO and DCLK are not left floating after configuration. For example, if you are also using a configuration device, the pull-up resistors on DATAO and DCLK are not needed.

- (3) Pin 6 of the header is a V<sub>IO</sub> reference voltage for the MasterBlaster output driver. V<sub>IO</sub> should match the device's V<sub>CCIO</sub>. Refer to the MasterBlaster Serial/USB Communications Cable Data Sheet for this value. In the ByteBlasterMV, this pin is a no connect. In the USB-Blaster and ByteBlaster II, this pin is connected to nCE when it is used for AS programming, otherwise it is a no connect.

- (4) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of I/O bank that the nCEO pin resides in.

- (5) The nCEO pin of the last device in chain can be left unconnected or used as a user I/O pin.

If you are using a download cable to configure Cyclone II devices on a PCB that also has configuration devices, you should electrically isolate the configuration devices from the target Cyclone II devices and cable. One way to isolate the configuration device is to add logic, such as a multiplexer, that can select between the configuration device and the cable. The multiplexer should allow bidirectional transfers on the nstatus and configuration. Additionally, you can add switches to

| Table 13–11. | Table 13–11. Dedicated Configuration Pins on the Cyclone II Device (Part 4 of 5) |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|--------------|----------------------------------------------------------------------------------|-------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name     | User<br>Mode                                                                     | Configuration<br>Scheme | Pin Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| nCEO         | N/A if option is on. I/O if option is off.                                       | All                     | Output   | This pin is an output that drives low when device configuration is complete. In single device configuration, you can leave this pin floating or use it as a user I/O pin after configuration. In multiple device configuration, this pin inputs the next device's $n\text{CE}$ pin. The $n\text{CEO}$ of the last device in the chain can be left floating or used as a user I/O pin after configuration. If you use the $n\text{CEO}$ pin to feed next device's $n\text{CE}$ pin, use an external 10-k $\Omega$ pull-up resistor to pull the $n\text{CEO}$ pin high to the $V_{\text{CCIO}}$ voltage of its I/O bank to help the internal weak pull-up resistor. |  |  |  |  |

|              |                                                                                  |                         |          | Use the Quartus II software to make this pin a user I/O pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| ASDO         | N/A in<br>AS<br>mode<br>I/O in<br>PS and<br>JTAG<br>mode                         | AS                      | Output   | This pin sends a control signal from the Cyclone II device to the serial configuration device in AS mode and is used to read out configuration data.  In AS mode, ASDO has an internal pull-up that is always active.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| nCSO         | N/A in<br>AS<br>mode<br>I/O in<br>PS and<br>JTAG<br>mode                         | AS                      | Output   | This pin sends an output control signal from the Cyclone II device to the serial configuration device in AS mode that enables the configuration device.  In AS mode, nCSO has an internal pull-up resistor that is always active.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

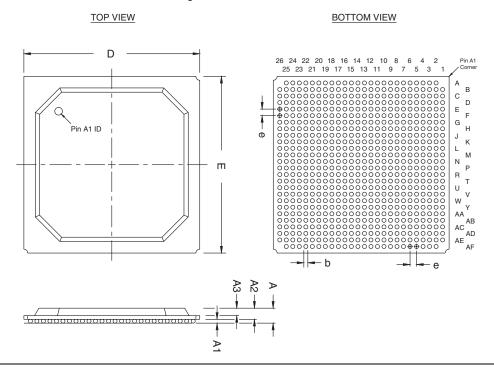

Figure 15–7 shows a 672-pin FineLine BGA package outline.

Figure 15-7. 672-Pin FineLine BGA Package Outline

# Document Revision History

Table 15–21 shows the revision history for this document.

| Table 15–21. Document Revision History |                                                   |                    |  |  |  |

|----------------------------------------|---------------------------------------------------|--------------------|--|--|--|

| Date &<br>Document<br>Version          | Changes Made                                      | Summary of Changes |  |  |  |

| February 2007<br>v2.3                  | Added document revision history.                  |                    |  |  |  |

| November 2005<br>v2.1                  | Updated information throughout.                   |                    |  |  |  |

| July 2005 v2.0                         | Updated packaging information.                    |                    |  |  |  |

| November 2004<br>v1.0                  | Added document to the Cyclone II Device Handbook. |                    |  |  |  |