Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 2076                                                     |

| Number of Logic Elements/Cells | 33216                                                    |

| Total RAM Bits                 | 483840                                                   |

| Number of I/O                  | 475                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 672-BGA                                                  |

| Supplier Device Package        | 672-FBGA (27x27)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c35f672c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Internal Timing                                                                                                                                                                                                                                                                                                                                                                                                         | 5–18                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Cyclone II Clock Timing Parameters                                                                                                                                                                                                                                                                                                                                                                                      |                                                 |

| Clock Network Skew Adders                                                                                                                                                                                                                                                                                                                                                                                               |                                                 |

| IOE Programmable Delay                                                                                                                                                                                                                                                                                                                                                                                                  | 5–30                                            |

| Default Capacitive Loading of Different I/O Standards                                                                                                                                                                                                                                                                                                                                                                   | 5–31                                            |

| I/O Delays                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

| Maximum Input and Output Clock Rate                                                                                                                                                                                                                                                                                                                                                                                     |                                                 |

| High Speed I/O Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |

| External Memory Interface Specifications                                                                                                                                                                                                                                                                                                                                                                                | 5–63                                            |

| JTAG Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

| PLL Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                               | 5–66                                            |

| Duty Cycle Distortion                                                                                                                                                                                                                                                                                                                                                                                                   |                                                 |

| DCD Measurement Techniques                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

| Referenced Documents                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                               |                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |

| Chapter 6. Reference & Ordering Information                                                                                                                                                                                                                                                                                                                                                                             |                                                 |

| Software                                                                                                                                                                                                                                                                                                                                                                                                                | 6–1                                             |

| Device Pin-Outs                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |

| Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                               |                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |

| Section II Clack Management                                                                                                                                                                                                                                                                                                                                                                                             |                                                 |

| Section II. Clock Management Revision History                                                                                                                                                                                                                                                                                                                                                                           | 6–1                                             |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 6–1                                             |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 6–1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices                                                                                                                                                                                                                                                                                                                                                                 |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction                                                                                                                                                                                                                                                                                                                                                   | 7–1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction  Cyclone II PLL Hardware Overview                                                                                                                                                                                                                                                                                                                 | 7–1<br>7–2                                      |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 7–1<br>7–2<br>7–6                               |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 7–1<br>7–2<br>7–6                               |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        |                                                 |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 7–1<br>7–2<br>7–10<br>7–10<br>7–10<br>7–11      |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode                                                                                                                                                                                                       | 7–17–27–67–107–117–12                           |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        |                                                 |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction  Cyclone II PLL Hardware Overview  PLL Reference Clock Generation  Clock Feedback Modes  Normal Mode  Zero Delay Buffer Mode  No Compensation Mode  Source-Synchronous Mode  Hardware Features  Clock Multiplication & Division                                                                                                                   |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle                                                                                                     |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation                                                                       |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals                                                       | 7-1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover                               | 7-1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover Clocking                      | 7-1 7-2 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover Clocking Global Clock Network | 7-1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover Clocking                      | 7-1 7-2 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 |

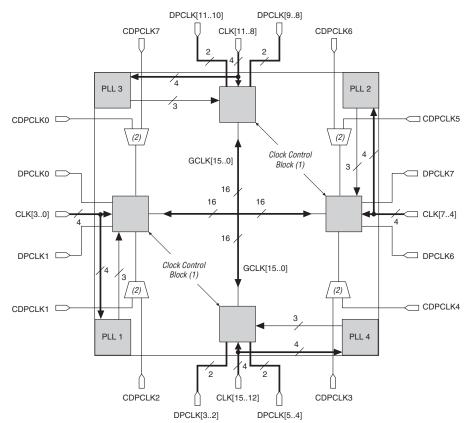

Figure 2-12. EP2C15 & Larger PLL, CLK[], DPCLK[] & Clock Control Block Locations

#### Notes to Figure 2–12:

- (1) There are four clock control blocks on each side.

- (2) Only one of the corner CDPCLK pins in each corner can feed the clock control block at a time. The other CDPCLK pins can be used as general-purpose I/O pins.

Embedded multipliers can operate at up to 250 MHz (for the fastest speed grade) for  $18 \times 18$  and  $9 \times 9$  multiplications when using both input and output registers.

Each Cyclone II device has one to three columns of embedded multipliers that efficiently implement multiplication functions. An embedded multiplier spans the height of one LAB row. Table 2–10 shows the number of embedded multipliers in each Cyclone II device and the multipliers that can be implemented.

| Table 2–10. Number of Embedded Multipliers in Cyclone II Devices Note (1) |                                |                         |                     |     |  |  |  |  |

|---------------------------------------------------------------------------|--------------------------------|-------------------------|---------------------|-----|--|--|--|--|

| Device                                                                    | Embedded<br>Multiplier Columns | Embedded<br>Multipliers | 18 × 18 Multipliers |     |  |  |  |  |

| EP2C5                                                                     | 1                              | 13                      | 26                  | 13  |  |  |  |  |

| EP2C8                                                                     | 1                              | 18                      | 36                  | 18  |  |  |  |  |

| EP2C15                                                                    | 1                              | 26                      | 52                  | 26  |  |  |  |  |

| EP2C20                                                                    | 1                              | 26                      | 52                  | 26  |  |  |  |  |

| EP2C35                                                                    | 1                              | 35                      | 70                  | 35  |  |  |  |  |

| EP2C50                                                                    | 2                              | 86                      | 172                 | 86  |  |  |  |  |

| EP2C70                                                                    | 3                              | 150                     | 300                 | 150 |  |  |  |  |

*Note to Table 2–10:*

The embedded multiplier consists of the following elements:

- Multiplier block

- Input and output registers

- Input and output interfaces

Figure 2–18 shows the multiplier block architecture.

<sup>(1)</sup> Each device has either the number of  $9 \times 9$ -, or  $18 \times 18$ -bit multipliers shown. The total number of multipliers for each device is not the sum of all the multipliers.

The reduced swing differential signaling (RSDS) and mini-LVDS standards are derivatives of the LVDS standard. The RSDS and mini-LVDS I/O standards are similar in electrical characteristics to LVDS, but have a smaller voltage swing and therefore provide increased power benefits and reduced electromagnetic interference (EMI). Cyclone II devices support the RSDS and mini-LVDS I/O standards at data rates up to 311 Mbps at the transmitter.

A subset of pins in each I/O bank (on both rows and columns) support the high-speed I/O interface. The dual-purpose LVDS pins require an external-resistor network at the transmitter channels in addition to 100- $\Omega$  termination resistors on receiver channels. These pins do not contain dedicated serialization or deserialization circuitry. Therefore, internal logic performs serialization and deserialization functions.

Cyclone II pin tables list the pins that support the high-speed I/O interface. The number of LVDS channels supported in each device family member is listed in Table 2–18.

| Table 2–18. Cyclone II Device LVDS Channels (Part 1 of 2) |           |                                |  |  |  |  |

|-----------------------------------------------------------|-----------|--------------------------------|--|--|--|--|

| Device                                                    | Pin Count | Number of LVDS<br>Channels (1) |  |  |  |  |

| EP2C5                                                     | 144       | 31 (35)                        |  |  |  |  |

|                                                           | 208       | 56 (60)                        |  |  |  |  |

|                                                           | 256       | 61 (65)                        |  |  |  |  |

| EP2C8                                                     | 144       | 29 (33)                        |  |  |  |  |

|                                                           | 208       | 53 (57)                        |  |  |  |  |

|                                                           | 256       | 75 (79)                        |  |  |  |  |

| EP2C15                                                    | 256       | 52 (60)                        |  |  |  |  |

|                                                           | 484       | 128 (136)                      |  |  |  |  |

| EP2C20                                                    | 240       | 45 (53)                        |  |  |  |  |

|                                                           | 256       | 52 (60)                        |  |  |  |  |

|                                                           | 484       | 128 (136)                      |  |  |  |  |

| EP2C35                                                    | 484       | 131 (139)                      |  |  |  |  |

|                                                           | 672       | 201 (209)                      |  |  |  |  |

| EP2C50                                                    | 484       | 119 (127)                      |  |  |  |  |

|                                                           | 672       | 189 (197)                      |  |  |  |  |

Cyclone II devices support driver impedance matching to the impedance of the transmission line, typically 25 or 50  $\Omega$  When used with the output drivers, on-chip termination sets the output driver impedance to 25 or 50  $\Omega$  Cyclone II devices also support I/O driver series termination ( $R_S = 50~\Omega$ ) for SSTL-2 and SSTL-18. Table 2–19 lists the I/O standards that support impedance matching and series termination.

| Table 2–19. I/O Standards S | nation Note (1)       |     |

|-----------------------------|-----------------------|-----|

| I/O Standards               | V <sub>CCIO</sub> (V) |     |

| 3.3-V LVTTL and LVCMOS      | 25 <i>(2)</i>         | 3.3 |

| 2.5-V LVTTL and LVCMOS      | 50 (2)                | 2.5 |

| 1.8-V LVTTL and LVCMOS      | 50 (2)                | 1.8 |

| SSTL-2 class I              | 50 (2)                | 2.5 |

| SSTL-18 class I             | 50 (2)                | 1.8 |

#### *Notes to Table 2–19:*

- (1) Supported conditions are  $V_{CCIO} = V_{CCIO} \pm 50 \text{ mV}$ .

- (2) These  $R_S$  values are nominal values. Actual impedance varies across process, voltage, and temperature conditions.

The recommended frequency range of operation is pending silicon characterization.

On-chip series termination can be supported on any I/O bank.  $V_{CCIO}$  and  $V_{REF}$  must be compatible for all I/O pins in order to enable on-chip series termination in a given I/O bank. I/O standards that support different  $R_{\rm S}$  values can reside in the same I/O bank as long as their  $V_{CCIO}$  and  $V_{REF}$  are not conflicting.

When using on-chip series termination, programmable drive strength is not available.

Impedance matching is implemented using the capabilities of the output driver and is subject to a certain degree of variation, depending on the process, voltage and temperature. The actual tolerance is pending silicon characterization.

| Table 5–25. EP2C15A Column Pins Global Clock Timing Parameters |                           |            |          |              |                  |          |      |  |  |

|----------------------------------------------------------------|---------------------------|------------|----------|--------------|------------------|----------|------|--|--|

|                                                                | Fast Corner               |            | -6 Speed | -7 Speed     | -7 Speed         | -8 Speed |      |  |  |

| Parameter                                                      | Industrial/<br>Automotive | Commercial | Grade    | Grade<br>(1) | <b>Grade</b> (2) | Grade    | Unit |  |  |

| t <sub>PLLCOUT</sub>                                           | -0.337                    | -0.357     | 0.079    | 0.04         | 0.075            | 0.045    | ns   |  |  |

Notes to Table 5-25:

- (1) These numbers are for commercial devices.

- (2) These numbers are for automotive devices.

| Table 5–26. EP2C15A Row Pins Global Clock Timing Parameters |                           |            |                   |                  |                  |                   |      |  |  |

|-------------------------------------------------------------|---------------------------|------------|-------------------|------------------|------------------|-------------------|------|--|--|

|                                                             | Fast Corner               |            | COmend            | -7 Speed         | -7 Speed         | 0.0===d           |      |  |  |

| Parameter                                                   | Industrial/<br>Automotive | Commercial | -6 Speed<br>Grade | <b>Grade</b> (1) | <b>Grade</b> (2) | –8 Speed<br>Grade | Unit |  |  |

| t <sub>CIN</sub>                                            | 1.542                     | 1.615      | 2.490             | 2.651            | 2.886            | 2.866             | ns   |  |  |

| t <sub>COUT</sub>                                           | 1.544                     | 1.617      | 2.506             | 2.664            | 2.894            | 2.874             | ns   |  |  |

| t <sub>PLLCIN</sub>                                         | -0.424                    | -0.448     | -0.057            | -0.107           | -0.077           | -0.107            | ns   |  |  |

| t <sub>PLLCOUT</sub>                                        | -0.422                    | -0.446     | -0.041            | -0.094           | -0.069           | -0.099            | ns   |  |  |

#### Notes to Table 5–26:

- (1) These numbers are for commercial devices.

- (2) These numbers are for automotive devices.

#### EP2C20/A Clock Timing Parameters

Tables 5–27 and 5–28 show the clock timing parameters for EP2C20/A devices.

| Table 5–27. EP2C20/A Column Pins Global Clock Timing Parameters (Part 1 of 2) |                           |            |          |              |                  |                   |      |  |  |

|-------------------------------------------------------------------------------|---------------------------|------------|----------|--------------|------------------|-------------------|------|--|--|

|                                                                               | Fast Corner               |            | -6 Speed | -7 Speed     | -7 Speed         | 0 Spood           |      |  |  |

| Parameter                                                                     | Industrial/<br>Automotive | Commercial | Grade    | Grade<br>(1) | <b>Grade</b> (2) | –8 Speed<br>Grade | Unit |  |  |

| t <sub>CIN</sub>                                                              | 1.621                     | 1.698      | 2.590    | 2.766        | 3.009            | 2.989             | ns   |  |  |

| t <sub>COUT</sub>                                                             | 1.635                     | 1.713      | 2.624    | 2.798        | 3.038            | 3.018             | ns   |  |  |

| t <sub>PLLCIN</sub>                                                           | -0.351                    | -0.372     | 0.045    | 0.008        | 0.046            | 0.016             | ns   |  |  |

| Table 5–45. Maximum Output Clock Toggle Rate on Cyclone II Devices (Part 3 of 4)  Maximum Output Clock Toggle Rate on Cyclone II Devices (MHz) |          |                                      |                      |                      |                      |                      |                      |                      |                         |                      |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-------------------------|----------------------|--|

| I/O Standard                                                                                                                                   | Drive    | Column I/O Pins (1) Row I/O Pins (1) |                      |                      |                      |                      |                      |                      | Dedicated Clock Outputs |                      |  |

| ,                                                                                                                                              | Strength | -6<br>Speed<br>Grade                 | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade    | –8<br>Speed<br>Grade |  |

| SSTL_18_ CLASS_II                                                                                                                              | 16 mA    | 260                                  | 220                  | 180                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

|                                                                                                                                                | 18 mA    | 270                                  | 220                  | 180                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| 1.8V_HSTL_ CLASS_I                                                                                                                             | 8 mA     | 260                                  | 220                  | 180                  | 260                  | 220                  | 180                  | 260                  | 220                     | 180                  |  |

|                                                                                                                                                | 10 mA    | 300                                  | 250                  | 210                  | 300                  | 250                  | 210                  | 300                  | 250                     | 210                  |  |

|                                                                                                                                                | 12 mA    | 320                                  | 270                  | 220                  | 320                  | 270                  | 220                  | 320                  | 270                     | 220                  |  |

| 1.8V_HSTL_ CLASS_II                                                                                                                            | 16 mA    | 230                                  | 190                  | 160                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

|                                                                                                                                                | 18 mA    | 240                                  | 200                  | 160                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

|                                                                                                                                                | 20 mA    | 250                                  | 210                  | 170                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| 1.5V_HSTL_ CLASS_I                                                                                                                             | 8 mA     | 210                                  | 170                  | 140                  | 210                  | 170                  | 140                  | 210                  | 170                     | 140                  |  |

|                                                                                                                                                | 10 mA    | 220                                  | 180                  | 150                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

|                                                                                                                                                | 12 mA    | 230                                  | 190                  | 160                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| 1.5V_HSTL_ CLASS_II                                                                                                                            | 16 mA    | 210                                  | 170                  | 140                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| DIFFERENTIAL_                                                                                                                                  | 8 mA     | 400                                  | 340                  | 280                  | 400                  | 340                  | 280                  | 400                  | 340                     | 280                  |  |

| SSTL_2_CLASS_I                                                                                                                                 | 12 mA    | 400                                  | 340                  | 280                  | 400                  | 340                  | 280                  | 400                  | 340                     | 280                  |  |

| DIFFERENTIAL_                                                                                                                                  | 16 mA    | 350                                  | 290                  | 240                  | 350                  | 290                  | 240                  | 350                  | 290                     | 240                  |  |

| SSTL_2_CLASS_II                                                                                                                                | 20 mA    | 400                                  | 340                  | 280                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

|                                                                                                                                                | 24 mA    | 400                                  | 340                  | 280                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| DIFFERENTIAL_                                                                                                                                  | 6 mA     | 260                                  | 220                  | 180                  | 260                  | 220                  | 180                  | 260                  | 220                     | 180                  |  |

| SSTL_18_CLASS_I                                                                                                                                | 8 mA     | 260                                  | 220                  | 180                  | 260                  | 220                  | 180                  | 260                  | 220                     | 180                  |  |

|                                                                                                                                                | 10 mA    | 270                                  | 220                  | 180                  | 270                  | 220                  | 180                  | 270                  | 220                     | 180                  |  |

|                                                                                                                                                | 12 mA    | 280                                  | 230                  | 190                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| DIFFERENTIAL_SSTL                                                                                                                              | 16 mA    | 260                                  | 220                  | 180                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| _18_CLASS_II                                                                                                                                   | 18 mA    | 270                                  | 220                  | 180                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| 1.8V_                                                                                                                                          | 8 mA     | 260                                  | 220                  | 180                  | 260                  | 220                  | 180                  | 260                  | 220                     | 180                  |  |

| DIFFERENTIAL_HSTL                                                                                                                              | 10 mA    | 300                                  | 250                  | 210                  | 300                  | 250                  | 210                  | 300                  | 250                     | 210                  |  |

| _CLASS_I                                                                                                                                       | 12 mA    | 320                                  | 270                  | 220                  | 320                  | 270                  | 220                  | 320                  | 270                     | 220                  |  |

| 1.8V_                                                                                                                                          | 16 mA    | 230                                  | 190                  | 160                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| DIFFERENTIAL_HSTL                                                                                                                              | 18 mA    | 240                                  | 200                  | 160                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| _CLASS_II                                                                                                                                      | 20 mA    | 250                                  | 210                  | 170                  | _                    | _                    | _                    | _                    | _                       | _                    |  |

| Table 7–5. PLL Output signals |                                                                                                                                                                                                                     |                         |                                                |  |  |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------|--|--|--|--|

| Port                          | Description                                                                                                                                                                                                         | Source                  | Destination                                    |  |  |  |  |

| c[20]                         | PLL clock outputs driving the internal global clock network or external clock output pin (PLL<#>_OUT)                                                                                                               | PLL post-scale counter  | Global clock<br>network or<br>external I/O pin |  |  |  |  |

| Locked                        | Gives the status of the PLL lock. When the PLL is locked, this port drives $V_{\text{CC}}$ . When the PLL is out of lock, this port drives GND. The locked port may pulse high and low during the PLL lock process. | PLL lock detect circuit | Logic array or output pin                      |  |  |  |  |

Table 7–6 shows a list of I/O standards supported in Cyclone II device PLLs.

| I/O Standard                                            | Input    | Output   |              |  |

|---------------------------------------------------------|----------|----------|--------------|--|

| I/O Standard                                            | inclk    | lock     | pll_out      |  |

| LVTTL (3.3, 2.5, and 1.8 V)                             | <b>✓</b> | <b>✓</b> | <b>✓</b>     |  |

| LVCMOS (3.3, 2.5, 1.8, and 1.5 V)                       | <b>✓</b> | ✓        | ~            |  |

| 3.3-V PCI                                               | ✓        | ✓        | <b>✓</b>     |  |

| 3.3-V PCI-X (1)                                         | <b>✓</b> | ✓        | <b>✓</b>     |  |

| LVPECL                                                  | ✓        |          |              |  |

| LVDS                                                    | <b>✓</b> | ✓        | <b>✓</b>     |  |

| 1.5 and 1.8 V differential<br>HSTL class I and class II | <b>✓</b> |          | <b>√</b> (2) |  |

| 1.8 and 2.5 V differential<br>SSTL class I and class II | <b>✓</b> |          | <b>√</b> (2) |  |

| 1.5-V HSTL class I                                      | ✓        | ✓        | <b>✓</b>     |  |

| 1.5-V HSTL class II (3)                                 | <b>✓</b> | <b>✓</b> | <b>✓</b>     |  |

| 1.8-V HSTL class I                                      | ✓        | ✓        | <b>✓</b>     |  |

| 1.8-V HSTL class II (3)                                 | <b>✓</b> | <b>✓</b> | <b>✓</b>     |  |

| SSTL-18 class I                                         | <b>✓</b> | <b>✓</b> | <b>✓</b>     |  |

| SSTL-18 class II (3)                                    | ✓        | <b>✓</b> | <b>✓</b>     |  |

| SSTL-25 class I                                         | <b>✓</b> | <b>✓</b> | <b>✓</b>     |  |

In addition, the clock networks in the Cyclone II device support dynamic selection of the clock source and also support a power-down mode where clock networks that are not being used can easily be turned off, reducing the overall power consumption of the device.

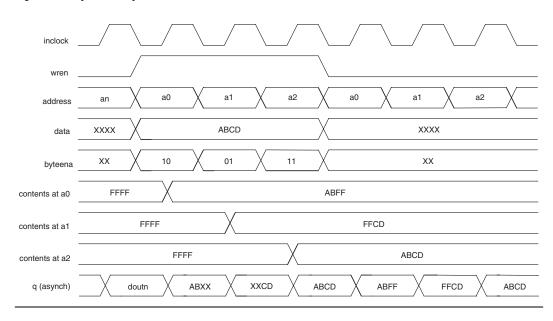

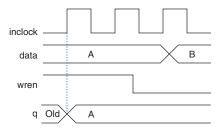

Figure 8–2. Cyclone II Byte Enable Functional Waveform

### **Packed Mode Support**

Cyclone II M4K memory blocks support packed mode. You can implement two single-port memory blocks in a single block under the following conditions:

- Each of the two independent block sizes is less than or equal to half of the M4K block size. The maximum data width for each independent block is 18 bits wide.

- Each of the single-port memory blocks is configured in single-clock mode.

See "Single-Port Mode" on page 8–9 and "Single-Clock Mode" on page 8–24 for more information.

#### **Address Clock Enable**

Cyclone II M4K memory blocks support address clock enables, which holds the previous address value until needed. When the memory blocks are configured in dual-port mode, each port has its own independent address clock enable.

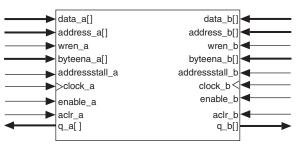

Figure 8–10. Cyclone II True Dual-Port Mode Note (1)

Note to Figure 8-10:

True dual-port memory supports input and output clock mode in addition to the independent clock mode shown.

The widest bit configuration of the M4K blocks in true dual-port mode is  $256 \times 16$ -bit (18-bit with parity).

The  $128 \times 32$ -bit (36-bit with parity) configuration of the M4K block is unavailable because the number of output drivers is equivalent to the maximum bit width. The maximum width of the true dual-port RAM equals half of the total number of output drivers because true dual-port RAM has outputs on two ports. Table 8–6 lists the possible M4K block mixed-port width configurations.

| Read Port |          |          |          | Write    | Port     |          |          |

|-----------|----------|----------|----------|----------|----------|----------|----------|

| neau Port | 4K×1     | 2K × 2   | 1K×4     | 256 × 16 | 512 × 9  | 256 × 18 |          |

| 4K × 1    | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |

| 2K × 2    | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |

| 1K × 4    | <b>✓</b> | <b>✓</b> | <b>✓</b> | ~        | <b>✓</b> |          |          |

| 512 × 8   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |

| 256 × 16  | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |

| 512 × 9   |          |          |          |          |          | <b>✓</b> | <b>✓</b> |

| 256 × 18  |          |          |          |          |          | <b>✓</b> | <b>✓</b> |

In true dual-port configuration, the RAM outputs are in read-during-write mode. This means that during a write operation, data being written to the A or B port of the RAM flows through to the A or B

applications require local data storage, traditionally implemented with standard flip-flops that quickly exhaust many logic cells for large shift registers. A more efficient alternative is to use embedded memory as a shift register block, which saves logic cell and routing resources.

The size of a  $(w \times m \times n)$  shift register is determined by the input data width (w), the length of the taps (m), and the number of taps (n), and must be less than or equal to the maximum number of memory bits, which is 4,608 bits. In addition, the size of  $(w \times n)$  must be less than or equal to the maximum width of the block, which is 36 bits. If a larger shift register is required, the memory blocks can be cascaded.

Data is written into each address location at the falling edge of the clock and read from the address at the rising edge of the clock. The shift register mode logic automatically controls the positive and negative edge clocking to shift the data in one clock cycle. Figure 8–12 shows the Cyclone II memory block in the shift register mode.

m-Bit Shift Register

Figure 8–12. Cyclone II Shift Register Mode Configuration

Figure 8–22. Cyclone II Same-Port Read-During-Write Functionality Note (1)

Note to Figure 8-22:

(1) Outputs are not registered.

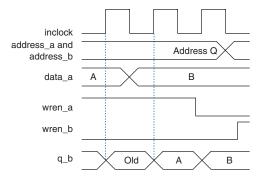

#### **Mixed-Port Read-During-Write Mode**

This mode applies to a RAM in simple or true dual-port mode, which has one port reading and the other port writing to the same address location with the same clock.

In this mode, you also have two output choices: old data or don't care. In Old Data Mode, a read-during-write operation to different ports causes the RAM outputs to reflect the old data at that address location. In Don't Care Mode, the same operation results in a "don't care" or unknown value on the RAM outputs.

Figure 8–23. Cyclone II Mixed-Port Read-During-Write: Old Data Mode Note (1)

Note to Figure 8-23:

(1) Outputs are not registered.

# Section VI. Configuration & Test

This section provides configuration information for all of the supported configuration schemes for Cyclone<sup>®</sup> II devices. These configuration schemes use either a microprocessor, configuration device, or download cable. There is detailed information on how to design with Altera<sup>®</sup> configuration devices. The last chapter provides information on JTAG support in Cyclone II devices.

This section includes the following chapters:

- Chapter 13, Configuring Cyclone II Devices

- Chapter 14, IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices

## **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

Altera Corporation Section VI-1

During initialization, the initialization clock source is either the Cyclone II 10 MHz (typical) internal oscillator (separate from the AS internal oscillator) or the optional CLKUSR pin. By default, the internal oscillator is the clock source for initialization. If the internal oscillator is used, the Cyclone II device provides itself with enough clock cycles for proper initialization. The advantage of using the internal oscillator is you do not need to send additional clock cycles from an external source to the CLKUSR pin during the initialization stage. You can also make use of the CLKUSR pin as a user I/O pin, which means you have an additional user I/O pin.

If you want to delay the initialization of the devices in the chain, you can use the CLKUSR pin option. The CLKUSR pin allows you to control when your device enters user mode. This feature also allows you to control the order of when each device enters user mode by feeding a separate clock to each device's CLKUSR pin. By using the CLKUSR pins, you can choose any device in the multiple device chain to enter user mode first and have the other devices enter user mode at a later time.

Different device families may require a different number of initialization clock cycles. Therefore, if your multiple device chain consists of devices from different families, the devices may enter user mode at a slightly different time due to the different number of initialization clock cycles required. However, if the number of initialization clock cycles is similar across different device families or if the devices are from the same family, then the devices enter user mode at the same time. See the respective device family handbook for more information about the number of initialization clock cycles required.

If an error occurs at any point during configuration, the FPGA with the error drives the <code>nstatus</code> signal low. If you enable the **Auto-restart configuration after error** option, the entire chain begins reconfiguration after a reset time-out period (a maximum of 40  $\mu s$ ). If the **Auto-restart configuration after error** option is turned off, a microprocessor or controller must monitor <code>nstatus</code> for errors and then pulse <code>nconfiguration</code>. The microprocessor or controller can pulse <code>nconfiguration</code> if it is under system control rather than tied to  $V_{\rm CC}$ .

While you can cascade Cyclone II devices, serial configuration devices cannot be cascaded or chained together.

If you use the optional CLKUSR pin and the nCONFIG is pulled low to restart configuration during device initialization, make sure the CLKUSR pin continues to toggle while nSTATUS is low (a maximum of  $40~\mu s$ ).

#### **Programming Serial Configuration Devices**

Serial configuration devices are non-volatile, flash-memory-based devices. You can program these devices in-system using the USB-Blaster<sup>TM</sup> or ByteBlaster<sup>TM</sup> II download cable. Alternatively, you can program them using the Altera Programming Unit (APU), supported third-party programmers, or a microprocessor with the SRunner software driver.

You can use the AS programming interface to program serial configuration devices in-system. During in-system programming, the download cable disables FPGA access to the AS interface by driving the nCE pin high. Cyclone II devices are also held in reset by pulling the nCONFIG signal low. After programming is complete, the download cable releases the nCE and nCONFIG signals, allowing the pull-down and pull-up resistor to drive GND and  $V_{CC}$ , respectively. Figure 13–7 shows the download cable connections to the serial configuration device.

For more information on the USB-Blaster download cable, see the *USB-Blaster USB Port Download Cable Data Sheet*. For more information on the ByteBlaster II cable, see the *ByteBlaster II Download Cable Data Sheet*.

#### Reconfiguration

After all the configuration data is written into the serial configuration device successfully, the Cyclone II device does not reconfigure by itself. The intelligent host issues the <code>PULSE\_NCONFIG</code> JTAG instruction to initialize the reconfiguration process. During reconfiguration, the master Cyclone II device is reset and the serial flash loader design no longer exists in the Cyclone II device and the serial configuration device configures all the devices in the chain with your user design.

# Device Configuration Pins

This section describes the connections and functionality of all the configuration related pins on the Cyclone II device. Table 13–11 describes the dedicated configuration pins, which are required to be connected properly on your board for successful configuration. Some of these pins may not be required for your configuration schemes.

| Table 13–11. Dedicated Configuration Pins on the Cyclone II Device (Part 1 of 5) |              |          |       |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|----------------------------------------------------------------------------------|--------------|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                                         | User<br>Mode | Pin Ivne |       | Description                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| MSEL[10]                                                                         | N/A          | All      | Input | This pin is a two-bit configuration input that sets the Cyclone II device configuration scheme. See Table 13–1 for the appropriate settings.   You must connect these pins to $V_{\text{CCIO}}$ or ground.   The $\texttt{MSEL}[10]$ pins have 9-k $\Omega$ internal pull-down resistors that are always active.                                                                                       |  |  |

| nCONFIG                                                                          | N/A          | All      | Input | This pin is a configuration control input. If this pin is pulled low during user mode, the FPGA loses its configuration data, enters a reset state, and tri-states all I/O pins. Transitioning this pin high initiates a reconfiguration.  If your configuration scheme uses an enhanced configuration device or EPC2 device, you can connect the nconfiguration directly to V <sub>CC</sub> or to the |  |  |

|                                                                                  |              |          |       | configuration device's nINIT_CONF pin.  The input buffer on this pin supports hysteresis using Schmitt trigger circuitry.                                                                                                                                                                                                                                                                              |  |  |

frequency (up to 40 MHz), which reduces your configuration time. In addition, Cyclone II devices can receive a compressed configuration bitstream and decompress this data on-the-fly in the AS or PS configuration scheme, which further reduces storage requirements and configuration time.

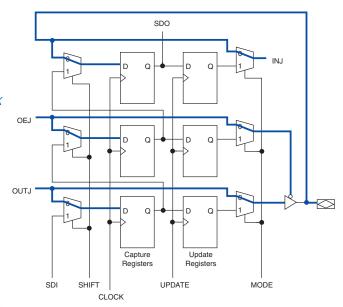

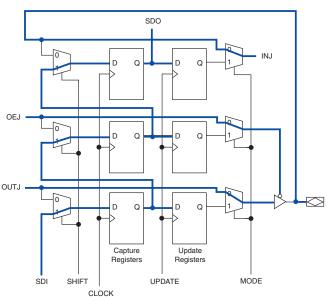

Figure 14-8. IEEE Std. 1149.1 BST SAMPLE/PRELOAD Mode

#### **Capture Phase**

In the capture phase, the signals at the pin, OEJ and OUTJ, are loaded into the capture registers. The CLOCK signals are supplied by the TAP controller's CLOCKDR output. The data retained in these registers consists of signals from normal device operation.

#### **Shift & Update Phases**

In the shift phase, the previously captured signals at the pin, OEJ and OUTJ, are shifted out of the boundary-scan register via the TDO pin using CLOCK. As data is shifted out, the patterns for the next test can be shifted in via the TDI pin.

In the update phase, data is transferred from the capture to the UPDATE registers using the UPDATE clock. The data stored in the UPDATE registers can be used for the EXTEST instruction.

Tables 15–5 and 15–6 show the package information and package outline figure references, respectively, for the 144-pin TQFP package.

| Table 15–5. 144-Pin TQFP Package Information |                                                |  |  |  |  |

|----------------------------------------------|------------------------------------------------|--|--|--|--|

| Description                                  | Specification                                  |  |  |  |  |

| Ordering code reference                      | Т                                              |  |  |  |  |

| Package acronym                              | TQFP                                           |  |  |  |  |

| Lead frame material                          | Copper                                         |  |  |  |  |

| Lead finish (plating)                        | Regular: 85Sn:15Pb (Typ.)<br>Pb-free: Matte Sn |  |  |  |  |

| JEDEC Outline Reference                      | MS-026 Variation: BFB                          |  |  |  |  |

| Maximum lead coplanarity                     | 0.003 inches (0.08mm)                          |  |  |  |  |

| Weight                                       | 1.3 g                                          |  |  |  |  |

| Moisture sensitivity level                   | Printed on moisture barrier bag                |  |  |  |  |

| Table 15–6. 144-Pin TQFP Package Outline Dimensions |            |      |      |  |  |  |  |

|-----------------------------------------------------|------------|------|------|--|--|--|--|

| Cumbal                                              | Millimeter |      |      |  |  |  |  |

| Symbol                                              | Min.       | Nom. | Max. |  |  |  |  |

| Α                                                   | _          | _    | 1.60 |  |  |  |  |

| A1                                                  | 0.05       | -    | 0.15 |  |  |  |  |

| A2                                                  | 1.35       | 1.40 | 1.45 |  |  |  |  |

| D                                                   | 22.00 BSC  |      |      |  |  |  |  |

| D1                                                  | 20.00 BSC  |      |      |  |  |  |  |

| E                                                   | 22.00 BSC  |      |      |  |  |  |  |

| E1                                                  | 20.00 BSC  |      |      |  |  |  |  |

| L                                                   | 0.45       | 0.60 | 0.75 |  |  |  |  |

| L1                                                  | 1.00 REF   |      |      |  |  |  |  |

| S                                                   | 0.20       | _    | _    |  |  |  |  |

| b                                                   | 0.17       | 0.22 | 0.27 |  |  |  |  |

| С                                                   | 0.09       | _    | 0.20 |  |  |  |  |

| е                                                   | 0.50 BSC   |      |      |  |  |  |  |

| θ 0°                                                |            | 3.5° | 7°   |  |  |  |  |