Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 2076                                                    |

| Number of Logic Elements/Cells | 33216                                                   |

| Total RAM Bits                 | 483840                                                  |

| Number of I/O                  | 475                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 672-BGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c35f672c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **PLLs**

Cyclone II PLLs provide general-purpose clocking as well as support for the following features:

- Clock multiplication and division

- Phase shifting

- Programmable duty cycle

- Up to three internal clock outputs

- One dedicated external clock output

- Clock outputs for differential I/O support

- Manual clock switchover

- Gated lock signal

- Three different clock feedback modes

- Control signals

Cyclone II devices contain either two or four PLLs. Table 2–3 shows the PLLs available for each Cyclone II device.

| Table 2–3. Cyclone II Device PLL Availability |          |          |          |      |  |  |

|-----------------------------------------------|----------|----------|----------|------|--|--|

| Device                                        | PLL1     | PLL2     | PLL3     | PLL4 |  |  |

| EP2C5                                         | <b>✓</b> | <b>✓</b> |          |      |  |  |

| EP2C8                                         | ✓        | ✓        |          |      |  |  |

| EP2C15                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> | ✓    |  |  |

| EP2C20                                        | <b>✓</b> | ~        | ✓        | ~    |  |  |

| EP2C35                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> | ✓    |  |  |

| EP2C50                                        | <b>✓</b> | ~        | ✓        | ~    |  |  |

| EP2C70                                        | ✓        | ✓        | ✓        | ✓    |  |  |

Table 2–4 describes the PLL features in Cyclone II devices.

| Feature                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock multiplication and division | $m / (n \times \text{post-scale counter})$<br>m and post-scale counter values (C0 to C2) range from 1 to 32. $n$ ranges from 1 to 4.                                                                                                                                                                                                                                                                                              |

| Phase shift                       | Cyclone II PLLs have an advanced clock shift capability that enables programmable phase shifts in increments of at least 45°. The finest resolution of phase shifting is determined by the voltage control oscillator (VCO) period divided by 8 (for example, 1/1000 MHz/8 = down to 125-ps increments).                                                                                                                          |

| Programmable duty cycle           | The programmable duty cycle allows PLLs to generate clock outputs with a variable duty cycle. This feature is supported on each PLL post-scale counter (C0-C2).                                                                                                                                                                                                                                                                   |

| Number of internal clock outputs  | The Cyclone II PLL has three outputs which can drive the global clock network. One of these outputs (C2) can also drive a dedicated PLL<#>_OUT pin (single ended or differential).                                                                                                                                                                                                                                                |

| Number of external clock outputs  | The C2 output drives a dedicated PLL<#>_OUT pin. If the C2 output is not used to drive an external clock output, it can be used to drive the internal global clock network. The C2 output can concurrently drive the external clock output and internal global clock network.                                                                                                                                                     |

| Manual clock switchover           | The Cyclone II PLLs support manual switchover of the reference clock through internal logic. This enables you to switch between two reference input clocks during user mode for applications that may require clock redundancy or support for clocks with two different frequencies.                                                                                                                                              |

| Gated lock signal                 | The lock output indicates that there is a stable clock output signal in phase with the reference clock. Cyclone II PLLs include a programmable counter that holds the lock signal low for a user-selected number of input clock transitions, allowing the PLL to lock before enabling the locked signal. Either a gated locked signal or an ungated locked signal from the locked port can drive internal logic or an output pin. |

| Clock feedback modes              | In zero delay buffer mode, the external clock output pin is phase-aligned with the clock input pin for zero delay.  In normal mode, the PLL compensates for the internal global clock network delay from the input clock pin to the clock port of the IOE output registers or registers in the logic array.  In no compensation mode, the PLL does not compensate for any clock networks.                                         |

| Control signals                   | The pllenable signal enables and disables the PLLs. The areset signal resets/resynchronizes the inputs for each PLL. The pfdena signal controls the phase frequency detector (PFD) output with a programmable gate.                                                                                                                                                                                                               |

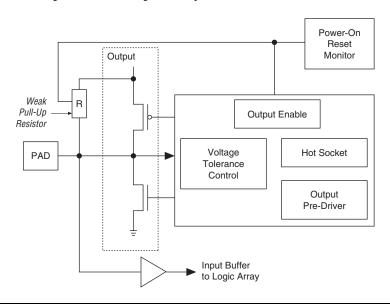

Figure 4–1. Hot-Socketing Circuit Block Diagram for Cyclone II Devices

The POR circuit monitors  $V_{CCINT}$  voltage level and keeps I/O pins tri-stated until the device is in user mode. The weak pull-up resistor (R) from the I/O pin to  $V_{CCIO}$  keeps the I/O pins from floating. The voltage tolerance control circuit permits the I/O pins to be driven by 3.3 V before  $V_{CCIO}$  and/or  $V_{CCINT}$  are powered, and it prevents the I/O pins from driving out when the device is not in user mode.

For more information, see the *DC Characteristics & Timing Specifications* chapter in Volume 1 of the *Cyclone II Device Handbook* for the value of the internal weak pull-up resistors.

Figure 4–2 shows a transistor level cross section of the Cyclone II device I/O buffers. This design ensures that the output buffers do not drive when  $V_{\text{CCIO}}$  is powered before  $V_{\text{CCINT}}$  or if the I/O pad voltage is higher than  $V_{\text{CCIO}}.$  This also applies for sudden voltage spikes during hot socketing. The  $V_{\text{PAD}}$  leakage current charges the voltage tolerance control circuit capacitance.

| Table 5–3.          | Table 5–3. DC Characteristics for User I/O, Dual-Purpose, and Dedicated Pins (Part 1 of 2) |                                 |            |          |         |                   |      |   |

|---------------------|--------------------------------------------------------------------------------------------|---------------------------------|------------|----------|---------|-------------------|------|---|

| Symbol              | Parameter                                                                                  | Cond                            | itions     | Minimum  | Typical | Maximum           | Unit |   |

| V <sub>IN</sub>     | Input voltage                                                                              | (1)                             | , (2)      | -0.5     | _       | 4.0               | V    |   |

| l <sub>i</sub>      | Input pin leakage current                                                                  | $V_{IN} = V_{CCIOmax} t$        | o 0 V (3)  | -10      | _       | 10                | μΑ   |   |

| V <sub>OUT</sub>    | Output voltage                                                                             | -                               | _          | 0        | _       | V <sub>CCIO</sub> | V    |   |

| l <sub>OZ</sub>     | Tri-stated I/O pin leakage current                                                         | $V_{OUT} = V_{CCIOmax}$         | to 0 V (3) | -10      | _       | 10                | μΑ   |   |

| I <sub>CCINTO</sub> | V <sub>CCINT</sub> supply                                                                  | V <sub>IN</sub> = ground,       | EP2C5/A    | _        | 0.010   | (4)               | Α    |   |

|                     | current (standby)                                                                          | no load, no toggling inputs     | EP2C8/A    | _        | 0.017   | (4)               | Α    |   |

|                     |                                                                                            | T <sub>.1</sub> = 25° C         | EP2C15A    | _        | 0.037   | (4)               | Α    |   |

|                     |                                                                                            |                                 | Nominal    | EP2C20/A | _       | 0.037             | (4)  | Α |

|                     |                                                                                            | V <sub>CCINT</sub>              | EP2C35     | _        | 0.066   | (4)               | Α    |   |

|                     |                                                                                            |                                 | EP2C50     | _        | 0.101   | (4)               | Α    |   |

|                     |                                                                                            |                                 | EP2C70     | _        | 0.141   | (4)               | Α    |   |

| I <sub>CCIO0</sub>  | V <sub>CCIO</sub> supply current                                                           | $V_{IN}$ = ground,              | EP2C5/A    | _        | 0.7     | (4)               | mA   |   |

|                     | (standby)                                                                                  | no load, no toggling inputs     | EP2C8/A    | _        | 0.8     | (4)               | mA   |   |

|                     |                                                                                            | $T_{.1} = 25^{\circ} \text{ C}$ | EP2C15A    | _        | 0.9     | (4)               | mA   |   |

|                     |                                                                                            | $V_{CCIO} = 2.5 \text{ V}$      | EP2C20/A   | _        | 0.9     | (4)               | mA   |   |

|                     |                                                                                            |                                 | EP2C35     |          | 1.3     | (4)               | mA   |   |

|                     |                                                                                            |                                 | EP2C50     |          | 1.3     | (4)               | mA   |   |

|                     |                                                                                            |                                 | EP2C70     | _        | 1.7     | (4)               | mA   |   |

| Table 5–3. DC Characteristics for User I/O, Dual-Purpose, and Dedicated Pins (Part 2 of 2) |                                                                                                      |                                                  |         |         |         |      |  |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------|---------|---------|------|--|

| Symbol                                                                                     | Parameter                                                                                            | Conditions                                       | Minimum | Typical | Maximum | Unit |  |

| R <sub>CONF</sub> (5) (6)                                                                  | Value of I/O pin                                                                                     | $V_{IN} = 0 \text{ V}; V_{CCIO} = 3.3 \text{ V}$ | 10      | 25      | 50      | kΩ   |  |

|                                                                                            | pull-up resistor<br>before and during<br>configuration                                               | V <sub>IN</sub> = 0 V; V <sub>CCIO</sub> = 2.5 V | 15      | 35      | 70      | kΩ   |  |

|                                                                                            |                                                                                                      | V <sub>IN</sub> = 0 V; V <sub>CCIO</sub> = 1.8 V | 30      | 50      | 100     | kΩ   |  |

|                                                                                            |                                                                                                      | V <sub>IN</sub> = 0 V; V <sub>CCIO</sub> = 1.5 V | 40      | 75      | 150     | kΩ   |  |

|                                                                                            |                                                                                                      | V <sub>IN</sub> = 0 V; V <sub>CCIO</sub> = 1.2 V | 50      | 90      | 170     | kΩ   |  |

|                                                                                            | Recommended<br>value of I/O pin<br>external pull-down<br>resistor before and<br>during configuration | (7)                                              | _       | 1       | 2       | kΩ   |  |

#### Notes to Table 5-3:

- All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (2) The minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to the voltages shown in Table 5-4, based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

- (3) This value is specified for normal device operation. The value may vary during power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, and 1.5 V).

- (4) Maximum values depend on the actual T<sub>J</sub> and design utilization. See the Excel-based PowerPlay Early Power Estimator (www.altera.com) or the Quartus II PowerPlay Power Analyzer feature for maximum values. Refer to "Power Consumption" on page 5–13 for more information.

- (5)  $R_{CONF}$  values are based on characterization.  $R_{CONF} = V_{CCIO}/I_{RCONF}$  values may be different if  $V_{IN}$  value is not 0 V. Pin pull-up resistance values will be lower if an external source drives the pin higher than  $V_{CCIO}$ .

- (6) Minimum condition at -40°C and high V<sub>CC</sub>, typical condition at 25°C and nominal V<sub>CC</sub> and maximum condition at 125°C and low V<sub>CC</sub> for R<sub>CONF</sub> values.

- (7) These values apply to all V<sub>CCIO</sub> settings.

Table 5–4 shows the maximum  $V_{\rm IN}$  overshoot voltage and the dependency on the duty cycle of the input signal. Refer to Table 5–3 for more information.

| Table 5–4. V <sub>IN</sub> Overshoot Voltage for All Input Buffers |           |  |  |  |  |  |

|--------------------------------------------------------------------|-----------|--|--|--|--|--|

| Maximum V <sub>IN</sub> (V) Input Signal Duty Cycle                |           |  |  |  |  |  |

| 4.0                                                                | 100% (DC) |  |  |  |  |  |

| 4.1                                                                | 90%       |  |  |  |  |  |

| 4.2                                                                | 50%       |  |  |  |  |  |

| 4.3                                                                | 30%       |  |  |  |  |  |

| 4.4                                                                | 17%       |  |  |  |  |  |

| 4.5                                                                | 10%       |  |  |  |  |  |

| Table 5–45. Maximum | Output Gloci |                      |                      | -                    |                                                | •                    |                      |                      | nuince (             | M11=/                |

|---------------------|--------------|----------------------|----------------------|----------------------|------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| I/O Standard        | Drive        |                      | nn I/O Pi            | l                    | one II Devices (MHz)  Dedicated Clock  Outputs |                      |                      |                      |                      |                      |

| ,                   | Strength     | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | -6<br>Speed<br>Grade                           | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade |

| SSTL_18_ CLASS_II   | 16 mA        | 260                  | 220                  | 180                  | _                                              | _                    | _                    | _                    | _                    | _                    |

|                     | 18 mA        | 270                  | 220                  | 180                  | _                                              | _                    | _                    | _                    | _                    | _                    |

| 1.8V_HSTL_ CLASS_I  | 8 mA         | 260                  | 220                  | 180                  | 260                                            | 220                  | 180                  | 260                  | 220                  | 180                  |

|                     | 10 mA        | 300                  | 250                  | 210                  | 300                                            | 250                  | 210                  | 300                  | 250                  | 210                  |

|                     | 12 mA        | 320                  | 270                  | 220                  | 320                                            | 270                  | 220                  | 320                  | 270                  | 220                  |

| 1.8V_HSTL_ CLASS_II | 16 mA        | 230                  | 190                  | 160                  | _                                              | _                    | _                    | _                    | _                    | _                    |

|                     | 18 mA        | 240                  | 200                  | 160                  | _                                              | _                    | _                    | _                    | _                    | _                    |

|                     | 20 mA        | 250                  | 210                  | 170                  | _                                              | _                    | _                    | _                    | _                    | _                    |

| 1.5V_HSTL_ CLASS_I  | 8 mA         | 210                  | 170                  | 140                  | 210                                            | 170                  | 140                  | 210                  | 170                  | 140                  |

|                     | 10 mA        | 220                  | 180                  | 150                  | _                                              | _                    | _                    | _                    | _                    | _                    |

|                     | 12 mA        | 230                  | 190                  | 160                  | _                                              | _                    | _                    | _                    | _                    | _                    |

| 1.5V_HSTL_ CLASS_II | 16 mA        | 210                  | 170                  | 140                  | _                                              | _                    | _                    | _                    | _                    | _                    |

| DIFFERENTIAL_       | 8 mA         | 400                  | 340                  | 280                  | 400                                            | 340                  | 280                  | 400                  | 340                  | 280                  |

| SSTL_2_CLASS_I      | 12 mA        | 400                  | 340                  | 280                  | 400                                            | 340                  | 280                  | 400                  | 340                  | 280                  |

| DIFFERENTIAL_       | 16 mA        | 350                  | 290                  | 240                  | 350                                            | 290                  | 240                  | 350                  | 290                  | 240                  |

| SSTL_2_CLASS_II     | 20 mA        | 400                  | 340                  | 280                  | _                                              | _                    | _                    | _                    | _                    | _                    |

|                     | 24 mA        | 400                  | 340                  | 280                  | _                                              | _                    | _                    | _                    | _                    | _                    |

| DIFFERENTIAL_       | 6 mA         | 260                  | 220                  | 180                  | 260                                            | 220                  | 180                  | 260                  | 220                  | 180                  |

| SSTL_18_CLASS_I     | 8 mA         | 260                  | 220                  | 180                  | 260                                            | 220                  | 180                  | 260                  | 220                  | 180                  |

|                     | 10 mA        | 270                  | 220                  | 180                  | 270                                            | 220                  | 180                  | 270                  | 220                  | 180                  |

|                     | 12 mA        | 280                  | 230                  | 190                  | _                                              | _                    | _                    | _                    | _                    | _                    |

| DIFFERENTIAL_SSTL   | 16 mA        | 260                  | 220                  | 180                  | _                                              | _                    | _                    | _                    | _                    | _                    |

| _18_CLASS_II        | 18 mA        | 270                  | 220                  | 180                  | _                                              | _                    | _                    | _                    | _                    | _                    |

| 1.8V_               | 8 mA         | 260                  | 220                  | 180                  | 260                                            | 220                  | 180                  | 260                  | 220                  | 180                  |

| DIFFERENTIAL_HSTL   | 10 mA        | 300                  | 250                  | 210                  | 300                                            | 250                  | 210                  | 300                  | 250                  | 210                  |

| _CLASS_I            | 12 mA        | 320                  | 270                  | 220                  | 320                                            | 270                  | 220                  | 320                  | 270                  | 220                  |

| 1.8V_               | 16 mA        | 230                  | 190                  | 160                  | _                                              | _                    | _                    | _                    | _                    | _                    |

| DIFFERENTIAL_HSTL   | 18 mA        | 240                  | 200                  | 160                  | _                                              | _                    | _                    | _                    | _                    | _                    |

| _CLASS_II           | 20 mA        | 250                  | 210                  | 170                  | _                                              | _                    | _                    | _                    | _                    | _                    |

| Table 7–8. Global Clock Network Connections (Part 3 of 3) |   |                        |   |   |   |                                    |       |       |       |      |    |    |    |    |    |          |

|-----------------------------------------------------------|---|------------------------|---|---|---|------------------------------------|-------|-------|-------|------|----|----|----|----|----|----------|

| Global Clock<br>Network Clock<br>Sources                  |   |                        |   |   |   |                                    | Globa | l Clo | k Net | work | S  |    |    |    |    |          |

|                                                           |   | All Cyclone II Devices |   |   |   | EP2C15 through EP2C70 Devices Only |       |       |       |      |    |    |    |    |    |          |

|                                                           | 0 | 1                      | 2 | 3 | 4 | 5                                  | 6     | 7     | 8     | 9    | 10 | 11 | 12 | 13 | 14 | 15       |

| DPCLK3 (1)                                                |   |                        |   |   |   |                                    |       |       |       |      |    |    |    |    |    | <b>✓</b> |

Notes to Table 7-8:

- See the Cyclone II Architecture chapter in Volume 1 of the Cyclone II Device Handbook for more information on DPCLK pins.

- (2) This pin only applies to EP2C5 and EP2C8 devices.

- (3) These pins only apply to EP2C15 devices and larger. Only one of the two CDPCLK pins can feed the clock control block. The other pin can be used as a regular I/O pin.

If the dedicated clock pins are not used to feed the global clock networks, they can be used as general-purpose input pins to feed the logic array using the MultiTrack interconnect. However, if they are used as general-purpose input pins, they do not have support for an I/O register and must use LE-based registers in place of an I/O register.

#### **Clock Control Block**

Every global clock network is driven by a clock control block residing either on the top, bottom, left, or right side of the Cyclone II device. The global clock network has been optimized for minimum clock skew and delay.

Table 7–9 lists the sources that can feed the clock control block, which in turn feeds the global clock networks.

| Table 7–9. Clock Control Block Inputs (Part 1 of 2) |                                                                                                                                                                                                                         |  |  |  |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Input                                               | Description                                                                                                                                                                                                             |  |  |  |  |

| Dedicated clock inputs                              | Dedicated clock input pins can drive clocks or global signals, such as asynchronous clears, presets, or clock enables onto a given global clock network.                                                                |  |  |  |  |

| Dual-purpose clock (DPCLK and CDPCLK) I/O inputs    | DPCLK and CDPCLK I/O pins are bidirectional dual function pins that can be used for high fanout control signals, such as protocol signals, TRDY and IRDY signals for PCI, or DQS for DDR, via the global clock network. |  |  |  |  |

# **Section III. Memory**

This section provides information on embedded memory blocks in Cyclone<sup>®</sup> II devices and the supported external memory interfaces.

This section includes the following chapters:

- Chapter 8, Cyclone II Memory Blocks

- Chapter 9, External Memory Interfaces

## **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

Altera Corporation Section III–1

outputs, respectively. When the output registers are bypassed, the new data is available on the rising edge of the same clock cycle on which it was written. See "Read-During-Write Operation at the Same Address" on page 8–28 for waveforms and information on mixed-port read-during-write mode.

Potential write contentions must be resolved external to the RAM because writing to the same address location at both ports results in unknown data storage at that location.

For the maximum synchronous write cycle time, refer to the *Cyclone II Device Family Data Sheet* in volume 1 of the *Cyclone II Device Handbook*.

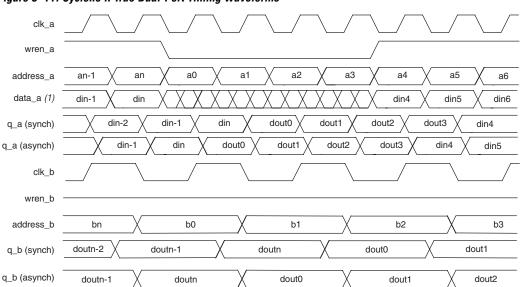

Figure 8–11 shows true dual-port timing waveforms for the write operation at port A and the read operation at port B.

Figure 8–11. Cyclone II True Dual-Port Timing Waveforms

*Note to Figure 8–11:*

The crosses in the data\_a waveform during write indicate "don't care."

## Shift Register Mode

Cyclone II memory blocks can implement shift registers for digital signal processing (DSP) applications, such as finite impulse response (FIR) filters, pseudo-random number generators, multi-channel filtering, and auto-correlation and cross-correlation functions. These and other DSP

| Table 10–2. Cyclone II 66-MHz PCI Support (Part 2 of 2) |                      |                        |          |  |  |  |

|---------------------------------------------------------|----------------------|------------------------|----------|--|--|--|

| Davisa                                                  | Dookono              | -6 and -7 Speed Grades |          |  |  |  |

| Device                                                  | Package              | 64 Bits                | 32 Bits  |  |  |  |

| EP2C8                                                   | 144-pin TQFP         |                        |          |  |  |  |

|                                                         | 208-pin PQFP         |                        | ✓        |  |  |  |

|                                                         | 256-pin FineLine BGA |                        | ✓        |  |  |  |

| EP2C15                                                  | 256-pin FineLine BGA |                        | <b>✓</b> |  |  |  |

|                                                         | 484-pin FineLine BGA | ✓                      | <b>✓</b> |  |  |  |

| EP2C20                                                  | 240-pin PQFP         |                        | ✓        |  |  |  |

|                                                         | 256-pin FineLine BGA |                        | ✓        |  |  |  |

|                                                         | 484-pin FineLine BGA | ✓                      | ✓        |  |  |  |

| EP2C35                                                  | 484-pin FineLine BGA | ✓                      | ✓        |  |  |  |

|                                                         | 672-pin FineLine BGA | ✓                      | ✓        |  |  |  |

| EP2C50                                                  | 484-pin FineLine BGA | ✓                      | ✓        |  |  |  |

|                                                         | 672-pin FineLine BGA | <b>✓</b>               | ✓        |  |  |  |

| EP2C70                                                  | 672-pin FineLine BGA | <b>✓</b>               | ✓        |  |  |  |

|                                                         | 896-pin FineLine BGA | ✓                      | ✓        |  |  |  |

Table 10–3 lists the specific Cyclone II devices that support 64-bit and 32-bit PCI at 33 MHz.

| Table 10–3. Cyclone II 33-MHz PCI Support (Part 1 of 2) |                      |                            |          |  |  |  |

|---------------------------------------------------------|----------------------|----------------------------|----------|--|--|--|

| Device                                                  | Dookogo              | -6, -7 and -8 Speed Grades |          |  |  |  |

| Device                                                  | Package              | 64 Bits                    | 32 Bits  |  |  |  |

| EP2C5                                                   | 144-pin TQFP         | _                          | _        |  |  |  |

|                                                         | 208-pin PQFP         | _                          | ✓        |  |  |  |

|                                                         | 256-pin FineLine BGA | _                          | ✓        |  |  |  |

| EP2C8                                                   | 144-pin TQFP         | _                          | _        |  |  |  |

|                                                         | 208-pin PQFP         | _                          | <b>✓</b> |  |  |  |

|                                                         | 256-pin FineLine BGA | _                          | ✓        |  |  |  |

| EP2C15                                                  | 256-pin FineLine BGA | _                          | ✓        |  |  |  |

|                                                         | 484-pin FineLine BGA | ✓                          | <b>✓</b> |  |  |  |

software makes it easy to use these I/O standards in Cyclone II device designs. After design compilation, the software also provides clear, visual representations of pads and pins and the selected I/O standards. Taking advantage of the support of these I/O standards in Cyclone II devices allows you to lower your design costs without compromising design flexibility or complexity.

## References

For more information on the I/O standards referred to in this document, refer to the following sources:

- Stub Series Terminated Logic for 2.5-V (SSTL-2), JESD8-9A, Electronic Industries Association, December 2000.

- 1.5-V +/- 0.1-V (Normal Range) and 0.9-V 1.6-V (Wide Range) Power Supply Voltage and Interface Standard for Non-terminated Digital Integrated Circuits, JESD8-11, Electronic Industries Association, October 2000.

- 1.8-V +/- 0.15-V (Normal Range) and 1.2-V 1.95-V (Wide Range) Power Supply Voltage and Interface Standard for Non-terminated Digital Integrated Circuits, JESD8-7, Electronic Industries Association, February 1997.

- 2.5-V +/- 0.2-V (Normal Range) and 1.8-V to 2.7-V (Wide Range) Power Supply Voltage and Interface Standard for Non-terminated Digital Integrated Circuits, JESD8-5, Electronic Industries Association, October 1995.

- Interface Standard for Nominal 3-V / 3.3-V Supply Digital Integrated Circuits, JESD8-B, Electronic Industries Association, September 1999.

- PCI Local Bus Specification, Revision 2.2, PCI Special Interest Group, December 1998.

- Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits, ANSI/TIA/EIA-644, American National Standards Institute/Telecommunications Industry/Electronic Industries Association, October 1995.

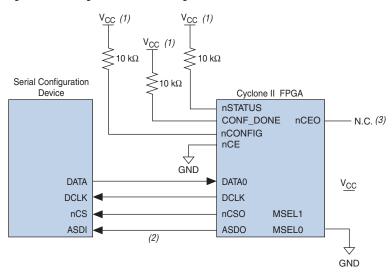

Figure 13–3. Single Device AS Configuration

#### Notes to Figure 13-3:

- (1) Connect the pull-up resistors to a 3.3-V supply.

- (2) Cyclone II devices use the ASDO to ASDI path to control the configuration device.

- (3) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed another device's nCE pin.

Upon power-up, the Cyclone II device goes through a POR. During POR, the device resets, holds <code>nSTATUS</code> and <code>CONF\_DONE</code> low, and tri-states all user I/O pins. After POR, which typically lasts 100 ms, the Cyclone II device releases <code>nSTATUS</code> and enters configuration mode when the external 10-k $\Omega$  resistor pulls the <code>nSTATUS</code> pin high. Once the FPGA successfully exits POR, all user I/O pins continue to be tri-stated. Cyclone II devices have weak pull-up resistors on the user I/O pins which are on before and during configuration.

The value of the weak pull-up resistors on the I/O pins that are on before and during configuration are available in the *DC Characteristics & Timing Specifications* chapter of the *Cyclone II Device Handbook*.

The configuration cycle consists of the reset, configuration, and initialization stages.

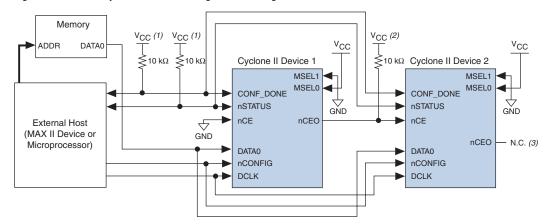

Figure 13–10. Multiple Device PS Configuration Using an External Host

Notes to Figure 13–10:

- (1) The pull-up resistor should be connected to a supply that provides an acceptable input signal for all devices in the chain.  $V_{CC}$  should be high enough to meet the  $V_{IH}$  specification of the I/O on the devices and the external host.

- (2) Connect the pull-up resistor to the V<sub>CCIO</sub> supply voltage of I/O bank that the nCEO pin resides in.

- (3) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed another device's nCE pin.

In multiple device PS configuration, connect the first Cyclone II device's nCE pin to GND and connect the nCEO pin to the nCE pin of the next Cyclone II device in the chain. Use an external 10-k $\Omega$  pull-up resistor to pull the Cyclone II device's nCEO pin high to its V<sub>CCIO</sub> level to help the internal weak pull-up resistor when the nCEO pin feeds next Cyclone II device's nCE pin. The input to the nCE pin of the last Cyclone II device in the chain comes from the previous Cyclone II device. After the first device completes configuration in a multiple device configuration chain, its nCEO pin transitions low to activate the second device's nCE pin, which prompts the second device to begin configuration. The second device in the chain begins configuration within one clock cycle. Therefore, the MAX II device begins to transfer data to the next Cyclone II device without interruption. The nCEO pin is a dual-purpose pin in Cyclone II devices. You can leave the nCEO pin of the last device unconnected or use it as a user I/O pin after configuration if the last device in chain is a Cyclone II device.

The Quartus II software sets the Cyclone II device nCEO pin as a dedicated output by default. If the nCEO pin feeds the next device's nCE pin, you must make sure that the nCEO pin is not used as a user I/O after configuration. This software setting is in the **Dual-Purpose Pins** tab of the **Device & Pin Options** dialog box in Quartus II software.

Upon power-up, the Cyclone II device goes through a POR. During POR, the device reset, holds <code>nSTATUS</code> and <code>CONF\_DONE</code> low, and tri-states all user I/O pins. After POR, which typically lasts 100 ms, the Cyclone II FPGA releases <code>nSTATUS</code> and enters configuration mode when this signal is pulled high by the external 10-k $\Omega$ resistor. Once the FPGA successfully exits POR, all user I/O pins continue to be tri-stated. Cyclone II devices have weak pull-up resistors on the user I/O pins which are on before and during configuration.

The configuration device also goes through a POR delay to allow the power supply to stabilize. The maximum POR time for EPC2 or EPC1 devices is 200 ms. The POR time for enhanced configuration devices can be set to 100 ms or 2 ms, depending on the enhanced configuration device's PORSEL pin setting. If the PORSEL pin is connected to ground, the POR delay is 100 ms. If the PORSEL pin is connected to  $V_{CC}$ , the POR delay is 2 ms. You must power the Cyclone II device before or during the enhanced configuration device POR time. During POR, the configuration device transitions its OE pin low. This low signal delays configuration because the OE pin is connected to the target device's nSTATUS pin. When the target and configuration devices complete POR, they both release the nSTATUS to OE line, which is then pulled high by a pull-up resistor.

When the power supplies have reached the appropriate operating voltages, the target FPGA senses the low-to-high transition on nconfig and initiates the configuration cycle. The configuration cycle consists of three stages: reset, configuration, and initialization.

The Cyclone II device does not have a PORSEL pin.

#### Reset Stage

While nCONFIG or nSTATUS is low, the device is in reset. You can delay configuration by holding the nCONFIG or nSTATUS pin low.

$V_{\rm CCINT}$  and  $V_{\rm CCIO}$  of the banks where the configuration and JTAG pins reside need to be fully powered to the appropriate voltage levels in order to begin the configuration process.

When the nconfig signal goes high, the device comes out of reset and releases the nstatus pin, which is pulled high by a pull-up resistor. Enhanced configuration and EPC2 devices have an optional internal pull-up resistor on the OE pin. You can turn on this option in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. If this internal pull-up resistor is not used, you need to connect an external  $10\text{-k}\Omega$  pull-up resistor to the OE and nstatus line. Once nstatus is released, the FPGA is ready to receive configuration data and the configuration stage begins.

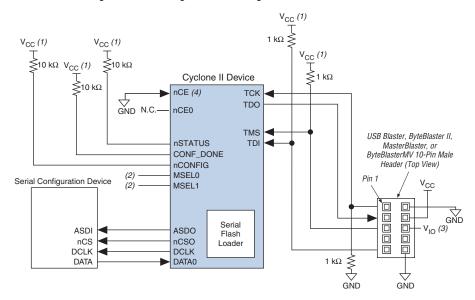

## **PS Configuration Using a Download Cable**

In PS configuration, an intelligent host (e.g., a PC) can use a download cable to transfer data from a storage device to the Cyclone II device. You can use the Altera USB-Blaster universal serial bus (USB) port download cable, MasterBlaster<sup>TM</sup> serial/USB communications cable, ByteBlaster II parallel port download cable, or the ByteBlasterMV<sup>TM</sup> parallel port as a download cable.

Upon power up, the Cyclone II device goes through POR, which lasts approximately 100 ms for non "A" devices. During POR, the device resets, holds nSTATUS low, and tri-states all user I/O pins. Once the FPGA successfully exits POR, the nSTATUS pin is released and all user I/O pins continue to be tri-stated.

The value of the weak pull-up resistors on the I/O pins that are on before and during configuration can be found in the *Cyclone II Device Handbook*.

The configuration cycle consists of three stages: reset, configuration, and initialization. While the nCONFIG or nSTATUS pins are low, the device is in reset. To initiate configuration in this scheme, the download cable generates a low-to-high transition on the nCONFIG pin.

Make sure  $V_{\text{CCINT}}$  and  $V_{\text{CCIO}}$  for the banks where the configuration and JTAG pins reside are powered to the appropriate voltage levels in order to begin the configuration process.

When nconfig transitions high, the Cyclone II device comes out of reset and begins configuration. The Cyclone II device releases the open-drain nstatus pin, which is then pulled high by an external 10-k  $\Omega$  pull-up resistor. Once nstatus transitions high, the Cyclone II device is ready to receive configuration data. The programming hardware or download cable then transmits the configuration data one bit at a time to the device's Data0 pin. The configuration data is clocked into the target device until Conf\_done goes high. The Conf\_done pin must have an external 10-k  $\Omega$  pull-up resistor in order for the device to initialize.

When using a download cable, you cannot use the **Auto-restart configuration after error** option. You must manually restart configuration in the Quartus II software when an error occurs. Additionally, you cannot use the **Enable user-supplied start-up clock (CLKUSR)** option when programming the FPGA using the Quartus II programmer and download cable. This option is disabled in the SOF. Therefore, if you turn on the CLKUSR option, you do not need to provide a clock on CLKUSR when you are configuring the FPGA with the

When designing a Cyclone II board for JTAG configuration, use the guidelines in Table 13–10 for the placement of the dedicated configuration pins.

| Table 13–10. D<br>Configuration | edicated Configuration Pin Connections During JTAG                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| nCE                             | On all Cyclone II devices in the chain, $nCE$ should be driven low by connecting it to ground, pulling it low via a resistor, or driving it by some control circuitry. For devices that are also in multiple device AS, or PS configuration chains, the $nCE$ pins should be connected to GND during JTAG configuration or JTAG configured in the same order as the configuration chain.                                                         |

| nCEO                            | On all Cyclone II devices in the chain, nCEO can be used as a user I/O or connected to the nCE of the next device. If nCEO is connected to the nCE of the next device, the nCEO pin must be pulled high to $V_{\text{CCIO}}$ by an external 10-k $\Omega$ pull-up resistor to help the internal weak pull-up resistor. If the nCEO pin is not connected to the nCE pin of the next device, you can use it as a user I/O pin after configuration. |

| MSEL                            | These pins must not be left floating. These pins support whichever non-JTAG configuration is used in production. If only JTAG configuration is used, you should tie these pins to ground.                                                                                                                                                                                                                                                        |

| nCONFIG                         | Driven high by connecting to $V_{\rm CC}$ , pulling up via a resistor, or driven high by some control circuitry.                                                                                                                                                                                                                                                                                                                                 |

| nSTATUS                         | Pull to $V_{CC}$ via a 10-k $\Omega$ resistor. When configuring multiple devices in the same JTAG chain, each <code>nSTATUS</code> pin should be pulled up to $V_{CC}$ individually. <code>nSTATUS</code> pulling low in the middle of JTAG configuration indicates that an error has occurred.                                                                                                                                                  |

| CONF_DONE                       | Pull to $V_{CC}$ via a 10-k $\Omega$ resistor. When configuring multiple devices in the same JTAG chain, each CONF_DONE pin should be pulled up to $V_{CC}$ individually. CONF_DONE going high at the end of JTAG configuration indicates successful configuration.                                                                                                                                                                              |

| DCLK                            | Should not be left floating. Drive low or high, whichever is more convenient on your board.                                                                                                                                                                                                                                                                                                                                                      |

Figure 13–23 shows JTAG configuration of a Cyclone II device with a microprocessor.

Figure 13–25. JTAG Configuration of a Single Device Using a Download Cable

#### Notes to Figure 13-25:

- (1) The pull-up resistor should be connected to the same supply voltage as the USB Blaster, MasterBlaster ( $V_{IO}$  pin), ByteBlaster II, or ByteBlasterMV cable.

- (2) The nconfig, MSEL[1..0] pins should be connected to support a non-JTAG configuration scheme. If only JTAG configuration is used, connect nconfig to V<sub>CC</sub>, and MSEL[1..0] to ground. Pull DCLK either high or low, whichever is convenient on your board.

- (3) Pin 6 of the header is a V<sub>IO</sub> reference voltage for the MasterBlaster output driver. V<sub>IO</sub> should match the device's V<sub>CCIO</sub>. Refer to the MasterBlaster Serial/USB Communications Cable Data Sheet for this value. In the ByteBlasterMV cable, this pin is a no connect. In the USB Blaster and ByteBlaster II cables, this pin is connected to nCE when it is used for active serial programming, otherwise it is a no connect.

- (4) nCE must be connected to GND or driven low for successful JTAG configuration.

### ISP of Serial Configuration Device

In the second stage, the serial flash loader design in the master Cyclone II device allows you to write the configuration data for the device chain into the serial configuration device by using the Cyclone II JTAG interface. The JTAG interface sends the programming data for the serial configuration device to the Cyclone II device first. The Cyclone II device then uses the ASMI pins to transmit the data to the serial configuration device.

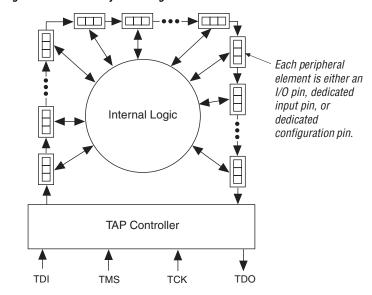

operate the TAP controller, and the  $\mathtt{TDI}$  and  $\mathtt{TDO}$  pins provide the serial path for the data registers. The  $\mathtt{TDI}$  pin also provides data to the instruction register, which then generates control logic for the data registers.

# IEEE Std. 1149.1 Boundary-Scan Register

The boundary-scan register is a large serial shift register that uses the TDI pin as an input and the TDO pin as an output. The boundary-scan register consists of 3-bit peripheral elements that are associated with Cyclone II I/O pins. You can use the boundary-scan register to test external pin connections or to capture internal data.

See the *Configuration & Testing* chapter in Volume 1 of the *Cyclone II Device Handbook* for the Cyclone II device boundary-scan register lengths.

Figure 14–3 shows how test data is serially shifted around the periphery of the IEEE Std. 1149.1 device.

Figure 14-3. Boundary-Scan Register

## Boundary-Scan Cells of a Cyclone II Device I/O Pin

The Cyclone II device 3-bit boundary-scan cell (BSC) consists of a set of capture registers and a set of update registers. The capture registers can connect to internal device data via the OUTJ and OEJ signals, and connect

Section VII-2 Altera Corporation