Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 2076                                                     |

| Number of Logic Elements/Cells | 33216                                                    |

| Total RAM Bits                 | 483840                                                   |

| Number of I/O                  | 322                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 484-FBGA                                                 |

| Supplier Device Package        | 484-UBGA (19x19)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c35u484i8n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- DSP intellectual property (IP) cores

- DSP Builder interface to The Mathworks Simulink and Matlab design environment

- DSP Development Kit, Cyclone II Edition

Cyclone II devices include a powerful FPGA feature set optimized for low-cost applications including a wide range of density, memory, embedded multiplier, and packaging options. Cyclone II devices support a wide range of common external memory interfaces and I/O protocols required in low-cost applications. Parameterizable IP cores from Altera and partners make using Cyclone II interfaces and protocols fast and easy.

## **Features**

The Cyclone II device family offers the following features:

- High-density architecture with 4,608 to 68,416 LEs

- M4K embedded memory blocks

- Up to 1.1 Mbits of RAM available without reducing available logic

- 4,096 memory bits per block (4,608 bits per block including 512 parity bits)

- Variable port configurations of ×1, ×2, ×4, ×8, ×9, ×16, ×18, ×32, and ×36

- True dual-port (one read and one write, two reads, or two writes) operation for ×1, ×2, ×4, ×8, ×9, ×16, and ×18 modes

- Byte enables for data input masking during writes

- Up to 260-MHz operation

#### Embedded multipliers

- Up to 150 18- x 18-bit multipliers are each configurable as two independent 9- x 9-bit multipliers with up to 250-MHz performance

- Optional input and output registers

#### Advanced I/O support

- High-speed differential I/O standard support, including LVDS, RSDS, mini-LVDS, LVPECL, differential HSTL, and differential SSTL

- Single-ended I/O standard support, including 2.5-V and 1.8-V, SSTL class I and II, 1.8-V and 1.5-V HSTL class I and II, 3.3-V PCI and PCI-X 1.0, 3.3-, 2.5-, 1.8-, and 1.5-V LVCMOS, and 3.3-, 2.5-, and 1.8-V LVTTL

- Peripheral Component Interconnect Special Interest Group (PCI SIG) PCI Local Bus Specification, Revision 3.0 compliance for 3.3-V operation at 33 or 66 MHz for 32- or 64-bit interfaces

- PCI Express with an external TI PHY and an Altera PCI Express ×1 Megacore<sup>®</sup> function

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, M4K memory blocks, embedded multipliers, and IOEs. C16 column interconnects drive to other row and column interconnects at every fourth LAB. C16 column interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly. C16 interconnects can drive R24, R4, C16, and C4 interconnects.

# **Device Routing**

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (for example, M4K memory, embedded multiplier, or PLL) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB.

Table 2–1 shows the Cyclone II device's routing scheme.

| Table 2–1. Cy               | Table 2–1. Cyclone II Device Routing Scheme (Part 1 of 2) |                    |                          |                 |                  |                 |                  |          |               |                     |          |            |          |

|-----------------------------|-----------------------------------------------------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|----------|---------------|---------------------|----------|------------|----------|

|                             |                                                           | Destination        |                          |                 |                  |                 |                  |          |               |                     |          |            |          |

| Source                      | Register Chain                                            | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | 31       | M4K RAM Block | Embedded Multiplier | PLL      | Column 10E | Row IOE  |

| Register<br>Chain           |                                                           |                    |                          |                 |                  |                 |                  | <b>~</b> |               |                     |          |            |          |

| Local<br>Interconnect       |                                                           |                    |                          |                 |                  |                 |                  | ~        | ~             | ~                   | <b>✓</b> | ~          | <b>✓</b> |

| Direct Link<br>Interconnect |                                                           | ~                  |                          |                 |                  |                 |                  |          |               |                     |          |            |          |

| R4<br>Interconnect          |                                                           | ~                  |                          | <b>✓</b>        | ~                | ~               | <b>✓</b>         |          |               |                     |          |            |          |

| R24<br>Interconnect         |                                                           |                    |                          | <b>✓</b>        | ~                | ~               | <b>✓</b>         |          |               |                     |          |            |          |

| C4<br>Interconnect          |                                                           | ~                  |                          | <b>✓</b>        | ~                | ~               | <b>✓</b>         |          |               |                     |          |            |          |

| C16<br>Interconnect         |                                                           |                    |                          | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>         |          |               |                     |          |            |          |

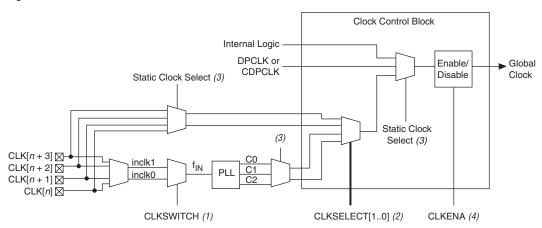

Of the sources listed, only two clock pins, two PLL clock outputs, one DPCLK pin, and one internally-generated signal are chosen to drive into a clock control block. Figure 2–13 shows a more detailed diagram of the clock control block. Out of these six inputs, the two clock input pins and two PLL outputs can be dynamic selected to feed a global clock network. The clock control block supports static selection of DPCLK and the signal from internal logic.

Figure 2-13. Clock Control Block

#### *Notes to Figure 2–13:*

- (1) The CLKSWITCH signal can either be set through the configuration file or it can be dynamically set when using the manual PLL switchover feature. The output of the multiplexer is the input reference clock (f<sub>IN</sub>) for the PLL.

- (2) The CLKSELECT[1..0] signals are fed by internal logic and can be used to dynamically select the clock source for the global clock network when the device is in user mode.

- (3) The static clock select signals are set in the configuration file and cannot be dynamically controlled when the device is in user mode.

- (4) Internal logic can be used to enabled or disabled the global clock network in user mode.

| Table 2–16. Programi | Table 2–16. Programmable Drive Strength (Part 2 of 2) Note (1) |               |  |  |  |  |

|----------------------|----------------------------------------------------------------|---------------|--|--|--|--|

| I/O Standard         | I <sub>OH</sub> /I <sub>OL</sub> Current Strength Setting (mA) |               |  |  |  |  |

| i/O Stalluaru        | Top & Bottom I/O Pins                                          | Side I/O Pins |  |  |  |  |

| LVCMOS (1.5 V)       | 2                                                              | 2             |  |  |  |  |

|                      | 4                                                              | 4             |  |  |  |  |

|                      | 6                                                              | 6             |  |  |  |  |

|                      | 8                                                              |               |  |  |  |  |

| SSTL-2 class I       | 8                                                              | 8             |  |  |  |  |

|                      | 12                                                             | 12            |  |  |  |  |

| SSTL-2 class II      | 16                                                             | 16            |  |  |  |  |

|                      | 20                                                             |               |  |  |  |  |

|                      | 24                                                             |               |  |  |  |  |

| SSTL-18 class I      | 6                                                              | 6             |  |  |  |  |

|                      | 8                                                              | 8             |  |  |  |  |

|                      | 10                                                             | 10            |  |  |  |  |

|                      | 12                                                             |               |  |  |  |  |

| SSTL-18 class II     | 16                                                             |               |  |  |  |  |

|                      | 18                                                             |               |  |  |  |  |

| HSTL-18 class I      | 8                                                              | 8             |  |  |  |  |

|                      | 10                                                             | 10            |  |  |  |  |

|                      | 12                                                             | 12            |  |  |  |  |

| HSTL-18 class II     | 16                                                             |               |  |  |  |  |

|                      | 18                                                             |               |  |  |  |  |

|                      | 20                                                             |               |  |  |  |  |

| HSTL-15 class I      | 8                                                              | 8             |  |  |  |  |

|                      | 10                                                             |               |  |  |  |  |

|                      | 12                                                             |               |  |  |  |  |

| HSTL-15 class II     | 16                                                             |               |  |  |  |  |

Note to Table 2–16:

The default current in the Quartus II software is the maximum setting for each I/O standard.

# **Open-Drain Output**

Cyclone II devices provide an optional open-drain (equivalent to an open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (that is, interrupt and write-enable signals) that can be asserted by any of several devices.

Cyclone II devices also use the JTAG port to monitor the logic operation of the device with the SignalTap $^{\$}$  II embedded logic analyzer. Cyclone II devices support the JTAG instructions shown in Table 3–1.

| Table 3–1. Cyclone | II JTAG Instructions | (Part 1 of 2)                                                                                                                                                                                                                                                                   |

|--------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Instruction   | Instruction Code     | Description                                                                                                                                                                                                                                                                     |

| SAMPLE/PRELOAD     | 00 0000 0101         | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap II embedded logic analyzer.                                         |

| EXTEST (1)         | 00 0000 1111         | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                                                             |

| BYPASS             | 11 1111 1111         | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                                                     |

| USERCODE           | 00 0000 0111         | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                       |

| IDCODE             | 00 0000 0110         | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                                                           |

| HIGHZ (1)          | 00 0000 1011         | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                              |

| CLAMP (1)          | 00 0000 1010         | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register. |

| ICR instructions   |                      | Used when configuring a Cyclone II device via the JTAG port with a USB Blaster <sup>™</sup> , ByteBlaster <sup>™</sup> II, MasterBlaster <sup>™</sup> or ByteBlasterMV <sup>™</sup> download cable, or when using a Jam File or JBC File via an embedded processor.             |

| PULSE_NCONFIG      | 00 0000 0001         | Emulates pulsing the nCONFIG pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                     |

# EP2C70 Clock Timing Parameters

Tables 5–33 and 5–34 show the clock timing parameters for EP2C70 devices.

| Table 5–33. EP2C70 Column Pins Global Clock Timing Parameters |            |            |          |          |          |      |  |  |

|---------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|

| Doromotor                                                     | Fast (     | Corner     | -6 Speed | -7 Speed | -8 Speed | Unit |  |  |

| Parameter                                                     | Industrial | Commercial | Grade    | Grade    | Grade    | Unit |  |  |

| $t_{CIN}$                                                     | 1.575      | 1.651      | 2.914    | 3.105    | 3.174    | ns   |  |  |

| t <sub>COUT</sub>                                             | 1.589      | 1.666      | 2.948    | 3.137    | 3.203    | ns   |  |  |

| t <sub>PLLCIN</sub>                                           | -0.149     | -0.158     | 0.27     | 0.268    | 0.089    | ns   |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.135     | -0.143     | 0.304    | 0.3      | 0.118    | ns   |  |  |

| Table 5–34. EP2C70 Row Pins Global Clock Timing Parameters |             |            |          |          |          |       |  |  |

|------------------------------------------------------------|-------------|------------|----------|----------|----------|-------|--|--|

| Parameter                                                  | Fast Corner |            | -6 Speed | -7 Speed | -8 Speed | Unit  |  |  |

| Parameter                                                  | Industrial  | Commercial | Grade    | Grade    | Grade    | UIIIL |  |  |

| t <sub>CIN</sub>                                           | 1.463       | 1.533      | 2.753    | 2.927    | 3.010    | ns    |  |  |

| t <sub>COUT</sub>                                          | 1.465       | 1.535      | 2.769    | 2.940    | 3.018    | ns    |  |  |

| t <sub>PLLCIN</sub>                                        | -0.261      | -0.276     | 0.109    | 0.09     | -0.075   | ns    |  |  |

| t <sub>PLLCOUT</sub>                                       | -0.259      | -0.274     | 0.125    | 0.103    | -0.067   | ns    |  |  |

#### **Clock Network Skew Adders**

Table 5–35 shows the clock network specifications.

| Table 5–35. Clock Network Specifications            |                                                |      |      |  |  |

|-----------------------------------------------------|------------------------------------------------|------|------|--|--|

| Name                                                | Description                                    | Max  | Unit |  |  |

| Clock skew adder                                    | Inter-clock network, same bank                 | ±88  | ps   |  |  |

| EP2C5/A, EP2C8/A (1)                                | Inter-clock network, same side and entire chip | ±88  | ps   |  |  |

| Clock skew adder                                    | Inter-clock network, same bank                 | ±118 | ps   |  |  |

| EP2C15A, EP2C20/A,<br>EP2C35, EP2C50,<br>EP2C70 (1) | Inter-clock network, same side and entire chip | ±138 | ps   |  |  |

Note to Table 5-35:

This is in addition to intra-clock network skew, which is modeled in the Quartus II software.

# PLL Specifications

See the *DC & Switching Characteristics* chapter in Volume 1 of the *Cyclone II Device Handbook* for information on PLL timing specifications.

# **Clocking**

Cyclone II devices provide up to 16 dedicated clock pins (CLK[15..0]) that can drive the global clock networks. The smaller Cyclone II devices (EP2C5 and EP2C8 devices) support four dedicated clock pins on each side (left and right) capable of driving a total of eight global clock networks, while the larger devices (EP2C15 devices and larger) support four clock pins on all four sides of the device. These clock pins can drive a total of 16 global clock networks.

Table 7–7 shows the number of global clocks available across the Cyclone II family members.

| Table 7–7. Number of Global Clocks Available in Cyclone II Devices |                         |  |  |  |

|--------------------------------------------------------------------|-------------------------|--|--|--|

| Device                                                             | Number of Global Clocks |  |  |  |

| EP2C5                                                              | 8                       |  |  |  |

| EP2C8                                                              | 8                       |  |  |  |

| EP2C15                                                             | 16                      |  |  |  |

| EP2C20                                                             | 16                      |  |  |  |

| EP2C35                                                             | 16                      |  |  |  |

| EP2C50                                                             | 16                      |  |  |  |

| EP2C70                                                             | 16                      |  |  |  |

#### **Global Clock Network**

Global clocks drive throughout the entire device, feeding all device quadrants. All resources within the device (IOEs, logic array blocks (LABs), dedicated multiplier blocks, and M4K memory blocks) can use the global clock networks as clock sources. These clock network resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed by an external pin. Internal logic can also drive the global clock networks for internally generated global clocks and asynchronous clears, clock enables, or other control signals with high fan-out.

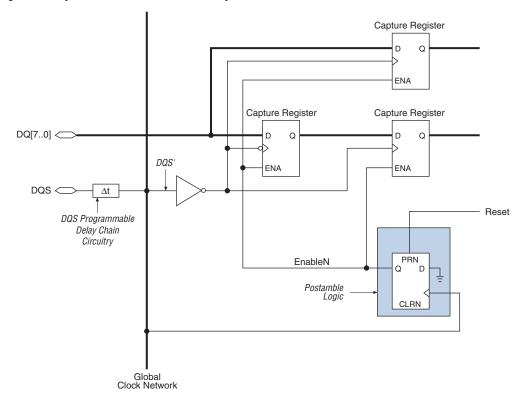

Figure 9-9. Cyclone II DQS Postamble Circuitry Connection

Figure 9–10 shows the timing waveform for Figure 9–9. When the postamble logic detects the falling DQS edge at the start of postamble, it sends out a signal to disable the capture registers to prevent any accidental latching.

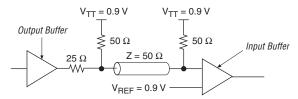

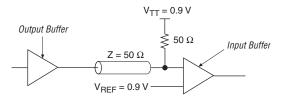

Figure 10-6. 1.8-V SSTL Class II Termination

#### 1.8-V HSTL Class I and II

The HSTL standard is a technology independent I/O standard developed by JEDEC to provide voltage scalability. It is used for applications designed to operate in the 0.0- to 1.8-V HSTL logic switching range such as quad data rate (QDR) memory clock interfaces.

Although JEDEC specifies a maximum  $V_{CCIO}$  value of 1.6 V, there are various memory chip vendors with HSTL standards that require a  $V_{CCIO}$  of 1.8 V. Cyclone II devices support interfaces with  $V_{CCIO}$  of 1.8 V for HSTL. Figures 10–7 and 10–8 show the nominal  $V_{REF}$  and  $V_{TT}$  required to track the higher value of  $V_{CCIO}$ . The value of  $V_{REF}$  is selected to provide optimum noise margin in the system. Cyclone II devices support both input and output levels of operation.

Figure 10-7. 1.8-V HSTL Class I Termination

Figure 10-8. 1.8-V HSTL Class II Termination

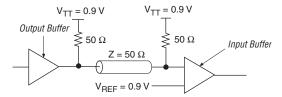

Figure 10–19. EP2C5 and EP2C8 Device I/O Banks Notes (1), (2)

Regular I/O Bank

Regular I/O Bank

#### Notes to Figure 10–19:

- (1) This is a top view of the silicon die.

- (2) This is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

| Table 11–1. LVDS I/O Specifications (Part 2 of 2) Note (1) |                                           |                        |     |     |      |       |  |

|------------------------------------------------------------|-------------------------------------------|------------------------|-----|-----|------|-------|--|

| Symbol                                                     | Parameter                                 | Condition              | Min | Тур | Max  | Units |  |

| V <sub>ID</sub>                                            | Input differential voltage (single-ended) |                        | 0.1 |     | 0.65 | V     |  |

| V <sub>ICM</sub>                                           | Input common mode voltage                 |                        | 0.1 |     | 2.0  | V     |  |

| $\Delta V_{OS}$                                            | Change in V <sub>OS</sub> between H and L | R <sub>L</sub> = 100 Ω |     |     | 50   | mV    |  |

| R <sub>L</sub>                                             | Receiver differential input resistor      |                        | 90  | 100 | 110  | Ω     |  |

Note to Table 11-1:

(1) The specifications apply at the resistor network output.

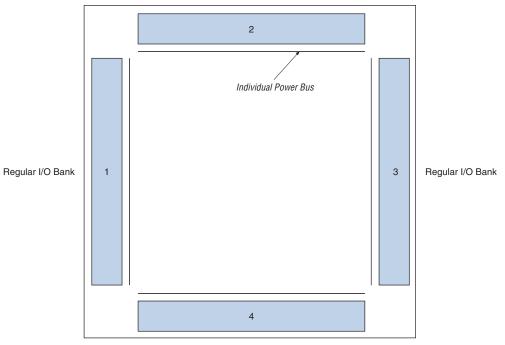

#### LVDS Receiver & Transmitter

Figure 11–3 shows a simple point-to-point LVDS application where the source of the data is an LVDS transmitter. These LVDS signals are typically transmitted over a pair of printed circuit board (PCB) traces, but a combination of a PCB trace, connectors, and cables is a common application setup.

Figure 11-3. Typical LVDS Application

Figures 11–4 and 11–5 show the signaling levels for LVDS receiver inputs and transmitter outputs, respectively.

Figure 11–9 shows the mini-LVDS receiver and transmitter signal waveforms.

Positive Channel (p) = V<sub>OH</sub>

V<sub>OD</sub>

Negative Channel (n) = V<sub>OL</sub>

Ground

V<sub>OD</sub>

V<sub>OD</sub>

V<sub>OD</sub>

Figure 11–9. Transmitter Output Signal Level Waveforms for mini-LVDS Note (1)

Note to Figure 11-9:

(1) The  $V_{OD}$  specifications apply at the resistor network output.

## Designing with mini-LVDS

Similar to RSDS, Cyclone II devices support the mini-LVDS output standard using the LVDS I/O buffer types. For transmitters, the LVDS output buffer can be used with the external resistor network shown in Figure 11–10. The resistor values chosen should satisfy the equation on page 11-8.

Section V-2 Altera Corporation

| Table 13–1. Cyclone II Configuration Schemes |     |     |  |  |  |

|----------------------------------------------|-----|-----|--|--|--|

| Configuration Scheme MSEL1 MSEL0             |     |     |  |  |  |

| AS (20 MHz)                                  | 0   | 0   |  |  |  |

| PS                                           | 0   | 1   |  |  |  |

| Fast AS (40 MHz) (1)                         | 1   | 0   |  |  |  |

| JTAG-based Configuration (2)                 | (3) | (3) |  |  |  |

#### Notes to Table 13–1:

- (1) Only the EPCS16 and EPCS64 devices support a DCLK up to 40 MHz clock; other EPCS devices support a DCLK up to 20 MHz. Refer to the Serial Configuration Devices Data Sheet for more information.

- (2) JTAG-based configuration takes precedence over other configuration schemes, which means MSEL pin settings are ignored.

- (3) Do not leave the MSEL pins floating; connect them to  $V_{\rm CCIO}$  or ground. These pins support the non-JTAG configuration scheme used in production. If you are only using JTAG configuration, you should connect the MSEL pins to ground.

You can download configuration data to Cyclone II FPGAs with the AS, PS, or JTAG interfaces using the options in Table 13–2.

| Table 13–2. Cyclone II Device Configuration Schemes |                                                                                                                                                                                    |  |  |  |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Configuration Scheme                                | Description                                                                                                                                                                        |  |  |  |

| AS configuration                                    | Configuration using serial configuration devices (EPCS1, EPCS4, EPCS16 or EPCS64 devices)                                                                                          |  |  |  |

| PS configuration                                    | Configuration using enhanced configuration devices (EPC4, EPC8, and EPC16 devices), EPC2 and EPC1 configuration devices, an intelligent host (microprocessor), or a download cable |  |  |  |

| JTAG-based configuration                            | Configuration via JTAG pins using a download cable, an intelligent host (microprocessor), or the Jam™ Standard Test and Programming Language (STAPL)                               |  |  |  |

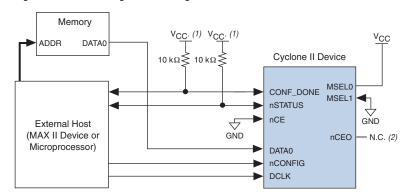

Figure 13–9. Single Device PS Configuration Using an External Host

#### Notes to Figure 13-9:

- Connect the pull-up resistor to a supply that provides an acceptable input signal for the device. V<sub>CC</sub> should be high

enough to meet the VIH specification of the I/O on the device and the external host.

- (2) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

Upon power-up, the Cyclone II device goes through a POR, which lasts approximately 100 ms. During POR, the device resets, holds nSTATUS low, and tri-states all user I/O pins. Once the FPGA successfully exits POR, all user I/O pins continue to be tri-stated.

The value of the weak pull-up resistors on the I/O pins that are on before and during configuration can be found in the *Cyclone II Device Handbook*.

The configuration cycle consists of three stages: reset, configuration, and initialization.

#### Reset Stage

While the Cyclone II device's nCONFIG or nSTATUS pins are low, the device is in reset. To initiate configuration, the MAX II device must transition the Cyclone II nCONFIG pin from low to high.

$V_{\text{CCINT}}$  and  $V_{\text{CCIO}}$  of the banks where the configuration and JTAG pins reside need to be fully powered to the appropriate voltage levels in order to begin the configuration process.

When the Cyclone II nconfig pin transitions high, the Cyclone II device comes out of reset and releases the open-drain nstatus pin, which is then pulled high by an external 10-k $\Omega$ pull-up resistor. Once nstatus is released, the FPGA is ready to receive configuration data and the MAX II device can start the configuration at any time.

All information in the "Single Device PS Configuration Using a MAX II Device as an External Host" on page 13–22 section is also applicable when using a microprocessor as an external host. Refer to that section for all configuration information.

The MicroBlaster™ software driver allows you to configure Altera FPGAs, including Cyclone II devices, through the ByteBlaster II or ByteBlasterMV cable in PS mode. The MicroBlaster software driver supports a RBF programming input file and is targeted for embedded PS configuration. The source code is developed for the Windows NT operating system, although you can customize it to run on other operating systems.

Since the Cyclone II device can decompress the compressed configuration data on-the-fly during PS configuration, the MicroBlaster software can accept a compressed RBF file as its input file.

For more information on the MicroBlaster software driver, see the *Configuring the MicroBlaster Passive Serial Software Driver White Paper* and source files on the Altera web site at **www.altera.com**.

If you turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Quartus II software, the Cyclone II devices does not enter user mode after the MicroBlaster has transmitted all the configuration data in the RBF file. You need to supply enough initialization clock cycles to CLKUSR pin to enter user mode.

# Single Device PS Configuration Using a Configuration Device

You can use an Altera configuration device (for example, an EPC2, EPC1, or enhanced configuration device) to configure Cyclone II devices using a serial configuration bitstream. Configuration data is stored in the configuration device. Figure 13–13 shows the configuration interface connections between the Cyclone II device and a configuration device.

The figures in this chapter only show the configuration-related pins and the configuration pin connections between the configuration device and the FPGA.

device releases its <code>nSTATUS</code> pin after a reset time-out period (maximum of 40 µs). When the <code>nSTATUS</code> pin is released and pulled high by a pull-up resistor, the configuration device reconfigures the chain. If this option is turned off, the external system must monitor <code>nSTATUS</code> for errors and then pulse <code>nCONFIG</code> low for at least 2 µs to restart configuration. The external system can pulse the <code>nCONFIG</code> pin if the pin is under system control rather than tied to  $V_{CC}$ .

Additionally, if the configuration device sends all of its data and then detects that the CONF\_DONE pin has not transitioned high, it recognizes that the FPGA has not configured successfully. Enhanced configuration devices wait for 64 DCLK cycles after the last configuration bit was sent for the CONF\_DONE pin to transition high. EPC2 devices wait for 16 DCLK cycles. After that, the configuration device pulls its OE pin low, which in turn drives the target device's nSTATUS pin low. If you turn on the **Autorestart configuration after error** option in the Quartus II software, the target device resets and then releases its nSTATUS pin after a reset timeout period (maximum of 40 µs). When nSTATUS transitions high again, the configuration device reconfigures the FPGA.

For more information on configuration issues, see the *Debugging Configuration Problems* chapter of the *Configuration Handbook* and the FPGA Configuration Troubleshooter on the Altera web site (www.altera.com).

# Multiple Device PS Configuration Using a Configuration Device

You can use Altera enhanced configuration devices (EPC16, EPC8, and EPC4 devices) or EPC2 and EPC1 configuration devices to configure multiple Cyclone II devices in a PS configuration chain.

Figure 13–14 shows how to configure multiple devices with an enhanced configuration device. This circuit is similar to the configuration device circuit for a single device, except Cyclone II devices are cascaded for multiple device configuration.

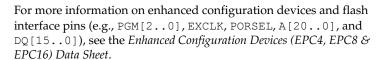

### Single Device JTAG Configuration

During JTAG configuration, you can use the USB-Blaster, MasterBlaster, ByteBlaster II, or ByteBlasterMV download cable to download data to the device. Configuring Cyclone II devices through a cable is similar to programming devices in system. Figure 13–22 shows JTAG configuration of a single Cyclone II device using a download cable.

Figure 13-22. JTAG Configuration of a Single Device Using a Download Cable

#### Notes to Figure 13-22:

- The pull-up resistor should be connected to the same supply voltage as the USB-Blaster, MasterBlaster (VIO pin), ByteBlaster II, or ByteBlasterMV cable.

- (2) Connect the nCONFIG and MSEL[1..0] pins to support a non-JTAG configuration scheme. If only JTAG configuration is used, connect the nCONFIG pin to V<sub>CC</sub>, and the MSEL[1..0] pins to ground. In addition, pull DCLK and DATAO to either high or low, whichever is convenient on your board.

- (3) Pin 6 of the header is a V<sub>IO</sub> reference voltage for the MasterBlaster output driver. V<sub>IO</sub> should match the device's V<sub>CCIO</sub>. Refer to the MasterBlaster Serial/USB Communications Cable Data Sheet for this value. In the ByteBlasterMV, this pin is a no connect. In the USB-Blaster and ByteBlaster II, this pin is connected to nCE when it is used for AS programming, otherwise it is a no connect.

- (4) nce must be connected to GND or driven low for successful JTAG configuration.

- (5) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

To configure a single device in a JTAG chain, the programming software places all other devices in BYPASS mode. In BYPASS mode, Cyclone II devices pass programming data from the TDI pin to the TDO pin through a single bypass register without being affected internally. This scheme

| Table 13–11. | Table 13–11. Dedicated Configuration Pins on the Cyclone II Device (Part 2 of 5) |                         |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|--------------|----------------------------------------------------------------------------------|-------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name     | User<br>Mode                                                                     | Configuration<br>Scheme | Pin Type                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| nSTATUS      | N/A                                                                              | All                     | Bidirectional open-drain | The Cyclone II device drives nSTATUS low immediately after power-up and releases it after the POR time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|              |                                                                                  |                         |                          | This pin provides a status output and input for the Cyclone II device. If the Cyclone II device detects an error during configuration, it drives the nSTATUS pin low to stop configuration. If an external source (for example, another Cyclone II device) drives the nSTATUS pin low during configuration or initialization, the target device enters an error state.  Driving nSTATUS low after configuration and initialization does not affect the configured device. If your design uses a configuration device, driving nSTATUS low causes the configuration device to attempt to configure the FPGA, but since the FPGA ignores transitions on nSTATUS in user mode, the |  |  |  |

|              |                                                                                  |                         |                          | FPGA does not reconfigure. To initiate a reconfiguration, pull the nCONFIG pin low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|              |                                                                                  |                         |                          | The enhanced configuration devices' and EPC2 devices' OE and nCS pins are connected to the Cyclone II device's nSTATUS and CONF_DONE pins, respectively, and have optional internal programmable pull-up resistors. If you use these internal pull-up resistors on the enhanced configuration device, do not use external $10\text{-}k\Omega$ pull-up resistors on these pins. When using EPC2 devices, you should only use external $10\text{-}k\Omega$ pull-up resistors.                                                                                                                                                                                                     |  |  |  |

|              |                                                                                  |                         |                          | The input buffer on this pin supports hysteresis using Schmitt trigger circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

frequency (up to 40 MHz), which reduces your configuration time. In addition, Cyclone II devices can receive a compressed configuration bitstream and decompress this data on-the-fly in the AS or PS configuration scheme, which further reduces storage requirements and configuration time.