Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 3158                                                     |

| Number of Logic Elements/Cells | 50528                                                    |

| Total RAM Bits                 | 594432                                                   |

| Number of I/O                  | 294                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 484-BGA                                                  |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c50f484c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1. Introduction

CII51001-3.2

### Introduction

Following the immensely successful first-generation Cyclone® device family, Altera® Cyclone II FPGAs extend the low-cost FPGA density range to 68,416 logic elements (LEs) and provide up to 622 usable I/O pins and up to 1.1 Mbits of embedded memory. Cyclone II FPGAs are manufactured on 300-mm wafers using TSMC's 90-nm low-k dielectric process to ensure rapid availability and low cost. By minimizing silicon area, Cyclone II devices can support complex digital systems on a single chip at a cost that rivals that of ASICs. Unlike other FPGA vendors who compromise power consumption and performance for low-cost, Altera's latest generation of low-cost FPGAs—Cyclone II FPGAs, offer 60% higher performance and half the power consumption of competing 90-nm FPGAs. The low cost and optimized feature set of Cyclone II FPGAs make them ideal solutions for a wide array of automotive, consumer, communications, video processing, test and measurement, and other end-market solutions. Reference designs, system diagrams, and IP, found at www.altera.com, are available to help you rapidly develop complete end-market solutions using Cyclone II FPGAs.

## **Low-Cost Embedded Processing Solutions**

Cyclone II devices support the Nios II embedded processor which allows you to implement custom-fit embedded processing solutions. Cyclone II devices can also expand the peripheral set, memory, I/O, or performance of embedded processors. Single or multiple Nios II embedded processors can be designed into a Cyclone II device to provide additional co-processing power or even replace existing embedded processors in your system. Using Cyclone II and Nios II together allow for low-cost, high-performance embedded processing solutions, which allow you to extend your product's life cycle and improve time to market over standard product solutions.

#### **Low-Cost DSP Solutions**

Use Cyclone II FPGAs alone or as DSP co-processors to improve price-to-performance ratios for digital signal processing (DSP) applications. You can implement high-performance yet low-cost DSP systems with the following Cyclone II features and design support:

- Up to  $150 18 \times 18$  multipliers

- Up to 1.1 Mbit of on-chip embedded memory

- High-speed interfaces to external memory

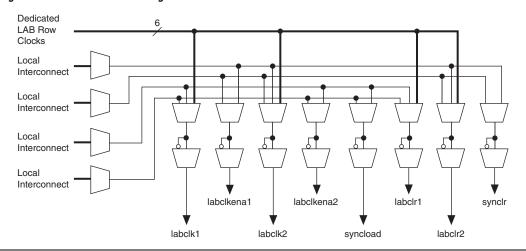

This gives a maximum of seven control signals at a time. When using the LAB-wide synchronous load, the clkena of labclk1 is not available. Additionally, register packing and synchronous load cannot be used simultaneously.

Each LAB can have up to four non-global control signals. Additional LAB control signals can be used as long as they are global signals.

Synchronous clear and load signals are useful for implementing counters and other functions. The synchronous clear and synchronous load signals are LAB-wide signals that affect all registers in the LAB.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked. For example, any LE in a particular LAB using the labclk1 signal also uses labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses both LAB-wide clock signals. De-asserting the clock enable signal turns off the LAB-wide clock.

The LAB row clocks [5..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack<sup>T</sup> interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–7 shows the LAB control signal generation circuit.

Figure 2-7. LAB-Wide Control Signals

LAB-wide signals control the logic for the register's clear signal. The LE directly supports an asynchronous clear function. Each LAB supports up to two asynchronous clear signals (labclr1 and labclr2).

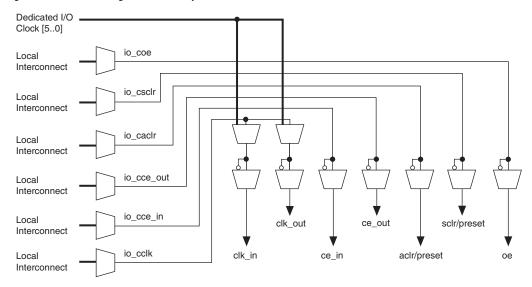

Figure 2-24. Control Signal Selection per IOE

In normal bidirectional operation, you can use the input register for input data requiring fast setup times. The input register can have its own clock input and clock enable separate from the OE and output registers. You can use the output register for data requiring fast clock-to-output performance. The OE register is available for fast clock-to-output enable timing. The OE and output register share the same clock source and the same clock enable source from the local interconnect in the associated LAB, dedicated I/O clocks, or the column and row interconnects. All registers share sclr and aclr, but each register can individually disable sclr and aclr. Figure 2–25 shows the IOE in bidirectional configuration.

| Table 2–18. Cyclone II Device LVDS Channels (Part 2 of 2) |           |                                |  |  |  |  |  |  |

|-----------------------------------------------------------|-----------|--------------------------------|--|--|--|--|--|--|

| Device                                                    | Pin Count | Number of LVDS<br>Channels (1) |  |  |  |  |  |  |

| EP2C70                                                    | 672       | 160 (168)                      |  |  |  |  |  |  |

|                                                           | 896       | 257 (265)                      |  |  |  |  |  |  |

Note to Table 2-18:

(1) The first number represents the number of bidirectional I/O pins which can be used as inputs or outputs. The number in parenthesis includes dedicated clock input pin pairs which can only be used as inputs.

You can use I/O pins and internal logic to implement a high-speed I/O receiver and transmitter in Cyclone II devices. Cyclone II devices do not contain dedicated serialization or deserialization circuitry. Therefore, shift registers, internal PLLs, and IOEs are used to perform serial-to-parallel conversions on incoming data and parallel-to-serial conversion on outgoing data.

The maximum internal clock frequency for a receiver and for a transmitter is 402.5 MHz. The maximum input data rate of 805 Mbps and the maximum output data rate of 640 Mbps is only achieved when DDIO registers are used. The LVDS standard does not require an input reference voltage, but it does require a  $100\text{-}\Omega$  termination resistor between the two signals at the input buffer. An external resistor network is required on the transmitter side.

For more information on Cyclone II differential I/O interfaces, see the *High-Speed Differential Interfaces in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

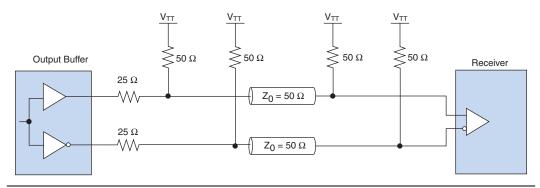

## **Series On-Chip Termination**

On-chip termination helps to prevent reflections and maintain signal integrity. This also minimizes the need for external resistors in high pin count ball grid array (BGA) packages. Cyclone II devices provide I/O driver on-chip impedance matching and on-chip series termination for single-ended outputs and bidirectional pins.

Cyclone II devices also use the JTAG port to monitor the logic operation of the device with the SignalTap $^{\$}$  II embedded logic analyzer. Cyclone II devices support the JTAG instructions shown in Table 3–1.

| Table 3–1. Cyclone | II JTAG Instructions | (Part 1 of 2)                                                                                                                                                                                                                                                                   |

|--------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Instruction   | Instruction Code     | Description                                                                                                                                                                                                                                                                     |

| SAMPLE/PRELOAD     | 00 0000 0101         | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap II embedded logic analyzer.                                         |

| EXTEST (1)         | 00 0000 1111         | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                                                             |

| BYPASS             | 11 1111 1111         | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                                                     |

| USERCODE           | 00 0000 0111         | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                       |

| IDCODE             | 00 0000 0110         | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                                                           |

| HIGHZ (1)          | 00 0000 1011         | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                              |

| CLAMP (1)          | 00 0000 1010         | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register. |

| ICR instructions   |                      | Used when configuring a Cyclone II device via the JTAG port with a USB Blaster <sup>™</sup> , ByteBlaster <sup>™</sup> II, MasterBlaster <sup>™</sup> or ByteBlasterMV <sup>™</sup> download cable, or when using a Jam File or JBC File via an embedded processor.             |

| PULSE_NCONFIG      | 00 0000 0001         | Emulates pulsing the nCONFIG pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                     |

| Table 5–44. Maximum Input Clock Toggle Rate on Cyclone II Devices (Part 2 of 2) |                                                             |                      |                      |                      |                      |                      |                           |                      |                      |  |  |

|---------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------------|----------------------|----------------------|--|--|

|                                                                                 | Maximum Input Clock Toggle Rate on Cyclone II Devices (MHz) |                      |                      |                      |                      |                      |                           |                      |                      |  |  |

| I/O Standard                                                                    | Colu                                                        | ımn I/O              | Pins                 | Ro                   | w I/O Pi             | ns                   | Dedicated Clock<br>Inputs |                      |                      |  |  |

| , o otamana                                                                     | -6<br>Speed<br>Grade                                        | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade      | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade |  |  |

| DIFFERENTIAL_SSTL_18_<br>CLASS_I                                                | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |

| DIFFERENTIAL_SSTL_18_<br>CLASS_II                                               | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |

| 1.8V_DIFFERENTIAL_HSTL_<br>CLASS_I                                              | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |

| 1.8V_DIFFERENTIAL_HSTL_<br>CLASS_II                                             | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |

| 1.5V_DIFFERENTIAL_HSTL_<br>CLASS_I                                              | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |

| 1.5V_DIFFERENTIAL_HSTL_<br>CLASS_II                                             | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |

| LVPECL                                                                          | _                                                           | _                    | _                    | _                    | _                    | _                    | 402                       | 402                  | 402                  |  |  |

| LVDS                                                                            | 402                                                         | 402                  | 402                  | 402                  | 402                  | 402                  | 402                       | 402                  | 402                  |  |  |

| 1.2V_HSTL                                                                       | 110                                                         | 90                   | 80                   | _                    | _                    | _                    | 110                       | 90                   | 80                   |  |  |

| 1.2V_DIFFERENTIAL_HSTL                                                          | 110                                                         | 90                   | 80                   | _                    | _                    | _                    | 110                       | 90                   | 80                   |  |  |

| Table 5–45. Maximum Output Clock Toggle Rate on Cyclone II Devices (Part 1 of 4) |          |                      |                                                              |                      |                      |                      |                      |                            |                      |                      |  |

|----------------------------------------------------------------------------------|----------|----------------------|--------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------------|----------------------|----------------------|--|

|                                                                                  |          | Max                  | Maximum Output Clock Toggle Rate on Cyclone II Devices (MHz) |                      |                      |                      |                      |                            |                      |                      |  |

| I/O Standard                                                                     | Drive    | Colum                | ın I/O Pi                                                    | ns (1)               | Row                  | / I/O Pins           | s (1)                | Dedicated Clock<br>Outputs |                      |                      |  |

| ·                                                                                | Strength | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade                                         | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade       | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade |  |

| LVTTL                                                                            | 4 mA     | 120                  | 100                                                          | 80                   | 120                  | 100                  | 80                   | 120                        | 100                  | 80                   |  |

|                                                                                  | 8 mA     | 200                  | 170                                                          | 140                  | 200                  | 170                  | 140                  | 200                        | 170                  | 140                  |  |

|                                                                                  | 12 mA    | 280                  | 230                                                          | 190                  | 280                  | 230                  | 190                  | 280                        | 230                  | 190                  |  |

|                                                                                  | 16 mA    | 290                  | 240                                                          | 200                  | 290                  | 240                  | 200                  | 290                        | 240                  | 200                  |  |

|                                                                                  | 20 mA    | 330                  | 280                                                          | 230                  | 330                  | 280                  | 230                  | 330                        | 280                  | 230                  |  |

|                                                                                  | 24 mA    | 360                  | 300                                                          | 250                  | 360                  | 300                  | 250                  | 360                        | 300                  | 250                  |  |

| Table 5–45. Maximum Output Clock Toggle Rate on Cyclone II Devices (Part 3 of 4)  Maximum Output Clock Toggle Rate on Cyclone II Devices (MHz) |          |                      |                      |                      |                         |                      |                      |                      |                      |                      |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|----------------------|----------------------|-------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| I/O Standard                                                                                                                                   | Drive    |                      | ımum U<br>ın I/O Pi  | l                    | Dedicated Clock Outputs |                      |                      |                      |                      |                      |

| ,                                                                                                                                              | Strength | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | -6<br>Speed<br>Grade    | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade |

| SSTL_18_ CLASS_II                                                                                                                              | 16 mA    | 260                  | 220                  | 180                  | _                       | _                    | _                    | _                    | _                    | _                    |

|                                                                                                                                                | 18 mA    | 270                  | 220                  | 180                  | _                       | _                    | _                    | _                    | _                    | _                    |

| 1.8V_HSTL_ CLASS_I                                                                                                                             | 8 mA     | 260                  | 220                  | 180                  | 260                     | 220                  | 180                  | 260                  | 220                  | 180                  |

|                                                                                                                                                | 10 mA    | 300                  | 250                  | 210                  | 300                     | 250                  | 210                  | 300                  | 250                  | 210                  |

|                                                                                                                                                | 12 mA    | 320                  | 270                  | 220                  | 320                     | 270                  | 220                  | 320                  | 270                  | 220                  |

| 1.8V_HSTL_ CLASS_II                                                                                                                            | 16 mA    | 230                  | 190                  | 160                  | _                       | _                    | _                    | _                    | _                    | _                    |

|                                                                                                                                                | 18 mA    | 240                  | 200                  | 160                  | _                       | _                    | _                    | _                    | _                    | _                    |

|                                                                                                                                                | 20 mA    | 250                  | 210                  | 170                  | _                       | _                    | _                    | _                    | _                    | _                    |

| 1.5V_HSTL_ CLASS_I                                                                                                                             | 8 mA     | 210                  | 170                  | 140                  | 210                     | 170                  | 140                  | 210                  | 170                  | 140                  |

|                                                                                                                                                | 10 mA    | 220                  | 180                  | 150                  | _                       | _                    | _                    | _                    | _                    | _                    |

|                                                                                                                                                | 12 mA    | 230                  | 190                  | 160                  | _                       | _                    | _                    | _                    | _                    | _                    |

| 1.5V_HSTL_ CLASS_II                                                                                                                            | 16 mA    | 210                  | 170                  | 140                  | _                       | _                    | _                    | _                    | _                    | _                    |

| DIFFERENTIAL_                                                                                                                                  | 8 mA     | 400                  | 340                  | 280                  | 400                     | 340                  | 280                  | 400                  | 340                  | 280                  |

| SSTL_2_CLASS_I                                                                                                                                 | 12 mA    | 400                  | 340                  | 280                  | 400                     | 340                  | 280                  | 400                  | 340                  | 280                  |

| DIFFERENTIAL_                                                                                                                                  | 16 mA    | 350                  | 290                  | 240                  | 350                     | 290                  | 240                  | 350                  | 290                  | 240                  |

| SSTL_2_CLASS_II                                                                                                                                | 20 mA    | 400                  | 340                  | 280                  | _                       | _                    | _                    | _                    | _                    | _                    |

|                                                                                                                                                | 24 mA    | 400                  | 340                  | 280                  | _                       | _                    | _                    | _                    | _                    | _                    |

| DIFFERENTIAL_                                                                                                                                  | 6 mA     | 260                  | 220                  | 180                  | 260                     | 220                  | 180                  | 260                  | 220                  | 180                  |

| SSTL_18_CLASS_I                                                                                                                                | 8 mA     | 260                  | 220                  | 180                  | 260                     | 220                  | 180                  | 260                  | 220                  | 180                  |

|                                                                                                                                                | 10 mA    | 270                  | 220                  | 180                  | 270                     | 220                  | 180                  | 270                  | 220                  | 180                  |

|                                                                                                                                                | 12 mA    | 280                  | 230                  | 190                  | _                       | _                    | _                    | _                    | _                    | _                    |

| DIFFERENTIAL_SSTL                                                                                                                              | 16 mA    | 260                  | 220                  | 180                  | _                       | _                    | _                    | _                    | _                    | _                    |

| _18_CLASS_II                                                                                                                                   | 18 mA    | 270                  | 220                  | 180                  | _                       | _                    | _                    | _                    | _                    | _                    |

| 1.8V_                                                                                                                                          | 8 mA     | 260                  | 220                  | 180                  | 260                     | 220                  | 180                  | 260                  | 220                  | 180                  |

| DIFFERENTIAL_HSTL                                                                                                                              | 10 mA    | 300                  | 250                  | 210                  | 300                     | 250                  | 210                  | 300                  | 250                  | 210                  |

| _CLASS_I                                                                                                                                       | 12 mA    | 320                  | 270                  | 220                  | 320                     | 270                  | 220                  | 320                  | 270                  | 220                  |

| 1.8V_                                                                                                                                          | 16 mA    | 230                  | 190                  | 160                  | _                       | _                    | _                    | _                    | _                    | _                    |

| DIFFERENTIAL_HSTL                                                                                                                              | 18 mA    | 240                  | 200                  | 160                  | _                       | _                    | _                    | _                    | _                    | _                    |

| _CLASS_II                                                                                                                                      | 20 mA    | 250                  | 210                  | 170                  | _                       | _                    | _                    | _                    | _                    | _                    |

Table 7–8 shows the clock sources connectivity to the global clock networks.

| Table 7–8. Global Cl          | ock N                  | etwoi    | k Con    | necti    | ons (    | Part :   | 1 of 3   | )        |          |          |          |          |          |          |          |          |

|-------------------------------|------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Global Clock                  | Global Clock Networks  |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |

| Global Clock<br>Network Clock | All Cyclone II Devices |          |          |          |          |          |          |          | EP       | 2C15     | throu    | gh EP    | 2C70     | Devi     | ces O    | nly      |

| Sources                       | 0                      | 1        | 2        | 3        | 4        | 5        | 6        | 7        | 8        | 9        | 10       | 11       | 12       | 13       | 14       | 15       |

| CLK0/LVDSCLK0p                | <b>✓</b>               |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK1/LVDSCLK0n                |                        | <b>✓</b> | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK2/LVDSCLK1p                | <b>✓</b>               |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK3/LVDSCLK1n                |                        | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK4/LVDSCLK2p                |                        |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| CLK5/LVDSCLK2n                |                        |          |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| CLK6/LVDSCLK3p                |                        |          |          |          | <b>✓</b> |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| CLK7/LVDSCLK3n                |                        |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| CLK8/LVDSCLK4n                |                        |          |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |

| CLK9/LVDSCLK4p                |                        |          |          |          |          |          |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          |          |          |

| CLK10/LVDSCLK5n               |                        |          |          |          |          |          |          |          | <b>✓</b> |          |          | <b>✓</b> |          |          |          |          |

| CLK11/LVDSCLK5p               |                        |          |          |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |          |          |

| CLK12/LVDSCLK6n               |                        |          |          |          |          |          |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          |

| CLK13/LVDSCLK6p               |                        |          |          |          |          |          |          |          |          |          |          |          |          | <b>✓</b> | <b>✓</b> |          |

| CLK14/LVDSCLK7n               |                        |          |          |          |          |          |          |          |          |          |          |          | <b>✓</b> |          |          | <b>~</b> |

| CLK15/LVDSCLK7p               |                        |          |          |          |          |          |          |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |

| PLL1_c0                       | <b>✓</b>               | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |

| PLL1_c1                       | <b>✓</b>               |          | <b>✓</b> | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |

| PLL1_c2                       |                        | <b>✓</b> | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |          |

| PLL2_c0                       |                        |          |          |          | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| PLL2_c1                       |                        |          |          |          | <b>✓</b> |          | <b>✓</b> | <b>✓</b> |          |          |          |          |          |          |          |          |

| PLL2_c2                       |                        |          |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| PLL3_c0                       |                        |          |          |          |          |          |          |          | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |          |          |          |          |

| PLL3_c1                       |                        |          |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> | <b>✓</b> |          |          |          |          |

| PLL3_c2                       |                        |          |          |          |          |          |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          |          |          |

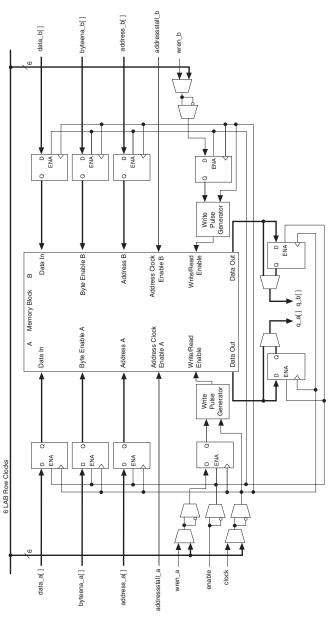

## 8. Cyclone II Memory Blocks

CII51008-2.4

## Introduction

Cyclone® II devices feature embedded memory structures to address the on-chip memory needs of FPGA designs. The embedded memory structure consists of columns of M4K memory blocks that can be configured to provide various memory functions such as RAM, first-in first-out (FIFO) buffers, and ROM. M4K memory blocks provide over 1 Mbit of RAM at up to 250-MHz operation (see Table 8–2 on page 8–2 for total RAM bits per density).

## **Overview**

The M4K blocks support the following features:

- Over 1 Mbit of RAM available without reducing available logic

- 4,096 memory bits per block (4,608 bits per block including parity)

- Variable port configurations

- True dual-port (one read and one write, two reads, or two writes) operation

- Byte enables for data input masking during writes

- Initialization file to pre-load content of memory in RAM and ROM modes

- Up to 250-MHz operation

Table 8–1 summarizes the features supported by the M4K memory.

| Table 8–1. Summary of M4K Memory Features (Part 1 of 2) |                                                                                                                                         |  |  |  |  |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Feature                                                 | M4K Blocks                                                                                                                              |  |  |  |  |

| Maximum performance (1)                                 | 250 MHz                                                                                                                                 |  |  |  |  |

| Total RAM bits (including parity bits)                  | 4,608                                                                                                                                   |  |  |  |  |

| Configurations                                          | $4K \times 1$ $2K \times 2$ $1K \times 4$ $512 \times 8$ $512 \times 9$ $256 \times 16$ $256 \times 18$ $128 \times 32$ $128 \times 36$ |  |  |  |  |

| Parity bits                                             | ✓                                                                                                                                       |  |  |  |  |

| Byte enable                                             | ✓                                                                                                                                       |  |  |  |  |

Figure 8–18. Cyclone II Single-Clock Mode in True Dual-Port Mode Note (1)

*Note to Figure 8–18*:

(1) Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

## Read-During-Write Operation at the Same Address

The "Same-Port Read-During-Write Mode" and "Mixed-Port Read-During-Write Mode" sections describe the functionality of the various RAM configurations when reading from an address during a write operation at that same address. There are two read-during-write data flows: same-port and mixed-port. Figure 8–21 shows the difference between these flows.

Port A data in

Mixed-port data flow

---- Same-port data flow

Port A data out

Figure 8-21. Cyclone II Read-During-Write Data Flow

## Same-Port Read-During-Write Mode

For read-during-write operation of a single-port RAM or the same port of a true dual-port RAM, the new data is available on the rising edge of the same clock cycle on which it was written. Figure 8–22 shows a sample functional waveform. When using byte enables in true dual-port RAM mode, the outputs for the masked bytes on the same port are unknown (see Figure 8–2 on page 8–6). The non-masked bytes are read out as shown in Figure 8–22.

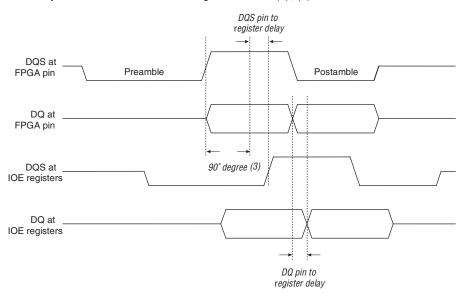

Figure 9–1. Example of a 90° Shift on the DQS Signal Notes (1), (2)

#### *Notes to Figure 9–1:*

- (1) RLDRAM II and QDRII SRAM memory interfaces do not have preamble and postamble specifications.

- (2) DDR2 SDRAM does not support a burst length of two.

- (3) The phase shift required for your system should be based on your timing analysis and may not be 90°.

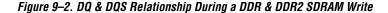

During write operations to a DDR or DDR2 SDRAM device, the FPGA must send the data strobe to the memory device center-aligned relative to the data. Cyclone II devices use a PLL to center-align the data strobe by generating a  $0^{\circ}$  phase-shifted system clock for the write data strobes and a  $-90^{\circ}$  phase-shifted write clock for the write data pins for the DDR and DDR2 SDRAM. Figure 9-2 shows an example of the relationship between the data and data strobe during a burst-of-two write.

After applying the equation above, apply one of the equations in Table 10–11, depending on the package type.

| Table 10–11. Bidirectional Pad Limitation Formulas (Multiple $V_{REF}$ Inputs and Outputs) |                                                                                              |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Package Type Formula                                                                       |                                                                                              |  |  |  |  |  |  |

| FineLine BGA                                                                               | (Total number of bidirectional pads) + (Total number of output pads) ≤9 (per VCCIO/GND pair) |  |  |  |  |  |  |

| QFP                                                                                        | Total number of bidirectional pads + Total number of output pads ≤5 (per VCCIO/GND pair)     |  |  |  |  |  |  |

Each I/O bank can only be set to a single  $V_{CCIO}$  voltage level and a single  $V_{REF}$  voltage level at a given time. Pins of different I/O standards can share the bank if they have compatible  $V_{CCIO}$  values (refer to Table 10–4 for more details) and compatible  $V_{REF}$  voltage levels.

#### DDR and QDR Pads

For dedicated DQ and DQS pads on a DDR interface, DQ pads have to be on the same power bank as DQS pads. With the DDR and DDR2 memory interfaces, a VCCIO and ground pair can have a maximum of five DQ pads.

For a QDR interface, D is the QDR output and Q is the QDR input. D pads and Q pads have to be on the same power bank as CQ. With the QDR and QDRII memory interfaces, a VCCIO and ground pair can have a maximum of five D and Q pads.

By default, the Quartus II software assigns D and Q pads as regular I/O pins. If you do not specify the function of a D or Q pad in the Quartus II software, the software sets them as regular I/O pins. If this occurs, Cyclone II QDR and QDRII performance is not guaranteed.

#### **DC** Guidelines

There is a current limit of 240 mA per eight consecutive output top and bottom pins per power pair, as shown by the following equation:

```

pin+7 \Sigma I_{\rm PIN} < 240mA per power pair pin

```

There is a current limit of 240 mA per 12 consecutive output side (left and right) pins per power pair, as shown by the following equation:

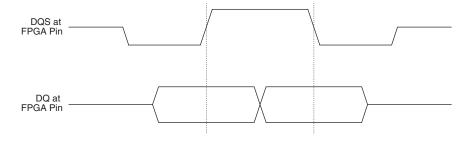

Figure 11-12. Differential SSTL Class I Interface

Figure 11–13. Differential SSTL Class II Interface

## **Differential HSTL Support in Cyclone II Devices**

The differential HSTL AC and DC specifications are the same as the HSTL single-ended specifications. The differential HSTL I/O standard is available on the GCLK pins only, treating differential inputs as two single-ended HSTL, and only decoding one of them. The differential HSTL output I/O standard is only supported at the PLLCLKOUT pins using two single-ended HSTL output buffers with the second output programmed as inverted. The standard requires two differential inputs with an external termination voltage ( $V_{\rm TT}$ ) of  $0.5 \times V_{\rm CCIO}$  to which termination resistors are connected.

For the HSTL signaling characteristics, see the *DC Characteristics & Timing Specifications* chapter and the *Selectable I/O Standards in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

## 12. Embedded Multipliers in Cyclone II Devices

CII51012-1.2

### Introduction

Use Cyclone® II FPGAs alone or as digital signal processing (DSP) co-processors to improve price-to-performance ratios for DSP applications. You can implement high-performance yet low-cost DSP systems with the following Cyclone II device features and design support:

- Up to 150 18 x 18 multipliers

- Up to 1.1 Mbit of on-chip embedded memory

- High-speed interface to external memory

- DSP Intellectual Property (IP) cores

- DSP Builder interface to the Mathworks Simulink and Matlab design environment

- DSP Development Kit, Cyclone II Edition

This chapter focuses on the Cyclone II embedded multiplier blocks.

Cyclone II devices have embedded multiplier blocks optimized for multiplier-intensive low-cost DSP applications. These embedded multipliers combined with the flexibility of programmable logic devices (PLDs), provide you with the ability to efficiently implement various cost sensitive DSP functions easily. Consumer-based application systems such as digital television (DTV) and home entertainment systems typically require a cost effective solution for implementing multipliers to perform signal processing functions like finite impulse response (FIR) filters, fast Fourier transform (FFT) functions, and discrete cosine transform (DCT) functions.

Along with the embedded multipliers, the M4K memory blocks in Cyclone II devices also support various soft multiplier implementations. These, in combination with the embedded multipliers increase the available number of multipliers in Cyclone II devices and provide the user with a wide variety of implementation options and flexibility when designing their systems.

See the Cyclone II Device Family Data Sheet section in Volume 1 of the *Cyclone II Device Handbook* for more information on Cyclone II devices.

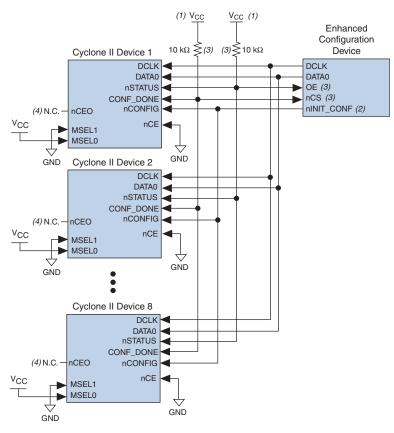

Figure 13–16. Multiple Device PS Configuration Using an Enhanced Configuration Device When FPGAs Receive the Same Data

#### Notes to Figure 13–16:

- The pull-up resistor should be connected to the same supply voltage as the configuration device.

- (2) The ninit\_conf pin is available on enhanced configuration devices and has an internal pull-up resistor that is always active, meaning an external pull-up resistor should not be used on the ninit\_conf to nconfig line. The ninit\_conf pin does not need to be connected if its functionality is not used. If ninit\_conf is not used, nconfig must be pulled to V<sub>CC</sub> either directly or through a resistor (if reconfiguration is required, a resistor is necessary).

- (3) The enhanced configuration devices' OE and nCS pins have internal programmable pull-up resistors. If internal pull-up resistors are used, external pull-up resistors should not be used on these pins. The internal pull-up resistors are used by default in the Quartus II software. To turn off the internal pull-up resistors, check the Disable nCS and OE pull-ups on configuration device option when generating programming files.

- (4) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

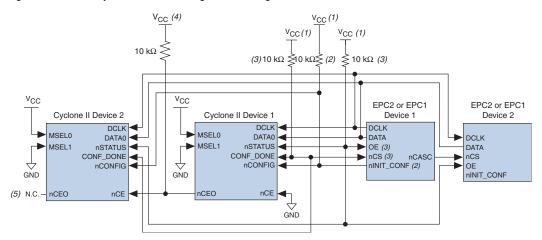

You can cascade several EPC2 or EPC1 devices to configure multiple Cyclone II devices. The first configuration device in the chain is the master configuration device, and the subsequent devices are the slave devices. The master configuration device sends DCLK to the Cyclone II

Figure 13-17. Multiple Device PS Configuration Using Cascaded EPC2 or EPC1 Devices

#### *Notes to Figure 13–17:*

- (1) The pull-up resistor should be connected to the same supply voltage as the configuration device.

- (2) The ninit\_conf pin (available on enhanced configuration devices and EPC2 devices only) has an internal pull-up resistor that is always active, meaning an external pull-up resistor should not be used on the ninit\_conf to nconfig line. The ninit\_conf pin does not need to be connected if its functionality is not used. If ninit\_conf is not used or not available (e.g., on EPC1 devices), nconfig must be pulled to V<sub>CC</sub> either directly or through a resistor (if reconfiguration is required, a resistor is necessary).

- (3) The enhanced configuration devices' and EPC2 devices' OE and nCS pins have internal programmable pull-up resistors. If internal pull-up resistors are used, external pull-up resistors should not be used on these pins. The internal pull-up resistors are used by default in the Quartus II software. To turn off the internal pull-up resistors, check the Disable nCS and OE pull-ups on configuration device option when generating programming files.

- (4) Use an external 10-kΩ pull-up resistor to pull the nCEO pin high to the I/O bank V<sub>CCIO</sub> level to help the internal weak pull-up when it feeds next device's nCE pin.

- (5) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

When using enhanced configuration devices or EPC2 devices, you can connect the Cyclone II device's <code>nCONFIG</code> pin to the configuration device's <code>nINIT\_CONF</code> pin, which allows the <code>INIT\_CONF</code> JTAG instruction to initiate FPGA configuration. You do not need to connect the <code>nINIT\_CONF</code> pin if it is not used. If the <code>nINIT\_CONF</code> pin is not used or not available (for example, on EPC1 devices), pull the <code>nCONFIG</code> pin to  $V_{CC}$  levels either directly or through a resistor (if reconfiguration is required, a resistor is necessary). An internal pull-up resistor on the <code>nINIT\_CONF</code> pin is always active in the enhanced configuration devices and the EPC2 devices. Therefore, do not use an external pull-up resistor if you connect the <code>nCONFIG</code> pin to <code>nINIT\_CONF</code>. If you use multiple EPC2 devices to configure a Cyclone II device(s), only connect the first EPC2 device's <code>nINIT\_CONF</code> pin to the device's <code>nCONFIG</code> pin.

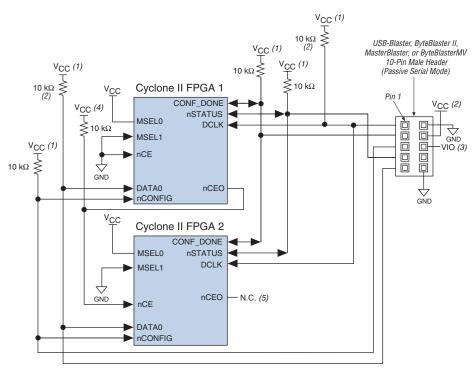

Figure 13–20. Multiple Device PS Configuration Using a USB-Blaster, MasterBlaster, ByteBlaster II or ByteBlasterMV Cable

#### *Notes to Figure 13–20:*

- (1) The pull-up resistor should be connected to the same supply voltage as the USB-Blaster, MasterBlaster (VIO pin), ByteBlaster II, or ByteBlasterMV cable.

- (2) The pull-up resistors on DATAO and DCLK are only needed if the download cable is the only configuration scheme used on your board. This is to ensure that DATAO and DCLK are not left floating after configuration. For example, if you are also using a configuration device, the pull-up resistors on DATAO and DCLK are not needed.

- (3) Pin 6 of the header is a V<sub>IO</sub> reference voltage for the MasterBlaster output driver. V<sub>IO</sub> should match the device's V<sub>CCIO</sub>. Refer to the MasterBlaster Serial/USB Communications Cable Data Sheet for this value. In the ByteBlasterMV, this pin is a no connect. In the USB-Blaster and ByteBlaster II, this pin is connected to nCE when it is used for AS programming, otherwise it is a no connect.

- (4) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of I/O bank that the nCEO pin resides in.

- (5) The nCEO pin of the last device in chain can be left unconnected or used as a user I/O pin.

If you are using a download cable to configure Cyclone II devices on a PCB that also has configuration devices, you should electrically isolate the configuration devices from the target Cyclone II devices and cable. One way to isolate the configuration device is to add logic, such as a multiplexer, that can select between the configuration device and the cable. The multiplexer should allow bidirectional transfers on the nstatus and configuration. Additionally, you can add switches to

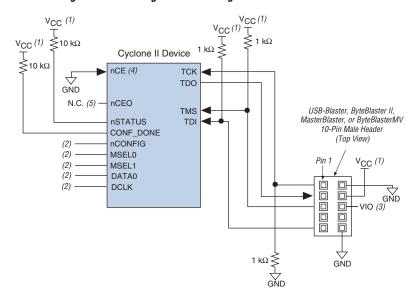

### Single Device JTAG Configuration

During JTAG configuration, you can use the USB-Blaster, MasterBlaster, ByteBlaster II, or ByteBlasterMV download cable to download data to the device. Configuring Cyclone II devices through a cable is similar to programming devices in system. Figure 13–22 shows JTAG configuration of a single Cyclone II device using a download cable.

Figure 13-22. JTAG Configuration of a Single Device Using a Download Cable

#### Notes to Figure 13-22:

- The pull-up resistor should be connected to the same supply voltage as the USB-Blaster, MasterBlaster (VIO pin), ByteBlaster II, or ByteBlasterMV cable.

- (2) Connect the nCONFIG and MSEL[1..0] pins to support a non-JTAG configuration scheme. If only JTAG configuration is used, connect the nCONFIG pin to V<sub>CC</sub>, and the MSEL[1..0] pins to ground. In addition, pull DCLK and DATAO to either high or low, whichever is convenient on your board.

- (3) Pin 6 of the header is a V<sub>IO</sub> reference voltage for the MasterBlaster output driver. V<sub>IO</sub> should match the device's V<sub>CCIO</sub>. Refer to the MasterBlaster Serial/USB Communications Cable Data Sheet for this value. In the ByteBlasterMV, this pin is a no connect. In the USB-Blaster and ByteBlaster II, this pin is connected to nCE when it is used for AS programming, otherwise it is a no connect.

- (4) nce must be connected to GND or driven low for successful JTAG configuration.

- (5) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

To configure a single device in a JTAG chain, the programming software places all other devices in BYPASS mode. In BYPASS mode, Cyclone II devices pass programming data from the TDI pin to the TDO pin through a single bypass register without being affected internally. This scheme

| Table 13–11. Dedicated Configuration Pins on the Cyclone II Device (Part 4 of 5) |                                                          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|----------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin Name                                                                         | User<br>Mode                                             | Configuration<br>Scheme | Pin Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| nCEO                                                                             | N/A if option is on. I/O if option is off.               | All                     | Output   | This pin is an output that drives low when device configuration is complete. In single device configuration, you can leave this pin floating or use it as a user I/O pin after configuration. In multiple device configuration, this pin inputs the next device's $n\text{CE}$ pin. The $n\text{CEO}$ of the last device in the chain can be left floating or used as a user I/O pin after configuration. If you use the $n\text{CEO}$ pin to feed next device's $n\text{CE}$ pin, use an external 10-k $\Omega$ pull-up resistor to pull the $n\text{CEO}$ pin high to the $V_{\text{CCIO}}$ voltage of its I/O bank to help the internal weak pull-up resistor. |  |  |  |  |  |  |

|                                                                                  |                                                          |                         |          | Use the Quartus II software to make this pin a user I/O pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| ASDO                                                                             | N/A in<br>AS<br>mode<br>I/O in<br>PS and<br>JTAG<br>mode | AS                      | Output   | This pin sends a control signal from the Cyclone II device to the serial configuration device in AS mode and is used to read out configuration data.  In AS mode, ASDO has an internal pull-up that is always active.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| nCSO                                                                             | N/A in<br>AS<br>mode<br>I/O in<br>PS and<br>JTAG<br>mode | AS                      | Output   | This pin sends an output control signal from the Cyclone II device to the serial configuration device in AS mode that enables the configuration device.  In AS mode, nCSO has an internal pull-up resistor that is always active.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |