Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 3158                                                    |

| Number of Logic Elements/Cells | 50528                                                   |

| Total RAM Bits                 | 594432                                                  |

| Number of I/O                  | 294                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

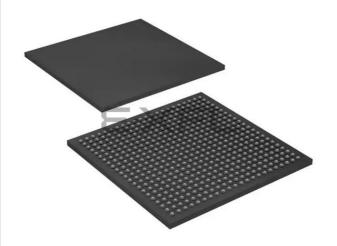

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 484-BGA                                                 |

| Supplier Device Package        | 484-FBGA (23x23)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c50f484c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- protocols. Visit the Altera IPMegaStore at www.altera.com to download IP MegaCore functions.

- Nios II Embedded Processor support

The Cyclone II family offers devices with the Fast-On feature, which offers a faster power-on-reset (POR) time. Devices that support the Fast-On feature are designated with an "A" in the device ordering code. For example, EP2C5A, EP2C8A, EP2C15A, and EP2C20A. The EP2C5A is only available in the automotive speed grade. The EP2C8A and EP2C20A are only available in the industrial speed grade. The EP2C15A is only available with the Fast-On feature and is available in both commercial and industrial grades. The Cyclone II "A" devices are identical in feature set and functionality to the non-A devices except for support of the faster POR time.

Cyclone II A devices are offered in automotive speed grade. For more information, refer to the Cyclone II section in the *Automotive-Grade Device Handbook*.

For more information on POR time specifications for Cyclone II A and non-A devices, refer to the *Hot Socketing & Power-On Reset* chapter in the *Cyclone II Device Handbook*.

Table 1–1 lists the Cyclone II device family features. Table 1–2 lists the Cyclone II device package offerings and maximum user I/O pins.

| Table 1–1. Cyclone II FPGA Family Features (Part 1 of 2) |                  |           |            |            |         |         |               |  |  |  |  |

|----------------------------------------------------------|------------------|-----------|------------|------------|---------|---------|---------------|--|--|--|--|

| Feature                                                  | <b>EP2C5</b> (2) | EP2C8 (2) | EP2C15 (1) | EP2C20 (2) | EP2C35  | EP2C50  | EP2C70        |  |  |  |  |

| LEs                                                      | 4,608            | 8,256     | 14,448     | 18,752     | 33,216  | 50,528  | 68,416        |  |  |  |  |

| M4K RAM blocks (4<br>Kbits plus<br>512 parity bits       | 26               | 36        | 52         | 52         | 105     | 129     | 250           |  |  |  |  |

| Total RAM bits                                           | 119,808          | 165,888   | 239,616    | 239,616    | 483,840 | 594,432 | 1,152,00<br>0 |  |  |  |  |

| Embedded multipliers (3)                                 | 13               | 18        | 26         | 26         | 35      | 86      | 150           |  |  |  |  |

| PLLs                                                     | 2                | 2         | 4          | 4          | 4       | 4       | 4             |  |  |  |  |

| Table 1–2. Cyclo | Table 1–2. Cyclone II Package Options & Maximum User I/O Pins         Notes (1) (2) |                     |                 |                            |                            |                                     |                            |                            |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------|---------------------|-----------------|----------------------------|----------------------------|-------------------------------------|----------------------------|----------------------------|--|--|--|--|

| Device           | 144-Pin<br>TQFP (3)                                                                 | 208-Pin<br>PQFP (4) | 240-Pin<br>PQFP | 256-Pin<br>FineLine<br>BGA | 484-Pin<br>FineLine<br>BGA | 484-Pin<br>Ultra<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 896-Pin<br>FineLine<br>BGA |  |  |  |  |

| EP2C5 (6) (8)    | 89                                                                                  | 142                 | _               | 158 <i>(5)</i>             | _                          | _                                   | _                          | _                          |  |  |  |  |

| EP2C8 (6)        | 85                                                                                  | 138                 | _               | 182                        | _                          | _                                   | _                          | _                          |  |  |  |  |

| EP2C8A (6), (7)  | _                                                                                   | _                   | _               | 182                        | _                          | _                                   | _                          | _                          |  |  |  |  |

| EP2C15A (6), (7) | _                                                                                   | _                   | _               | 152                        | 315                        | _                                   | _                          | _                          |  |  |  |  |

| EP2C20 (6)       | _                                                                                   | _                   | 142             | 152                        | 315                        | _                                   | _                          | _                          |  |  |  |  |

| EP2C20A (6), (7) | _                                                                                   | _                   | _               | 152                        | 315                        | _                                   | _                          | _                          |  |  |  |  |

| EP2C35 (6)       | _                                                                                   | _                   | _               | _                          | 322                        | 322                                 | 475                        | _                          |  |  |  |  |

| EP2C50 (6)       | _                                                                                   | _                   | _               | _                          | 294                        | 294                                 | 450                        | _                          |  |  |  |  |

| EP2C70 (6)       | _                                                                                   | _                   | _               |                            | _                          | _                                   | 422                        | 622                        |  |  |  |  |

#### Notes to Table 1-2:

- Cyclone II devices support vertical migration within the same package (for example, you can migrate between the EP2C20 device in the 484-pin FineLine BGA package and the EP2C35 and EP2C50 devices in the same package).

- (2) The Quartus® II software I/O pin counts include four additional pins, TDI, TDO, TMS, and TCK, which are not available as general purpose I/O pins.

- (3) TQFP: thin quad flat pack.

- (4) PQFP: plastic quad flat pack.

- (5) Vertical migration is supported between the EP2C5F256 and the EP2C8F256 devices. However, not all of the DQ and DQS groups are supported. Vertical migration between the EP2C5 and the EP2C15 in the F256 package is not supported.

- (6) The I/O pin counts for the EP2C5, EP2C8, and EP2C15A devices include 8 dedicated clock pins that can be used for data inputs. The I/O counts for the EP2C20, EP2C35, EP2C50, and EP2C70 devices include 16 dedicated clock pins that can be used for data inputs.

- (7) EP2C8A, EP2C15A, and EP2C20A have a Fast On feature that has a faster POR time. The EP2C15A is only available with the Fast On option.

- (8) The EP2C5 optionally support the Fast On feature, which is designated with an "A" in the device ordering code. The EP2C5A is only available in the automotive speed grade. Refer to the Cyclone II section in the *Automotive-Grade Device Handbook*.

Cyclone II devices support vertical migration within the same package (for example, you can migrate between the EP2C35, EPC50, and EP2C70 devices in the 672-pin FineLine BGA package). The exception to vertical migration support within the Cyclone II family is noted in Table 1–3.

Cyclone II devices are available in up to three speed grades: –6, –7, and –8, with –6 being the fastest. Table 1–4 shows the Cyclone II device speed-grade offerings.

| Table 1–4. Cy | Table 1–4. Cyclone II Device Speed Grades |                 |                 |                            |                            |                                     |                            |                            |  |  |  |

|---------------|-------------------------------------------|-----------------|-----------------|----------------------------|----------------------------|-------------------------------------|----------------------------|----------------------------|--|--|--|

| Device        | 144-Pin<br>TQFP                           | 208-Pin<br>PQFP | 240-Pin<br>PQFP | 256-Pin<br>FineLine<br>BGA | 484-Pin<br>FineLine<br>BGA | 484-Pin<br>Ultra<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 896-Pin<br>FineLine<br>BGA |  |  |  |

| EP2C5 (1)     | -6, -7, -8                                | -7, -8          | _               | -6, -7, -8                 | _                          | _                                   | _                          | _                          |  |  |  |

| EP2C8         | -6, -7, -8                                | -7, -8          | _               | -6, -7, -8                 | _                          | _                                   | _                          | _                          |  |  |  |

| EP2C8A (2)    | _                                         | _               | _               | -8                         | _                          | _                                   | _                          | _                          |  |  |  |

| EP2C15A       | _                                         | _               | _               | -6, -7, -8                 | -6, -7, -8                 | _                                   | _                          | _                          |  |  |  |

| EP2C20        | _                                         | _               | -8              | -6, -7, -8                 | -6, -7, -8                 | _                                   | _                          | _                          |  |  |  |

| EP2C20A (2)   | _                                         | _               | _               | -8                         | -8                         | _                                   | _                          | _                          |  |  |  |

| EP2C35        | _                                         | _               | _               | _                          | -6, -7, -8                 | -6, -7, -8                          | -6, -7, -8                 | _                          |  |  |  |

| EP2C50        | _                                         | _               | _               | _                          | -6, -7, -8                 | -6, -7, -8                          | -6, -7, -8                 | _                          |  |  |  |

| EP2C70        | _                                         | _               | _               | _                          | _                          | _                                   | -6, -7, -8                 | -6, -7, -8                 |  |  |  |

### Notes to Table 1-4:

<sup>(1)</sup> The EP2C5 optionally support the Fast On feature, which is designated with an "A" in the device ordering code. The EP2C5A is only available in the automotive speed grade. Refer to the Cyclone II section in the *Automotive-Grade Device Handbook* for detailed information.

<sup>(2)</sup> EP2C8A and EP2C20A are only available in industrial grade.

# 2. Cyclone II Architecture

CII51002-3.1

# Functional Description

Cyclone<sup>®</sup> II devices contain a two-dimensional row- and column-based architecture to implement custom logic. Column and row interconnects of varying speeds provide signal interconnects between logic array blocks (LABs), embedded memory blocks, and embedded multipliers.

The logic array consists of LABs, with 16 logic elements (LEs) in each LAB. An LE is a small unit of logic providing efficient implementation of user logic functions. LABs are grouped into rows and columns across the device. Cyclone II devices range in density from 4,608 to 68,416 LEs.

Cyclone II devices provide a global clock network and up to four phase-locked loops (PLLs). The global clock network consists of up to 16 global clock lines that drive throughout the entire device. The global clock network can provide clocks for all resources within the device, such as input/output elements (IOEs), LEs, embedded multipliers, and embedded memory blocks. The global clock lines can also be used for other high fan-out signals. Cyclone II PLLs provide general-purpose clocking with clock synthesis and phase shifting as well as external outputs for high-speed differential I/O support.

M4K memory blocks are true dual-port memory blocks with 4K bits of memory plus parity (4,608 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 36-bits wide at up to 260 MHz. These blocks are arranged in columns across the device in between certain LABs. Cyclone II devices offer between 119 to 1,152 Kbits of embedded memory.

Each embedded multiplier block can implement up to either two 9  $\times$  9-bit multipliers, or one 18  $\times$  18-bit multiplier with up to 250-MHz performance. Embedded multipliers are arranged in columns across the device.

Each Cyclone II device I/O pin is fed by an IOE located at the ends of LAB rows and columns around the periphery of the device. I/O pins support various single-ended and differential I/O standards, such as the 66- and 33-MHz, 64- and 32-bit PCI standard, PCI-X, and the LVDS I/O standard at a maximum data rate of 805 megabits per second (Mbps) for inputs and 640 Mbps for outputs. Each IOE contains a bidirectional I/O buffer and three registers for registering input, output, and output-enable signals. Dual-purpose DQS, DQ, and DM pins along with delay chains (used to

A LAB-wide asynchronous load signal to control the logic for the register's preset signal is not available. The register preset is achieved by using a NOT gate push-back technique. Cyclone II devices can only support either a preset or asynchronous clear signal.

In addition to the clear port, Cyclone II devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals.

# MultiTrack Interconnect

In the Cyclone II architecture, connections between LEs, M4K memory blocks, embedded multipliers, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive™ technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement within the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

The MultiTrack interconnect consists of row (direct link, R4, and R24) and column (register chain, C4, and C16) interconnects that span fixed distances. A routing structure with fixed-length resources for all devices allows predictable and repeatable performance when migrating through different device densities.

#### Row Interconnects

Dedicated row interconnects route signals to and from LABs, PLLs, M4K memory blocks, and embedded multipliers within the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks

- R4 interconnects traversing four blocks to the right or left

- R24 interconnects for high-speed access across the length of the device

Each M4K block can implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and first-in first-out (FIFO) buffers. The M4K blocks support the following features:

- 4,608 RAM bits

- 250-MHz performance

- True dual-port memory

- Simple dual-port memory

- Single-port memory

- Byte enable

- Parity bits

- Shift register

- FIFO buffer

- ROM

- Various clock modes

- Address clock enable

Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

Table 2–5 shows the capacity and distribution of the M4K memory blocks in each Cyclone II device.

| Table 2–5. M4K Memory Capacity & Distribution in Cyclone II Devices |                |     |           |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|----------------|-----|-----------|--|--|--|--|--|--|--|

| Device                                                              | Total RAM Bits |     |           |  |  |  |  |  |  |  |

| EP2C5                                                               | 2              | 26  | 119,808   |  |  |  |  |  |  |  |

| EP2C8                                                               | 2              | 36  | 165,888   |  |  |  |  |  |  |  |

| EP2C15                                                              | 2              | 52  | 239,616   |  |  |  |  |  |  |  |

| EP2C20                                                              | 2              | 52  | 239,616   |  |  |  |  |  |  |  |

| EP2C35                                                              | 3              | 105 | 483,840   |  |  |  |  |  |  |  |

| EP2C50                                                              | 3              | 129 | 594,432   |  |  |  |  |  |  |  |

| EP2C70                                                              | 5              | 250 | 1,152,000 |  |  |  |  |  |  |  |

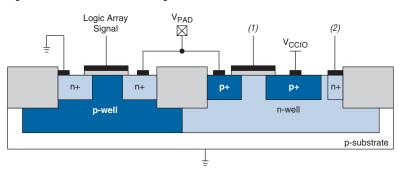

Figure 4–2. Transistor Level Diagram of FPGA Device I/O Buffers

*Notes to Figure 4–2:*

- (1) This is the logic array signal or the larger of either the  $V_{CCIO}$  or  $V_{PAD}$  signal.

- (2) This is the larger of either the  $V_{CCIO}$  or  $V_{PAD}$  signal.

# Power-On Reset Circuitry

Cyclone II devices contain POR circuitry to keep the device in a reset state until the power supply voltage levels have stabilized during power-up. The POR circuit monitors the  $V_{\rm CCINT}$  voltage levels and tri-states all user I/O pins until the  $V_{\rm CC}$  reaches the recommended operating levels. In addition, the POR circuitry also monitors the  $V_{\rm CCIO}$  level of the two I/O banks that contains configuration pins (I/O banks 1 and 3 for EP2C5 and EP2C8, I/O banks 2 and 6 for EP2C15A, EP2C20, EP2C35, EP2C50, and EP2C70) and tri-states all user I/O pins until the  $V_{\rm CC}$  reaches the recommended operating levels.

After the Cyclone II device enters user mode, the POR circuit continues to monitor the  $V_{CCINT}$  voltage level so that a brown-out condition during user mode can be detected. If the  $V_{CCINT}$  voltage sags below the POR trip point during user mode, the POR circuit resets the device. If the  $V_{CCIO}$  voltage sags during user mode, the POR circuit does not reset the device.

# "Wake-up" Time for Cyclone II Devices

In some applications, it may be necessary for a device to wake up very quickly in order to begin operation. The Cyclone II device family offers the Fast-On feature to support fast wake-up time applications. Devices that support the Fast-On feature are designated with an "A" in the ordering code and have stricter power up requirements compared to non-A devices.

| Table 5–18. DSP Bloc | Table 5–18. DSP Block Internal Timing Microparameters (Part 2 of 2) |           |          |           |          |      |      |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------|-----------|----------|-----------|----------|------|------|--|--|--|--|--|

| Davamatav            | -6 Speed                                                            | Grade (1) | -7 Speed | Grade (2) | -8 Speed | IIiA |      |  |  |  |  |  |

| Parameter            | Min                                                                 | Max       | Min      | Max       | Min      | Max  | Unit |  |  |  |  |  |

| TPIPE2OUTREG         | 47                                                                  | 104       | 45       | 142       | 45       | 185  | ps   |  |  |  |  |  |

|                      | _                                                                   | _         | 47       | _         | 47       | _    | ps   |  |  |  |  |  |

| TPD9                 | 529                                                                 | 2470      | 505      | 3353      | 505      | 4370 | ps   |  |  |  |  |  |

|                      | _                                                                   | _         | 529      | _         | 529      | _    | ps   |  |  |  |  |  |

| TPD18                | 425                                                                 | 2903      | 406      | 3941      | 406      | 5136 | ps   |  |  |  |  |  |

|                      | _                                                                   | _         | 425      | _         | 425      | _    | ps   |  |  |  |  |  |

| TCLR                 | 2686                                                                | _         | 3572     | _         | 3572     | _    | ps   |  |  |  |  |  |

|                      | _                                                                   | _         | 3129     | _         | 3572     | _    | ps   |  |  |  |  |  |

| TCLKL                | 1923                                                                | _         | 2769     | _         | 2769     | _    | ps   |  |  |  |  |  |

|                      | _                                                                   | _         | 2307     | _         | 2769     | _    | ps   |  |  |  |  |  |

| TCLKH                | 1923                                                                | _         | 2769     | _         | 2769     | _    | ps   |  |  |  |  |  |

|                      | _                                                                   | _         | 2307     | _         | 2769     | _    | ps   |  |  |  |  |  |

#### Notes to Table 5-18:

- (1) For the –6 speed grades, the minimum timing is for the commercial temperature grade. The –7 speed grade devices offer the automotive temperature grade. The –8 speed grade devices offer the industrial temperature grade.

- (2) For each parameter of the –7 speed grade columns, the value in the first row represents the minimum timing parameter for automotive devices. The second row represents the minimum timing parameter for commercial devices.

- (3) For each parameter of the –8 speed grade columns, the value in the first row represents the minimum timing parameter for industrial devices. The second row represents the minimum timing parameter for commercial devices.

| Table 5–19. M4K Block Internal Timing Microparameters (Part 1 of 3) |          |           |          |           |          |      |      |  |  |  |

|---------------------------------------------------------------------|----------|-----------|----------|-----------|----------|------|------|--|--|--|

| Parameter                                                           | -6 Speed | Grade (1) | -7 Speed | Grade (2) | -8 Speed | Unit |      |  |  |  |

| Parameter                                                           | Min      | Max       | Min      | Max       | Min      | Max  | Unit |  |  |  |

| TM4KRC                                                              | 2387     | 3764      | 2275     | 4248      | 2275     | 4736 | ps   |  |  |  |

|                                                                     | _        | _         | 2387     | _         | 2387     | _    | ps   |  |  |  |

| TM4KWERESU                                                          | 35       | _         | 46       | _         | 46       | _    | ps   |  |  |  |

|                                                                     | _        | _         | 40       | _         | 46       | _    | ps   |  |  |  |

| TM4KWEREH                                                           | 234      | _         | 267      | _         | 267      | _    | ps   |  |  |  |

|                                                                     | _        | _         | 250      | _         | 267      | _    | ps   |  |  |  |

| TM4KBESU                                                            | 35       | _         | 46       | _         | 46       | _    | ps   |  |  |  |

|                                                                     | _        | _         | 40       | _         | 46       | _    | ps   |  |  |  |

# **IOE Programmable Delay**

Refer to Table 5–36 and 5–37 for IOE programmable delay.

| Table 5-36                       | Table 5–36. Cyclone II IOE Programmable Delay on Column Pins       Notes (1), (2) |              |               |               |                   |               |                          |               |                   |               |      |  |

|----------------------------------|-----------------------------------------------------------------------------------|--------------|---------------|---------------|-------------------|---------------|--------------------------|---------------|-------------------|---------------|------|--|

| Parameter                        | Paths Affected                                                                    | Number<br>of | Fast Corner   |               | –6 Speed<br>Grade |               | -7 Speed<br>Grade<br>(4) |               | –8 Speed<br>Grade |               | Unit |  |

|                                  |                                                                                   | Settings     | Min<br>Offset | Max<br>Offset | Min<br>Offset     | Max<br>Offset | Min<br>Offset            | Max<br>Offset | Min<br>Offset     | Max<br>Offset |      |  |

| Input Delay                      | Pad -> I/O                                                                        | 7            | 0             | 2233          | 0                 | 3827          | 0                        | 4232          | 0                 | 4349          | ps   |  |

| from Pin to<br>Internal<br>Cells | dataout to core                                                                   |              | 0             | 2344          | _                 | _             | 0                        | 4088          | _                 | _             | ps   |  |

| Input Delay                      | Pad -> I/O                                                                        | 8            | 0             | 2656          | 0                 | 4555          | 0                        | 4914          | 0                 | 4940          | ps   |  |

| from Pin to<br>Input<br>Register | input register                                                                    |              | 0             | 2788          | _                 | _             | 0                        | 4748          | _                 | _             | ps   |  |

| Delay from                       | I/O output                                                                        | 2            | 0             | 303           | 0                 | 563           | 0                        | 638           | 0                 | 670           | ps   |  |

| Output Register to Output Pin    | register -> Pad                                                                   |              | 0             | 318           | _                 | _             | 0                        | 617           | _                 |               | ps   |  |

#### *Notes to Table 5–36:*

- (1) The incremental values for the settings are generally linear. For exact values of each setting, use the latest version of the Quartus II software.

- (2) The minimum and maximum offset timing numbers are in reference to setting "0" as available in the Quartus II software.

- (3) The value in the first row for each parameter represents the fast corner timing parameter for industrial and automotive devices. The second row represents the fast corner timing parameter for commercial devices.

- (4) The value in the first row is for automotive devices. The second row is for commercial devices.

| Table 5-37                       | Table 5–37. Cyclone II IOE Programmable Delay on Row Pins Notes (1), (2) (Part 1 of 2) |                |               |                 |                   |               |                       |               |                |               |      |

|----------------------------------|----------------------------------------------------------------------------------------|----------------|---------------|-----------------|-------------------|---------------|-----------------------|---------------|----------------|---------------|------|

| Doromotor                        | Paths Nu                                                                               |                |               | rner <i>(3)</i> | –6 Speed<br>Grade |               | -7 Speed<br>Grade (4) |               | -8 Speed Grade |               | Unit |

| Parameter                        | Affected                                                                               | of<br>Settings | Min<br>Offset | Max<br>Offset   | Min<br>Offset     | Max<br>Offset | Min<br>Offset         | Max<br>Offset | Min<br>Offset  | Max<br>Offset | UIII |

| Input Delay                      | Pad ->                                                                                 | 7              | 0             | 2240            | 0                 | 3776          | 0                     | 4174          | 0              | 4290          | ps   |

| from Pin to<br>Internal<br>Cells | I/O<br>dataout<br>to core                                                              |                | 0             | 2352            |                   |               | 0                     | 4033          | _              | _             | ps   |

(T/2 - D1) / T (the low percentage boundary)

(T/2 + D2) / T (the high percentage boundary)

# **DCD Measurement Techniques**

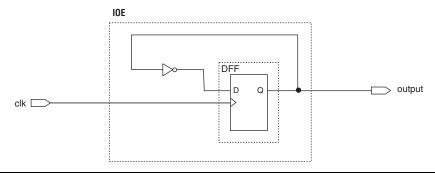

DCD is measured at an FPGA output pin driven by registers inside the corresponding I/O element (IOE) block. When the output is a single data rate signal (non-DDIO), only one edge of the register input clock (positive or negative) triggers output transitions (Figure 5–9). Therefore, any DCD present on the input clock signal, or caused by the clock input buffer, or different input I/O standard, does not transfer to the output signal.

Figure 5–9. DCD Measurement Technique for Non-DDIO (Single-Data Rate) Outputs

However, when the output is a double data rate input/output (DDIO) signal, both edges of the input clock signal (positive and negative) trigger output transitions (Figure 5–10). Therefore, any distortion on the input clock and the input clock buffer affect the output DCD.

Table 7–8 shows the clock sources connectivity to the global clock networks.

| Table 7–8. Global Cl | ock N                  | etwoi    | k Con    | necti    | ons (    | Part :   | 1 of 3   | )        |          |          |          |          |          |          |          |          |

|----------------------|------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Global Clock         |                        |          |          |          |          | (        | Globa    | l Cloc   | k Net    | works    | S        |          |          |          |          |          |

| Network Clock        | All Cyclone II Devices |          |          |          |          |          |          | EP       | 2C15     | throu    | gh EP    | 2C70     | Devi     | ces O    | nly      |          |

| Sources              | 0                      | 1        | 2        | 3        | 4        | 5        | 6        | 7        | 8        | 9        | 10       | 11       | 12       | 13       | 14       | 15       |

| CLK0/LVDSCLK0p       | <b>✓</b>               |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK1/LVDSCLK0n       |                        | <b>✓</b> | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK2/LVDSCLK1p       | <b>✓</b>               |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK3/LVDSCLK1n       |                        | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK4/LVDSCLK2p       |                        |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| CLK5/LVDSCLK2n       |                        |          |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| CLK6/LVDSCLK3p       |                        |          |          |          | <b>✓</b> |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| CLK7/LVDSCLK3n       |                        |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| CLK8/LVDSCLK4n       |                        |          |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |

| CLK9/LVDSCLK4p       |                        |          |          |          |          |          |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          |          |          |

| CLK10/LVDSCLK5n      |                        |          |          |          |          |          |          |          | <b>✓</b> |          |          | <b>✓</b> |          |          |          |          |

| CLK11/LVDSCLK5p      |                        |          |          |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |          |          |

| CLK12/LVDSCLK6n      |                        |          |          |          |          |          |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          |

| CLK13/LVDSCLK6p      |                        |          |          |          |          |          |          |          |          |          |          |          |          | <b>✓</b> | <b>✓</b> |          |

| CLK14/LVDSCLK7n      |                        |          |          |          |          |          |          |          |          |          |          |          | <b>✓</b> |          |          | <b>✓</b> |

| CLK15/LVDSCLK7p      |                        |          |          |          |          |          |          |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |

| PLL1_c0              | <b>✓</b>               | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |

| PLL1_c1              | <b>✓</b>               |          | <b>✓</b> | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |

| PLL1_c2              |                        | <b>✓</b> | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |          |          |

| PLL2_c0              |                        |          |          |          | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| PLL2_c1              |                        |          |          |          | <b>✓</b> |          | <b>✓</b> | <b>✓</b> |          |          |          |          |          |          |          |          |

| PLL2_c2              |                        |          |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| PLL3_c0              |                        |          |          |          |          |          |          |          | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |          |          |          |          |

| PLL3_c1              |                        |          |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> | <b>✓</b> |          |          |          |          |

| PLL3_c2              |                        |          |          |          |          |          |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          |          |          |

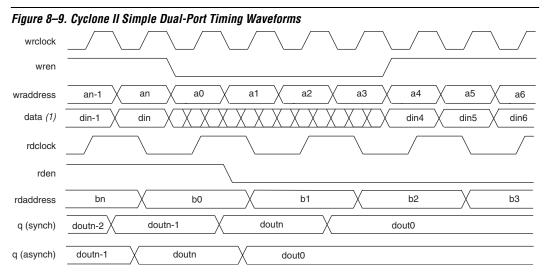

address. See "Read-During- Write Operation at the Same Address" on page 8–28 for more information. Figure 8–9 shows timing waveforms for read and write operations in simple dual-port mode.

#### *Note to Figure 8–9:*

(1) The crosses in the data waveform during read mean "don't care."

#### True Dual-Port Mode

True dual-port mode supports any combination of two-port operations: two reads, two writes, or one read and one write at two different clock frequencies. Figure 8–10 shows Cyclone II true dual-port memory configuration.

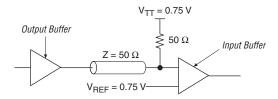

Figure 10-13. 1.5-V HSTL Class I Termination

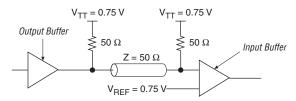

Figure 10-14. 1.5-V HSTL Class II Termination

#### 1.5-V Pseudo-Differential HSTL Class I and II

The 1.5-V differential HSTL standard is formulated under EIA/JEDEC Standard, EIA/JESD8-6: A 1.5V Output Buffer Supply Voltage Based Interface Standard for Digital Integrated Circuits.

The 1.5-V differential HSTL specification is the same as the 1.5-V single-ended HSTL specification. It is used for applications designed to operate in the 0.0- to 1.5-V HSTL logic switching range, such as QDR memory clock interfaces. Cyclone II devices support both input and output levels. Refer to Figures 10–15 and 10–16 for details on the 1.5-V differential HSTL termination.

Cyclone II devices do not support true 1.5-V differential HSTL standards. Cyclone II devices support pseudo-differential HSTL outputs for PLL\_OUT pins and pseudo-differential HSTL inputs for clock pins. Pseudo-differential inputs require an input reference voltage as opposed to the true differential inputs. Refer to Table 10–1 on page 10–2 for information about pseudo-differential HSTL.

The number of embedded multipliers per column and the number of columns available increases with device density. Table 12–1 shows the number of embedded multipliers in each Cyclone II device and the multipliers that you can implement.

| Table 12–1. Number of Embedded Multipliers in Cyclone II Devices |                         |                   |                            |  |  |  |  |  |  |  |

|------------------------------------------------------------------|-------------------------|-------------------|----------------------------|--|--|--|--|--|--|--|

| Device                                                           | Embedded<br>Multipliers | 9 × 9 Multipliers | 18 × 18<br>Multipliers (1) |  |  |  |  |  |  |  |

| EP2C5                                                            | 13                      | 26                | 13                         |  |  |  |  |  |  |  |

| EP2C8                                                            | 18                      | 36                | 18                         |  |  |  |  |  |  |  |

| EP2C20                                                           | 26                      | 52                | 26                         |  |  |  |  |  |  |  |

| EP2C35                                                           | 35                      | 70                | 35                         |  |  |  |  |  |  |  |

| EP2C50                                                           | 86                      | 172               | 86                         |  |  |  |  |  |  |  |

| EP2C70                                                           | 150                     | 300               | 150                        |  |  |  |  |  |  |  |

Note to Table 12-1:

(1) Each device has either the number of 9 × 9 or 18 × 18 multipliers shown. The total number of multipliers for each device is not the sum of all the multipliers.

In addition to the embedded multipliers, you can also implement soft multipliers using Cyclone II M4K memory blocks. The availability of soft multipliers increases the number of multipliers available within the device. Table 12–2 shows the total number of multipliers available in Cyclone II devices using embedded multipliers and soft multipliers.

| Table 12–2. Number of Multipliers in Cyclone II Devices |                   |     |     |  |  |  |  |  |  |

|---------------------------------------------------------|-------------------|-----|-----|--|--|--|--|--|--|

| Device                                                  | Total Multipliers |     |     |  |  |  |  |  |  |

| EP2C5                                                   | 13                | 26  | 39  |  |  |  |  |  |  |

| EP2C8                                                   | 18                | 36  | 54  |  |  |  |  |  |  |

| EP2C20                                                  | 26                | 52  | 78  |  |  |  |  |  |  |

| EP2C35                                                  | 35                | 105 | 140 |  |  |  |  |  |  |

| EP2C50                                                  | 86                | 129 | 215 |  |  |  |  |  |  |

| EP2C70                                                  | 150               | 250 | 400 |  |  |  |  |  |  |

Notes to Table 12-2:

- (1) Soft multipliers are implemented in sum of multiplication mode. The M4K memory blocks are configured with 18-bit data widths to support 16-bit coefficients. The sum of the coefficients requires 18 bits of resolution to account for overflow.

- (2) The total number of multipliers may vary according to the multiplier mode used.

device also pulls nSTATUS and CONF\_DONE low and tri-states all I/O pins. Once the nCONFIG pin returns to a logic high level and the Cyclone II device releases the nSTATUS pin, the MAX II device can begin reconfiguration.

## Error During Configuration

If an error occurs during configuration, the Cyclone II device transitions its <code>nSTATUS</code> pin low, resetting itself internally. The low signal on the <code>nSTATUS</code> pin tells the MAX II device that there is an error. If you turn on the **Auto-restart configuration after error** option in the Quartus II software, the Cyclone II device releases <code>nSTATUS</code> after a reset time-out period (maximum of 40  $\mu$ s). After <code>nSTATUS</code> is released and pulled high by a pull-up resistor, the MAX II device can try to reconfigure the target device without needing to pulse <code>nCONFIG</code> low. If this option is turned off, the MAX II device must generate a low-to-high transition (with a low pulse of at least 2  $\mu$ s) on <code>nCONFIG</code> to restart the configuration process.

The MAX II device can also monitor the CONF\_DONE and INIT\_DONE pins to ensure successful configuration. The MAX II device must monitor the Cyclone II device's CONF\_DONE pin to detect errors and determine when programming completes. If all configuration data is sent, but CONF\_DONE or INIT\_DONE do not transition high, the MAX II device must reconfigure the target device.

For more information on configuration issues, see the *Debugging Configuration Problems* chapter of the *Configuration Handbook* and the FPGA Configuration Troubleshooter on the Altera web site (www.altera.com).

# Multiple Device PS Configuration Using a MAX II Device as an External Host

Figure 13–10 shows how to configure multiple devices using a MAX II device. This circuit is similar to the PS configuration circuit for a single device, except Cyclone II devices are cascaded for multiple device configuration.

### Configuration Stage

When the nSTATUS pin transitions high, the configuration device's OE pin also transitions high and the configuration device clocks data out serially to the FPGA using its internal oscillator. The Cyclone II device receives configuration data on its DATAO pin and the clock is received on the DCLK pin. Data is latched into the FPGA on the rising edge of DCLK.

After the FPGA has received all configuration data successfully, it releases the open-drain CONF\_DONE pin, which is pulled high by a pull-up resistor. Since the Cyclone II device's CONF\_DONE pin is tied to the configuration device's nCS pin, the configuration device is disabled when CONF\_DONE goes high. Enhanced configuration and EPC2 devices have an optional internal pull-up resistor on the nCS pin. You can turn this option on in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. If you do not use this internal pull-up resistor, you need to connect an external 10-k $\Omega$ pull-up resistor to the nCS and CONF\_DONE line. A low-to-high transition on CONF\_DONE indicates configuration is complete, and the device can begin initialization.

## Initialization Stage

In Cyclone II devices, the default initialization clock source is the Cyclone II internal oscillator (typically 10 MHz). Cyclone II devices can also use the optional CLKUSR pin. If your design uses the internal oscillator, the Cyclone II device supplies itself with enough clock cycles for proper initialization. The advantage of using the internal oscillator is you do not need to use another device or source to send additional clock cycles to the CLKUSR pin during the initialization stage. Additionally, you can use of the CLKUSR pin as a user I/O pin, which means you have an additional user I/O pin.

If you want to delay the initialization of the device, you can use the CLKUSR pin. Using the CLKUSR pin allows you to control when the Cyclone II device enters user mode. You can delay the Cyclone II devices from entering user mode for an indefinite amount of time. You can turn on the Enable user-supplied start-up clock (CLKUSR) option in the Quartus II software from the General tab of the Device & Pin Options dialog box. Supplying a clock on CLKUSR does not affect the configuration process. After all configuration data is accepted and CONF\_DONE goes high, Cyclone II devices require 299 clock cycles to properly initialize and support a CLKUSR  $f_{\rm MAX}$  of 100 MHz.

An optional <code>INIT\_DONE</code> pin is available, which signals the end of initialization and the start of user mode with a low-to-high transition. The <code>Enable INIT\_DONE</code> output option is available in the Quartus II software from the <code>General</code> tab of the <code>Device & Pin Options</code> dialog box. If you use the <code>INIT\_DONE</code> pin, an external 10-k $\Omega$ pull-up resistor pulls it high when

| Table 13–11. Dedicated Configuration Pins on the Cyclone II Device (Part 4 of 5) |                                                          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|----------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                                                         | User<br>Mode                                             | Configuration<br>Scheme | Pin Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| nCEO                                                                             | N/A if option is on. I/O if option is off.               | All                     | Output   | This pin is an output that drives low when device configuration is complete. In single device configuration, you can leave this pin floating or use it as a user I/O pin after configuration. In multiple device configuration, this pin inputs the next device's nCE pin. The nCEO of the last device in the chain can be left floating or used as a user I/O pin after configuration. If you use the nCEO pin to feed next device's nCE pin, use an external 10-k $\Omega$ pull-up resistor to pull the nCEO pin high to the V $_{CCIO}$ voltage of its I/O bank to help the internal weak pull-up resistor. |  |  |  |

|                                                                                  |                                                          |                         |          | Use the Quartus II software to make this pin a user I/O pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| ASDO                                                                             | N/A in<br>AS<br>mode<br>I/O in<br>PS and<br>JTAG<br>mode | AS                      | Output   | This pin sends a control signal from the Cyclone II device to the serial configuration device in AS mode and is used to read out configuration data.  In AS mode, ASDO has an internal pull-up that is always active.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| nCSO                                                                             | N/A in<br>AS<br>mode<br>I/O in<br>PS and<br>JTAG<br>mode | AS                      | Output   | This pin sends an output control signal from the Cyclone II device to the serial configuration device in AS mode that enables the configuration device.  In AS mode, nCSO has an internal pull-up resistor that is always active.                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

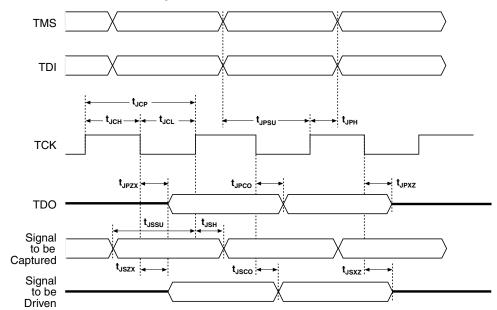

When the TAP controller is in the TEST\_LOGIC/RESET state, the BST circuitry is disabled, the device is in normal operation, and the instruction register is initialized with IDCODE as the initial instruction. At device power-up, the TAP controller starts in this TEST\_LOGIC/RESET state. In addition, forcing the TAP controller to the TEST\_LOGIC/RESET state is done by holding TMS high for five TCK clock cycles. Once in the TEST\_LOGIC/RESET state, the TAP controller remains in this state as long as TMS is held high (while TCK is clocked). Figure 14–6 shows the timing requirements for the IEEE Std. 1149.1 signals.

Figure 14-6. IEEE Std. 1149.1 Timing Waveforms

To start IEEE Std. 1149.1 operation, select an instruction mode by advancing the TAP controller to the shift instruction register (SHIFT\_IR) state and shift in the appropriate instruction code on the <code>TDI</code> pin. The waveform diagram in Figure 14–7 represents the entry of the instruction code into the instruction register. It shows the values of <code>TCK</code>, <code>TMS</code>, <code>TDI</code>, <code>TDO</code>, and the states of the TAP controller. From the <code>RESET</code> state, <code>TMS</code> is clocked with the pattern <code>01100</code> to advance the TAP controller to <code>SHIFT\_IR</code>.

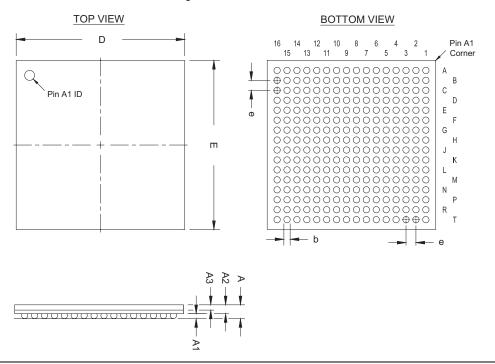

# 256-Pin FineLine Ball-Grid Array, Option 2 - Wirebond

- All dimensions and tolerances conform to ASME Y14.5M 1994.

- Controlling dimension is in millimeters.

- Pin A1 may be indicated by an ID dot, or a special feature, in its proximity on the package surface.

This POD is applicable to the F256 package of the Cyclone II product only.

Tables 15–11 and 15–12 show the package information and package outline figure references, respectively, for the 256-pin FineLine BGA package.

| Table 15–11. 256-Pin FineLine BGA Package Information |                                                           |  |  |  |  |  |

|-------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|

| Description                                           | Specification                                             |  |  |  |  |  |

| Ordering code reference                               | F                                                         |  |  |  |  |  |

| Package acronym                                       | FineLine BGA                                              |  |  |  |  |  |

| Substrate material                                    | ВТ                                                        |  |  |  |  |  |

| Solder ball composition                               | Regular: 63Sn:37Pb (Typ.)<br>Pb-free: Sn:3Ag:0.5Cu (Typ.) |  |  |  |  |  |

| JEDEC Outline Reference                               | MO-192 Variation: AAF-1                                   |  |  |  |  |  |

| Maximum lead coplanarity                              | 0.008 inches (0.20 mm)                                    |  |  |  |  |  |

| Weight                                                | 1.9 g                                                     |  |  |  |  |  |

| Moisture sensitivity level                            | Printed on moisture barrier bag                           |  |  |  |  |  |

| Table 15–12. 256-Pin FineLine BGA Package Outline Dimensions |            |      |      |  |  |  |

|--------------------------------------------------------------|------------|------|------|--|--|--|

| Cumbal                                                       | Millimeter |      |      |  |  |  |

| Symbol                                                       | Min.       | Nom. | Max. |  |  |  |

| Α                                                            | _          | _    | 1.55 |  |  |  |

| A1                                                           | 0.25       | _    | _    |  |  |  |

| A2                                                           | 1.05 REF   |      |      |  |  |  |

| A3                                                           | _          | _    | 0.80 |  |  |  |

| D                                                            | 17.00 BSC  |      |      |  |  |  |

| E                                                            | 17.00 BSC  |      |      |  |  |  |

| b                                                            | 0.40       | 0.50 | 0.55 |  |  |  |

| е                                                            | 1.00 BSC   |      |      |  |  |  |

Figure 15–4 shows a 256-pin FineLine BGA package outline.

Figure 15-4. 256-Pin FineLine BGA Package Outline