Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 3158                                                    |

| Number of Logic Elements/Cells | 50528                                                   |

| Total RAM Bits                 | 594432                                                  |

| Number of I/O                  | 294                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                      |

| Package / Case                 | 484-BGA                                                 |

| Supplier Device Package        | 484-FBGA (23x23)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c50f484i8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Configuration File Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13–1                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Comiguration inc i office                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13–3                                          |

| Configuration Data Compression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               |

| Active Serial Configuration (Serial Configuration Devices)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                               |

| Single Device AS Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               |

| Multiple Device AS Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

| Configuring Multiple Cyclone II Devices with the Same Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |

| Estimating AS Configuration Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13–18                                         |

| Programming Serial Configuration Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13–19                                         |

| PS Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

| Single Device PS Configuration Using a MAX II Device as an External Host                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13–22                                         |

| Multiple Device PS Configuration Using a MAX II Device as an External Host                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13–26                                         |

| PS Configuration Using a Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |

| Single Device PS Configuration Using a Configuration Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |

| Multiple Device PS Configuration Using a Configuration Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |

| PS Configuration Using a Download Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |

| JTAG Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

| Single Device JTAG Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

| JTAG Configuration of Multiple Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |

| Jam STAPL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13–60                                         |

| Configuring Cyclone II FPGAs with JRunner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                               |

| Combining JTAG & Active Serial Configuration Schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |

| Programming Serial Configuration Devices In-System Using the JTAG Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13–61                                         |

| Device Configuration Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13_64                                         |

| Device Comiguration in 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10 01                                         |

| Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                               |

| O .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

| Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                               |

| Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13–70                                         |

| Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13–70                                         |

| Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13–70                                         |

| Conclusion  Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction  IEEE Std. 1149.1 BST Architecture IEEE Std. 1149.1 Boundary-Scan Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13–70<br>14–1<br>14–2<br>14–4                 |

| Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction IEEE Std. 1149.1 BST Architecture IEEE Std. 1149.1 Boundary-Scan Register Boundary-Scan Cells of a Cyclone II Device I/O Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13–70<br>14–1<br>14–2<br>14–4                 |

| Conclusion  Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction  IEEE Std. 1149.1 BST Architecture  IEEE Std. 1149.1 Boundary-Scan Register  Boundary-Scan Cells of a Cyclone II Device I/O Pin  IEEE Std. 1149.1 BST Operation Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13–70<br>14–1<br>14–2<br>14–4<br>14–6         |

| Conclusion  Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction  IEEE Std. 1149.1 BST Architecture IEEE Std. 1149.1 Boundary-Scan Register Boundary-Scan Cells of a Cyclone II Device I/O Pin IEEE Std. 1149.1 BST Operation Control SAMPLE/PRELOAD Instruction Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13–70<br>14–1<br>14–2<br>14–4<br>14–6<br>14–9 |

| Conclusion  Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction  IEEE Std. 1149.1 BST Architecture  IEEE Std. 1149.1 Boundary-Scan Register  Boundary-Scan Cells of a Cyclone II Device I/O Pin  IEEE Std. 1149.1 BST Operation Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |

| Conclusion  Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction  IEEE Std. 1149.1 BST Architecture IEEE Std. 1149.1 Boundary-Scan Register Boundary-Scan Cells of a Cyclone II Device I/O Pin IEEE Std. 1149.1 BST Operation Control  SAMPLE/PRELOAD Instruction Mode Capture Phase Shift & Update Phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               |

| Conclusion  Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction IEEE Std. 1149.1 BST Architecture IEEE Std. 1149.1 Boundary-Scan Register Boundary-Scan Cells of a Cyclone II Device I/O Pin IEEE Std. 1149.1 BST Operation Control SAMPLE/PRELOAD Instruction Mode Capture Phase Shift & Update Phases EXTEST Instruction Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |

| Conclusion  Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |

| Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction IEEE Std. 1149.1 BST Architecture IEEE Std. 1149.1 Boundary-Scan Register Boundary-Scan Cells of a Cyclone II Device I/O Pin IEEE Std. 1149.1 BST Operation Control SAMPLE/PRELOAD Instruction Mode Capture Phase Shift & Update Phases EXTEST Instruction Mode Capture Phase Shift & Update Phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |

| Conclusion  Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |

| Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction IEEE Std. 1149.1 BST Architecture IEEE Std. 1149.1 Boundary-Scan Register Boundary-Scan Cells of a Cyclone II Device I/O Pin IEEE Std. 1149.1 BST Operation Control SAMPLE/PRELOAD Instruction Mode Capture Phase Shift & Update Phases EXTEST Instruction Mode Capture Phase Shift & Update Phases Shift & Update Phases Shift & Update Phases Shift & Update Phases Shift Struction Mode                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

| Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction IEEE Std. 1149.1 BST Architecture IEEE Std. 1149.1 Boundary-Scan Register Boundary-Scan Cells of a Cyclone II Device I/O Pin IEEE Std. 1149.1 BST Operation Control SAMPLE/PRELOAD Instruction Mode Capture Phase Shift & Update Phases EXTEST Instruction Mode Capture Phase Shift & Update Phases Shift & Update Phases BYPASS Instruction Mode IDCODE Instruction Mode USERCODE Instruction Mode                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |

| Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction IEEE Std. 1149.1 BST Architecture IEEE Std. 1149.1 Boundary-Scan Register Boundary-Scan Cells of a Cyclone II Device I/O Pin IEEE Std. 1149.1 BST Operation Control SAMPLE/PRELOAD Instruction Mode Capture Phase Shift & Update Phases EXTEST Instruction Mode Capture Phase Shift & Update Phases Shift & Update Phases BYPASS Instruction Mode IDCODE Instruction Mode                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

| Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction IEEE Std. 1149.1 BST Architecture IEEE Std. 1149.1 Boundary-Scan Register Boundary-Scan Cells of a Cyclone II Device I/O Pin IEEE Std. 1149.1 BST Operation Control SAMPLE/PRELOAD Instruction Mode Capture Phase Shift & Update Phases EXTEST Instruction Mode Capture Phase Shift & Update Phases BYPASS Instruction Mode IDCODE Instruction Mode USERCODE Instruction Mode CLAMP Instruction Mode CLAMP Instruction Mode HIGHZ Instruction Mode                                                                                                                                                                                                                                                                                                                                                      |                                               |

| Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction IEEE Std. 1149.1 BST Architecture IEEE Std. 1149.1 Boundary-Scan Register Boundary-Scan Cells of a Cyclone II Device I/O Pin IEEE Std. 1149.1 BST Operation Control SAMPLE/PRELOAD Instruction Mode Capture Phase Shift & Update Phases EXTEST Instruction Mode Capture Phase Shift & Update Phases BYPASS Instruction Mode IDCODE Instruction Mode USERCODE Instruction Mode CLAMP Instruction Mode                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |

| Conclusion  Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction IEEE Std. 1149.1 BST Architecture IEEE Std. 1149.1 Boundary-Scan Register Boundary-Scan Cells of a Cyclone II Device I/O Pin IEEE Std. 1149.1 BST Operation Control SAMPLE/PRELOAD Instruction Mode Capture Phase Shift & Update Phases EXTEST Instruction Mode Capture Phase Shift & Update Phases Shift & Update Phases BYPASS Instruction Mode IDCODE Instruction Mode USERCODE Instruction Mode CLAMP Instruction Mode HIGHZ Instruction Mode I/O Voltage Support in JTAG Chain                                                                                                                                                                                                                                                                                                         |                                               |

| Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices Introduction IEEE Std. 1149.1 BST Architecture IEEE Std. 1149.1 Boundary-Scan Register Boundary-Scan Cells of a Cyclone II Device I/O Pin IEEE Std. 1149.1 BST Operation Control SAMPLE/PRELOAD Instruction Mode Capture Phase Shift & Update Phases EXTEST Instruction Mode Capture Phase Shift & Update Phases BYPASS Instruction Mode USERCODE Instruction Mode USERCODE Instruction Mode IDCODE Instruction Mode IJCONE INSTRUCTION MODE |                                               |

133-MHz PCI-X 1.0 specification compatibility

High-speed external memory support, including DDR, DDR2, and SDR SDRAM, and QDRII SRAM supported by drop in

Altera IP MegaCore functions for ease of use

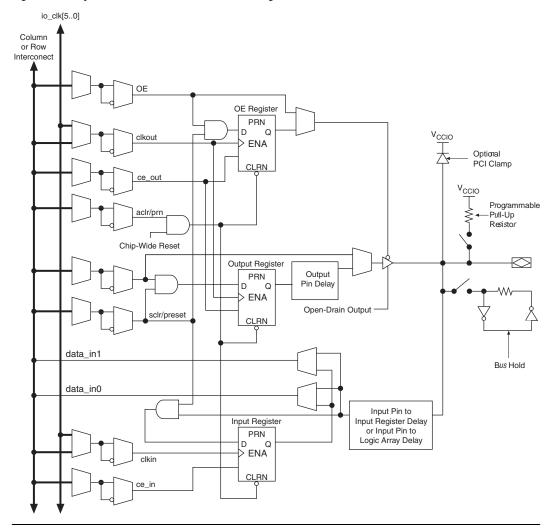

Three dedicated registers per I/O element (IOE): one input register, one output register, and one output-enable register Programmable bus-hold feature

Programmable output drive strength feature

Programmable delays from the pin to the IOE or logic array I/O bank grouping for unique VCCIO and/or VREF bank settings

MultiVolt<sup> $\mathbb{M}$ </sup> I/O standard support for 1.5-, 1.8-, 2.5-, and 3.3-interfaces

Hot-socketing operation support

Tri-state with weak pull-up on I/O pins before and during configuration

Programmable open-drain outputs

Series on-chip termination support

#### Flexible clock management circuitry

Hierarchical clock network for up to 402.5-MHz performance Up to four PLLs per device provide clock multiplication and division, phase shifting, programmable duty cycle, and external clock outputs, allowing system-level clock management and skew control

Up to 16 global clock lines in the global clock network that drive throughout the entire device

#### Device configuration

Fast serial configuration allows configuration times less than  $100 \ \mathrm{ms}$

Decompression feature allows for smaller programming file storage and faster configuration times

Supports multiple configuration modes: active serial, passive serial, and JTAG-based configuration

Supports configuration through low-cost serial configuration devices

Device configuration supports multiple voltages (either 3.3, 2.5, or 1.8 V)

#### Intellectual property

Altera megafunction and Altera MegaCore function support, and Altera Megafunctions Partners Program (AMPP<sup>SM</sup>) megafunction support, for a wide range of embedded processors, on-chip and off-chip interfaces, peripheral functions, DSP functions, and communications functions and

Figure 2–25. Cyclone II IOE in Bidirectional I/O Configuration

The Cyclone II device IOE includes programmable delays to ensure zero hold times, minimize setup times, or increase clock to output times.

A path in which a pin directly drives a register may require a programmable delay to ensure zero hold time, whereas a path in which a pin drives a register through combinational logic may not require the delay. Programmable delays decrease input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time.

The reduced swing differential signaling (RSDS) and mini-LVDS standards are derivatives of the LVDS standard. The RSDS and mini-LVDS I/O standards are similar in electrical characteristics to LVDS, but have a smaller voltage swing and therefore provide increased power benefits and reduced electromagnetic interference (EMI). Cyclone II devices support the RSDS and mini-LVDS I/O standards at data rates up to 311 Mbps at the transmitter.

A subset of pins in each I/O bank (on both rows and columns) support the high-speed I/O interface. The dual-purpose LVDS pins require an external-resistor network at the transmitter channels in addition to 100-termination resistors on receiver channels. These pins do not contain dedicated serialization or deserialization circuitry. Therefore, internal logic performs serialization and deserialization functions.

Cyclone II pin tables list the pins that support the high-speed I/O interface. The number of LVDS channels supported in each device family member is listed in Table 2–18.

| Table 2–18. Cyclone II Device LVDS Channels (Part 1 of 2) |           |                                |  |  |  |  |

|-----------------------------------------------------------|-----------|--------------------------------|--|--|--|--|

| Device                                                    | Pin Count | Number of LVDS<br>Channels (1) |  |  |  |  |

| EP2C5                                                     | 144       | 31 (35)                        |  |  |  |  |

|                                                           | 208       | 56 (60)                        |  |  |  |  |

|                                                           | 256       | 61 (65)                        |  |  |  |  |

| EP2C8                                                     | 144       | 29 (33)                        |  |  |  |  |

|                                                           | 208       | 53 (57)                        |  |  |  |  |

|                                                           | 256       | 75 (79)                        |  |  |  |  |

| EP2C15                                                    | 256       | 52 (60)                        |  |  |  |  |

|                                                           | 484       | 128 (136)                      |  |  |  |  |

| EP2C20                                                    | 240       | 45 (53)                        |  |  |  |  |

|                                                           | 256       | 52 (60)                        |  |  |  |  |

|                                                           | 484       | 128 (136)                      |  |  |  |  |

| EP2C35                                                    | 484       | 131 (139)                      |  |  |  |  |

|                                                           | 672       | 201 (209)                      |  |  |  |  |

| EP2C50                                                    | 484       | 119 (127)                      |  |  |  |  |

|                                                           | 672       | 189 (197)                      |  |  |  |  |

| Table 3–1. Cyclone II JTAG Instructions (Part 2 of 2) |                  |                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|-------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| JTAG Instruction                                      | Instruction Code | Description                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| CONFIG_IO                                             | 00 0000 1101     | Allows configuration of I/O standards through the JTAG chain for JTAG testing. Can be executed before, after, or during configuration. Stops configuration if executed during configuration. Once issued, the CONFIG_IO instruction holds nSTATUS low to reset the configuration device. nSTATUS is held low until the device is reconfigured. |  |  |  |  |

| SignalTap II instructions                             |                  | Monitors internal device operation with the SignalTap II embedded logic analyzer.                                                                                                                                                                                                                                                              |  |  |  |  |

#### *Note to Table 3–1:*

(1) Bus hold and weak pull-up resistor features override the high-impedance state of HIGHZ, CLAMP, and EXTEST.

The Quartus II software has an Auto Usercode feature where you can choose to use the checksum value of a programming file as the JTAG user code. If selected, the checksum is automatically loaded to the USERCODE register. In the **Settings** dialog box in the Assignments menu, click **Device** & Pin Options, then **General**, and then turn on the **Auto Usercode** option.

## **Devices Can Be Driven before Power-Up**

You can drive signals into the I/O pins, dedicated input pins, and dedicated clock pins of Cyclone II devices before or during power-up or power-down without damaging the device. Cyclone II devices support any power-up or power-down sequence ( $V_{\text{CCIO}}$  and  $V_{\text{CCINT}}$ ) to simplify system level design.

# I/O Pins Remain Tri-Stated during Power-Up

A device that does not support hot socketing may interrupt system operation or cause contention by driving out before or during power-up. In a hot-socketing situation, the Cyclone II device's output buffers are turned off during system power-up or power-down. The Cyclone II device also does not drive out until the device is configured and has attained proper operating conditions. The I/O pins are tri-stated until the device enters user mode with a weak pull-up resistor (R) to 3.3V. Refer to Figure 4–1 for more information.

You can power up or power down the  $V_{CCIO}$  and  $V_{CCINT}$  pins in any sequence. The  $V_{CCIO}$  and  $V_{CCINT}$  must have monotonic rise to their steady state levels. (Refer to Figure 4–3 for more information.) The power supply ramp rates can range from 100  $\mu$ s to 100 ms for non "A" devices. Both  $V_{CC}$  supplies must power down within 100 ms of each other to prevent I/O pins from driving out. During hot socketing, the I/O pin capacitance is less than 15 pF and the clock pin capacitance is less than 20 pF. Cyclone II devices meet the following hot-socketing specification.

The hot-socketing DC specification is  $\mid$   $I_{IOPIN}\mid$  < 300  $\mu$ A. The hot-socketing AC specification is  $\mid$   $I_{IOPIN}\mid$  < 8 mA for 10 ns or less.

This specification takes into account the pin capacitance but not board trace and external loading capacitance. You must consider additional capacitance for trace, connector, and loading separately.

$I_{IOPIN}$  is the current at any user I/O pin on the device. The DC specification applies when all  $V_{CC}$  supplies to the device are stable in the powered-up or powered-down conditions. For the AC specification, the peak current duration due to power-up transients is 10 ns or less.

A possible concern for semiconductor devices in general regarding hot socketing is the potential for latch-up. Latch-up can occur when electrical subsystems are hot socketed into an active system. During hot socketing, the signal pins may be connected and driven by the active system before

| Table 5–3.          | Table 5–3. DC Characteristics for User I/O, Dual-Purpose, and Dedicated Pins (Part 1 of 2) |                                                 |            |         |         |                   |      |  |

|---------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------|------------|---------|---------|-------------------|------|--|

| Symbol              | Parameter                                                                                  | Conditions                                      |            | Minimum | Typical | Maximum           | Unit |  |

| V <sub>IN</sub>     | Input voltage                                                                              | (1)                                             | , (2)      | -0.5    | _       | 4.0               | V    |  |

| l <sub>i</sub>      | Input pin leakage current                                                                  | $V_{IN} = V_{CCIOmax} t$                        | o 0 V (3)  | -10     | _       | 10                | μA   |  |

| V <sub>OUT</sub>    | Output voltage                                                                             | -                                               | _          | 0       | _       | V <sub>CCIO</sub> | V    |  |

| l <sub>oz</sub>     | Tri-stated I/O pin leakage current                                                         | $V_{OUT} = V_{CCIOmax}$                         | to 0 V (3) | -10     | _       | 10                | μΑ   |  |

| I <sub>CCINTO</sub> | V <sub>CCINT</sub> supply                                                                  | V <sub>IN</sub> = ground,                       | EP2C5/A    | _       | 0.010   | (4)               | Α    |  |

|                     | current (standby)                                                                          | no load, no                                     | EP2C8/A    | _       | 0.017   | (4)               | Α    |  |

|                     |                                                                                            | toggling inputs $T_{.1} = 25^{\circ} \text{ C}$ | EP2C15A    | _       | 0.037   | (4)               | Α    |  |

|                     |                                                                                            | Nominal                                         | EP2C20/A   | _       | 0.037   | (4)               | Α    |  |

|                     |                                                                                            | V <sub>CCINT</sub>                              | EP2C35     | _       | 0.066   | (4)               | Α    |  |

|                     |                                                                                            |                                                 | EP2C50     | _       | 0.101   | (4)               | Α    |  |

|                     |                                                                                            |                                                 | EP2C70     | _       | 0.141   | (4)               | Α    |  |

| I <sub>CCIO0</sub>  | V <sub>CCIO</sub> supply current                                                           | V <sub>IN</sub> = ground,                       | EP2C5/A    | _       | 0.7     | (4)               | mA   |  |

|                     | (standby)                                                                                  | no load, no toggling inputs                     | EP2C8/A    | _       | 0.8     | (4)               | mA   |  |

|                     |                                                                                            | $T_{.1} = 25^{\circ} \text{ C}$                 | EP2C15A    | _       | 0.9     | (4)               | mA   |  |

|                     |                                                                                            | $V_{CCIO} = 2.5 \text{ V}$                      | EP2C20/A   | _       | 0.9     | (4)               | mA   |  |

|                     |                                                                                            |                                                 | EP2C35     | _       | 1.3     | (4)               | mA   |  |

|                     |                                                                                            |                                                 | EP2C50     | _       | 1.3     | (4)               | mA   |  |

|                     |                                                                                            |                                                 | EP2C70     | _       | 1.7     | (4)               | mA   |  |

| Table 5–42. Cyclone II I/O Output Delay for Column Pins (Part 2 of 6) |                   |                  |                           |                 |                |                       |                       |                      |      |

|-----------------------------------------------------------------------|-------------------|------------------|---------------------------|-----------------|----------------|-----------------------|-----------------------|----------------------|------|

|                                                                       |                   |                  | Fast Co                   | rner            | -6             | -7                    | -7                    | -8<br>Speed<br>Grade |      |

| I/O Standard                                                          | Drive<br>Strength | Parameter        | Industrial/<br>Automotive | Commer<br>-cial | Speed<br>Grade | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) |                      | Unit |

| 2.5V                                                                  | 4 mA              | t <sub>OP</sub>  | 1208                      | 1267            | 2478           | 2614                  | 2743                  | 2750                 | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1340                      | 1406            | 2648           | 2808                  | 2969                  | 2969                 | ps   |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 1190                      | 1248            | 2307           | 2434                  | 2554                  | 2561                 | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1322                      | 1387            | 2477           | 2628                  | 2780                  | 2780                 | ps   |

|                                                                       | 12 mA             | t <sub>OP</sub>  | 1154                      | 1210            | 2192           | 2314                  | 2430                  | 2437                 | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1286                      | 1349            | 2362           | 2508                  | 2656                  | 2656                 | ps   |

|                                                                       | 16 mA             | t <sub>OP</sub>  | 1140                      | 1195            | 2152           | 2263                  | 2375                  | 2382                 | ps   |

|                                                                       | (1)               | t <sub>DIP</sub> | 1272                      | 1334            | 2322           | 2457                  | 2601                  | 2601                 | ps   |

| 1.8V                                                                  | 2 mA              | t <sub>OP</sub>  | 1682                      | 1765            | 3988           | 4279                  | 4563                  | 4570                 | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1814                      | 1904            | 4158           | 4473                  | 4789                  | 4789                 | ps   |

|                                                                       | 4 mA              | t <sub>OP</sub>  | 1567                      | 1644            | 3301           | 3538                  | 3768                  | 3775                 | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1699                      | 1783            | 3471           | 3732                  | 3994                  | 3994                 | ps   |

|                                                                       | 6 mA              | t <sub>OP</sub>  | 1475                      | 1547            | 2993           | 3195                  | 3391                  | 3398                 | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1607                      | 1686            | 3163           | 3389                  | 3617                  | 3617                 | ps   |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 1451                      | 1522            | 2882           | 3074                  | 3259                  | 3266                 | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1583                      | 1661            | 3052           | 3268                  | 3485                  | 3485                 | ps   |

|                                                                       | 10 mA             | t <sub>OP</sub>  | 1438                      | 1508            | 2853           | 3041                  | 3223                  | 3230                 | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1570                      | 1647            | 3023           | 3235                  | 3449                  | 3449                 | ps   |

|                                                                       | 12 mA             | t <sub>OP</sub>  | 1438                      | 1508            | 2853           | 3041                  | 3223                  | 3230                 | ps   |

|                                                                       | (1)               | t <sub>DIP</sub> | 1570                      | 1647            | 3023           | 3235                  | 3449                  | 3449                 | ps   |

| 1.5V                                                                  | 2 mA              | t <sub>OP</sub>  | 2083                      | 2186            | 4477           | 4870                  | 5256                  | 5263                 | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 2215                      | 2325            | 4647           | 5064                  | 5482                  | 5482                 | ps   |

|                                                                       | 4 mA              | t <sub>OP</sub>  | 1793                      | 1881            | 3649           | 3965                  | 4274                  | 4281                 | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1925                      | 2020            | 3819           | 4159                  | 4500                  | 4500                 | ps   |

|                                                                       | 6 mA              | t <sub>OP</sub>  | 1770                      | 1857            | 3527           | 3823                  | 4112                  | 4119                 | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1902                      | 1996            | 3697           | 4017                  | 4338                  | 4338                 | ps   |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 1703                      | 1787            | 3537           | 3827                  | 4111                  | 4118                 | ps   |

|                                                                       | (1)               | t <sub>DIP</sub> | 1835                      | 1926            | 3707           | 4021                  | 4337                  | 4337                 | ps   |

(T/2 - D1) / T (the low percentage boundary)

(T/2 + D2) / T (the high percentage boundary)

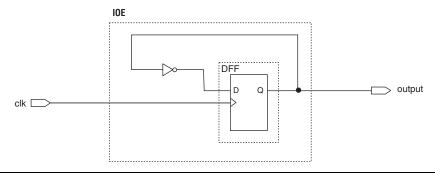

## **DCD Measurement Techniques**

DCD is measured at an FPGA output pin driven by registers inside the corresponding I/O element (IOE) block. When the output is a single data rate signal (non-DDIO), only one edge of the register input clock (positive or negative) triggers output transitions (Figure 5–9). Therefore, any DCD present on the input clock signal, or caused by the clock input buffer, or different input I/O standard, does not transfer to the output signal.

Figure 5–9. DCD Measurement Technique for Non-DDIO (Single-Data Rate) Outputs

However, when the output is a double data rate input/output (DDIO) signal, both edges of the input clock signal (positive and negative) trigger output transitions (Figure 5–10). Therefore, any distortion on the input clock and the input clock buffer affect the output DCD.

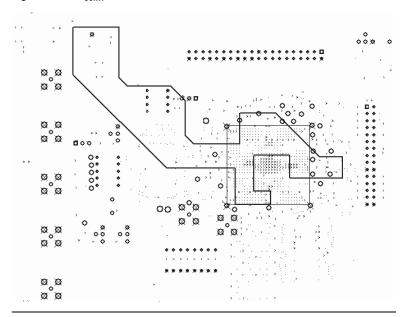

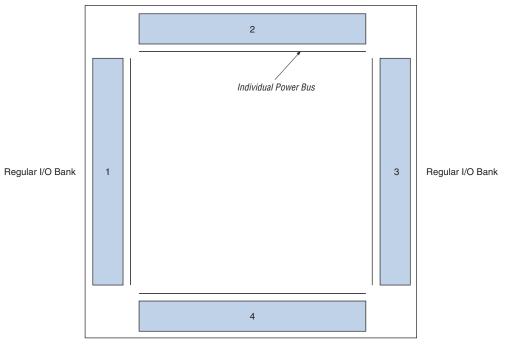

Figure 7–16. V<sub>CCINT</sub> Plane Partitioned for VCCA Island

#### Thick VCCA Trace

Because of board constraints, you may not be able to partition a VCCA island. Instead, run a thick trace from the power supply to each VCCA pin. The traces should be at least 20 mils thick.

In each of these three cases, you should filter each VCCA pin with a decoupling circuit shown in Figure 7–17. Place a ferrite bead that exhibits high impedance at frequencies of 50 MHz or higher and a 10  $\mu F$  tantalum parallel capacitor where the power enters the board. Decouple each VCCA pin with a 0.1  $\mu F$  and 0.001  $\mu F$  parallel combination of ceramic capacitors located as close as possible to the Cyclone II device. You can connect the GNDA pins directly to the same ground plane as the device's digital ground.

# Document Revision History

Table 7–10 shows the revision history for this document.

| Table 7–10. Document Revision History |                                                                                                                                                                                                         |                                                                                                                                                             |  |  |  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date & Document Changes Made Version  |                                                                                                                                                                                                         | Summary of Changes                                                                                                                                          |  |  |  |

| February 2007<br>v3.1                 | Added document revision history.  Updated handpara note in "Introduction".  Updated Note (3)in Table 7–2.  Updated Figure 7–5.  Updated "Control Signals" section.  Updated "Thick VCCA Trace" section. | Updated chapter with extended temperature information. Updated pllena information in "Control Signals" section. Corrected capacitor unit from10-F to 10 µF. |  |  |  |

| December 2005<br>v2.2                 | Updated industrial temperature range                                                                                                                                                                    |                                                                                                                                                             |  |  |  |

| November 2005<br>v2.1                 | Updated Figure 7–12.<br>Updated Figure 7–17.                                                                                                                                                            |                                                                                                                                                             |  |  |  |

| July 2005 v2.0                        | Updated Table 7–6. Updated "Hardware Features" section. Updated "areset" section. Updated Table 7–8. Added "Board Layout" section.                                                                      |                                                                                                                                                             |  |  |  |

| February 2005<br>v1.2                 | Updated information concerning signals. Added a note to Figures 7-9 through 7-13 regarding violating the setup or hold time on address registers.                                                       |                                                                                                                                                             |  |  |  |

| November,<br>2004 v1.1                | Updated "Introduction" section.                                                                                                                                                                         |                                                                                                                                                             |  |  |  |

| June 2004 v1.0                        | Added document to the Cyclone II Device Handbook.                                                                                                                                                       |                                                                                                                                                             |  |  |  |

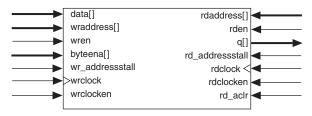

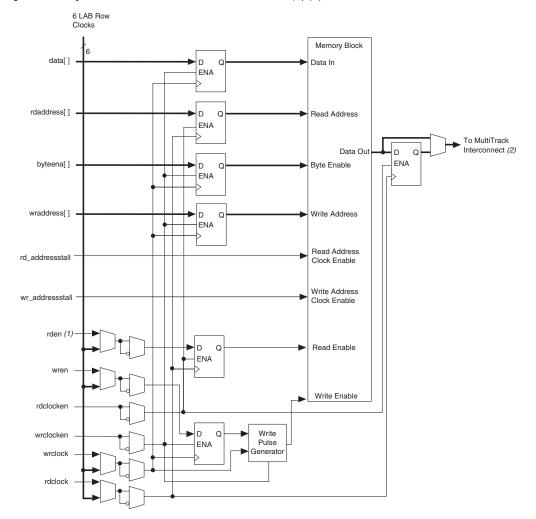

Figure 8–8. Cyclone II Simple Dual-Port Mode Note (1)

#### Simple Dual-Port Memory

*Note to Figure 8–8:*

Simple dual-port RAM supports input and output clock mode in addition to the read and write clock mode shown.

Cyclone II memory blocks support mixed-width configurations, allowing different read and write port widths. Tables 8–5 and 8–6 show the mixed-width configurations.

| Table 8–5. | Table 8–5. Cyclone II Memory Block Mixed-Width Configurations (Simple Dual-Port Mode) |        |        |         |          |          |         |          |          |  |

|------------|---------------------------------------------------------------------------------------|--------|--------|---------|----------|----------|---------|----------|----------|--|

| Dood Dow   | Write Port                                                                            |        |        |         |          |          |         |          |          |  |

| Read Port  | 4K × 1                                                                                | 2K × 2 | 1K × 4 | 512 × 8 | 256 × 16 | 128 × 32 | 512 × 9 | 256 × 18 | 128 × 36 |  |

| 4K × 1     | V                                                                                     | V      | V      | / V     | V        |          |         |          |          |  |

| 2K × 2     | V                                                                                     | ٧      | V      | / V     | V        |          |         |          |          |  |

| 1K × 4     | V                                                                                     | V      | V      | / v     | V        |          |         |          |          |  |

| 512 × 8    | ٧                                                                                     | V      | ٧      | / V     | V        |          |         |          |          |  |

| 256 × 16   | V                                                                                     | V      | V      | / V     | V        |          |         |          |          |  |

| 128 × 32   | V                                                                                     | V      | V      | / v     | V        |          |         |          |          |  |