Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 3158                                                    |

| Number of Logic Elements/Cells | 50528                                                   |

| Total RAM Bits                 | 594432                                                  |

| Number of I/O                  | 294                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 484-FBGA                                                |

| Supplier Device Package        | 484-UBGA (19x19)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c50u484c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Global Clock Network

The 16 or 8 global clock networks drive throughout the entire device. Dedicated clock pins (CLK[]), PLL outputs, the logic array, and dual-purpose clock (DPCLK[]) pins can also drive the global clock network.

The global clock network can provide clocks for all resources within the device, such as IOEs, LEs, memory blocks, and embedded multipliers. The global clock lines can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin, or DQS signals for DDR SDRAM or QDRII SRAM interfaces. Internal logic can also drive the global clock network for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fan-out.

### Clock Control Block

There is a clock control block for each global clock network available in Cyclone II devices. The clock control blocks are arranged on the device periphery and there are a maximum of 16 clock control blocks available per Cyclone II device. The larger Cyclone II devices (EP2C15 devices and larger) have 16 clock control blocks, four on each side of the device. The smaller Cyclone II devices (EP2C5 and EP2C8 devices) have eight clock control blocks, four on the left and right sides of the device.

The control block has these functions:

- Dynamic global clock network clock source selection

- Dynamic enable/disable of the global clock network

In Cyclone II devices, the dedicated CLK[] pins, PLL counter outputs, DPCLK[] pins, and internal logic can all feed the clock control block. The output from the clock control block in turn feeds the corresponding global clock network.

The following sources can be inputs to a given clock control block:

- Four clock pins on the same side as the clock control block

- Three PLL clock outputs from a PLL

- Four DPCLK pins (including CDPCLK pins) on the same side as the clock control block

- Four internally-generated signals

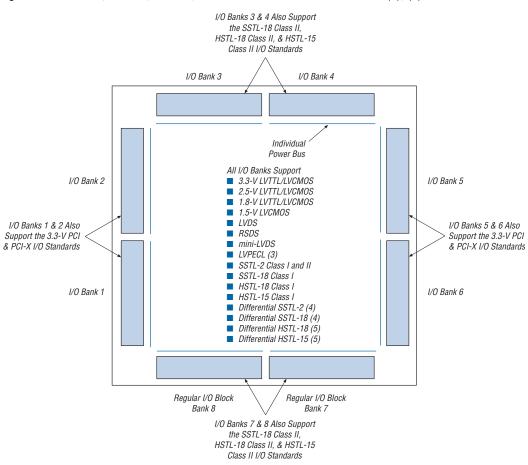

Figure 2–29. EP2C15, EP2C20, EP2C35, EP2C50 & EP2C70 I/O Banks Notes (1), (2)

### Notes to Figure 2–29:

- (1) This is a top view of the silicon die.

- (2) This is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (5) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

Each I/O bank has its own VCCIO pins. A single device can support 1.5-V, 1.8-V, 2.5-V, and 3.3-V interfaces; each individual bank can support a different standard with different I/O voltages. Each bank also has dual-purpose VREF pins to support any one of the voltage-referenced

# 5. DC Characteristics and Timing Specifications

CII51005-4.0

# Operating Conditions

Cyclone® II devices are offered in commercial, industrial, automotive, and extended temperature grades. Commercial devices are offered in -6 (fastest), -7, and -8 speed grades.

All parameter limits are representative of worst-case supply voltage and junction temperature conditions. Unless otherwise noted, the parameter values in this chapter apply to all Cyclone II devices. AC and DC characteristics are specified using the same numbers for commercial, industrial, and automotive grades. All parameters representing voltages are measured with respect to ground.

Tables 5–1 through 5–4 provide information on absolute maximum ratings.

| Table 5–1. Cyclone II Device Absolute Maximum Ratings         Notes (1), (2) |                            |                         |         |         |      |

|------------------------------------------------------------------------------|----------------------------|-------------------------|---------|---------|------|

| Symbol                                                                       | Parameter                  | Conditions              | Minimum | Maximum | Unit |

| V <sub>CCINT</sub>                                                           | Supply voltage             | With respect to ground  | -0.5    | 1.8     | V    |

| V <sub>CCIO</sub>                                                            | Output supply voltage      |                         | -0.5    | 4.6     | V    |

| V <sub>CCA—PLL</sub> [14]                                                    | PLL supply voltage         |                         | -0.5    | 1.8     | V    |

| V <sub>IN</sub>                                                              | DC input voltage (3)       | _                       | -0.5    | 4.6     | V    |

| I <sub>OUT</sub>                                                             | DC output current, per pin | _                       | -25     | 40      | mA   |

| T <sub>STG</sub>                                                             | Storage temperature        | No bias                 | -65     | 150     | °C   |

| $T_J$                                                                        | Junction temperature       | BGA packages under bias | _       | 125     | °C   |

#### Notes to Table 5-1:

- (1) Conditions beyond those listed in this table cause permanent damage to a device. These are stress ratings only. Functional operation at these levels or any other conditions beyond those specified in this chapter is not implied. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effect on the device reliability.

- (2) Refer to the Operating Requirements for Altera Devices Data Sheet for more information.

- (3) During transitions, the inputs may overshoot to the voltage shown in Table 5–4 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transition, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

Table 5–2 specifies the recommended operating conditions for Cyclone II devices. It shows the allowed voltage ranges for  $V_{CCINT}$ ,  $V_{CCIO}$ , and the operating junction temperature ( $T_J$ ). The LVTTL and LVCMOS inputs are powered by  $V_{CCIO}$  only. The LVDS and LVPECL input buffers on dedicated clock pins are powered by  $V_{CCINT}$ . The SSTL, HSTL, LVDS input buffers are powered by both  $V_{CCINT}$  and  $V_{CCIO}$ .

| Table 5–2. Recommended Operating Conditions |                                                     |                              |              |                     |      |

|---------------------------------------------|-----------------------------------------------------|------------------------------|--------------|---------------------|------|

| Symbol                                      | Parameter                                           | Conditions                   | Minimum      | Maximum             | Unit |

| V <sub>CCINT</sub>                          | Supply voltage for internal logic and input buffers | (1)                          | 1.15         | 1.25                | V    |

| V <sub>CCIO</sub> (2)                       | Supply voltage for output buffers, 3.3-V operation  | (1)                          | 3.135 (3.00) | 3.465 (3.60)<br>(3) | V    |

|                                             | Supply voltage for output buffers, 2.5-V operation  | (1)                          | 2.375        | 2.625               | V    |

|                                             | Supply voltage for output buffers, 1.8-V operation  | (1)                          | 1.71         | 1.89                | V    |

|                                             | Supply voltage for output buffers, 1.5-V operation  | (1)                          | 1.425        | 1.575               | V    |

| T <sub>J</sub>                              | Operating junction                                  | For commercial use           | 0            | 85                  | °C   |

|                                             | temperature                                         | For industrial use           | -40          | 100                 | °C   |

|                                             |                                                     | For extended temperature use | -40          | 125                 | °C   |

|                                             |                                                     | For automotive use           | -40          | 125                 | °C   |

#### Notes to Table 5-2:

- (1) The  $V_{CC}$  must rise monotonically. The maximum  $V_{CC}$  (both  $V_{CCIO}$  and  $V_{CCINT}$ ) rise time is 100 ms for non-A devices and 2 ms for A devices.

- (2) The V<sub>CCIO</sub> range given here spans the lowest and highest operating voltages of all supported I/O standards. The recommended V<sub>CCIO</sub> range specific to each of the single-ended I/O standards is given in Table 5–6, and those specific to the differential standards is given in Table 5–8.

- (3) The minimum and maximum values of 3.0 V and 3.6 V, respectively, for V<sub>CCIO</sub> only applies to the PCI and PCI-X I/O standards. Refer to Table 5–6 for the voltage range of other I/O standards.

Table 5–19. M4K Block Internal Timing Microparameters (Part 2 of 3) -6 Speed Grade (1) -7 Speed Grade (2) -8 Speed Grade (3) Parameter Unit Min Max Min Max Min Max TM4KBEH 234 267 267 ps 250 267 ps TM4KDATAASU 35 46 46 ps 40 46 ps TM4KDATAAH 234 267 267 ps 250 267 ps TM4KADDRASU 35 46 46 ps 40 46 ps TM4KADDRAH 234 267 267 ps 250 267 ps TM4KDATABSU 35 46 46 ps 40 46 ps TM4KDATABH 234 267 267 ps 250 267 ps TM4KRADDRBSU 46 35 46 ps 40 46 ps TM4KRADDRBH 234 267 267 ps 250 267 ps TM4KDATACO1 724 445 826 445 930 466 ps 466 466 ps 2345 TM4KDATACO2 3680 2234 4157 2234 4636 ps 2345 2345 ps TM4KCLKH 1923 2769 2769 ps 2307 2769 ps ps TM4KCLKL 1923 2769 2769 2307 2769 ps

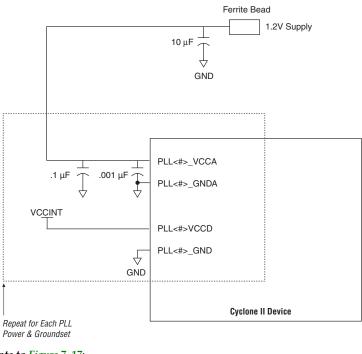

Figure 7–17. PLL Power Schematic for Cyclone II PLLs

Note to Figure 7–17:

(1) Applies to PLLs 1 through 4.

### **VCCD & GND**

The digital power and ground pins are labeled VCCD\_ PLL</br/>

PLL (PLL number) and GND\_PLL</br/>

PLL (PLL number). The VCCD pin supplies the power for the digital circuitry in the PLL. Connect these VCCD pins to the quietest digital supply on the board. In most systems, this is the digital 1.2-V supply supplied to the device's  $V_{CCINT}$  pins. Connect the VCCD pins to a power supply even if you do not use the PLL. When connecting the  $V_{CCD}$  pins to  $V_{CCINT}$ , you do not need any filtering or isolation. You can connect the GND pins directly to the same ground plane as the device's digital ground. See Figure 7–17.

### Conclusion

Cyclone II device PLLs provide you with complete control of device clocks and system timing. These PLLs support clock multiplication/division, phase shift, and programmable duty cycle for your cost-sensitive clock synthesis applications.

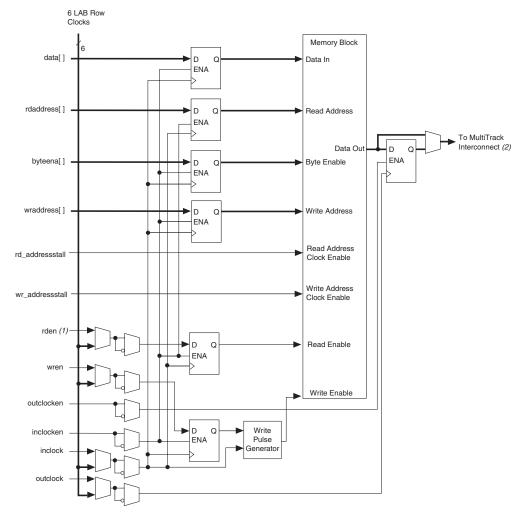

Figure 8–15. Cyclone II Input/Output Clock Mode in Simple Dual-Port Mode Notes (1), (2)

### Notes to Figure 8–15:

- (1) Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

- (2) See the Cyclone II Device Family Data Sheet in volume 1 of the Cyclone II Device Handbook for more information on the MultiTrack™ interconnect.

# Document Revision History

Table 9–4 shows the revision history for this document.

| Table 9–4. Document Revision History |                                                                                                                                                                                                                                          |                                                                                |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|

| Date &<br>Document<br>Version        | Changes Made                                                                                                                                                                                                                             | Summary of Changes                                                             |  |  |

| February 2007<br>v3.1                | <ul> <li>Added document revision history.</li> <li>Added handpara note in "Data &amp; Data Strobe Pins" section.</li> <li>Updated "DDR Output Registers" section.</li> </ul>                                                             | Elaboration of DDR2 and<br>QDRII interfaces supported<br>by I/O bank included. |  |  |

| November<br>2005, v2.1               | <ul><li>Introduction</li><li>Updated Table 9–2.</li><li>Updated Figure 9–7.</li></ul>                                                                                                                                                    |                                                                                |  |  |

| July 2005, v2.0                      | Updated Table 9–2.                                                                                                                                                                                                                       |                                                                                |  |  |

| November 2004, v1.1                  | <ul> <li>Moved the "External Memory Interface Standards" section to follow the "Introduction" section.</li> <li>Updated the "Data &amp; Data Strobe Pins" section.</li> <li>Updated Figures 9–11, 9–12, 9–15, 9–16, and 9–17.</li> </ul> |                                                                                |  |  |

| June 2004, v1.0                      | Added document to the Cyclone II Device Handbook.                                                                                                                                                                                        |                                                                                |  |  |

Additionally, each Cyclone II I/O bank has its own VCCIO pins. Any single I/O bank can only support one  $V_{CCIO}$  setting from among 1.5, 1.8, 2.5 or 3.3 V. Although there can only be one  $V_{CCIO}$  voltage per I/O bank, Cyclone II devices permit additional input signaling capabilities, as shown in Table 10–4.

| Table 10–4. Acceptable Input Levels for LVTTL and LVCMOS |              |                             |          |              |  |

|----------------------------------------------------------|--------------|-----------------------------|----------|--------------|--|

| Bank V <sub>ccio</sub> (V)                               |              | Acceptable Input Levels (V) |          |              |  |

| Dalik VCCIO (V)                                          | 3.3          | 2.5                         | 1.8      | 1.5          |  |

| 3.3                                                      | <b>✓</b>     | <b>√</b> (1)                |          |              |  |

| 2.5                                                      | <b>✓</b>     | <b>✓</b>                    |          |              |  |

| 1.8                                                      | <b>√</b> (2) | <b>√</b> (2)                | ✓        | <b>√</b> (1) |  |

| 1.5                                                      | <b>√</b> (2) | <b>√</b> (2)                | <b>✓</b> | <b>✓</b>     |  |

#### Notes to Table 10-4:

- (1) Because the input level does not drive to the rail, the input buffer does not completely shut off, and the I/O current is slightly higher than the default value.

- (2) These input values overdrive the input buffer, so the pin leakage current is slightly higher than the default value. To drive inputs higher than V<sub>CCIO</sub> but less than 4.0 V, disable the PCI clamping diode and turn on **Allow voltage overdrive for LVTTL/LVCMOS input pins** in Settings > Device > Device and Pin Options > Pin Placement tab. This setting allows input pins with LVTTL or LVCMOS I/O standards to be placed by the Quartus II software in an I/O bank with a lower V<sub>CCIO</sub> voltage than the voltage specified by the pins.

Any number of supported single-ended or differential standards can be simultaneously supported in a single I/O bank as long as they use compatible  $\rm V_{CCIO}$  levels for input and output pins. For example, an I/O bank with a 2.5-V  $\rm V_{CCIO}$  setting can support 2.5-V LVTTL inputs and outputs, 2.5-V LVDS-compatible inputs and outputs, and 3.3-V LVCMOS inputs only.

Voltage-referenced standards can be supported in an I/O bank using any number of single-ended or differential standards as long as they use the same  $V_{REF}$  and a compatible  $V_{CCIO}$  value. For example, if you choose to implement both SSTL-2 and SSTL-18 in your Cyclone II device, I/O pins using these standards—because they require different  $V_{REF}$  values—must be in different banks from each other. However, the same I/O bank can support SSTL-2 and 2.5-V LVCMOS with the  $V_{CCIO}$  set to 2.5 V and the  $V_{REF}$  set to 1.25 V.

Refer to "Pad Placement and DC Guidelines" on page 10–27 for more information.

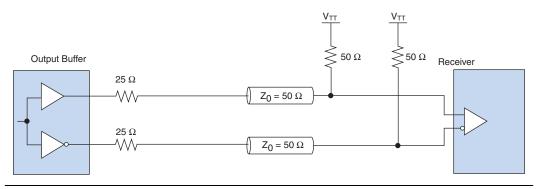

Figure 11-12. Differential SSTL Class I Interface

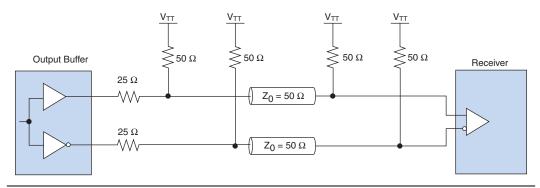

Figure 11–13. Differential SSTL Class II Interface

# **Differential HSTL Support in Cyclone II Devices**

The differential HSTL AC and DC specifications are the same as the HSTL single-ended specifications. The differential HSTL I/O standard is available on the GCLK pins only, treating differential inputs as two single-ended HSTL, and only decoding one of them. The differential HSTL output I/O standard is only supported at the PLLCLKOUT pins using two single-ended HSTL output buffers with the second output programmed as inverted. The standard requires two differential inputs with an external termination voltage ( $V_{\rm TT}$ ) of  $0.5 \times V_{\rm CCIO}$  to which termination resistors are connected.

For the HSTL signaling characteristics, see the *DC Characteristics & Timing Specifications* chapter and the *Selectable I/O Standards in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

# Document Revision History

Table 11–6 shows the revision history for this document.

| Table 11–6. Document Revision History |                                                                                                                                                                                                                                                                                                                   |                                                                                                                                           |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date &<br>Document<br>Version         | Changes Made                                                                                                                                                                                                                                                                                                      | Summary of Changes                                                                                                                        |  |  |

| February 2007<br>v2.2                 | <ul> <li>Added document revision history.</li> <li>Added Note (1) to Table 11-1.</li> <li>Updated Figure 11-5 and added Note (1)</li> <li>Added Note (1) to Table 11-2.</li> <li>Updated Figure 11-6 and added Note (1)</li> <li>Added Note (1) to Table 11-3.</li> <li>Added Note (1) to Figure 11-9.</li> </ul> | Added information stating<br>LVDS/RSDS/mini-LVDS<br>I/O standards<br>specifications apply at the<br>external resistors network<br>output. |  |  |

| November 2005<br>v2.1                 | <ul> <li>Updated Table 11–2.</li> <li>Updated Figures 11–7 through 11–9.</li> <li>Added Resistor Network Solution for RSDS.</li> <li>Updated note for mini-LVDS Resistor Network table.</li> </ul>                                                                                                                |                                                                                                                                           |  |  |

| July 2005 v2.0                        | <ul> <li>Updated "I/O Standards Support" section.</li> <li>Updated Tables 11–1 through 11–3.</li> </ul>                                                                                                                                                                                                           |                                                                                                                                           |  |  |

| November 2004<br>v1.1                 | <ul> <li>Updated Table 11–1.</li> <li>Updated Figures 11–4, 11–5, 11–7, and 11–9.</li> </ul>                                                                                                                                                                                                                      |                                                                                                                                           |  |  |

| June 2004, v1.0                       | Added document to the Cyclone II Device Handbook.                                                                                                                                                                                                                                                                 |                                                                                                                                           |  |  |

See the *Cyclone II Memory Blocks* chapter in Volume 1 of the *Cyclone II Device Handbook* for more information on Cyclone II M4K memory blocks.

Refer to AN 306: Techniques for Implementing Multipliers in FPGA Devices for more information on soft multipliers.

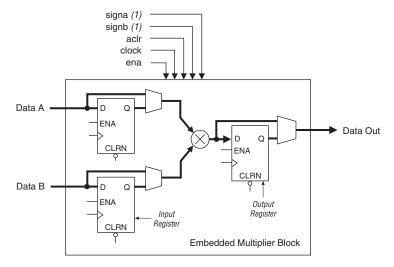

# **Architecture**

Each embedded multiplier consists of the following elements:

- Multiplier stage

- Input and output registers

- Input and output interfaces

Figure 12–2 shows the multiplier block architecture.

Figure 12-2. Multiplier Block Architecture

*Note to Figure 12–2:*

If necessary, you can send these signals through one register to match the data signal path.

# **Input Registers**

You can send each multiplier input signal into an input register or directly into the multiplier in 9- or 18-bit sections depending on the operational mode of the multiplier. You can send each multiplier input signal through a register independently of each other (e.g., you can send the multiplier's

# Software Support

Altera provides two methods for implementing multipliers in your design using embedded multiplier resources: instantiation and inference. Both methods use the following three Quartus II megafunctions:

- lpm mult

- altmult add

- altmult accum

You can instantiate the megafunctions in the Quartus II software to use the embedded multipliers. You can use the <code>lpm\_mult</code> and <code>altmult\_add</code> megafunctions to implement multipliers. Additionally, you can use the <code>altmult\_add</code> megafunctions to implement multiplieradders where the embedded multiplier is used to implement the multiply function and the adder function is implemented in LEs. The <code>altmult\_accum</code> megafunction implements multiply accumulate functions where the embedded multiplier implements the multiplier and the accumulator function is implemented in LEs.

See Quartus II On-Line Help for instructions on using the megafunctions and the MegaWizard Plug-In Manager.

For information on our complete DSP Design and Intellectual Property offerings, see www.Altera.com.

You can also infer the megafunctions by creating an HDL design and synthesize it using Quartus II integrated synthesis or a third-party synthesis tool that recognizes and infers the appropriate multiplier megafunction. Using either method, the Quartus II software maps the multiplier functionality to the embedded multipliers during compilation.

See the Synthesis section in Volume 1 of the *Quartus II Handbook* for more information.

# Conclusion

The Cyclone II device embedded multipliers are optimized to support multiplier-intensive DSP applications such as FIR filters, FFT functions and encoders. These embedded multipliers can be configured to implement multipliers of various bit widths up to 18-bits to suit a particular application resulting in efficient resource utilization and improved performance and data throughput. The Quartus II software, together with the LeonardoSpectrum and Synplify software provide a complete and easy-to-use flow for implementing multiplier functions using embedded multipliers.

Section VI-2 Altera Corporation

# Configuration File Format

Table 13–3 shows the approximate uncompressed configuration file sizes for Cyclone II devices. To calculate the amount of storage space required for multiple device configurations, add the file size of each device together.

| Table 13–3. Cyclone II Raw Binary File (.rbf) Sizes Note (1) |                  |                   |  |

|--------------------------------------------------------------|------------------|-------------------|--|

| Device                                                       | Data Size (Bits) | Data Size (Bytes) |  |

| EP2C5                                                        | 1,265,792        | 152,998           |  |

| EP2C8                                                        | 1,983,536        | 247,974           |  |

| EP2C15                                                       | 3,892,496        | 486,562           |  |

| EP2C20                                                       | 3,892,496        | 486,562           |  |

| EP2C35                                                       | 6,858,656        | 857,332           |  |

| EP2C50                                                       | 9,963,392        | 1,245,424         |  |

| EP2C70                                                       | 14,319,216       | 1,789,902         |  |

*Note to Table 13–3:*

These values are preliminary.

Use the data in Table 13–3 only to estimate the file size before design compilation. Different configuration file formats, such as a Hexadecimal (.hex) or Tabular Text File (.ttf) format, have different file sizes. However, for any specific version of the Quartus® II software, any design targeted for the same device has the same uncompressed configuration file size. If compression is used, the file size can vary after each compilation since the compression ratio is dependent on the design.

# Configuration Data Compression

Cyclone II devices support configuration data decompression, which saves configuration memory space and time. This feature allows you to store compressed configuration data in configuration devices or other memory and transmit this compressed bitstream to Cyclone II devices. During configuration, the Cyclone II device decompresses the bitstream in real time and programs its SRAM cells.

Preliminary data indicates that compression reduces configuration bitstream size by 35 to 55%.

Cyclone II devices support decompression in the AS and PS configuration schemes. Decompression is not supported in JTAG-based configuration.

Cyclone II devices offer an optional INIT\_DONE pin which signals the end of initialization and the start of user mode with a low-to-high transition. The Enable INIT\_DONE output option is available in the Quartus II software from the General tab of the Device & Pin Options window. If you use the INIT\_DONE pin, an external 10-kΩ pull-up resistor is required to pull the signal high when nCONFIG is low and during the beginning of configuration. Once the optional bit to enable INIT\_DONE is programmed into the device (during the first frame of configuration data), the INIT\_DONE pin goes low. When initialization is complete, the INIT\_DONE pin is released and pulled high. This low-to-high transition signals that the FPGA has entered user mode. If you do not use the INIT\_DONE pin, the initialization period is complete after CONF\_DONE goes high and 299 clock cycles are sent to the CLKUSR pin or after the time t<sub>CF2UM</sub> (see Table 13–8) if the Cyclone II device uses the internal oscillator.

#### User Mode

When initialization is complete, the FPGA enters user mode. In user mode, the user I/O pins no longer have weak pull-up resistors and function as assigned in your design.

When the Cyclone II device is in user mode, you can initiate reconfiguration by pulling the <code>nCONFIG</code> signal low. The <code>nCONFIG</code> signal should be low for at least 2  $\mu$ s. When <code>nCONFIG</code> is pulled low, the Cyclone II device is reset and enters the reset stage. The Cyclone II device also pulls <code>nSTATUS</code> and <code>CONF\_DONE</code> low and all I/O pins are tri-stated. Once <code>nCONFIG</code> returns to a logic high level and <code>nSTATUS</code> is released by the Cyclone II device, reconfiguration begins.

### Error During Configuration

If an error occurs during configuration, the Cyclone II device drives the nSTATUS signal low to indicate a data frame error, and the CONF\_DONE signal stays low. If you enable the **Auto-restart configuration after error** option in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box, the Cyclone II device resets the serial configuration device by pulsing nCSO, releases nSTATUS after a reset time-out period (about 40  $\mu$ s), and retries configuration. If the **Auto-restart configuration after error** option is turned off, the external system must monitor nSTATUS for errors and then pull nCONFIG low for at least 2  $\mu$ s to restart configuration.

If you use the optional CLKUSR pin and the nCONFIG pin is pulled low to restart configuration during device initialization, ensure CLKUSR continues to toggle during the time nSTATUS is low (a maximum of 40 µs).

For more information on configuration issues, see the *Debugging Configuration Problems* chapter of the *Configuration Handbook* and the FPGA Configuration Troubleshooter on the Altera web site (www.altera.com).

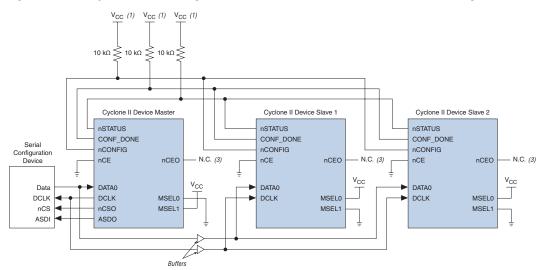

### **Multiple Device AS Configuration**

You can configure multiple Cyclone II devices using a single serial configuration device. You can cascade multiple Cyclone II devices using the chip-enable (nCE) and chip-enable-out (nCEO) pins. Connect the nCE pin of the first device in the chain to ground and connect the nCEO pin to the nCE pin of the next device in the chain. Use an external 10-k $\Omega$ pull-up resistor to pull the nCEO signal high to its  $V_{CCIO}$  level to help the internal weak pull-up resistor. When the first device captures all of its configuration data from the bitstream, it transitions its nCEO pin low, initiating the configuration of the next device in the chain. You can leave the nCEO pin of the last device unconnected or use it as a user I/O pin after configuration if the last device in chain is a Cyclone II device.

The Quartus II software sets the Cyclone II device <code>nCEO</code> pin as an output pin driving to ground by default. If the device is in a chain, and the <code>nCEO</code> pin is connected to the next device's <code>nCE</code> pin, you must make sure that the <code>nCEO</code> pin is not used as a user I/O pin after configuration. The software setting is in the <code>Dual-Purpose Pins</code> tab of the <code>Device & Pin Options</code> dialog box in Quartus II software.

The first Cyclone II device in the chain is the configuration master and controls the configuration of the entire chain. Select the AS configuration scheme for the first Cyclone II device and the PS configuration scheme for the remaining Cyclone II devices (configuration slaves). Any other Altera® device that supports PS configuration can also be part of the chain as a configuration slave. In a multiple device chain, the nCONFIG, nSTATUS, CONF\_DONE, DCLK, and DATAO pins of each device in the chain are connected (see Figure 13–4). Figure 13–4 shows the pin connections for this setup.

### Single SOF

The second method configures both the master and slave Cyclone II devices with the same SOF. The serial configuration device stores one copy of the SOF file. This setup is shown in Figure 13–6 where the master is setup in AS mode, and the slave devices are setup in PS mode (MSEL=01). You could setup one or more slave devices in the chain and all the slave devices are setup in the same way as shown in Figure 13–6.

Figure 13-6. Multiple Device AS Configuration When FPGAS Receive the Same Data with a Single SOF

#### *Notes to Figure 13–6:*

- Connect the pull-up resistors to a 3.3-V supply.

- (2) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed another device's nCE pin.

In this setup, all the Cyclone II devices in the chain are connected for concurrent configuration. This can reduce the AS configuration time because all the Cyclone II devices are configured in one configuration cycle. Connect the nCE input pins of all the Cyclone II devices to ground. You can either leave the nCEO output pins on all the Cyclone II devices unconnected or use the nCEO output pins as normal user I/O pins. The DATA and DCLK pins are connected in parallel to all the Cyclone II devices.

# 15. Package Information for Cyclone II Devices

CII51015-2.3

# Introduction

This chapter provides package information for Altera® Cyclone® II devices, including:

- Device and package cross reference

- Thermal resistance values

- Package outlines

Table 15–1 shows Cyclone II device package options.

| Table 15–1. Cyclone II Device Package Options |                                               |      |  |

|-----------------------------------------------|-----------------------------------------------|------|--|

| Device                                        | Package                                       | Pins |  |

| EP2C5                                         | Plastic Thin Quad Flat Pack (TQFP) – Wirebond | 144  |  |

|                                               | Plastic Quad Flat Pack (PQFP) - Wirebond      | 208  |  |

|                                               | Low profile FineLine BGA® – Wirebond          | 256  |  |

| EP2C8                                         | TQFP – Wirebond                               | 144  |  |

|                                               | PQFP – Wirebond                               | 208  |  |

|                                               | Low profile FineLine BGA – Wirebond           | 256  |  |

| EP2C15                                        | Low profile FineLine BGA, Option 2 – Wirebond | 256  |  |

|                                               | FineLine BGA, Option 3– Wirebond              | 484  |  |

| EP2C20                                        | PQFP – Wirebond                               | 240  |  |

|                                               | Low profile FineLine BGA, Option 2 – Wirebond | 256  |  |

|                                               | FineLine BGA, Option 3– Wirebond              | 484  |  |

| EP2C35                                        | FineLine BGA, Option 3 – Wirebond             | 484  |  |

|                                               | Ultra FineLine BGA – Wirebond                 | 484  |  |

|                                               | FineLine BGA, Option 3 – Wirebond             | 672  |  |

| EP2C50                                        | FineLine BGA, Option 3 – Wirebond             | 484  |  |

|                                               | Ultra FineLine BGA – Wirebond                 | 484  |  |

|                                               | FineLine BGA, Option 3 – Wirebond             | 672  |  |

| EP2C70                                        | FineLine BGA, Option 3 – Wirebond             | 672  |  |

|                                               | FineLine BGA – Wirebond                       | 896  |  |

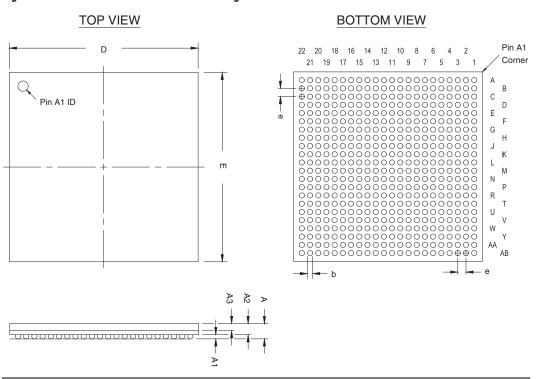

Figure 15–6 shows a 484-pin Ultra FineLine BGA package outline.

Figure 15-6. 484-Pin Ultra FineLine BGA Package Outline