Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 3158                                                     |

| Number of Logic Elements/Cells | 50528                                                    |

| Total RAM Bits                 | 594432                                                   |

| Number of I/O                  | 294                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 484-FBGA                                                 |

| Supplier Device Package        | 484-UBGA (19x19)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c50u484c6n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ]   | nternal Timing                                        | 5-18 |

|-----|-------------------------------------------------------|------|

| (   | Cyclone II Clock Timing Parameters                    | 5-23 |

|     | Clock Network Skew Adders                             |      |

| ]   | OE Programmable Delay                                 | 5-30 |

|     | Default Capacitive Loading of Different I/O Standards |      |

|     | /O Delays                                             |      |

| l   | Maximum Input and Output Clock Rate                   | 5-46 |

|     | High Speed I/O Timing Specifications                  |      |

|     | External Memory Interface Specifications              |      |

| J   | TAG Timing Specifications                             | 5-64 |

| j   | PLL Timing Specifications                             | 5-66 |

|     | y Cycle Distortion                                    |      |

|     | DCD Measurement Techniques                            |      |

|     | erenced Documents                                     |      |

| Doc | cument Revision History                               | 5-74 |

|     |                                                       |      |

## Chapter 6. Reference & Ordering Information

| Software                  | <b>)</b> –1 |

|---------------------------|-------------|

| Device Pin-Outs           |             |

| Ordering Information      | -1          |

| Document Revision History |             |

|                           | -           |

# Section II. Clock Management

| Revision History |  | 6– | -1 |

|------------------|--|----|----|

|------------------|--|----|----|

## Chapter 7. PLLs in Cyclone II Devices

| Introduction                                 | 7–1  |

|----------------------------------------------|------|

| Cyclone II PLL Hardware Overview             | 7–2  |

| PLL Reference Clock Generation               | 7–6  |

| Clock Feedback Modes                         | 7–10 |

| Normal Mode                                  | 7–10 |

| Zero Delay Buffer Mode                       | 7–11 |

| No Compensation Mode                         | 7–12 |

| Source-Synchronous Mode                      |      |

| Hardware Features                            |      |

| Clock Multiplication & Division              | 7–14 |

| Programmable Duty Cycle                      |      |

| Phase-Shifting Implementation                |      |

| Control Signals                              | 7–17 |

| Manual Clock Switchover                      |      |

| Clocking                                     | 7–21 |

| Global Clock Network                         | 7–21 |

| Clock Control Block                          | 7–24 |

| Global Clock Network Clock Source Generation | 7–26 |

| Global Clock Network Power Down              | 7–28 |

# Referenced Documents

This chapter references the following documents:

Hot Socketing & Power-On Reset chapter in Cyclone II Device Handbook

Automotive-Grade Device Handbook

# Document Revision History

Table 1–5 shows the revision history for this document.

| Table 1–5. Doci               | ument Revision History                                                                                                                                           |                                                                                                                                              |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Date &<br>Document<br>Version | Changes Made                                                                                                                                                     | Summary of Changes                                                                                                                           |

| February 2008<br>v3.2         | <ul> <li>Added "Referenced Documents".</li> <li>Updated "Features" section and Table 1–1, Table 1–2,<br/>and Table 1–4 with information about EP2C5A.</li> </ul> | _                                                                                                                                            |

| February 2007<br>v3.1         | <ul> <li>Added document revision history.</li> <li>Added new <i>Note (2)</i> to Table 1–2.</li> </ul>                                                            | Note to explain difference<br>between I/O pin count<br>information provided in<br>Table 1–2 and in the Quartus II<br>software documentation. |

| November 2005<br>v2.1         | <ul><li>Updated Introduction and Features.</li><li>Updated Table 1–3.</li></ul>                                                                                  | —                                                                                                                                            |

| July 2005 v2.0                | <ul> <li>Updated technical content throughout.</li> <li>Updated Table 1–2.</li> <li>Added Tables 1–3 and 1–4.</li> </ul>                                         | _                                                                                                                                            |

| November 2004<br>v1.1         | <ul> <li>Updated Table 1–2.</li> <li>Updated bullet list in the "Features" section.</li> </ul>                                                                   | —                                                                                                                                            |

| June 2004 v1.0                | Added document to the Cyclone II Device Handbook.                                                                                                                | —                                                                                                                                            |

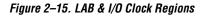

• For more information on the global clock network and the clock control block, see the *PLLs in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

## **Memory Modes**

Table 2–7 summarizes the different memory modes supported by the M4K memory blocks.

| Table 2–7. M4K Memory M           | odes                                                                                                                                                                                                     |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Mode                       | Description                                                                                                                                                                                              |

| Single-port memory                | M4K blocks support single-port mode, used when<br>simultaneous reads and writes are not required.<br>Single-port memory supports non-simultaneous<br>reads and writes.                                   |

| Simple dual-port memory           | Simple dual-port memory supports a simultaneous read and write.                                                                                                                                          |

| Simple dual-port with mixed width | Simple dual-port memory mode with different read and write port widths.                                                                                                                                  |

| True dual-port memory             | True dual-port mode supports any combination of<br>two-port operations: two reads, two writes, or one<br>read and one write at two different clock<br>frequencies.                                       |

| True dual-port with mixed width   | True dual-port mode with different read and write port widths.                                                                                                                                           |

| Embedded shift register           | M4K memory blocks are used to implement shift<br>registers. Data is written into each address<br>location at the falling edge of the clock and read<br>from the address at the rising edge of the clock. |

| ROM                               | The M4K memory blocks support ROM mode. A MIF initializes the ROM contents of these blocks.                                                                                                              |

| FIFO buffers                      | A single clock or dual clock FIFO may be<br>implemented in the M4K blocks. Simultaneous<br>read and write from an empty FIFO buffer is not<br>supported.                                                 |

P

Embedded Memory can be inferred in your HDL code or directly instantiated in the Quartus II software using the MegaWizard<sup>®</sup> Plug-in Manager Memory Compiler feature.

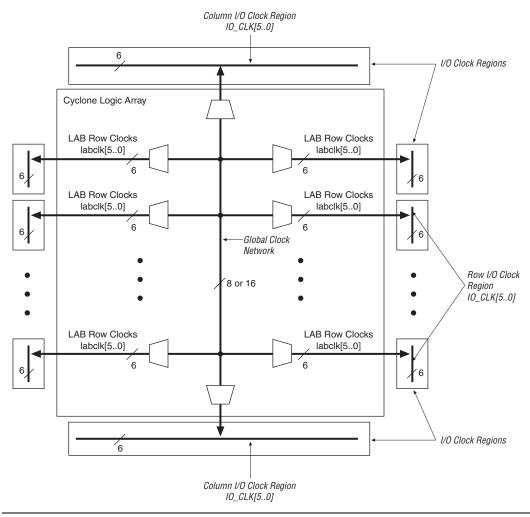

Figure 2–17. M4K RAM Block LAB Row Interface

For more information on Cyclone II embedded memory, see the *Cyclone II Memory Blocks* chapter in Volume 1 of the *Cyclone II Device Handbook*.

# Embedded Multipliers

Cyclone II devices have embedded multiplier blocks optimized for multiplier-intensive digital signal processing (DSP) functions, such as finite impulse response (FIR) filters, fast Fourier transform (FFT) functions, and discrete cosine transform (DCT) functions. You can use the embedded multiplier in one of two basic operational modes, depending on the application needs:

- One 18-bit multiplier

- Up to two independent 9-bit multipliers

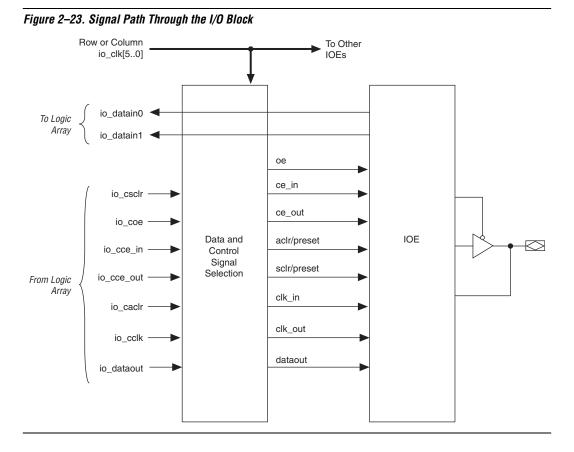

The pin's datain signals can drive the logic array. The logic array drives the control and data signals, providing a flexible routing resource. The row or column IOE clocks, io\_clk[5..0], provide a dedicated routing resource for low-skew, high-speed clocks. The global clock network generates the IOE clocks that feed the row or column I/O regions (see "Global Clock Network & Phase-Locked Loops" on page 2–16). Figure 2–23 illustrates the signal paths through the I/O block.

Each IOE contains its own control signal selection for the following control signals: oe, ce\_in, ce\_out, aclr/preset, sclr/preset, clk\_in, and clk\_out. Figure 2–24 illustrates the control signal selection.

## Advanced I/O Standard Support

Table 2–17 shows the I/O standards supported by Cyclone II devices and which I/O pins support them.

| 1/0 Otendend                   | Turne              | V <sub>ccio</sub> | Level  |             | & Bottom<br>) Pins |              | Side I/O P              | ins              |

|--------------------------------|--------------------|-------------------|--------|-------------|--------------------|--------------|-------------------------|------------------|

| I/O Standard                   | Туре               | Input             | Output | CLK,<br>DQS | User I/O<br>Pins   | CLK,<br>DQS  | PLL_OUT                 | User I/O<br>Pins |

| 3.3-V LVTTL and LVCMOS (1)     | Single ended       | 3.3 V/<br>2.5 V   | 3.3 V  | ~           | ~                  | ~            | $\checkmark$            | $\checkmark$     |

| 2.5-V LVTTL and LVCMOS         | Single ended       | 3.3 V/<br>2.5 V   | 2.5 V  | ~           | ~                  | ~            | ~                       | ~                |

| 1.8-V LVTTL and LVCMOS         | Single ended       | 1.8 V/<br>1.5 V   | 1.8 V  | ~           | ~                  | ~            | ~                       | ~                |

| 1.5-V LVCMOS                   | Single ended       | 1.8 V/<br>1.5 V   | 1.5 V  | ~           | ~                  | ~            | $\checkmark$            | ~                |

| SSTL-2 class I                 | Voltage referenced | 2.5 V             | 2.5 V  | ~           | ~                  | ~            | $\checkmark$            | ~                |

| SSTL-2 class II                | Voltage referenced | 2.5 V             | 2.5 V  | ~           | ~                  | ~            | ~                       | ~                |

| SSTL-18 class I                | Voltage referenced | 1.8 V             | 1.8 V  | ~           | ~                  | ~            | ~                       | ~                |

| SSTL-18 class II               | Voltage referenced | 1.8 V             | 1.8 V  | ~           | ~                  | (2)          | (2)                     | (2)              |

| HSTL-18 class I                | Voltage referenced | 1.8 V             | 1.8 V  | ~           | ~                  | ~            | ~                       | ~                |

| HSTL-18 class II               | Voltage referenced | 1.8 V             | 1.8 V  | ~           | ~                  | (2)          | (2)                     | (2)              |

| HSTL-15 class I                | Voltage referenced | 1.5 V             | 1.5 V  | ~           | ~                  | ~            | ~                       | ~                |

| HSTL-15 class II               | Voltage referenced | 1.5 V             | 1.5 V  | ~           | ~                  | (2)          | (2)                     | (2)              |

| PCI and PCI-X (1) (3)          | Single ended       | 3.3 V             | 3.3 V  |             |                    | $\checkmark$ | $\checkmark$            | ~                |

| Differential SSTL-2 class I or | Pseudo             | (5)               | 2.5 V  |             |                    |              | $\checkmark$            |                  |

| class II                       | differential (4)   | 2.5 V             | (5)    | ✓<br>(6)    |                    | ✓<br>(6)     |                         |                  |

| Differential SSTL-18 class I   | Pseudo             | (5)               | 1.8 V  |             |                    |              | <ul> <li>(7)</li> </ul> |                  |

| or class II                    | differential (4)   | 1.8 V             | (5)    | ✓<br>(6)    |                    | ✓<br>(6)     |                         |                  |

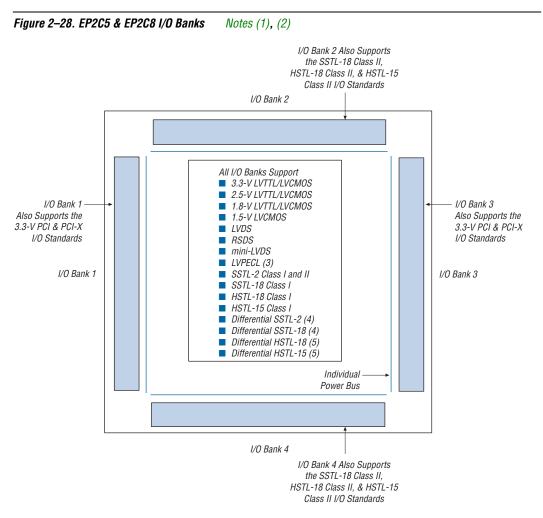

#### Notes to Figure 2–28:

- (1) This is a top view of the silicon die.

- (2) This is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (5) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

| Table 2–20            | ). Cyclone II | MultiVolt I/ | O Support               | (Part 2 of 2) | Note (1)                |        |        |       |

|-----------------------|---------------|--------------|-------------------------|---------------|-------------------------|--------|--------|-------|

| v w                   |               | Input        | Signal                  |               |                         | Output | Signal |       |

| V <sub>CCIO</sub> (V) | 1.5 V         | 1.8 V        | 2.5 V                   | 3.3 V         | 1.5 V                   | 1.8 V  | 2.5 V  | 3.3 V |

| 3.3                   |               |              | <ul><li>✓ (4)</li></ul> | ~             | <ul> <li>(6)</li> </ul> | 🗸 (6)  | 🗸 (6)  | ~     |

#### Notes to Table 2–20:

(1) The PCI clamping diode must be disabled to drive an input with voltages higher than V<sub>CCIO</sub>.

(2) These input values overdrive the input buffer, so the pin leakage current is slightly higher than the default value. To drive inputs higher than V<sub>CCIO</sub> but less than 4.0 V, disable the PCI clamping diode and turn on Allow voltage overdrive for LVTTL/LVCMOS input pins option in Device setting option in the Quartus II software.

(3) When V<sub>CCIO</sub> = 1.8-V, a Cyclone II device can drive a 1.5-V device with 1.8-V tolerant inputs.

(4) When  $V_{CCIO} = 3.3$ -V and a 2.5-V input signal feeds an input pin or when  $V_{CCIO} = 1.8$ -V and a 1.5-V input signal feeds an input pin, the  $V_{CCIO}$  supply current will be slightly larger than expected. The reason for this increase is that the input signal level does not drive to the  $V_{CCIO}$  rail, which causes the input buffer to not completely shut off.

(5) When V<sub>CCIO</sub> = 2.5-V, a Cyclone II device can drive a 1.5-V or 1.8-V device with 2.5-V tolerant inputs.

(6) When V<sub>CCIO</sub> = 3.3-V, a Cyclone II device can drive a 1.5-V, 1.8-V, or 2.5-V device with 3.3-V tolerant inputs.

the power supply can provide current to the device's  $V_{CC}$  and ground planes. This condition can lead to latch-up and cause a low-impedance path from  $V_{CC}$  to ground within the device. As a result, the device extends a large amount of current, possibly causing electrical damage.

Altera has ensured by design of the I/O buffers and hot-socketing circuitry, that Cyclone II devices are immune to latch-up during hot socketing.

# Hot-Socketing Feature Implementation in Cyclone II Devices

The hot-socketing feature turns off the output buffer during power up (either V<sub>CCINT</sub> or V<sub>CCIO</sub> supplies) or power down. The hot-socket circuit generates an internal HOTSCKT signal when either V<sub>CCINT</sub> or V<sub>CCIO</sub> is below the threshold voltage. Designs cannot use the HOTSCKT signal for other purposes. The HOTSCKT signal cuts off the output buffer to ensure that no DC current (except for weak pull-up leakage current) leaks through the pin. When V<sub>CC</sub> ramps up slowly, V<sub>CC</sub> is still relatively low even after the internal POR signal (not available to the FPGA fabric used by customer designs) is released and the configuration is finished. The CONF\_DONE, nCEO, and nSTATUS pins fail to respond, as the output buffer cannot drive out because the hot-socketing circuitry keeps the I/O pins tristated at this low V<sub>CC</sub> voltage. Therefore, the hot-socketing circuit has been removed on these configuration output or bidirectional pins to ensure that they are able to operate during configuration. These pins are expected to drive out during power-up and power-down sequences.

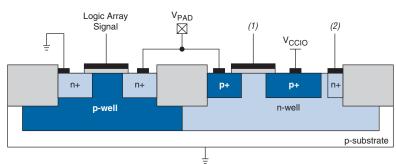

Each I/O pin has the circuitry shown in Figure 4–1.

#### Notes to Figure 4-2:

- (1) This is the logic array signal or the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

- (2) This is the larger of either the  $V_{CCIO}$  or  $V_{PAD}$  signal.

# Power-On Reset Circuitry

Cyclone II devices contain POR circuitry to keep the device in a reset state until the power supply voltage levels have stabilized during power-up. The POR circuit monitors the  $V_{CCINT}$  voltage levels and tri-states all user I/O pins until the  $V_{CC}$  reaches the recommended operating levels. In addition, the POR circuitry also monitors the  $V_{CCIO}$  level of the two I/O banks that contains configuration pins (I/O banks 1 and 3 for EP2C5 and EP2C8, I/O banks 2 and 6 for EP2C15A, EP2C20, EP2C35, EP2C50, and EP2C70) and tri-states all user I/O pins until the  $V_{CC}$  reaches the recommended operating levels.

After the Cyclone II device enters user mode, the POR circuit continues to monitor the  $V_{CCINT}$  voltage level so that a brown-out condition during user mode can be detected. If the  $V_{CCINT}$  voltage sags below the POR trip point during user mode, the POR circuit resets the device. If the  $V_{CCIO}$  voltage sags during user mode, the POR circuit does not reset the device.

### "Wake-up" Time for Cyclone II Devices

In some applications, it may be necessary for a device to wake up very quickly in order to begin operation. The Cyclone II device family offers the Fast-On feature to support fast wake-up time applications. Devices that support the Fast-On feature are designated with an "A" in the ordering code and have stricter power up requirements compared to non-A devices.

|              |                   |                  | Fast Co                   | rner            | -6             | -7                    | -7                    | -8             |      |

|--------------|-------------------|------------------|---------------------------|-----------------|----------------|-----------------------|-----------------------|----------------|------|

| I/O Standard | Drive<br>Strength | Parameter        | Industrial/<br>Automotive | Commer<br>-cial | Speed<br>Grade | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | Speed<br>Grade | Unit |

| LVTTL        | 4 mA              | t <sub>OP</sub>  | 1524                      | 1599            | 2903           | 3125                  | 3341                  | 3348           | ps   |

|              |                   | t <sub>DIP</sub> | 1656                      | 1738            | 3073           | 3319                  | 3567                  | 3567           | ps   |

|              | 8 mA              | t <sub>OP</sub>  | 1343                      | 1409            | 2670           | 2866                  | 3054                  | 3061           | ps   |

|              |                   | t <sub>DIP</sub> | 1475                      | 1548            | 2840           | 3060                  | 3280                  | 3280           | ps   |

|              | 12 mA             | t <sub>OP</sub>  | 1287                      | 1350            | 2547           | 2735                  | 2917                  | 2924           | ps   |

|              |                   | t <sub>DIP</sub> | 1419                      | 1489            | 2717           | 2929                  | 3143                  | 3143           | ps   |

|              | 16 mA             | t <sub>OP</sub>  | 1239                      | 1299            | 2478           | 2665                  | 2844                  | 2851           | ps   |

|              |                   | t <sub>DIP</sub> | 1371                      | 1438            | 2648           | 2859                  | 3070                  | 3070           | ps   |

|              | 20 mA             | t <sub>OP</sub>  | 1228                      | 1288            | 2456           | 2641                  | 2820                  | 2827           | ps   |

|              |                   | t <sub>DIP</sub> | 1360                      | 1427            | 2626           | 2835                  | 3046                  | 3046           | ps   |

|              | 24 mA             | t <sub>OP</sub>  | 1220                      | 1279            | 2452           | 2637                  | 2815                  | 2822           | ps   |

|              | (1)               | t <sub>DIP</sub> | 1352                      | 1418            | 2622           | 2831                  | 3041                  | 3041           | ps   |

| LVCMOS       | 4 mA              | t <sub>OP</sub>  | 1346                      | 1412            | 2509           | 2695                  | 2873                  | 2880           | ps   |

|              |                   | t <sub>DIP</sub> | 1478                      | 1551            | 2679           | 2889                  | 3099                  | 3099           | ps   |

|              | 8 mA              | t <sub>OP</sub>  | 1240                      | 1300            | 2473           | 2660                  | 2840                  | 2847           | ps   |

|              |                   | t <sub>DIP</sub> | 1372                      | 1439            | 2643           | 2854                  | 3066                  | 3066           | ps   |

|              | 12 mA             | t <sub>OP</sub>  | 1221                      | 1280            | 2428           | 2613                  | 2790                  | 2797           | ps   |

|              |                   | t <sub>DIP</sub> | 1353                      | 1419            | 2598           | 2807                  | 3016                  | 3016           | ps   |

|              | 16 mA             | t <sub>OP</sub>  | 1203                      | 1262            | 2403           | 2587                  | 2765                  | 2772           | ps   |

|              |                   | t <sub>DIP</sub> | 1335                      | 1401            | 2573           | 2781                  | 2991                  | 2991           | ps   |

|              | 20 mA             | t <sub>OP</sub>  | 1194                      | 1252            | 2378           | 2562                  | 2738                  | 2745           | ps   |

|              |                   | t <sub>DIP</sub> | 1326                      | 1391            | 2548           | 2756                  | 2964                  | 2964           | ps   |

|              | 24 mA             | t <sub>OP</sub>  | 1192                      | 1250            | 2382           | 2566                  | 2742                  | 2749           | ps   |

|              | (1)               | t <sub>DIP</sub> | 1324                      | 1389            | 2552           | 2760                  | 2968                  | 2968           | ps   |

| Table 10–3. Cycl | lone II 33-MHz PCI Support | (Part 2 of 2) |              |

|------------------|----------------------------|---------------|--------------|

| Davias           | Deskone                    | –6, –7 and –8 | Speed Grades |

| Device           | Package                    | 64 Bits       | 32 Bits      |

| EP2C20           | 240-pin PQFP               | —             | $\checkmark$ |

|                  | 256-pin FineLine BGA       | —             | $\checkmark$ |

|                  | 484-pin FineLine BGA       | $\checkmark$  | $\checkmark$ |

| EP2C35           | 484-pin FineLine BGA       | $\checkmark$  | $\checkmark$ |

|                  | 672-pin FineLine BGA       | $\checkmark$  | $\checkmark$ |

| EP2C50           | 484-pin FineLine BGA       | $\checkmark$  | $\checkmark$ |

|                  | 672-pin FineLine BGA       | $\checkmark$  | $\checkmark$ |

| EP2C70           | 672-pin FineLine BGA       | $\checkmark$  | $\checkmark$ |

|                  | 896-pin FineLine BGA       | $\checkmark$  | $\checkmark$ |

## 3.3-V PCI-X

The 3.3-V PCI-X I/O standard is formulated under PCI-X Local Bus Specification Revision 1.0 developed by the PCI SIG.

The PCI-X 1.0 standard is used for applications that interface to the PCI local bus. The standard enables the design of systems and devices that operate at clock speeds up to 133 MHz, or 1 gigabit per second (Gbps) for a 64-bit bus. The PCI-X 1.0 protocol enhancements enable devices to operate much more efficiently, providing more usable bandwidth at any clock frequency. By using the PCI-X 1.0 standard, devices can be designed to meet PCI-X 1.0 requirements and operate as conventional 33- and 66-MHz PCI devices when installed in those systems. This standard requires 3.3-V V<sub>CCIO</sub>. Cyclone II devices are fully compliant with the 3.3-V PCI-X Specification Revision 1.0a and meet the 133 MHz operating frequency and timing requirements. The 3.3-V PCI-X standard does not require input reference voltages or board terminations. Cyclone II devices support both input and output levels operation for left and right I/O banks.

## Easy-to-Use, Low-Cost PCI Express Solution

PCI Express is rapidly establishing itself as the successor to PCI, providing higher performance, increased flexibility, and scalability for next-generation systems without increasing costs, all while maintaining software compatibility with existing PCI applications. Now you can easily design high volume, low-cost PCI Express ×1 solutions today featuring:

## I/O Driver Impedance Matching (R<sub>S</sub>) and Series Termination (R<sub>S</sub>)

Cyclone II devices support driver impedance matching to the impedance of the transmission line, typically 25 or 50  $\Omega$  When used with the output drivers, on-chip termination (OCT) sets the output driver impedance to 25 or 50  $\Omega$ by choosing the driver strength. Once matching impedance is selected, driver current can not be changed. Table 10–7 provides a list of output standards that support impedance matching. All I/O banks and I/O pins support impedance matching and series termination. Dedicated configuration pins and JTAG pins do not support impedance matching or series termination.

| I/O Standard     | Target $R_{S}$ ( $\Omega$ ) |

|------------------|-----------------------------|

| 3.3-V LVTTL/CMOS | 25 (1)                      |

| 2.5-V LVTTL/CMOS | 50 (1)                      |

| 1.8-V LVTTL/CMOS | 50 (1)                      |

| SSTL-2 class I   | 50 (1)                      |

| SSTL-18 class I  | 50 (1)                      |

#### Note to Table 10–7:

(1) These RS values are nominal values. Actual impedance varies across process, voltage, and temperature conditions. Tolerance is specified in the DC Characteristics and Timing Specifications chapter in volume 1 of the Cyclone II Handbook.

# Pad Placement and DC Guidelines

This section provides pad placement guidelines for the programmable I/O standards supported by Cyclone II devices and includes essential information for designing systems using the devices' selectable I/O capabilities. This section also discusses the DC limitations and guidelines.

Quartus II software provides user controlled restriction relaxation options for some placement constraints. When a default restriction is relaxed by a user, the Quartus II fitter generates warnings.

For more information about how Quartus II software checks I/O restrictions, refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook*.

| Table 11–1. LVDS I/O Specifications (Part 2 of 2)     Note (1) |                                              |                        |     |     |      |       |

|----------------------------------------------------------------|----------------------------------------------|------------------------|-----|-----|------|-------|

| Symbol                                                         | Parameter                                    | Condition              | Min | Тур | Max  | Units |

| V <sub>ID</sub>                                                | Input differential voltage (single-ended)    |                        | 0.1 |     | 0.65 | V     |

| VICM                                                           | Input common mode voltage                    |                        | 0.1 |     | 2.0  | V     |

| $\Delta V_{OS}$                                                | Change in V <sub>OS</sub> between<br>H and L | R <sub>L</sub> = 100 Ω |     |     | 50   | mV    |

| RL                                                             | Receiver differential input resistor         |                        | 90  | 100 | 110  | Ω     |

Note to Table 11–1:

(1) The specifications apply at the resistor network output.

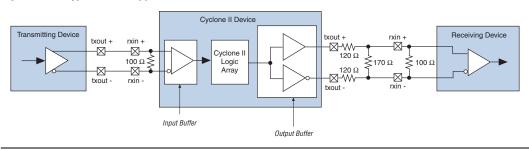

LVDS Receiver & Transmitter

Figure 11–3 shows a simple point-to-point LVDS application where the source of the data is an LVDS transmitter. These LVDS signals are typically transmitted over a pair of printed circuit board (PCB) traces, but a combination of a PCB trace, connectors, and cables is a common application setup.

### Figure 11–3. Typical LVDS Application

Figures 11–4 and 11–5 show the signaling levels for LVDS receiver inputs and transmitter outputs, respectively.

### Configuration Stage

When the nSTATUS pin transitions high, the configuration device's OE pin also transitions high and the configuration device clocks data out serially to the FPGA using its internal oscillator. The Cyclone II device receives configuration data on its DATA0 pin and the clock is received on the DCLK pin. Data is latched into the FPGA on the rising edge of DCLK.

After the FPGA has received all configuration data successfully, it releases the open-drain CONF\_DONE pin, which is pulled high by a pull-up resistor. Since the Cyclone II device's CONF\_DONE pin is tied to the configuration device's nCS pin, the configuration device is disabled when CONF\_DONE goes high. Enhanced configuration and EPC2 devices have an optional internal pull-up resistor on the nCS pin. You can turn this option on in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. If you do not use this internal pull-up resistor, you need to connect an external 10-k $\Omega$  pull-up resistor to the nCS and CONF\_DONE line. A low-to-high transition on CONF\_DONE indicates configuration is complete, and the device can begin initialization.

### Initialization Stage

In Cyclone II devices, the default initialization clock source is the Cyclone II internal oscillator (typically 10 MHz). Cyclone II devices can also use the optional CLKUSR pin. If your design uses the internal oscillator, the Cyclone II device supplies itself with enough clock cycles for proper initialization. The advantage of using the internal oscillator is you do not need to use another device or source to send additional clock cycles to the CLKUSR pin during the initialization stage. Additionally, you can use of the CLKUSR pin as a user I/O pin, which means you have an additional user I/O pin.

If you want to delay the initialization of the device, you can use the CLKUSR pin. Using the CLKUSR pin allows you to control when the Cyclone II device enters user mode. You can delay the Cyclone II devices from entering user mode for an indefinite amount of time. You can turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. Supplying a clock on CLKUSR does not affect the configuration process. After all configuration data is accepted and CONF\_DONE goes high, Cyclone II devices require 299 clock cycles to properly initialize and support a CLKUSR f<sub>MAX</sub> of 100 MHz.

An optional INIT\_DONE pin is available, which signals the end of initialization and the start of user mode with a low-to-high transition. The **Enable INIT\_DONE output** option is available in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. If you use the INIT\_DONE pin, an external 10-k $\Omega$ pull-up resistor pulls it high when

enables the programming software to program or verify the target device. Configuration data driven into the target device appears on the TDO pin one clock cycle later.

The Quartus II software verifies successful JTAG configuration upon completion. At the end of configuration, the software checks the CONF\_DONE pin through the JTAG port. When the Quartus II software generates a JAM file for a multiple device chain, it contains instructions so that all the devices in the chain are initialized at the same time. If CONF\_DONE is not high, the Quartus II software indicates that configuration has failed. If the CONF\_DONE pin transitions high, the software indicates that configuration was successful. After the configuration bitstream is transmitted serially via the JTAG TDI port, the TCK port is clocked an additional 299 cycles to perform Cyclone II device initialization.

The **Enable user-supplied start-up clock (CLKUSR)** option has no affect on the device initialization since this option is disabled in the SOF when configuring the FPGA in JTAG using the Quartus II programmer and download cable. Therefore, if you turn on the CLKUSR option, you do not need to provide a clock on CLKUSR when you are configuring the FPGA with the Quartus II programmer and a download cable.

Cyclone II devices have dedicated JTAG pins that always function as JTAG pins. You can perform JTAG testing on Cyclone II devices before, after, and during configuration. Cyclone II devices support the BYPASS, IDCODE and SAMPLE instructions during configuration without interruption. All other JTAG instructions may only be issued by first interrupting configuration and reprogramming I/O pins using the CONFIG\_IO instruction.

The CONFIG\_IO instruction allows I/O buffers to be configured via the JTAG port. The CONFIG\_IO instruction interrupts configuration. This instruction allows you to perform board-level testing before configuring the Cyclone II device or waiting for a configuration device to complete configuration. If you interrupt configuration, the Cyclone II device must be reconfigured via JTAG (PULSE\_CONFIG instruction) or by pulsing nCONFIG low after JTAG testing is complete.

For more information, see the *MorphIO: An I/O Reconfiguration Solution for Altera White Paper.*

The chip-wide reset (DEV\_CLRn) and chip-wide output enable (DEV\_OE) pins on Cyclone II devices do not affect JTAG boundary-scan or programming operations. Toggling these pins does not affect JTAG operations (other than the usual boundary-scan operation).

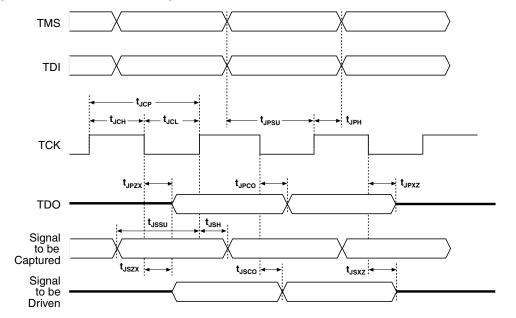

When the TAP controller is in the TEST\_LOGIC/RESET state, the BST circuitry is disabled, the device is in normal operation, and the instruction register is initialized with IDCODE as the initial instruction. At device power-up, the TAP controller starts in this TEST\_LOGIC/RESET state. In addition, forcing the TAP controller to the TEST\_LOGIC/RESET state is done by holding TMS high for five TCK clock cycles. Once in the TEST\_LOGIC/RESET state, the TAP controller remains in this state as long as TMS is held high (while TCK is clocked). Figure 14–6 shows the timing requirements for the IEEE Std. 1149.1 signals.

Figure 14–6. IEEE Std. 1149.1 Timing Waveforms

To start IEEE Std. 1149.1 operation, select an instruction mode by advancing the TAP controller to the shift instruction register (SHIFT\_IR) state and shift in the appropriate instruction code on the TDI pin. The waveform diagram in Figure 14–7 represents the entry of the instruction code into the instruction register. It shows the values of TCK, TMS, TDI, TDO, and the states of the TAP controller. From the RESET state, TMS is clocked with the pattern 01100 to advance the TAP controller to SHIFT IR. If you are testing the device after configuring it, the programmable weak pull-up resister or the bus hold feature overrides the CLAMP value (the value stored in the update register of the boundary-scan cell) at the pin.

## **HIGHZ Instruction Mode**

The HIGHZ instruction mode is used to set all of the user I/O pins to an inactive drive state. These pins are tri-stated until a new JTAG instruction is executed. When this instruction is loaded into the instruction register, the bypass register is connected between the TDI and TDO ports.

If you are testing the device after configuring it, the programmable weak pull-up resistor or the bus hold feature overrides the HIGHZ value at the pin.

## I/O Voltage Support in JTAG Chain

A JTAG chain can contain several different devices. However, you should be cautious if the chain contains devices that have different  $V_{CCIO}$  levels. The output voltage level of the TDO pin must meet the specifications of the TDI pin it drives. For Cyclone II devices, the TDO pin is powered by the  $V_{CCIO}$  power supply. Since the  $V_{CCIO}$  supply is 3.3 V, the TDO pin drives out 3.3 V.

Devices can interface with each other although they might have different  $V_{CCIO}$  levels. For example, a device with a 3.3-V TDO pin can drive to a device with a 5.0-V TDI pin because 3.3 V meets the minimum TTL-level  $V_{\rm IH}$  for the 5.0-V TDI pin. JTAG pins on Cyclone II devices can support 2.5- or 3.3-V input levels.

For more information on MultiVolt I/O support, see the *Cyclone II Architecture* chapter in Volume 1 of the *Cyclone II Device Handbook*.

You can also interface the TDI and TDO lines of the devices that have different V<sub>CCIO</sub> levels by inserting a level shifter between the devices. If possible, the JTAG chain should be built such that a device with a higher V<sub>CCIO</sub> level drives to a device with an equal or lower V<sub>CCIO</sub> level. This way, a level shifter may be required only to shift the TDO level to a level acceptable to the JTAG tester. Figure 14–13 shows the JTAG chain of mixed voltages and how a level shifter is inserted in the chain.