#### Intel - EP2C5AT144A7N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 288                                                      |

| Number of Logic Elements/Cells | 4608                                                     |

| Total RAM Bits                 | 119808                                                   |

| Number of I/O                  | 89                                                       |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 125°C (TJ)                                       |

| Package / Case                 | 144-LQFP                                                 |

| Supplier Device Package        | 144-TQFP (20x20)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c5at144a7n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2–18. Cyclone II Device LVDS Channels (Part 2 of 2) |     |           |  |  |  |  |

|-----------------------------------------------------------|-----|-----------|--|--|--|--|

| DevicePin CountNumber of LVD<br>Channels (1)              |     |           |  |  |  |  |

| EP2C70                                                    | 672 | 160 (168) |  |  |  |  |

|                                                           | 896 | 257 (265) |  |  |  |  |

Note to Table 2–18:

The first number represents the number of bidirectional I/O pins which can be used as inputs or outputs. The number in parenthesis includes dedicated clock input pin pairs which can only be used as inputs.

You can use I/O pins and internal logic to implement a high-speed I/O receiver and transmitter in Cyclone II devices. Cyclone II devices do not contain dedicated serialization or deserialization circuitry. Therefore, shift registers, internal PLLs, and IOEs are used to perform serial-to-parallel conversions on incoming data and parallel-to-serial conversion on outgoing data.

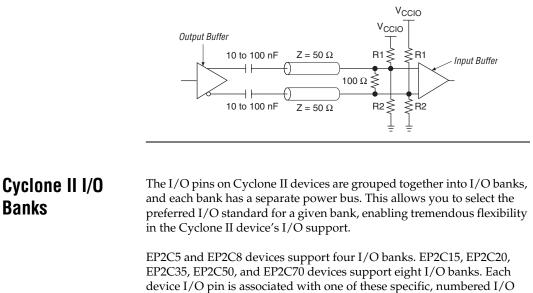

The maximum internal clock frequency for a receiver and for a transmitter is 402.5 MHz. The maximum input data rate of 805 Mbps and the maximum output data rate of 640 Mbps is only achieved when DDIO registers are used. The LVDS standard does not require an input reference voltage, but it does require a 100- $\Omega$  termination resistor between the two signals at the input buffer. An external resistor network is required on the transmitter side.

For more information on Cyclone II differential I/O interfaces, see the *High-Speed Differential Interfaces in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

## **Series On-Chip Termination**

On-chip termination helps to prevent reflections and maintain signal integrity. This also minimizes the need for external resistors in high pin count ball grid array (BGA) packages. Cyclone II devices provide I/O driver on-chip impedance matching and on-chip series termination for single-ended outputs and bidirectional pins.

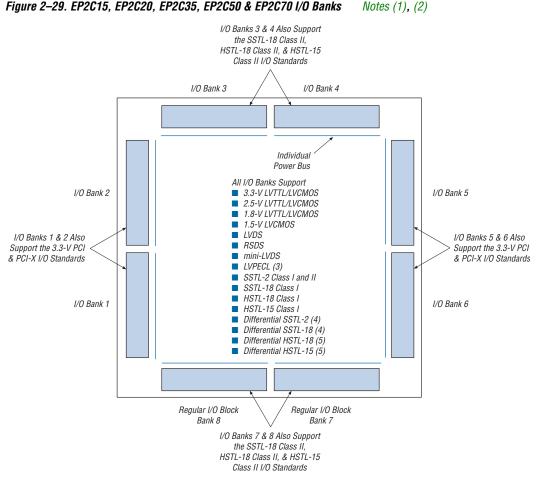

#### Notes to Figure 2–29:

- (1) This is a top view of the silicon die.

- (2) This is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (5) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

Each I/O bank has its own VCCIO pins. A single device can support 1.5-V, 1.8-V, 2.5-V, and 3.3-V interfaces; each individual bank can support a different standard with different I/O voltages. Each bank also has dual-purpose VREF pins to support any one of the voltage-referenced

standards (e.g., SSTL-2) independently. If an I/O bank does not use voltage-referenced standards, the VREF pins are available as user I/O pins.

Each I/O bank can support multiple standards with the same  $V_{\rm CCIO}$  for input and output pins. For example, when  $V_{\rm CCIO}$  is 3.3-V, a bank can support LVTTL, LVCMOS, and 3.3-V PCI for inputs and outputs. Voltage-referenced standards can be supported in an I/O bank using any number of single-ended or differential standards as long as they use the same  $V_{\rm REF}$  and a compatible  $V_{\rm CCIO}$  value.

## MultiVolt I/O Interface

The Cyclone II architecture supports the MultiVolt I/O interface feature, which allows Cyclone II devices in all packages to interface with systems of different supply voltages. Cyclone II devices have one set of  $V_{CC}$  pins (VCCINT) that power the internal device logic array and input buffers that use the LVPECL, LVDS, HSTL, or SSTL I/O standards. Cyclone II devices also have four or eight sets of VCC pins (VCCIO) that power the I/O output drivers and input buffers that use the LVTTL, LVCMOS, or PCI I/O standards.

The Cyclone II VCCINT pins must always be connected to a 1.2-V power supply. If the V<sub>CCINT</sub> level is 1.2 V, then input pins are 1.5-V, 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-V, 1.8-V, 2.5-V, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (i.e., when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3-V and is compatible with 3.3-V systems. Table 2–20 summarizes Cyclone II MultiVolt I/O support.

| Table 2–2             | 2-20. Cyclone II MultiVolt I/O Support (Part 1 of 2) Note (1) |              |                         |                         |                         |              |       |       |

|-----------------------|---------------------------------------------------------------|--------------|-------------------------|-------------------------|-------------------------|--------------|-------|-------|

| V (1)                 | Input Signal Output Signal                                    |              |                         |                         |                         |              |       |       |

| V <sub>ccio</sub> (V) | 1.5 V                                                         | 1.8 V        | 2.5 V                   | 3.3 V                   | 1.5 V                   | 1.8 V        | 2.5 V | 3.3 V |

| 1.5                   | $\checkmark$                                                  | $\checkmark$ | <ul> <li>(2)</li> </ul> | <ul> <li>(2)</li> </ul> | $\checkmark$            |              |       |       |

| 1.8                   | <ul><li>✓ (4)</li></ul>                                       | $\checkmark$ | <ul> <li>(2)</li> </ul> | <ul><li>✓ (2)</li></ul> | <ul><li>✓ (3)</li></ul> | $\checkmark$ |       |       |

| 2.5                   |                                                               |              | $\checkmark$            | $\checkmark$            | <ul> <li>(5)</li> </ul> | 🗸 (5)        | ~     |       |

# 5. DC Characteristics and Timing Specifications

CII51005-4.0

# Operating Conditions

Cyclone<sup>®</sup> II devices are offered in commercial, industrial, automotive, and extended temperature grades. Commercial devices are offered in –6 (fastest), –7, and –8 speed grades.

All parameter limits are representative of worst-case supply voltage and junction temperature conditions. Unless otherwise noted, the parameter values in this chapter apply to all Cyclone II devices. AC and DC characteristics are specified using the same numbers for commercial, industrial, and automotive grades. All parameters representing voltages are measured with respect to ground.

Tables 5–1 through 5–4 provide information on absolute maximum ratings.

| Table 5–1. Cyclone II Device Absolute Maximum Ratings       Notes (1), (2) |                            |                         |         |         |      |  |  |  |

|----------------------------------------------------------------------------|----------------------------|-------------------------|---------|---------|------|--|--|--|

| Symbol                                                                     | Parameter                  | Conditions              | Minimum | Maximum | Unit |  |  |  |

| V <sub>CCINT</sub>                                                         | Supply voltage             | With respect to ground  | -0.5    | 1.8     | V    |  |  |  |

| V <sub>CCIO</sub>                                                          | Output supply voltage      |                         | -0.5    | 4.6     | V    |  |  |  |

| V <sub>CCA-PLL</sub> [14]                                                  | PLL supply voltage         |                         | -0.5    | 1.8     | V    |  |  |  |

| V <sub>IN</sub>                                                            | DC input voltage (3)       | —                       | -0.5    | 4.6     | V    |  |  |  |

| I <sub>OUT</sub>                                                           | DC output current, per pin | -                       | -25     | 40      | mA   |  |  |  |

| T <sub>STG</sub>                                                           | Storage temperature        | No bias                 | -65     | 150     | °C   |  |  |  |

| TJ                                                                         | Junction temperature       | BGA packages under bias | —       | 125     | °C   |  |  |  |

Notes to Table 5–1:

- (1) Conditions beyond those listed in this table cause permanent damage to a device. These are stress ratings only. Functional operation at these levels or any other conditions beyond those specified in this chapter is not implied. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effect on the device reliability.

- (2) Refer to the Operating Requirements for Altera Devices Data Sheet for more information.

- (3) During transitions, the inputs may overshoot to the voltage shown in Table 5–4 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transition, the inputs may undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

| Parameter | –6 Speed | Grade (1) | –7 Speed | Grade (2) | –8 Speed | 11  |      |

|-----------|----------|-----------|----------|-----------|----------|-----|------|

| Parameter | Min      | Max       | Min      | Max       | Min      | Max | Unit |

| TPRE      | 191      | —         | 244      | —         | 244      | —   | ps   |

|           | _        | —         | 217      | —         | 244      |     | ps   |

| TCLKL     | 1000     | —         | 1242     | —         | 1242     |     | ps   |

|           | _        | —         | 1111     | —         | 1242     |     | ps   |

| TCLKH     | 1000     | —         | 1242     | —         | 1242     | —   | ps   |

|           | _        | —         | 1111     | —         | 1242     |     | ps   |

| tLUT      | 180      | 438       | 172      | 545       | 172      | 651 | ps   |

|           | _        |           | 180      | —         | 180      |     | ps   |

#### Notes to Table 5–16:

(1) For the -6 speed grades, the minimum timing is for the commercial temperature grade. The -7 speed grade devices offer the automotive temperature grade. The -8 speed grade devices offer the industrial temperature grade.

(2) For each parameter of the -7 speed grade columns, the value in the first row represents the minimum timing parameter for automotive devices. The second row represents the minimum timing parameter for commercial devices.

(3) For each parameter of the -8 speed grade columns, the value in the first row represents the minimum timing parameter for industrial devices. The second row represents the minimum timing parameter for commercial devices.

| Table 5–17. IOE Interna | Table 5–17. IOE Internal Timing Microparameters (Part 1 of 2) |           |          |           |          |      |    |  |

|-------------------------|---------------------------------------------------------------|-----------|----------|-----------|----------|------|----|--|

| Deremeter               | –6 Speed                                                      | Grade (1) | –7 Speed | Grade (2) | –8 Speed | Unit |    |  |

| Parameter               | Min                                                           | Max       | Min Max  |           | Min      | Unit |    |  |

| TSU                     | 76                                                            | —         | 101      | —         | 101      | —    | ps |  |

|                         | —                                                             | —         | 89       | —         | 101      | _    | ps |  |

| тн                      | 88                                                            | —         | 106      | —         | 106      | —    | ps |  |

|                         | —                                                             | —         | 97       | —         | 106      | —    | ps |  |

| тсо                     | 99                                                            | 155       | 95       | 171       | 95       | 187  | ps |  |

|                         | —                                                             | —         | 99       | —         | 99       | _    | ps |  |

| TPIN2COMBOUT_R          | 384                                                           | 762       | 366      | 784       | 366      | 855  | ps |  |

|                         | —                                                             | —         | 384      | —         | 384      | _    | ps |  |

| TPIN2COMBOUT_C          | 385                                                           | 760       | 367      | 783       | 367      | 854  | ps |  |

|                         | —                                                             | —         | 385      | —         | 385      | —    | ps |  |

| TCOMBIN2PIN_R           | 1344                                                          | 2490      | 1280     | 2689      | 1280     | 2887 | ps |  |

|                         | —                                                             | —         | 1344     | —         | 1344     | _    | ps |  |

| Table 5–40. Cyclone II I/O Input Delay for Column Pins (Part 3 of 3) |                    |     |       |                |                       |                             |                      |      |

|----------------------------------------------------------------------|--------------------|-----|-------|----------------|-----------------------|-----------------------------|----------------------|------|

|                                                                      | Fast Co            |     | orner | -6             | -7                    | -7<br>Speed<br>Grade<br>(2) | –8<br>Speed<br>Grade |      |

| I/O Standard                                                         | Parameter          |     |       | Speed<br>Grade | Speed<br>Grade<br>(1) |                             |                      | Unit |

| 1.2V_DIFFERENTIAL_HSTL                                               | t <sub>PI</sub>    | 570 | 597   | 1263           | 1324                  | 1385                        | 1385                 | ps   |

|                                                                      | t <sub>PCOUT</sub> | 356 | 373   | 801            | 879                   | 957                         | 957                  | ps   |

*Notes to Table 5–40 :*

(1) These numbers are for commercial devices.

(2) These numbers are for automotive devices.

|                   |                    | Fast Co                   | -6              | 7              | _7                    | -8                    |                |      |

|-------------------|--------------------|---------------------------|-----------------|----------------|-----------------------|-----------------------|----------------|------|

| I/O Standard      | Parameter          | Industrial/<br>Automotive | Commer<br>-cial | Speed<br>Grade | Speed<br>Grade<br>(1) | Speed<br>Grade<br>(2) | Speed<br>Grade | Unit |

| LVTTL             | t <sub>P1</sub>    | 583                       | 611             | 1129           | 1160                  | 1240                  | 1240           | ps   |

|                   | t <sub>PCOUT</sub> | 366                       | 384             | 762            | 784                   | 855                   | 855            | ps   |

| 2.5V              | t <sub>P1</sub>    | 629                       | 659             | 1099           | 1171                  | 1244                  | 1244           | ps   |

|                   | t <sub>PCOUT</sub> | 412                       | 432             | 732            | 795                   | 859                   | 859            | ps   |

| 1.8V              | t <sub>PI</sub>    | 729                       | 764             | 1278           | 1360                  | 1443                  | 1443           | ps   |

|                   | t <sub>PCOUT</sub> | 512                       | 537             | 911            | 984                   | 1058                  | 1058           | ps   |

| 1.5V              | t <sub>P1</sub>    | 794                       | 832             | 1345           | 1429                  | 1513                  | 1513           | ps   |

|                   | t <sub>PCOUT</sub> | 577                       | 605             | 978            | 1053                  | 1128                  | 1128           | ps   |

| LVCMOS            | t <sub>P1</sub>    | 583                       | 611             | 1129           | 1160                  | 1240                  | 1240           | ps   |

|                   | t <sub>PCOUT</sub> | 366                       | 384             | 762            | 784                   | 855                   | 855            | ps   |

| SSTL_2_CLASS_I    | t <sub>P1</sub>    | 536                       | 561             | 896            | 947                   | 998                   | 998            | ps   |

|                   | t <sub>PCOUT</sub> | 319                       | 334             | 529            | 571                   | 613                   | 613            | ps   |

| SSTL_2_CLASS_II   | t <sub>P1</sub>    | 536                       | 561             | 896            | 947                   | 998                   | 998            | ps   |

|                   | t <sub>PCOUT</sub> | 319                       | 334             | 529            | 571                   | 613                   | 613            | ps   |

| SSTL_18_CLASS_I   | t <sub>P1</sub>    | 581                       | 609             | 933            | 967                   | 1004                  | 1004           | ps   |

|                   | t <sub>PCOUT</sub> | 364                       | 382             | 566            | 591                   | 619                   | 619            | ps   |

| SSTL_18_CLASS_II  | t <sub>P1</sub>    | 581                       | 609             | 933            | 967                   | 1004                  | 1004           | ps   |

|                   | t <sub>PCOUT</sub> | 364                       | 382             | 566            | 591                   | 619                   | 619            | ps   |

| 1.5V_HSTL_CLASS_I | t <sub>P1</sub>    | 593                       | 621             | 1051           | 1109                  | 1167                  | 1167           | ps   |

|                   | t <sub>PCOUT</sub> | 376                       | 394             | 684            | 733                   | 782                   | 782            | ps   |

| Table 5-          | Table 5–50. LVDS Transmitter Timing Specification (Part 2 of 2) |     |                |                   |            |     |                |            |            |                |     |                   |                   |      |

|-------------------|-----------------------------------------------------------------|-----|----------------|-------------------|------------|-----|----------------|------------|------------|----------------|-----|-------------------|-------------------|------|

|                   |                                                                 |     | –6 Speed Grade |                   |            |     | –7 Speed Grade |            |            | –8 Speed Grade |     |                   |                   |      |

| Symbol            | Conditions                                                      | Min | Тур            | <b>Max</b><br>(1) | Max<br>(2) | Min | Тур            | Max<br>(1) | Max<br>(2) | Min            | Тур | <b>Max</b><br>(1) | Max<br><i>(2)</i> | Unit |

| t <sub>FALL</sub> | 80–20%                                                          | 150 | 200            | 25                | 50         | 150 | 200            | 25         | 50         | 150            | 200 | 250               | (11)              | ps   |

| t <sub>LOCK</sub> | _                                                               |     |                | 10                | 00         | _   | —              | 1(         | 00         | _              | _   | 100               | (12)              | μs   |

#### Notes to Table 5–50:

- (1) The maximum data rate that complies with duty cycle distortion of 45–55%.

- (2) The maximum data rate when taking duty cycle in absolute ps into consideration that may not comply with 45–55% duty cycle distortion. If the downstream receiver can handle duty cycle distortion beyond the 45–55% range, you may use the higher data rate values from this column. You can calculate the duty cycle distortion as a percentage using the absolute ps value. For example, for a data rate of 640 Mbps (UI = 1562.5 ps) and a  $t_{DUTY}$  of 250 ps, the duty cycle distortion is  $\pm t_{DUTY}/(UI*2)*100\% = \pm 250 \text{ ps}/(1562.5*2)*100\% = \pm 8\%$ , which gives you a duty cycle distortion of 42–58%.

- (3) The TCCS specification applies to the entire bank of LVDS, as long as the SERDES logic is placed within the LAB adjacent to the output pins.

- (4) For extended temperature devices, the maximum input clock frequency for ×10 through ×2 modes is 137.5 MHz.

- (5) For extended temperature devices, the maximum data rate for  $\times 10$  through  $\times 2$  modes is 275 Mbps.

- (6) For extended temperature devices, the maximum input clock frequency for ×10 through ×2 modes is 200 MHz.

- (7) For extended temperature devices, the maximum data rate for ×10 through ×2 modes is 400 Mbps.

- (8) For extended temperature devices, the maximum input clock frequency for ×1 mode is 340 MHz.

- (9) For extended temperature devices, the maximum data rate for ×1 mode is 340 Mbps.

- (10) For extended temperature devices, the maximum output jitter (peak to peak) is 600 ps.

- (11) For extended temperature devices, the maximum  $t_{RISE}$  and  $t_{FALL}$  are 300 ps.

- (12) For extended temperature devices, the maximum lock time is 500 us.

| Path Notes (1), (2) (Part 2 of 2)   |     |            |     |      |

|-------------------------------------|-----|------------|-----|------|

| Row Pins with PLL in the Clock Path | C6  | <b>C</b> 7 | C8  | Unit |

| 1.5-V                               | 280 | 280        | 280 | ps   |

| SSTL-2 Class I                      | 150 | 190        | 230 | ps   |

| SSTL-2 Class II                     | 155 | 200        | 230 | ps   |

| SSTL-18 Class I                     | 180 | 240        | 260 | ps   |

| HSTL-18 Class I                     | 180 | 235        | 235 | ps   |

| HSTL-15 Class I                     | 205 | 220        | 220 | ps   |

| Differential SSTL-2 Class I         | 150 | 190        | 230 | ps   |

| Differential SSTL-2 Class II        | 155 | 200        | 230 | ps   |

| Differential SSTL-18 Class I        | 180 | 240        | 260 | ps   |

| Differential HSTL-18 Class I        | 180 | 235        | 235 | ps   |

| Differential HSTL-15 Class I        | 205 | 220        | 220 | ps   |

| LVDS                                | 95  | 110        | 120 | ps   |

| Simple RSDS                         | 100 | 155        | 155 | ps   |

| Mini LVDS                           | 95  | 110        | 120 | ps   |

| PCI                                 | 285 | 305        | 335 | ps   |

| PCI-X                               | 285 | 305        | 335 | ps   |

Table 5–57. Maximum for DDIO Output on Row Pins with PLL in the Clock

Path

Notes (1), (2)

(Part 2 of 2)

Notes to Table 5–57:

(1) The DCD specification is characterized using the maximum drive strength available for each I/O standard.

(2) Numbers are applicable for commercial, industrial, and automotive devices.

For DDIO outputs, you can calculate actual half period from the following equation:

Actual half period = ideal half period - maximum DCD

For example, if the DDR output I/O standard is SSTL-2 Class II, the maximum DCD for a -5 device is 155 ps (refer to Table 5–57). If the clock frequency is 167 MHz, the half-clock period T/2 is:

T/2 = 1/(2\* f) = 1/(2\*167 MHz) = 3 ns = 3000 ps

## **ROM Mode**

Cyclone II memory blocks support ROM mode. A MIF initializes the ROM contents of these blocks. The address lines of the ROM are registered. The outputs can be registered or unregistered. The ROM read operation is identical to the read operation in the single-port RAM configuration.

#### **FIFO Buffer Mode**

A single clock or dual clock FIFO buffer may be implemented in the memory blocks. Dual clock FIFO buffers are useful when transferring data from one clock domain to another clock domain. All FIFO memory configurations have synchronous inputs. However, the FIFO buffer outputs are always combinational (i.e., not registered). Simultaneous read and write from an empty FIFO buffer is not supported.

For more information on FIFO buffers, refer to the *Single-* & *Dual-Clock FIFO Megafunctions User Guide*.

# **Clock Modes**

Depending on which memory mode is selected, the following clock modes are available:

- Independent

- Input/output

- Read/write

- Single-clock

Table 8–7 shows these clock modes supported by all memory blocks when configured in each respective memory modes.

| Table 8–7. Cyclone II Memory Clock Modes |                        |                          |                     |  |  |  |  |  |

|------------------------------------------|------------------------|--------------------------|---------------------|--|--|--|--|--|

| Clocking Modes                           | True Dual-Port<br>Mode | Simple Dual-Port<br>Mode | Single-Port<br>Mode |  |  |  |  |  |

| Independent                              | $\checkmark$           |                          |                     |  |  |  |  |  |

| Input/output                             | ~                      | ~                        | $\checkmark$        |  |  |  |  |  |

| Read/write                               |                        | ~                        |                     |  |  |  |  |  |

| Single clock                             | ~                      | ~                        | ~                   |  |  |  |  |  |

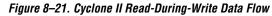

# Read-During-Write Operation at the Same Address

The "Same-Port Read-During-Write Mode" and "Mixed-Port Read-During-Write Mode" sections describe the functionality of the various RAM configurations when reading from an address during a write operation at that same address. There are two read-during-write data flows: same-port and mixed-port. Figure 8–21 shows the difference between these flows.

## Same-Port Read-During-Write Mode

For read-during-write operation of a single-port RAM or the same port of a true dual-port RAM, the new data is available on the rising edge of the same clock cycle on which it was written. Figure 8–22 shows a sample functional waveform. When using byte enables in true dual-port RAM mode, the outputs for the masked bytes on the same port are unknown (see Figure 8–2 on page 8–6). The non-masked bytes are read out as shown in Figure 8–22.

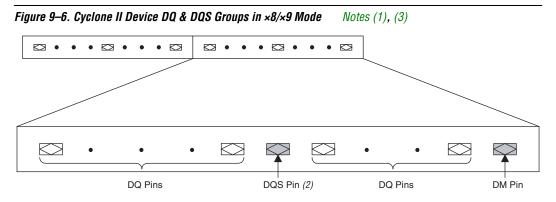

# DDR Memory Interface Pins

Cyclone II devices use data (DQ), data strobe (DQS), and clock pins to interface with external memory. Figure 9–6 shows the DQ and DQS pins in the  $\times 8/\times 9$  mode.

#### Notes to Figure 9–6:

- (1) Each DQ group consists of a DQS pin, a DM pin, and up to nine DQ pins.

- (2) For the QDRII memory interface, other DQS pins implement the CQn pins. These pins are denoted by DQS/CQ# in the pin table.

- (3) This is an idealized pin layout. For the actual pin layout, refer to the pin tables in the *PCB Layout Guidelines* section of the *Cyclone II Device Handbook, Volume 1*.

## Data & Data Strobe Pins

Cyclone II data pins for the DDR memory interfaces are called DQ pins. Cyclone II devices can use either bidirectional data strobes or unidirectional read clocks. Depending on the external memory interface, either the memory device's read data strobes or read clocks feed the DQS pins.

In Cyclone II devices, all the I/O banks support DDR and DDR2 SDRAM and QDRII SRAM memory at up to 167 MHz. All the I/O banks support DQS signals with the DQ bus modes of  $\times 8/\times 9$  and  $\times 16/\times 18$ . Cyclone II devices can support either bidirectional data strobes or unidirectional read clocks.

P

DDR2 and QDRII interfaces with class II I/O standard can only be implemented on the top and bottom I/O banks of the Cyclone II device.

#### Figure 10–18. LVPECL AC Coupled Termination

# devices I/O pin is associated with one of these specific, numbered I/O banks (refer to Figures 10–19 and 10–20). To accommodate voltage-referenced I/O standards, each Cyclone II I/O bank has separate $V_{REF}$ bus. Each bank in EP2C5, EP2C8, EP2C15, EP2C20, EP2C35, and EP2C50 devices supports two VREF pins and each bank in EP2C70 devices supports four VREF pins. In the event these pins are not used as VREF pins, they may be used as regular I/O pins. However, they are expected to have slightly higher pin capacitance than other user I/O pins when used with regular user I/O pins.

Additionally, each Cyclone II I/O bank has its own VCCIO pins. Any single I/O bank can only support one V<sub>CCIO</sub> setting from among 1.5, 1.8, 2.5 or 3.3 V. Although there can only be one V<sub>CCIO</sub> voltage per I/O bank, Cyclone II devices permit additional input signaling capabilities, as shown in Table 10–4.

| Donk V (V)                 | Acceptable Input Levels (V) |                         |              |                       |  |  |  |

|----------------------------|-----------------------------|-------------------------|--------------|-----------------------|--|--|--|

| Bank V <sub>ccio</sub> (V) | 3.3                         | 2.5                     | 1.8          | 1.5                   |  |  |  |

| 3.3                        | $\checkmark$                | 🗸 (1)                   |              |                       |  |  |  |

| 2.5                        | $\checkmark$                | $\checkmark$            |              |                       |  |  |  |

| 1.8                        | <ul> <li>(2)</li> </ul>     | <ul><li>✓ (2)</li></ul> | $\checkmark$ | <ul><li>(1)</li></ul> |  |  |  |

| 1.5                        | <ul> <li>(2)</li> </ul>     | <ul> <li>(2)</li> </ul> | $\checkmark$ | $\checkmark$          |  |  |  |

Notes to Table 10–4:

- Because the input level does not drive to the rail, the input buffer does not completely shut off, and the I/O current is slightly higher than the default value.

- (2) These input values overdrive the input buffer, so the pin leakage current is slightly higher than the default value. To drive inputs higher than V<sub>CCIO</sub> but less than 4.0 V, disable the PCI clamping diode and turn on Allow voltage overdrive for LVTTL/LVCMOS input pins in Settings > Device > Device and Pin Options > Pin Placement tab. This setting allows input pins with LVTTL or LVCMOS I/O standards to be placed by the Quartus II software in an I/O bank with a lower V<sub>CCIO</sub> voltage than the voltage specified by the pins.

Any number of supported single-ended or differential standards can be simultaneously supported in a single I/O bank as long as they use compatible  $V_{\rm CCIO}$  levels for input and output pins. For example, an I/O bank with a 2.5-V  $V_{\rm CCIO}$  setting can support 2.5-V LVTTL inputs and outputs, 2.5-V LVDS-compatible inputs and outputs, and 3.3-V LVCMOS inputs only.

Voltage-referenced standards can be supported in an I/O bank using any number of single-ended or differential standards as long as they use the same V<sub>REF</sub> and a compatible V<sub>CCIO</sub> value. For example, if you choose to implement both SSTL-2 and SSTL-18 in your Cyclone II device, I/O pins using these standards—because they require different V<sub>REF</sub> values—must be in different banks from each other. However, the same I/O bank can support SSTL-2 and 2.5-V LVCMOS with the V<sub>CCIO</sub> set to 2.5 V and the V<sub>REF</sub> set to 1.25 V.

Refer to "Pad Placement and DC Guidelines" on page 10–27 for more information.

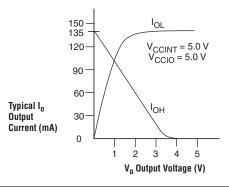

As shown above,  $R_1 = 5.0$ -V/135 mA.

$\label{eq:shown in data sheets usually reflect typical operating conditions. Subtract 20% from the data sheet value for guard band. This subtraction when applied in the example in Figure 10–22 gives R1 a value of 30 <math display="inline">\Omega$

$R_2$  should be selected so that it does not violate the driving device's  $I_{OH}$  specification. For example, if the device has a maximum  $I_{OH}$  of 8 mA, given that the PCI clamping diode,  $V_{\rm IN} = V_{\rm CCIO} + 0.7 - V = 3.7 - V$ , and the maximum supply load of a 5.0-V device ( $V_{\rm CC}$ ) is 5.25-V, the value of  $R_2$  can be calculated as follows:

$$R_2 = (5.25 \text{ V} - 3.7 \text{ V}) - (8 \text{ mA} \times 30 \Omega) = 164 \Omega$$

8 mA

This analysis assumes worst case conditions. If your system does not have a wide variation in voltage-supply levels, you can adjust these calculations accordingly.

Because 5.0-V device tolerance in Cyclone II devices requires use of the PCI clamp, and this clamp is activated during configuration, 5.0-V signals may not be driven into the device until it is configured.

# Conclusion

Cyclone II device I/O capabilities enable you to keep pace with increasing design complexity utilizing a low-cost FPGA device family. Support for I/O standards including SSTL and LVDS compatibility allow Cyclone II devices to fit into a wide variety of applications. The Quartus II

You can use I/O pins and internal logic to implement a high-speed I/O receiver and transmitter in Cyclone II devices. Cyclone II devices do not contain dedicated serialization or deserialization circuitry. Therefore, shift registers, internal global phase-locked loops (PLLs), and I/O cells are used to perform serial-to-parallel conversions on incoming data and parallel-to-serial conversion on outgoing data.

# I/O Standards Support

This section provides information on the I/O standards that Cyclone II devices support.

## LVDS Standard Support in Cyclone II Devices

The LVDS I/O standard is a high-speed, low-voltage swing, low power, and general purpose I/O interface standard. The Cyclone II device meets the ANSI/TIA/EIA-644 standard.

I/O banks on all four sides of the Cyclone II device support LVDS channels. See the pin tables on the Altera web site for the number of LVDS channels supported throughout different family members. Cyclone II LVDS receivers (input) support a data rate of up to 805 Mbps while LVDS transmitters (output) support up to 640 Mbps. The maximum internal clock frequency for a receiver and for a transmitter is 402.5 MHz. The maximum input data rate of 805 Mbps and the maximum output data rate of 640 Mbps is only achieved when DDIO registers are used. The LVDS standard does not require an input reference voltage; however, it does require a 100- $\Omega$  termination resistor between the two signals at the input buffer.

For LVDS data rates in Cyclone II devices with different speed grades, see the *DC Characteristics & Timing Specifications* chapter of the *Cyclone II Device Handbook*.

Table 11–1 shows LVDS I/O specifications.

| Table 11–1. LVDS I/O Specifications (Part 1 of 2)       Note (1) |                                              |                        |       |      |       |       |  |  |

|------------------------------------------------------------------|----------------------------------------------|------------------------|-------|------|-------|-------|--|--|

| Symbol                                                           | Parameter                                    | Condition              | Min   | Тур  | Max   | Units |  |  |

| V <sub>CCINT</sub>                                               | Supply voltage                               |                        | 1.15  | 1.2  | 1.25  | V     |  |  |

| V <sub>CCIO</sub>                                                | I/O supply voltage                           |                        | 2.375 | 2.5  | 2.625 | V     |  |  |

| V <sub>OD</sub>                                                  | Differential output voltage                  | $R_L = 100 \Omega$     | 250   |      | 600   | mV    |  |  |

| $\Delta V_{OD}$                                                  | Change in V <sub>OD</sub> between<br>H and L | R <sub>L</sub> = 100 Ω |       |      | 50    | mV    |  |  |

| V <sub>OS</sub>                                                  | Output offset voltage                        | $R_L = 100 \Omega$     | 1.125 | 1.25 | 1.375 | V     |  |  |

#### Configuration Stage

When the nSTATUS pin transitions high, the configuration device's OE pin also transitions high and the configuration device clocks data out serially to the FPGA using its internal oscillator. The Cyclone II device receives configuration data on its DATA0 pin and the clock is received on the DCLK pin. Data is latched into the FPGA on the rising edge of DCLK.

After the FPGA has received all configuration data successfully, it releases the open-drain CONF\_DONE pin, which is pulled high by a pull-up resistor. Since the Cyclone II device's CONF\_DONE pin is tied to the configuration device's nCS pin, the configuration device is disabled when CONF\_DONE goes high. Enhanced configuration and EPC2 devices have an optional internal pull-up resistor on the nCS pin. You can turn this option on in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. If you do not use this internal pull-up resistor, you need to connect an external 10-k $\Omega$  pull-up resistor to the nCS and CONF\_DONE line. A low-to-high transition on CONF\_DONE indicates configuration is complete, and the device can begin initialization.

#### Initialization Stage

In Cyclone II devices, the default initialization clock source is the Cyclone II internal oscillator (typically 10 MHz). Cyclone II devices can also use the optional CLKUSR pin. If your design uses the internal oscillator, the Cyclone II device supplies itself with enough clock cycles for proper initialization. The advantage of using the internal oscillator is you do not need to use another device or source to send additional clock cycles to the CLKUSR pin during the initialization stage. Additionally, you can use of the CLKUSR pin as a user I/O pin, which means you have an additional user I/O pin.

If you want to delay the initialization of the device, you can use the CLKUSR pin. Using the CLKUSR pin allows you to control when the Cyclone II device enters user mode. You can delay the Cyclone II devices from entering user mode for an indefinite amount of time. You can turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. Supplying a clock on CLKUSR does not affect the configuration process. After all configuration data is accepted and CONF\_DONE goes high, Cyclone II devices require 299 clock cycles to properly initialize and support a CLKUSR f<sub>MAX</sub> of 100 MHz.

An optional INIT\_DONE pin is available, which signals the end of initialization and the start of user mode with a low-to-high transition. The **Enable INIT\_DONE output** option is available in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. If you use the INIT\_DONE pin, an external 10-k $\Omega$ pull-up resistor pulls it high when

# Document Revision History

Table 13–14 shows the revision history for this document.

| Table 13–14. Document Revision History |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Date &<br>Document<br>Version          | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Summary of Changes                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| February 2007<br>v3.1                  | <ul> <li>Added document revision history.</li> <li>Added Note (1) to Table 13–1.</li> <li>Added Note (1) to Table 13–1.</li> <li>Added Note (1) to Table 13–4.</li> <li>Updated Figure 13–3.</li> <li>Updated Figures 13–6 and 13–7.</li> <li>Updated Note (2) to Figure 13–13.</li> <li>Updated "Single Device PS Configuration Using a Configuration Device" section.</li> <li>Updated Note (2) to Figure 13–14.</li> <li>Updated Note (2) to Figure 13–15.</li> <li>Updated Note (2) to Figure 13–16.</li> <li>Updated Note (2) to Figure 13–17.</li> <li>Updated Note (4) to Figure 13–21.</li> <li>Updated Note (2) to Figure 13–25.</li> </ul>                                                                                                                                                                                                                                                                   | <ul> <li>Changed unit 'kw' to 'kΩ' in Figures 13–6 and 13–7.</li> <li>Added note about serial configuration devices supporting 20 MHz and 40 MHz DCLK.</li> <li>Added infomation about the need for a resistor on nCONFIG if reconfiguration is required.</li> <li>Added information about MSEL[10] internal pull-down resistor value.</li> </ul> |  |  |  |  |  |

| July 2005 v2.0                         | <ul> <li>Updated "Configuration Stage" section.</li> <li>Updated "PS Configuration Using a<br/>Download Cable" section.</li> <li>Updated Figures 13–8, 13–12, and<br/>13–18.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| November 2004<br>v1.1                  | <ul> <li>Updated "Configuration Stage" section in<br/>"Single Device AS Configuration" section.</li> <li>Updated "Initialization Stage" section in<br/>"Single Device AS Configuration" section.</li> <li>Updated Figure 13–8.</li> <li>Updated "Initialization Stage" section in<br/>"Single Device PS Configuration Using a<br/>MAX II Device as an External Host"<br/>section.</li> <li>Updated Table 13–7.</li> <li>Updated Table 13–7.</li> <li>Updated "Single Device PS Configuration<br/>Using a Configuration Device" section.</li> <li>Updated "Initialization Stage" section in<br/>"Single Device PS Configuration<br/>Using a Configuration Device" section.</li> <li>Updated "Initialization Stage" section in<br/>"Single Device PS Configuration Using a<br/>Configuration Device" section.</li> <li>Updated Figure 13–18.</li> <li>Updated "Single Device JTAG<br/>Configuration" section.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| June 2004 v1.0                         | Added document to the Cyclone II Device Handbook.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

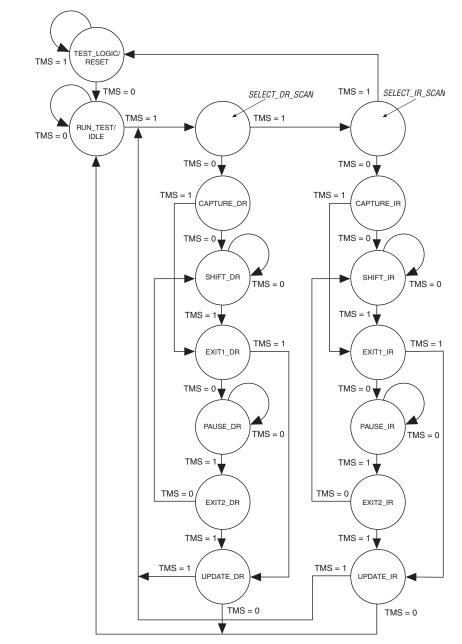

Figure 14–5. IEEE Std. 1149.1 TAP Controller State Machine

## 208-Pin Plastic Quad Flat Pack (PQFP) – Wirebond

- All dimensions and tolerances conform to ASME Y14.5M 1994.

- Controlling dimension is in millimeters.

- Pin 1 may be indicated by an ID dot in its proximity on package surface.

Tables 15–7 and 15–8 show the package information and package outline figure references, respectively, for the 208-pin PQFP package.

| Table 15–7. 208-Pin PQFP Package Information |                                                |  |  |  |  |

|----------------------------------------------|------------------------------------------------|--|--|--|--|

| Description                                  | Specification                                  |  |  |  |  |

| Ordering code reference                      | Q                                              |  |  |  |  |

| Package acronym                              | PQFP                                           |  |  |  |  |

| Lead material                                | Copper                                         |  |  |  |  |

| Lead finish (plating)                        | Regular: 85Sn:15Pb (Typ.)<br>Pb-free: Matte Sn |  |  |  |  |

| JEDEC Outline Reference                      | MS-029 Variation: FA-1                         |  |  |  |  |

| Maximum lead coplanarity                     | 0.003 inches (0.08 mm)                         |  |  |  |  |

| Weight                                       | 5.7 g                                          |  |  |  |  |

| Moisture sensitivity level                   | Printed on moisture barrier bag                |  |  |  |  |

| Table 15–8. 208-Pin PQFP Package Outline Dimensions (Part 1 of 2) |            |           |      |  |  |  |

|-------------------------------------------------------------------|------------|-----------|------|--|--|--|

| Sumbol                                                            | Millimeter |           |      |  |  |  |

| Symbol                                                            | Min.       | Nom.      | Max. |  |  |  |

| А                                                                 | -          | -         | 4.10 |  |  |  |

| A1                                                                | 0.25       | -         | 0.50 |  |  |  |

| A2                                                                | 3.20       | 3.40      | 3.60 |  |  |  |

| D                                                                 |            | 30.60 BSC |      |  |  |  |

| D1                                                                | 28.00 BSC  |           |      |  |  |  |

| E                                                                 |            | 30.60 BSC |      |  |  |  |

| E1                                                                |            | 28.00 BSC |      |  |  |  |

| L                                                                 | 0.50       | 0.60      | 0.75 |  |  |  |

| L1                                                                | 1.30 REF   |           |      |  |  |  |

| S                                                                 | 0.20       | -         | _    |  |  |  |

| b                                                                 | 0.17       | -         | 0.27 |  |  |  |

| с                                                                 | 0.09       | _         | 0.20 |  |  |  |