Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                        |

|--------------------------------|--------------------------------------------------------|

| Product Status                 | Active                                                 |

| Number of LABs/CLBs            | 288                                                    |

| Number of Logic Elements/Cells | 4608                                                   |

| Total RAM Bits                 | 119808                                                 |

| Number of I/O                  | 158                                                    |

| Number of Gates                | -                                                      |

| Voltage - Supply               | 1.15V ~ 1.25V                                          |

| Mounting Type                  | Surface Mount                                          |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                        |

| Package / Case                 | 256-LBGA                                               |

| Supplier Device Package        | 256-FBGA (17x17)                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c5f256c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Internal Timing                                                                                                                                                                                                                                                                                                                                                                                                         | 5–18                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Cyclone II Clock Timing Parameters                                                                                                                                                                                                                                                                                                                                                                                      |                                               |

| Clock Network Skew Adders                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

| IOE Programmable Delay                                                                                                                                                                                                                                                                                                                                                                                                  | 5–30                                          |

| Default Capacitive Loading of Different I/O Standards                                                                                                                                                                                                                                                                                                                                                                   | 5–31                                          |

| I/O Delays                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

| Maximum Input and Output Clock Rate                                                                                                                                                                                                                                                                                                                                                                                     |                                               |

| High Speed I/O Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                    |                                               |

| External Memory Interface Specifications                                                                                                                                                                                                                                                                                                                                                                                | 5–63                                          |

| JTAG Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

| PLL Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                               | 5–66                                          |

| Duty Cycle Distortion                                                                                                                                                                                                                                                                                                                                                                                                   |                                               |

| DCD Measurement Techniques                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

| Referenced Documents                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                                               |

| Chapter 6. Reference & Ordering Information                                                                                                                                                                                                                                                                                                                                                                             |                                               |

| Software                                                                                                                                                                                                                                                                                                                                                                                                                | 6–1                                           |

| Device Pin-Outs                                                                                                                                                                                                                                                                                                                                                                                                         |                                               |

| Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                                               |

| Section II Clock Management                                                                                                                                                                                                                                                                                                                                                                                             |                                               |

| Section II. Clock Management Revision History                                                                                                                                                                                                                                                                                                                                                                           | 6–1                                           |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 6–1                                           |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 6–1                                           |

| Revision History  Chapter 7. PLLs in Cyclone II Devices                                                                                                                                                                                                                                                                                                                                                                 |                                               |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction                                                                                                                                                                                                                                                                                                                                                   | 7–1                                           |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction  Cyclone II PLL Hardware Overview                                                                                                                                                                                                                                                                                                                 | 7–1<br>7–2                                    |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 7–1<br>7–2<br>7–6                             |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        |                                               |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction  Cyclone II PLL Hardware Overview  PLL Reference Clock Generation  Clock Feedback Modes  Normal Mode                                                                                                                                                                                                                                              |                                               |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode                                                                                                                                                                                                                            |                                               |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode                                                                                                                                                                                                       |                                               |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction  Cyclone II PLL Hardware Overview  PLL Reference Clock Generation  Clock Feedback Modes  Normal Mode  Zero Delay Buffer Mode  No Compensation Mode  Source-Synchronous Mode                                                                                                                                                                       |                                               |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction  Cyclone II PLL Hardware Overview  PLL Reference Clock Generation  Clock Feedback Modes  Normal Mode  Zero Delay Buffer Mode  No Compensation Mode  Source-Synchronous Mode  Hardware Features                                                                                                                                                    |                                               |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction  Cyclone II PLL Hardware Overview  PLL Reference Clock Generation  Clock Feedback Modes  Normal Mode  Zero Delay Buffer Mode  No Compensation Mode  Source-Synchronous Mode  Hardware Features  Clock Multiplication & Division                                                                                                                   |                                               |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle                                                                                                     |                                               |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation                                                                       |                                               |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals                                                       | 7-1                                           |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover                               | 7-1                                           |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover Clocking                      |                                               |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover Clocking Global Clock Network | 7-1                                           |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover Clocking                      | 7-1 7-2 7-1 7-1 7-12 7-14 7-15 7-16 7-20 7-21 |

- 133-MHz PCI-X 1.0 specification compatibility

- High-speed external memory support, including DDR, DDR2, and SDR SDRAM, and QDRII SRAM supported by drop in Altera IP MegaCore functions for ease of use

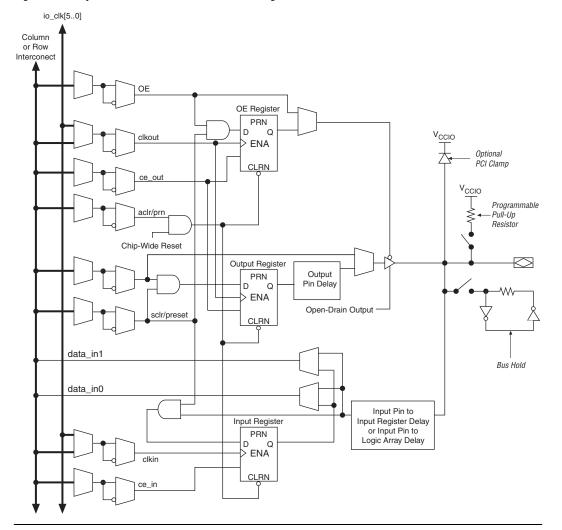

- Three dedicated registers per I/O element (IOE): one input register, one output register, and one output-enable register

- Programmable bus-hold feature

- Programmable output drive strength feature

- Programmable delays from the pin to the IOE or logic array

- I/O bank grouping for unique VCCIO and/or VREF bank settings

- MultiVolt<sup> $\mathbb{M}$ </sup> I/O standard support for 1.5-, 1.8-, 2.5-, and 3.3-interfaces

- Hot-socketing operation support

- Tri-state with weak pull-up on I/O pins before and during configuration

- Programmable open-drain outputs

- Series on-chip termination support

#### Flexible clock management circuitry

- Hierarchical clock network for up to 402.5-MHz performance

- Up to four PLLs per device provide clock multiplication and division, phase shifting, programmable duty cycle, and external clock outputs, allowing system-level clock management and skew control

- Up to 16 global clock lines in the global clock network that drive throughout the entire device

#### Device configuration

- Fast serial configuration allows configuration times less than 100 ms

- Decompression feature allows for smaller programming file storage and faster configuration times

- Supports multiple configuration modes: active serial, passive serial, and JTAG-based configuration

- Supports configuration through low-cost serial configuration devices

- Device configuration supports multiple voltages (either 3.3, 2.5, or 1.8 V)

#### Intellectual property

Altera megafunction and Altera MegaCore function support, and Altera Megafunctions Partners Program (AMPP<sup>SM</sup>) megafunction support, for a wide range of embedded processors, on-chip and off-chip interfaces, peripheral functions, DSP functions, and communications functions and

| Table 2–1. Cyclone II Device Routing Scheme (Part 2 of 2) |                |                    |                          |                 |                  |                 |                  |    |               |                     |     |            |         |

|-----------------------------------------------------------|----------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|----|---------------|---------------------|-----|------------|---------|

|                                                           |                | Destination        |                          |                 |                  |                 |                  |    |               |                     |     |            |         |

| Source                                                    | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | 31 | M4K RAM Block | Embedded Multiplier | PLL | Column 10E | Row IOE |

| LE                                                        | <b>✓</b>       | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |    |               |                     |     |            |         |

| M4K memory<br>Block                                       |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |    |               |                     |     |            |         |

| Embedded<br>Multipliers                                   |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |    |               |                     |     |            |         |

| PLL                                                       |                |                    | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |    |               |                     |     |            |         |

| Column IOE                                                |                |                    |                          |                 |                  | ~               | <b>✓</b>         |    |               |                     |     |            |         |

| Row IOE                                                   |                |                    | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        |                  |    |               |                     |     |            |         |

## Global Clock Network & Phase-Locked Loops

Cyclone II devices provide global clock networks and up to four PLLs for a complete clock management solution. Cyclone II clock network features include:

- Up to 16 global clock networks

- Up to four PLLs

- Global clock network dynamic clock source selection

- Global clock network dynamic enable and disable

#### **Embedded Multiplier Routing Interface**

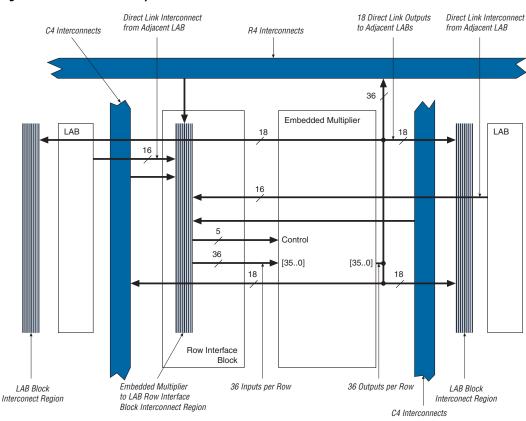

The R4, C4, and direct link interconnects from adjacent LABs drive the embedded multiplier row interface interconnect. The embedded multipliers can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 16 direct link input connections to the embedded multiplier are possible from the left adjacent LABs and another 16 possible from the right adjacent LAB. Embedded multiplier outputs can also connect to left and right LABs through 18 direct link interconnects each. Figure 2–19 shows the embedded multiplier to logic array interface.

Figure 2-19. Embedded Multiplier LAB Row Interface

Figure 2–25. Cyclone II IOE in Bidirectional I/O Configuration

The Cyclone II device IOE includes programmable delays to ensure zero hold times, minimize setup times, or increase clock to output times.

A path in which a pin directly drives a register may require a programmable delay to ensure zero hold time, whereas a path in which a pin drives a register through combinational logic may not require the delay. Programmable delays decrease input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time.

| Table 5–43. Cyclone II I/O Output Delay for Row Pins (Part 1 of 4) |                   |                  |                                |                 |                      |                      |                      |                      |      |

|--------------------------------------------------------------------|-------------------|------------------|--------------------------------|-----------------|----------------------|----------------------|----------------------|----------------------|------|

|                                                                    |                   | Parameter        | Fast (                         | Corner          | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | Unit |

| I/O Standard                                                       | Drive<br>Strength |                  | Industrial<br>/Auto-<br>motive | Commer-<br>cial |                      |                      |                      |                      |      |

| LVTTL                                                              | 4 mA              | t <sub>OP</sub>  | 1343                           | 1408            | 2539                 | 2694                 | 2885                 | 2891                 | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1467                           | 1540            | 2747                 | 2931                 | 3158                 | 3158                 | ps   |

|                                                                    | 8 mA              | t <sub>OP</sub>  | 1198                           | 1256            | 2411                 | 2587                 | 2756                 | 2762                 | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1322                           | 1388            | 2619                 | 2824                 | 3029                 | 3029                 | ps   |

|                                                                    | 12 mA             | t <sub>OP</sub>  | 1156                           | 1212            | 2282                 | 2452                 | 2614                 | 2620                 | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1280                           | 1344            | 2490                 | 2689                 | 2887                 | 2887                 | ps   |

|                                                                    | 16 mA             | t <sub>OP</sub>  | 1124                           | 1178            | 2286                 | 2455                 | 2618                 | 2624                 | ps   |

| 20 mA                                                              |                   | t <sub>DIP</sub> | 1248                           | 1310            | 2494                 | 2692                 | 2891                 | 2891                 | ps   |

|                                                                    | 20 mA             | t <sub>OP</sub>  | 1112                           | 1165            | 2245                 | 2413                 | 2574                 | 2580                 | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1236                           | 1297            | 2453                 | 2650                 | 2847                 | 2847                 | ps   |

|                                                                    | 24 mA             | t <sub>OP</sub>  | 1105                           | 1158            | 2253                 | 2422                 | 2583                 | 2589                 | ps   |

|                                                                    | (1)               | t <sub>DIP</sub> | 1229                           | 1290            | 2461                 | 2659                 | 2856                 | 2856                 | ps   |

| LVCMOS                                                             | 4 mA              | t <sub>OP</sub>  | 1200                           | 1258            | 2231                 | 2396                 | 2555                 | 2561                 | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1324                           | 1390            | 2439                 | 2633                 | 2828                 | 2828                 | ps   |

| 8 mA<br>12 mA<br>(1)                                               | 8 mA              | t <sub>OP</sub>  | 1125                           | 1179            | 2260                 | 2429                 | 2591                 | 2597                 | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1249                           | 1311            | 2468                 | 2666                 | 2864                 | 2864                 | ps   |

|                                                                    |                   | t <sub>OP</sub>  | 1106                           | 1159            | 2217                 | 2383                 | 2543                 | 2549                 | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1230                           | 1291            | 2425                 | 2620                 | 2816                 | 2816                 | ps   |

| 2.5V                                                               | 4 mA              | t <sub>OP</sub>  | 1126                           | 1180            | 2350                 | 2477                 | 2598                 | 2604                 | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1250                           | 1312            | 2558                 | 2714                 | 2871                 | 2871                 | ps   |

|                                                                    | 8 mA              | t <sub>OP</sub>  | 1105                           | 1158            | 2177                 | 2296                 | 2409                 | 2415                 | ps   |

|                                                                    | (1)               | t <sub>DIP</sub> | 1229                           | 1290            | 2385                 | 2533                 | 2682                 | 2682                 | ps   |

The actual half period is then = 3000 ps - 155 ps = 2845 ps

| Table 5–58. Maximum DCD for DDIO Output on Column I/O Pins with PLL in the Clock Path Notes (1), (2) |     |            |     |      |  |  |

|------------------------------------------------------------------------------------------------------|-----|------------|-----|------|--|--|

| Column I/O Pins in the Clock Path                                                                    | C6  | <b>C</b> 7 | C8  | Unit |  |  |

| LVCMOS                                                                                               | 285 | 400        | 445 | ps   |  |  |

| LVTTL                                                                                                | 305 | 405        | 460 | ps   |  |  |

| 2.5-V                                                                                                | 175 | 195        | 285 | ps   |  |  |

| 1.8-V                                                                                                | 190 | 205        | 260 | ps   |  |  |

| 1.5-V                                                                                                | 605 | 645        | 645 | ps   |  |  |

| SSTL-2 Class I                                                                                       | 125 | 210        | 245 | ps   |  |  |

| SSTL-2 Class II                                                                                      | 195 | 195        | 195 | ps   |  |  |

| SSTL-18 Class I                                                                                      | 130 | 240        | 245 | ps   |  |  |

| SSTL-18 Class II                                                                                     | 135 | 270        | 330 | ps   |  |  |

| HSTL-18 Class I                                                                                      | 135 | 240        | 240 | ps   |  |  |

| HSTL-18 Class II                                                                                     | 165 | 240        | 285 | ps   |  |  |

| HSTL-15 Class I                                                                                      | 220 | 335        | 335 | ps   |  |  |

| HSTL-15 Class II                                                                                     | 190 | 210        | 375 | ps   |  |  |

| Differential SSTL-2 Class I                                                                          | 125 | 210        | 245 | ps   |  |  |

| Differential SSTL-2 Class II                                                                         | 195 | 195        | 195 | ps   |  |  |

| Differential SSTL-18 Class I                                                                         | 130 | 240        | 245 | ps   |  |  |

| Differential SSTL-18 Class II                                                                        | 132 | 270        | 330 | ps   |  |  |

| Differential HSTL-18 Class I                                                                         | 135 | 240        | 240 | ps   |  |  |

| Differential HSTL-18 Class II                                                                        | 165 | 240        | 285 | ps   |  |  |

| Differential HSTL-15 Class I                                                                         | 220 | 335        | 335 | ps   |  |  |

| Differential HSTL-15 Class II                                                                        | 190 | 210        | 375 | ps   |  |  |

| LVDS                                                                                                 | 110 | 120        | 125 | ps   |  |  |

| Simple RSDS                                                                                          | 125 | 125        | 275 | ps   |  |  |

| Missi LV/DO                                                                                          |     |            | 405 |      |  |  |

#### *Notes to Table 5–58:*

Mini-LVDS

110

120

125

ps

<sup>(1)</sup> The DCD specification is characterized using the maximum drive strength available for each I/O standard.

<sup>(2)</sup> Numbers are applicable for commercial, industrial, and automotive devices.

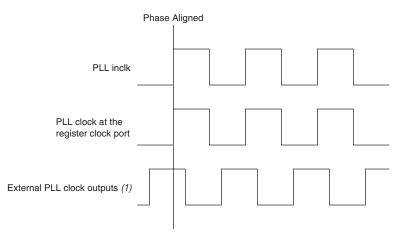

Figure 7–4. Phase Relationship between Cyclone II PLL Clocks in Normal Mode

Note to Figure 7-4:

(1) The external clock output can lead or lag the PLL clock signals.

### **Zero Delay Buffer Mode**

In zero delay buffer mode, the clock signal on the PLL external clock output pin (PLL<#>\_OUT), fed by the c2 counter, is phase-aligned with the PLL input clock pin for zero delay. If the c[1..0] ports drive internal clock ports, there is a phase shift with respect to the input clock pin. Figure 7–5 shows an example waveform of the PLL clocks' phase relationship in this mode.

Figure 7–7. Phase Relationship between Cyclone II PLL Clocks in Source-Synchronous Compensation Mode

Set the input pin to the register delay chain within the IOE to zero in the Quartus II software for all data pins clocked by a source-synchronous mode PLL.

### Hardware **Features**

Cyclone II device PLLs support a number of features for general-purpose clock management. This section discusses clock multiplication and division implementation, phase-shifting implementation and PLL lock circuits.

### **Clock Multiplication & Division**

Cyclone II device PLLs provide clock synthesis for PLL output ports using  $m/(n \times post\text{-scale})$  scaling factors. Every PLL has one pre-scale divider, n, with a range of 1 to 4 and one multiply counter, m, with a range of 1 to 32. The input clock,  $f_{IN}$ , is divided by a pre-scale counter, n, to produce the input reference clock, f<sub>REF</sub>, to the PFD. This input reference clock,  $\mathbf{f}_{\text{REF}}$  is then multiplied by the m feedback factor. The control loop drives the VCO frequency to match  $f_{IN} \times (m/n)$ . The equations for these frequencies are:

$$f_{REF} = \frac{f_{IN}}{n}$$

$$f_{VCO} = f_{REF} \times m = f_{IN} \frac{m}{n}$$

outputs, respectively. When the output registers are bypassed, the new data is available on the rising edge of the same clock cycle on which it was written. See "Read-During-Write Operation at the Same Address" on page 8–28 for waveforms and information on mixed-port read-during-write mode.

Potential write contentions must be resolved external to the RAM because writing to the same address location at both ports results in unknown data storage at that location.

For the maximum synchronous write cycle time, refer to the *Cyclone II Device Family Data Sheet* in volume 1 of the *Cyclone II Device Handbook*.

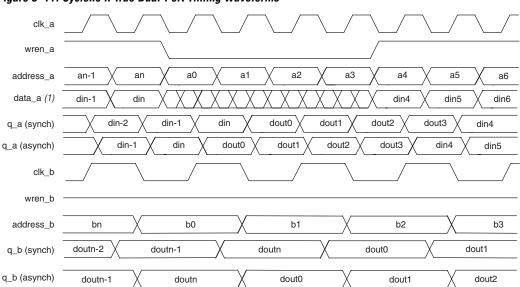

Figure 8–11 shows true dual-port timing waveforms for the write operation at port A and the read operation at port B.

Figure 8–11. Cyclone II True Dual-Port Timing Waveforms

*Note to Figure 8–11:*

The crosses in the data\_a waveform during write indicate "don't care."

### Shift Register Mode

Cyclone II memory blocks can implement shift registers for digital signal processing (DSP) applications, such as finite impulse response (FIR) filters, pseudo-random number generators, multi-channel filtering, and auto-correlation and cross-correlation functions. These and other DSP

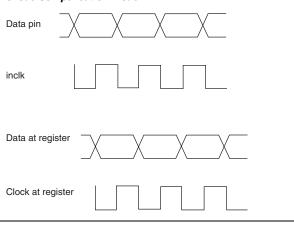

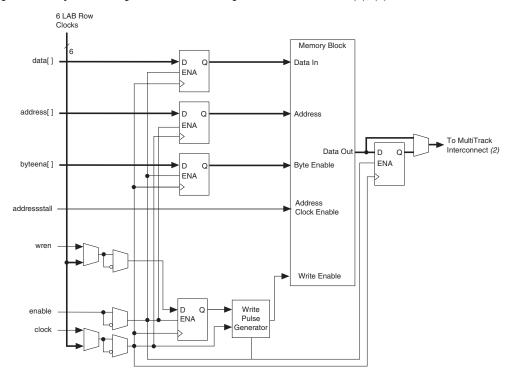

Figure 8–20. Cyclone II Single-Clock Mode in Single-Port Mode Notes (1), (2)

Notes to Figure 8-20:

- (1) Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

- (2) See the Cyclone II Device Family Data Sheet in Volume 1 of the Cyclone II Device Handbook for more information on the MultiTrack interconnect.

### **Power-Up Conditions & Memory Initialization**

The Cyclone II memory block outputs always power-up to zero, regardless of whether the output registers are used or bypassed. Even if an MIF pre-loads the contents of the memory block, the outputs still power up cleared. For example, if address 0 is pre-initialized to FF, M4K blocks power up with the output at 00. A subsequent read after power up from address 0 outputs the pre-initialized value of FF.

For example, to implement a 72-bit wide SDRAM memory interface in Cyclone II devices, use 5 DQS/DQ groups in the top I/O bank and 4 DQS/DQ groups in the bottom I/O bank, or vice-versa. In this case, if DQS0T or DQS1T is used for the fifth DQS signal, the DQS2R or DQS2L pins become regular I/O pins and are unavailable for DQS signals in memory interface. For detailed information about the global clock network, refer to the Global Clock Network & Phase Locked Loops section in the Cyclone II Architecture chapter of the Cyclone II Device Handbook.

You must configure the DQ and DQS pins as bidirectional DDR pins on all the I/O banks of the device. Use the altdq and altdqs megafunctions to configure the DQ and DQS paths, respectively. If you only want to use the DQ or DQS pins as inputs, for instance in the QDRII memory interface where DQ and DQS are unidirectional read data and read clock, set the output enable of the DQ or DQS pins to ground. For further information, please refer to the section "QDRII SRAM" on page 9–5 of this handbook.

### Clock, Command & Address Pins

You can use any of the user I/O pins on all the I/O banks (that support the external memory's I/O standard) of the device to generate clocks and command and address signals to the memory device.

### Parity, DM & ECC Pins

You can use any of the DQ pins for the parity pins in Cyclone II devices. Cyclone II devices support parity in the  $\times 8/\times 9$  and  $\times 16/\times 18$  modes. There is one parity bit available per 8 bits of data pins.

The data mask (DM) pins are required when writing to DDR SDRAM and DDR2 SDRAM devices. A low signal on the DM pin indicates that the write is valid. If the DM signal is high, the memory masks the DQ signals. In Cyclone II devices, the DM pins are pre-assigned in the device pin outs, and these are the preferred pins. Each group of DQS and DQ signals requires a DM pin. Similar to the DQ output signals, the DM signals are clocked by the  $-90^{\circ}$  shifted clock.

Some DDR SDRAM and DDR2 SDRAM devices support error correction coding (ECC) or parity. Parity bit checking is a way to detect errors, but it has no correction capabilities. ECC can detect and automatically correct errors in data transmission. In 72-bit DDR SDRAM, there are 8 ECC pins on top of the 64 data pins. Connect the DDR and DDR2 SDRAM ECC pins to a Cyclone II device's DQS/DQ group. The memory controller needs extra logic to encode and decode the ECC data.

Figure 10-10. Differential SSTL-18 Class II Termination

#### 1.8-V Pseudo-Differential HSTL Class I and II

The 1.8-V differential HSTL specification is the same as the 1.8-V single-ended HSTL specification. It is used for applications designed to operate in the 0.0 to 1.8-V HSTL logic switching range such as QDR memory clock interfaces. Cyclone II devices support both input and output levels. Refer to Figures 10–11 and 10–12 for details on 1.8-V differential HSTL termination.

Cyclone II devices do not support true 1.8-V differential HSTL standards. Cyclone II devices support pseudo-differential HSTL outputs for PLL\_OUT pins and pseudo-differential HSTL inputs for clock pins. Pseudo-differential inputs require an input reference voltage as opposed to the true differential inputs. Refer to Table 10–1 on page 10–2 for information about pseudo-differential HSTL.

Figure 10–11. 1.8-V Differential HSTL Class I Termination

Figure 11-11. LVPECL I/O Interface

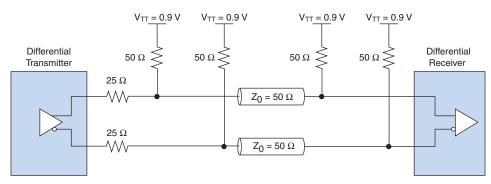

#### **Differential SSTL Support in Cyclone II Devices**

The differential SSTL I/O standard is a memory bus standard used for applications such as high-speed double data rate (DDR) SDRAM interfaces. The differential SSTL I/O standard is similar to voltage referenced SSTL and requires two differential inputs with an external termination voltage (V $_{\rm TT}$ ) of 0.5  $\times$  V $_{\rm CCIO}$  to which termination resistors are connected. A 2.5-V output source voltage is required for differential SSTL-2, while a 1.8-V output source voltage is required for differential SSTL-18. The differential SSTL output standard is only supported at PLLCLKOUT pins using two single-ended SSTL output buffers programmed to have opposite polarity.

The differential SSTL input standard is supported at the global clock (GCLK) pins only, treating differential inputs as two single-ended SSTL, and only decoding one of them.

For SSTL signaling characteristics, see the *DC Characteristics & Timing Specification* chapter and the *Selectable I/O Standards in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

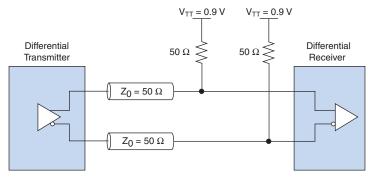

Figures 11–12 and 11–13 show the differential SSTL class I and II interfaces, respectively.

Figure 13–1. Enabling Compression for Cyclone II Bitstreams in Compiler Settings

You can also use the following steps to enable compression when creating programming files from the Convert Programming Files window.

- 1. Click **Convert Programming Files** (File menu).

- 2. Select the Programming File type. Only Programmer Object Files (.pof), SRAM HEXOUT, RBF, or TTF files support compression.

- 3. For POFs, select a configuration device.

- 4. Select **Add File** and add a Cyclone II SRAM Object File(s) (.sof).

- 5. Select the name of the file you added to the SOF Data area and click on **Properties**.

- 6. Check the **Compression** check box.

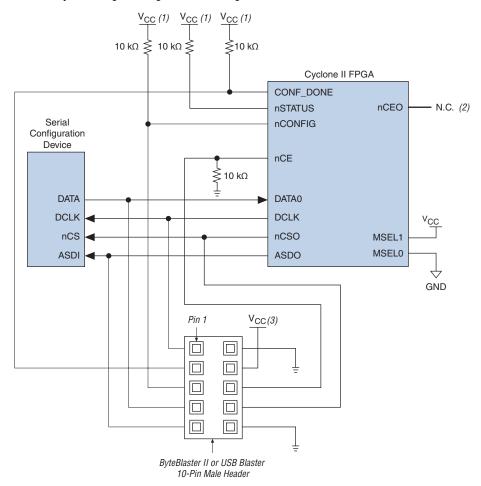

Figure 13–7. In-System Programming of Serial Configuration Devices

*Notes to Figure 13–7:*

- (1) Connect these pull-up resistors to 3.3-V supply.

- (2) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

- (3) Power up the ByteBlaster II or USB Blaster cable's V<sub>CC</sub> with a 3.3-V supply.

You can use the Quartus II software with the APU and the appropriate configuration device programming adapter to program serial configuration devices. All serial configuration devices are offered in an 8-pin or 16-pin small outline integrated circuit (SOIC) package and can be programmed using the PLMSEPC-8 adapter.

Quartus II programmer and a download cable. Figure 13–19 shows the PS configuration for Cyclone II devices using a USB-Blaster, MasterBlaster, ByteBlaster II or ByteBlasterMV cable.

10 kΩ V<sub>CC</sub> (1) **≤**10 kΩ ≤10 kΩ Cyclone II Device CONF DONE MSEL0 USB-Blaster, ByteBlaster II, MSEL1 MasterBlaster. nCEO - N.C. (4) nCE or ByteBlasterMV 10-Pin Male Header DCI K Pin 1 DATA0 **nCONFIG** VIO (3) 回

Figure 13-19. PS Configuration Using a USB-Blaster, MasterBlaster, ByteBlaster II or ByteBlasterMV Cable

#### Notes to Figure 13-19:

- (1) The pull-up resistor should be connected to the same supply voltage as the USB-Blaster, MasterBlaster (VIO pin), ByteBlaster II, or ByteBlasterMV cable.

- (2) The pull-up resistors on DATAO and DCLK are only needed if the download cable is the only configuration scheme used on your board. This is to ensure that DATAO and DCLK are not left floating after configuration. For example, if you are also using a configuration device, the pull-up resistors on DATAO and DCLK are not needed.

- (3) Pin 6 of the header is a V<sub>IO</sub> reference voltage for the MasterBlaster output driver. V<sub>IO</sub> should match the device's V<sub>CCIO</sub>. Refer to the MasterBlaster Serial/USB Communications Cable Data Sheet for this value. In the ByteBlasterMV, this pin is a no connect. In the USB-Blaster and ByteBlaster II, this pin is connected to nCE when it is used for AS programming, otherwise it is a no connect.

- (4) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

You can use a download cable to configure multiple Cyclone II devices by connecting each device's nCEO pin to the subsequent device's nCE pin. Connect the first Cyclone II device's nCE pin to GND and connect its nCEO pin to the nCE pin of the next device in the chain. Use an external 10-k $\Omega$  pull-up resistor to pull the nCEO pin high to  $V_{CCIO}$  when it feeds next device's nCE pin. Connect all other configuration pins (nCONFIG, nSTATUS, DCLK, DATAO, and CONF\_DONE) on every device in the chain together. Because all CONF\_DONE pins are connected, all devices in the chain initialize and enter user mode at the same time.

Shield GND When designing a Cyclone II board for JTAG configuration, use the guidelines in Table 13–10 for the placement of the dedicated configuration pins.

| Table 13–10. Dedicated Configuration Pin Connections During JTAG<br>Configuration |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Signal                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| nCE                                                                               | On all Cyclone II devices in the chain, $nCE$ should be driven low by connecting it to ground, pulling it low via a resistor, or driving it by some control circuitry. For devices that are also in multiple device AS, or PS configuration chains, the $nCE$ pins should be connected to GND during JTAG configuration or JTAG configured in the same order as the configuration chain.                                                         |  |  |  |  |

| nCEO                                                                              | On all Cyclone II devices in the chain, nCEO can be used as a user I/O or connected to the nCE of the next device. If nCEO is connected to the nCE of the next device, the nCEO pin must be pulled high to $V_{\text{CCIO}}$ by an external 10-k $\Omega$ pull-up resistor to help the internal weak pull-up resistor. If the nCEO pin is not connected to the nCE pin of the next device, you can use it as a user I/O pin after configuration. |  |  |  |  |

| MSEL                                                                              | These pins must not be left floating. These pins support whichever non-JTAG configuration is used in production. If only JTAG configuration is used, you should tie these pins to ground.                                                                                                                                                                                                                                                        |  |  |  |  |

| nCONFIG                                                                           | Driven high by connecting to $V_{\rm CC}$ , pulling up via a resistor, or driven high by some control circuitry.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| nSTATUS                                                                           | Pull to $V_{CC}$ via a 10-k $\Omega$ resistor. When configuring multiple devices in the same JTAG chain, each <code>nSTATUS</code> pin should be pulled up to $V_{CC}$ individually. <code>nSTATUS</code> pulling low in the middle of JTAG configuration indicates that an error has occurred.                                                                                                                                                  |  |  |  |  |

| CONF_DONE                                                                         | Pull to $V_{CC}$ via a 10-k $\Omega$ resistor. When configuring multiple devices in the same JTAG chain, each CONF_DONE pin should be pulled up to $V_{CC}$ individually. CONF_DONE going high at the end of JTAG configuration indicates successful configuration.                                                                                                                                                                              |  |  |  |  |

| DCLK                                                                              | Should not be left floating. Drive low or high, whichever is more convenient on your board.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

Figure 13–23 shows JTAG configuration of a Cyclone II device with a microprocessor.

Cyclone II FPGA Memory nCE (3) DATA ADDR (4) nCEO MSEL1 nCONFIG MSEL0 (2) -DATA0 ≥10 kΩ **DCLK** TDI **≶**10 kΩ **TCK** Microprocessor TDO **TMS nSTATUS** CONF DONE

Figure 13–23. JTAG Configuration of a Single Device Using a Microprocessor

Notes to Figure 13-23:

- The pull-up resistor should be connected to a supply that provides an acceptable input signal for all devices in the chain.

- (2) Connect the nconfig and MSEL[1..0] pins to support a non-JTAG configuration scheme. If only JTAG configuration is used, connect the nconfig pin to  $V_{CC}$ , and the MSEL[1..0] pins to ground. In addition, pull DCLK and DATAO to either high or low, whichever is convenient on your board.

- (3) nCE must be connected to GND or driven low for successful JTAG configuration.

- (4) If using an EPCS4 or EPCS1 device, set MSEL [1..0] to 00. See Table 13–4 for more details.

#### JTAG Configuration of Multiple Devices

When programming a JTAG device chain, one JTAG-compatible header is connected to several devices. The number of devices in the JTAG chain is limited only by the drive capability of the download cable. When four or more devices are connected in a JTAG chain, Altera recommends buffering the TCK, TDI, and TMS pins with an on-board buffer.

JTAG-chain device programming is ideal when the system contains multiple devices, or when testing your system using JTAG BST circuitry. Figure 13–24 shows multiple device JTAG configuration.