### Intel - EP2C5Q208C8N Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detailo                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 288                                                     |

| Number of Logic Elements/Cells | 4608                                                    |

| Total RAM Bits                 | 119808                                                  |

| Number of I/O                  | 142                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 208-BFQFP                                               |

| Supplier Device Package        | 208-PQFP (28x28)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c5q208c8n |

|                                |                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ]   | nternal Timing                                        | 5-18 |

|-----|-------------------------------------------------------|------|

| (   | Cyclone II Clock Timing Parameters                    | 5-23 |

|     | Clock Network Skew Adders                             |      |

| ]   | OE Programmable Delay                                 | 5-30 |

|     | Default Capacitive Loading of Different I/O Standards |      |

|     | /O Delays                                             |      |

| l   | Maximum Input and Output Clock Rate                   | 5-46 |

|     | High Speed I/O Timing Specifications                  |      |

|     | External Memory Interface Specifications              |      |

| J   | TAG Timing Specifications                             | 5-64 |

| j   | PLL Timing Specifications                             | 5-66 |

|     | y Cycle Distortion                                    |      |

|     | DCD Measurement Techniques                            |      |

|     | erenced Documents                                     |      |

| Doc | cument Revision History                               | 5-74 |

|     |                                                       |      |

# Chapter 6. Reference & Ordering Information

| Software                  | <b>)</b> –1 |

|---------------------------|-------------|

| Device Pin-Outs           |             |

| Ordering Information      | -1          |

| Document Revision History |             |

|                           | -           |

# Section II. Clock Management

| Revision History |  | 6– | -1 |

|------------------|--|----|----|

|------------------|--|----|----|

# Chapter 7. PLLs in Cyclone II Devices

| Introduction                                 | 7–1  |

|----------------------------------------------|------|

| Cyclone II PLL Hardware Overview             | 7–2  |

| PLL Reference Clock Generation               | 7–6  |

| Clock Feedback Modes                         | 7–10 |

| Normal Mode                                  | 7–10 |

| Zero Delay Buffer Mode                       | 7–11 |

| No Compensation Mode                         | 7–12 |

| Source-Synchronous Mode                      |      |

| Hardware Features                            |      |

| Clock Multiplication & Division              | 7–14 |

| Programmable Duty Cycle                      |      |

| Phase-Shifting Implementation                |      |

| Control Signals                              | 7–17 |

| Manual Clock Switchover                      |      |

| Clocking                                     | 7–21 |

| Global Clock Network                         | 7–21 |

| Clock Control Block                          | 7–24 |

| Global Clock Network Clock Source Generation | 7–26 |

| Global Clock Network Power Down              | 7–28 |

The Quartus II Compiler automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 16 LEs by automatically linking LABs in the same column. For enhanced fitting, a long carry chain runs vertically, which allows fast horizontal connections to M4K memory blocks or embedded multipliers through direct link interconnects. For example, if a design has a long carry chain in a LAB column next to a column of M4K memory blocks, any LE output can feed an adjacent M4K memory block through the direct link interconnect. Whereas if the carry chains ran horizontally, any LAB not next to the column of M4K memory blocks would use other row or column interconnects to drive a M4K memory block. A carry chain continues as far as a full column. The direct link interconnect allows an LAB, M4K memory block, or embedded multiplier block to drive into the local interconnect of its left and right neighbors. Only one side of a PLL block interfaces with direct link and row interconnects. The direct link interconnect provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

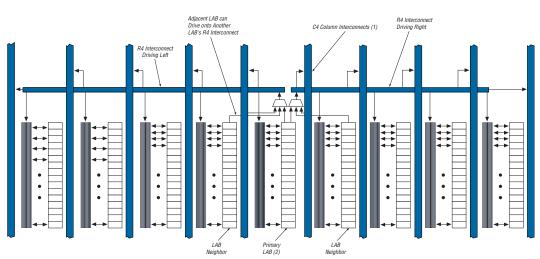

The R4 interconnects span four LABs, three LABs and one M4K memory block, or three LABs and one embedded multiplier to the right or left of a source LAB. These resources are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–8 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by LABs, M4K memory blocks, embedded multipliers, PLLs, and row IOEs. For LAB interfacing, a primary LAB or LAB neighbor (see Figure 2–8) can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnect. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. Additionally, R4 interconnects can drive R24 interconnects, C4, and C16 interconnects for connections from one row to another.

#### Notes to Figure 2–8:

(1) C4 interconnects can drive R4 interconnects.

(2) This pattern is repeated for every LAB in the LAB row.

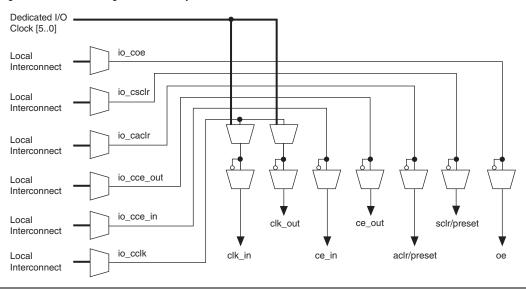

Figure 2–24. Control Signal Selection per IOE

In normal bidirectional operation, you can use the input register for input data requiring fast setup times. The input register can have its own clock input and clock enable separate from the OE and output registers. You can use the output register for data requiring fast clock-to-output performance. The OE register is available for fast clock-to-output enable timing. The OE and output register share the same clock source and the same clock enable source from the local interconnect in the associated LAB, dedicated I/O clocks, or the column and row interconnects. All registers share sclr and aclr, but each register can individually disable sclr and aclr. Figure 2–25 shows the IOE in bidirectional configuration.

#### EP2C70 Clock Timing Parameters

Tables 5–33 and 5–34 show the clock timing parameters for EP2C70 devices.

| Table 5–33. EP2C70 Column Pins Global Clock Timing Parameters |            |            |          |          |          |      |  |  |

|---------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|

| Parameter                                                     | Fast (     | Corner     | –6 Speed | –7 Speed | –8 Speed | Unit |  |  |

| Farameter                                                     | Industrial | Commercial | Grade    | Grade    | Grade    | UIII |  |  |

| t <sub>CIN</sub>                                              | 1.575      | 1.651      | 2.914    | 3.105    | 3.174    | ns   |  |  |

| t <sub>COUT</sub>                                             | 1.589      | 1.666      | 2.948    | 3.137    | 3.203    | ns   |  |  |

| t <sub>PLLCIN</sub>                                           | -0.149     | -0.158     | 0.27     | 0.268    | 0.089    | ns   |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.135     | -0.143     | 0.304    | 0.3      | 0.118    | ns   |  |  |

| Table 5–34. EP2C70 Row Pins Global Clock Timing Parameters |            |            |                   |                   |                   |      |  |  |

|------------------------------------------------------------|------------|------------|-------------------|-------------------|-------------------|------|--|--|

| Davamatar                                                  | Fast       | Corner     | –6 Speed<br>Grade | –7 Speed<br>Grade | –8 Speed<br>Grade | Unit |  |  |

| Parameter                                                  | Industrial | Commercial |                   |                   |                   |      |  |  |

| t <sub>CIN</sub>                                           | 1.463      | 1.533      | 2.753             | 2.927             | 3.010             | ns   |  |  |

| t <sub>cout</sub>                                          | 1.465      | 1.535      | 2.769             | 2.940             | 3.018             | ns   |  |  |

| t <sub>PLLCIN</sub>                                        | -0.261     | -0.276     | 0.109             | 0.09              | -0.075            | ns   |  |  |

| t <sub>PLLCOUT</sub>                                       | -0.259     | -0.274     | 0.125             | 0.103             | -0.067            | ns   |  |  |

### **Clock Network Skew Adders**

Table 5–35 shows the clock network specifications.

| Table 5–35. Clock Network Specifications                   |                                                |      |    |  |  |  |

|------------------------------------------------------------|------------------------------------------------|------|----|--|--|--|

| Name                                                       | Max                                            | Unit |    |  |  |  |

| Clock skew adder                                           | Inter-clock network, same bank                 | ±88  | ps |  |  |  |

| EP2C5/A, EP2C8/A (1)                                       | Inter-clock network, same side and entire chip | ±88  | ps |  |  |  |

| Clock skew adder                                           | Inter-clock network, same bank                 | ±118 | ps |  |  |  |

| EP2C15A, EP2C20/A,<br>EP2C35, EP2C50,<br>EP2C70 <i>(1)</i> | Inter-clock network, same side and entire chip | ±138 | ps |  |  |  |

#### Note to Table 5–35:

(1) This is in addition to intra-clock network skew, which is modeled in the Quartus II software.

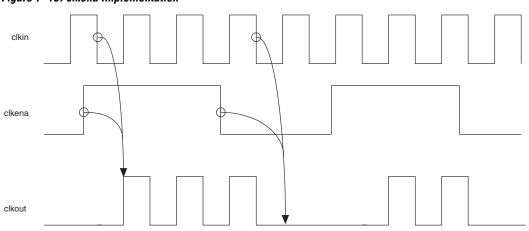

Figure 7–15. clkena Implementation

The clkena signal can also disable clock outputs if the system is not tolerant to frequency overshoot during PLL resynchronization.

Altera recommends using the clkena signals when switching the clock source to the PLLs or the global clock network. The recommended sequence to be followed is:

- 1. Disable the primary output clock by de-asserting the clkena signal.

- 2. Switch to the secondary clock using the dynamic select signals of the clock control block.

- 3. Allow some clock cycles of the secondary clock to pass before re-asserting the clkena signal. The exact number of clock cycles you need to wait before enabling the secondary clock is design dependent. You can build custom logic to ensure glitch-free transition when switching between different clock sources.

# **Board Layout** The PLL circuits in Cyclone II devices contain analog components embedded in a digital device. These analog components have separate power and ground pins to minimize noise generated by the digital components.

| Table 8–2. Number of M4K Blocks in Cyclone II Devices (Part 2 of 2) |     |         |  |  |  |

|---------------------------------------------------------------------|-----|---------|--|--|--|

| Device M4K Blocks Total RAM Bits                                    |     |         |  |  |  |

| EP2C50                                                              | 129 | 594,432 |  |  |  |

| EP2C70 250 1,152,000                                                |     |         |  |  |  |

# **Control Signals**

Figure 8–1 shows how the register clocks, clears, and control signals are implemented in the Cyclone II memory block.

The clock enable control signal controls the clock entering the entire memory block, not just the input and output registers. The signal disables the clock so that the memory block does not see any clock edges and will not perform any operations.

Cyclone II devices do not support asynchronous clear signals to input registers. Only output registers support asynchronous clears. There are three ways to reset the registers in the M4K blocks: power up the device, use the aclr signal for output register only, or assert the device-wide reset signal using the DEV\_CLRn option.

When applied to output registers, the asynchronous clear signal clears the output registers and the effects are seen immediately.

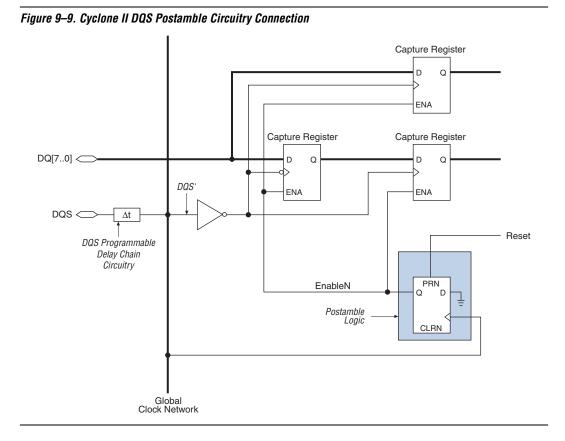

Figure 9–10 shows the timing waveform for Figure 9–9. When the postamble logic detects the falling DQS edge at the start of postamble, it sends out a signal to disable the capture registers to prevent any accidental latching.

## 1.5-V Pseudo-Differential HSTL Class I and II

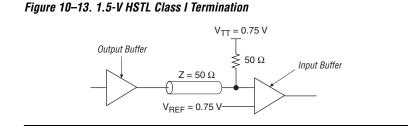

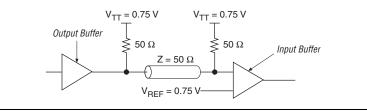

The 1.5-V differential HSTL standard is formulated under EIA/JEDEC Standard, EIA/JESD8-6: A 1.5V Output Buffer Supply Voltage Based Interface Standard for Digital Integrated Circuits.

The 1.5-V differential HSTL specification is the same as the 1.5-V single-ended HSTL specification. It is used for applications designed to operate in the 0.0- to 1.5-V HSTL logic switching range, such as QDR memory clock interfaces. Cyclone II devices support both input and output levels. Refer to Figures 10–15 and 10–16 for details on the 1.5-V differential HSTL termination.

Cyclone II devices do not support true 1.5-V differential HSTL standards. Cyclone II devices support pseudo-differential HSTL outputs for PLL\_OUT pins and pseudo-differential HSTL inputs for clock pins. Pseudo-differential inputs require an input reference voltage as opposed to the true differential inputs. Refer to Table 10–1 on page 10–2 for information about pseudo-differential HSTL.

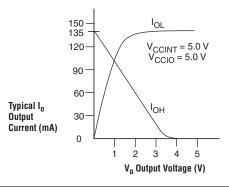

As shown above,  $R_1 = 5.0$ -V/135 mA.

$\label{eq:shown in data sheets usually reflect typical operating conditions. Subtract 20% from the data sheet value for guard band. This subtraction when applied in the example in Figure 10–22 gives R1 a value of 30 <math display="inline">\Omega$

$R_2$  should be selected so that it does not violate the driving device's  $I_{OH}$  specification. For example, if the device has a maximum  $I_{OH}$  of 8 mA, given that the PCI clamping diode,  $V_{\rm IN} = V_{\rm CCIO} + 0.7 - V = 3.7 - V$ , and the maximum supply load of a 5.0-V device ( $V_{\rm CC}$ ) is 5.25-V, the value of  $R_2$  can be calculated as follows:

$$R_2 = (5.25 \text{ V} - 3.7 \text{ V}) - (8 \text{ mA} \times 30 \Omega) = 164 \Omega$$

8 mA

This analysis assumes worst case conditions. If your system does not have a wide variation in voltage-supply levels, you can adjust these calculations accordingly.

Because 5.0-V device tolerance in Cyclone II devices requires use of the PCI clamp, and this clamp is activated during configuration, 5.0-V signals may not be driven into the device until it is configured.

# Conclusion

Cyclone II device I/O capabilities enable you to keep pace with increasing design complexity utilizing a low-cost FPGA device family. Support for I/O standards including SSTL and LVDS compatibility allow Cyclone II devices to fit into a wide variety of applications. The Quartus II

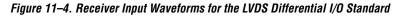

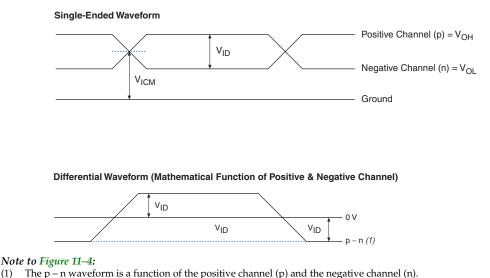

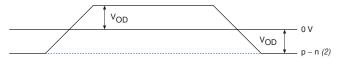

#### Figure 11–5. Transmitter Output Waveform for the LVDS Differential I/O Standard Note (2)

#### Notes to Figure 11–5:

(1)

The V<sub>OD</sub> specifications apply at the resistor network output. (1)

The p - n waveform is a function of the positive channel (p) and the negative channel (n). (2)

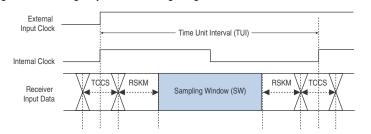

Table 11–5 defines the parameters of the timing diagram shown in Figure 11–16. Figure 11–17 shows the Cyclone II high-speed I/O timing budget.

| Table 11–5. High-Speed I/O Timing Definitions |        |                                                                                                                                                                                                                                       |  |  |  |

|-----------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter                                     | Symbol | Description                                                                                                                                                                                                                           |  |  |  |

| Transmitter channel-to-<br>channel skew (1)   | TCCS   | The timing difference between the fastest and slowest output edges, including $t_{\rm CO}$ variation and clock skew. The clock is included in the TCCS measurement.                                                                   |  |  |  |

| Sampling window                               | SW     | The period of time during which the data must be valid in order for you to capture it correctly. The setup and hold times determine the ideal strobe position within the sampling window.<br>$T_{SW} = T_{SU} + T_{hd} + PLL$ jitter. |  |  |  |

| Receiver input skew margin                    | RSKM   | RSKM is defined by the total margin left after accounting for the sampling window and TCCS. The RSKM equation is: RSKM = (TUI $-$ SW $-$ TCCS) / 2.                                                                                   |  |  |  |

| Input jitter tolerance (peak-<br>to-peak)     |        | Allowed input jitter on the input clock to the PLL that is tolerable while maintaining PLL lock.                                                                                                                                      |  |  |  |

| Output jitter (peak-to-peak)                  |        | Peak-to-peak output jitter from the PLL.                                                                                                                                                                                              |  |  |  |

#### Note to Table 11–5:

The TCCS specification applies to the entire bank of LVDS as long as the SERDES logic are placed within the LAB adjacent to the output pins.

#### Figure 11–16. High-Speed I/O Timing Diagram

# Section VI. Configuration & Test

This section provides configuration information for all of the supported configuration schemes for Cyclone<sup>®</sup> II devices. These configuration schemes use either a microprocessor, configuration device, or download cable. There is detailed information on how to design with Altera<sup>®</sup> configuration devices. The last chapter provides information on JTAG support in Cyclone II devices.

This section includes the following chapters:

- Chapter 13, Configuring Cyclone II Devices

- Chapter 14, IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices

# **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

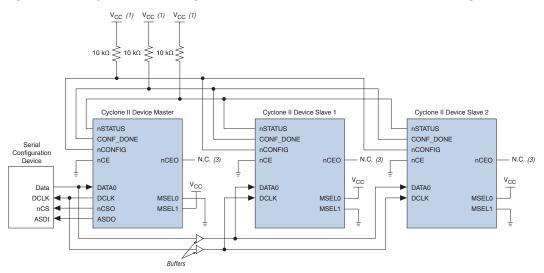

#### Single SOF

The second method configures both the master and slave Cyclone II devices with the same SOF. The serial configuration device stores one copy of the SOF file. This setup is shown in Figure 13–6 where the master is setup in AS mode, and the slave devices are setup in PS mode (MSEL=01). You could setup one or more slave devices in the chain and all the slave devices are setup in the same way as shown in Figure 13–6.

Figure 13–6. Multiple Device AS Configuration When FPGAs Receive the Same Data with a Single SOF

#### Notes to Figure 13–6:

(2) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed another device's nCE pin.

In this setup, all the Cyclone II devices in the chain are connected for concurrent configuration. This can reduce the AS configuration time because all the Cyclone II devices are configured in one configuration cycle. Connect the nCE input pins of all the Cyclone II devices to ground. You can either leave the nCEO output pins on all the Cyclone II devices unconnected or use the nCEO output pins as normal user I/O pins. The DATA and DCLK pins are connected in parallel to all the Cyclone II devices.

<sup>(1)</sup> Connect the pull-up resistors to a 3.3-V supply.

٦

When designing a Cyclone II board for JTAG configuration, use the guidelines in Table 13–10 for the placement of the dedicated configuration pins.

Г

| Signal    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| nCE       | On all Cyclone II devices in the chain, nCE should be driven<br>low by connecting it to ground, pulling it low via a resistor, or<br>driving it by some control circuitry. For devices that are also in<br>multiple device AS, or PS configuration chains, the nCE pins<br>should be connected to GND during JTAG configuration or<br>JTAG configured in the same order as the configuration chain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| nCEO      | DTAG contigured in the same order as the configuration characteristic of the same order as the configuration characteristic of the number of |  |  |  |  |  |

| MSEL      | These pins must not be left floating. These pins support<br>whichever non-JTAG configuration is used in production.<br>only JTAG configuration is used, you should tie these pin<br>ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| nCONFIG   | Driven high by connecting to V <sub>CC</sub> , pulling up via a resistor, or driven high by some control circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| nSTATUS   | Pull to $V_{CC}$ via a 10-k $\Omega$ resistor. When configuring multiple devices in the same JTAG chain, each <code>nSTATUS</code> pin should be pulled up to $V_{CC}$ individually. <code>nSTATUS</code> pulling low in the middle of JTAG configuration indicates that an error has occurred.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| CONF_DONE | Pull to $V_{CC}$ via a 10-k $\Omega$ resistor. When configuring multiple devices in the same JTAG chain, each CONF_DONE pin should be pulled up to $V_{CC}$ individually. CONF_DONE going high at the end of JTAG configuration indicates successful configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| DCLK      | Should not be left floating. Drive low or high, whichever is more convenient on your board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

Figure 13–23 shows JTAG configuration of a Cyclone II device with a microprocessor.

### **Combining JTAG & Active Serial Configuration Schemes**

You can combine the AS configuration scheme with JTAG-based configuration. Set the MSEL[1..0] pins to 00 (AS mode) or 10 (Fast AS mode) in this setup, which uses two 10-pin download cable headers on the board. The first header programs the serial configuration device in the system via the AS programming interface, and the second header configures the Cyclone II directly via the JTAG interface.

If you try configuring the device using both schemes simultaneously, JTAG configuration takes precedence and AS configuration is terminated.

When a blank serial configuration device is attached to Cyclone II device, turn on the **Halt on-chip configuration controller** option under the Tools menu by clicking **Options**. The Options dialog box appears. In the **Category** list, select **Programmer** before starting the JTAG configuration with the Quartus II programmer. This option stops the AS reconfiguration loop from a blank serial configuration device before starting the JTAG configuration. This includes using the Serial Flash Loader IP because JTAG is used for configuring the Cyclone II device. Users do not need to recompile their Quartus II designs after turning on this Option.

# Programming Serial Configuration Devices In-System Using the JTAG Interface

Cyclone II devices in a single device chain or in a multiple device chain support in-system programming of a serial configuration device using the JTAG interface via the serial flash loader design. The board's intelligent host or download cable can use the four JTAG pins on the Cyclone II device to program the serial configuration device in system, even if the host or download cable cannot access the configuration device's configuration pins (DCLK, DATA, ASDI, and nCS pins).

The serial flash loader design is a JTAG-based in-system programming solution for Altera serial configuration devices. The serial flash loader is a bridge design for the FPGA that uses its JTAG interface to access the EPCS JIC (JTAG Indirect Configuration Device Programming) file and then uses the AS interface to program the EPCS device. Both the JTAG interface and AS interface are bridged together inside the serial flash loader design.

In a multiple device chain, you only need to configure the master Cyclone II device which is controlling the serial configuration device. The slave devices in the multiple device chain which are configured by the serial configuration device do not need to be configured when using this operate the TAP controller, and the TDI and TDO pins provide the serial path for the data registers. The TDI pin also provides data to the instruction register, which then generates control logic for the data registers.

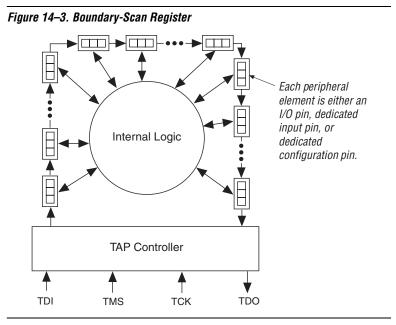

# IEEE Std. 1149.1 Boundary-Scan Register

The boundary-scan register is a large serial shift register that uses the TDI pin as an input and the TDO pin as an output. The boundary-scan register consists of 3-bit peripheral elements that are associated with Cyclone II I/O pins. You can use the boundary-scan register to test external pin connections or to capture internal data.

••••

See the *Configuration & Testing* chapter in Volume 1 of the *Cyclone II Device Handbook* for the Cyclone II device boundary-scan register lengths.

Figure 14–3 shows how test data is serially shifted around the periphery of the IEEE Std. 1149.1 device.

# Boundary-Scan Cells of a Cyclone II Device I/O Pin

The Cyclone II device 3-bit boundary-scan cell (BSC) consists of a set of capture registers and a set of update registers. The capture registers can connect to internal device data via the OUTJ and OEJ signals, and connect

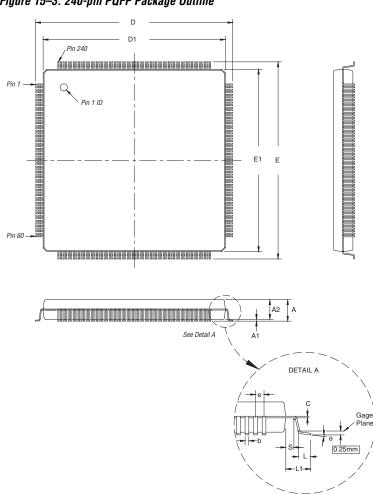

| Table 15–10. 240-Pin PQFP Package Outline Dimensions (Part 2 of 2) |            |      |      |  |  |  |

|--------------------------------------------------------------------|------------|------|------|--|--|--|

| Symbol                                                             | Millimeter |      |      |  |  |  |

| Symbol                                                             | Min.       | Nom. | Max. |  |  |  |

| е                                                                  | 0.50 BSC   |      |      |  |  |  |

| θ                                                                  | 0° 3.5° 8° |      |      |  |  |  |

Figure 15–3 shows a 240-pin PQFP package outline.

Figure 15–3. 240-pin PQFP Package Outline

# DocumentTable 15–21 shows the revision history for this document.Revision History

| Table 15–21. Document Revision History |                                                   |                    |

|----------------------------------------|---------------------------------------------------|--------------------|

| Date &<br>Document<br>Version          | Changes Made                                      | Summary of Changes |

| February 2007<br>v2.3                  | Added document revision history.                  |                    |

| November 2005<br>v2.1                  | Updated information throughout.                   |                    |

| July 2005 v2.0                         | Updated packaging information.                    |                    |

| November 2004<br>v1.0                  | Added document to the Cyclone II Device Handbook. |                    |