### Intel - EP2C5Q208I8N Datasheet

Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |  |

|--------------------------------|---------------------------------------------------------|--|

| Product Status                 | Active                                                  |  |

| Number of LABs/CLBs            | 288                                                     |  |

| Number of Logic Elements/Cells | 4608                                                    |  |

| Total RAM Bits                 | 119808                                                  |  |

| Number of I/O                  | 142                                                     |  |

| Number of Gates                |                                                         |  |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |  |

| Mounting Type                  | Surface Mount                                           |  |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                      |  |

| Package / Case                 | 208-BFQFP                                               |  |

| Supplier Device Package        | 208-PQFP (28x28)                                        |  |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c5q208i8n |  |

|                                |                                                         |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Referenced Documents

This chapter references the following documents:

Hot Socketing & Power-On Reset chapter in Cyclone II Device Handbook

Automotive-Grade Device Handbook

# Document Revision History

Table 1–5 shows the revision history for this document.

| Table 1–5. Doci               | Table 1–5. Document Revision History                                                                                                                             |                                                                                                                                              |  |  |  |  |  |  |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Date &<br>Document<br>Version | Changes Made                                                                                                                                                     | Summary of Changes                                                                                                                           |  |  |  |  |  |  |  |

| February 2008<br>v3.2         | <ul> <li>Added "Referenced Documents".</li> <li>Updated "Features" section and Table 1–1, Table 1–2,<br/>and Table 1–4 with information about EP2C5A.</li> </ul> | _                                                                                                                                            |  |  |  |  |  |  |  |

| February 2007<br>v3.1         | <ul> <li>Added document revision history.</li> <li>Added new <i>Note (2)</i> to Table 1–2.</li> </ul>                                                            | Note to explain difference<br>between I/O pin count<br>information provided in<br>Table 1–2 and in the Quartus II<br>software documentation. |  |  |  |  |  |  |  |

| November 2005<br>v2.1         | <ul><li>Updated Introduction and Features.</li><li>Updated Table 1–3.</li></ul>                                                                                  | —                                                                                                                                            |  |  |  |  |  |  |  |

| July 2005 v2.0                | <ul> <li>Updated technical content throughout.</li> <li>Updated Table 1–2.</li> <li>Added Tables 1–3 and 1–4.</li> </ul>                                         | _                                                                                                                                            |  |  |  |  |  |  |  |

| November 2004<br>v1.1         | <ul> <li>Updated Table 1–2.</li> <li>Updated bullet list in the "Features" section.</li> </ul>                                                                   | —                                                                                                                                            |  |  |  |  |  |  |  |

| June 2004 v1.0                | Added document to the Cyclone II Device Handbook.                                                                                                                | —                                                                                                                                            |  |  |  |  |  |  |  |

| Table 2–1. Cy           | Table 2–1. Cyclone II Device Routing Scheme (Part 2 of 2) |                    |                          |                 |                  |                 |                  |    |               |                     |     |            |         |

|-------------------------|-----------------------------------------------------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|----|---------------|---------------------|-----|------------|---------|

|                         |                                                           | Destination        |                          |                 |                  |                 |                  |    |               |                     |     |            |         |

| Source                  | Register Chain                                            | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | ΓE | M4K RAM Block | Embedded Multiplier | PLL | Column 10E | Row IOE |

| LE                      | $\checkmark$                                              | $\checkmark$       | $\checkmark$             | $\checkmark$    |                  | $\checkmark$    |                  |    |               |                     |     |            |         |

| M4K memory<br>Block     |                                                           | >                  | >                        | ~               |                  | ~               |                  |    |               |                     |     |            |         |

| Embedded<br>Multipliers |                                                           | ~                  | >                        | ~               |                  | ~               |                  |    |               |                     |     |            |         |

| PLL                     |                                                           |                    | >                        | $\checkmark$    |                  | $\checkmark$    |                  |    |               |                     |     |            |         |

| Column IOE              |                                                           |                    |                          |                 |                  | ~               | >                |    |               |                     |     |            |         |

| Row IOE                 |                                                           |                    | $\checkmark$             | $\checkmark$    | $\checkmark$     | $\checkmark$    |                  |    |               |                     |     |            |         |

# Global Clock Network & Phase-Locked Loops

Cyclone II devices provide global clock networks and up to four PLLs for a complete clock management solution. Cyclone II clock network features include:

- Up to 16 global clock networks

- Up to four PLLs

- Global clock network dynamic clock source selection

- Global clock network dynamic enable and disable

In Cyclone II devices, all the I/O banks support SDR and DDR SDRAM memory up to 167 MHz/333 Mbps. All I/O banks support DQS signals with the DQ bus modes of  $\times 8/\times 9$ , or  $\times 16/\times 18$ . Table 2–14 shows the external memory interfaces supported in Cyclone II devices.

| Table 2–14. External Memory Support in Cyclone II Devices       Note (1) |                            |                      |                                          |                                          |  |  |  |  |

|--------------------------------------------------------------------------|----------------------------|----------------------|------------------------------------------|------------------------------------------|--|--|--|--|

| Memory Standard                                                          | I/O Standard               | Maximum Bus<br>Width | Maximum Clock<br>Rate Supported<br>(MHz) | Maximum Data<br>Rate Supported<br>(Mbps) |  |  |  |  |

| SDR SDRAM                                                                | LVTTL (2)                  | 72                   | 167                                      | 167                                      |  |  |  |  |

| DDR SDRAM                                                                | SSTL-2 class I (2)         | 72                   | 167                                      | 333 (1)                                  |  |  |  |  |

|                                                                          | SSTL-2 class II (2)        | 72                   | 133                                      | 267 (1)                                  |  |  |  |  |

| DDR2 SDRAM                                                               | SSTL-18 class I (2)        | 72                   | 167                                      | 333 (1)                                  |  |  |  |  |

|                                                                          | SSTL-18 class II (3)       | 72                   | 125                                      | 250 (1)                                  |  |  |  |  |

| QDRII SRAM (4)                                                           | 1.8-V HSTL class I<br>(2)  | 36                   | 167                                      | 668 (1)                                  |  |  |  |  |

|                                                                          | 1.8-V HSTL class II<br>(3) | 36                   | 100                                      | 400 (1)                                  |  |  |  |  |

#### Notes to Table 2–14:

(1) The data rate is for designs using the Clock Delay Control circuitry.

(2) The I/O standards are supported on all the I/O banks of the Cyclone II device.

(3) The I/O standards are supported only on the I/O banks on the top and bottom of the Cyclone II device.

(4) For maximum performance, Altera recommends using the 1.8-V HSTL I/O standard because of higher I/O drive strength. QDRII SRAM devices also support the 1.5-V HSTL I/O standard.

Cyclone II devices use data (DQ), data strobe (DQS), and clock pins to interface with external memory. Figure 2–26 shows the DQ and DQS pins in the  $\times 8/\times 9$  mode.

# SignalTap II Embedded Logic Analyzer

Cyclone II devices support the SignalTap II embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA<sup>®</sup> packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.

For more information on the SignalTap II, see the *Signal Tap* chapter of the *Quartus II Handbook, Volume 3*.

# Configuration

The logic, circuitry, and interconnects in the Cyclone II architecture are configured with CMOS SRAM elements. Altera FPGA devices are reconfigurable and every device is tested with a high coverage production test program so you do not have to perform fault testing and can instead focus on simulation and design verification.

Cyclone II devices are configured at system power-up with data stored in an Altera configuration device or provided by a system controller. The Cyclone II device's optimized interface allows the device to act as controller in an active serial configuration scheme with EPCS serial configuration devices. The serial configuration device can be programmed via SRunner, the ByteBlaster II or USB Blaster download cable, the Altera Programming Unit (APU), or third-party programmers.

In addition to EPCS serial configuration devices, Altera offers in-system programmability (ISP)-capable configuration devices that can configure Cyclone II devices via a serial data stream using the Passive serial (PS) configuration mode. The PS interface also enables microprocessors to treat Cyclone II devices as memory and configure them by writing to a virtual memory location, simplifying reconfiguration. After a Cyclone II device has been configured, it can be reconfigured in-circuit by resetting the device and loading new configuration data. Real-time changes can be made during system operation, enabling innovative reconfigurable applications.

# Operating Modes

The Cyclone II architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. You can use the 10MHz internal oscillator or the optional CLKUSR pin during the initialization. The 10 MHz internal oscillator is disabled in user mode. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

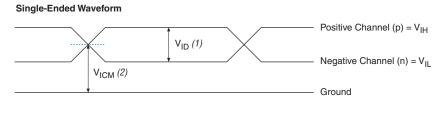

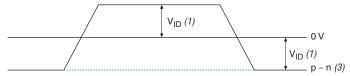

## Figure 5–1. Receiver Input Waveforms for Differential I/O Standards

Differential Waveform (Mathematical Function of Positive and Negative Channel)

#### *Notes to Figure 5–1:*

- (1)  $V_{ID}$  is the differential input voltage.  $V_{ID} = |p n|$ .

- (2)  $V_{ICM}$  is the input common mode voltage.  $V_{ICM} = (p + n)/2$ .

- (3) The p n waveform is a function of the positive channel (p) and the negative channel (n).

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| Device   | Speed Grade           | Preliminary  | Final        |

|----------|-----------------------|--------------|--------------|

| EP2C5/A  | Commercial/Industrial | —            | $\checkmark$ |

|          | Automotive            | $\checkmark$ | —            |

| EP2C8/A  | Commercial/Industrial | —            | $\checkmark$ |

|          | Automotive            | $\checkmark$ | _            |

| EP2C15A  | Commercial/Industrial | —            | $\checkmark$ |

|          | Automotive            | $\checkmark$ | _            |

| EP2C20/A | Commercial/Industrial | —            | $\checkmark$ |

|          | Automotive            | $\checkmark$ | _            |

| EP2C35   | Commercial/Industrial | —            | $\checkmark$ |

| EP2C50   | Commercial/Industrial | —            | $\checkmark$ |

| EP2C70   | Commercial/Industrial | —            | $\checkmark$ |

### Performance

Table 5–15 shows Cyclone II performance for some common designs. All performance values were obtained with Quartus II software compilation of LPM, or MegaCore functions for the FIR and FFT designs.

| Table        | Table 5–15. Cyclone II Performance (Part 1 of 4) |     |                         |               |                      |                             |                             |                      |

|--------------|--------------------------------------------------|-----|-------------------------|---------------|----------------------|-----------------------------|-----------------------------|----------------------|

|              |                                                  | R   | esources U              | lsed          | F                    | Performan                   | ice (MHz                    | )                    |

| Applications |                                                  | LEs | M4K<br>Memory<br>Blocks | DSP<br>Blocks | –6<br>Speed<br>Grade | -7<br>Speed<br>Grade<br>(6) | -7<br>Speed<br>Grade<br>(7) | –8<br>Speed<br>Grade |

| LE           | 16-to-1 multiplexer (1)                          | 21  | 0                       | 0             | 385.35               | 313.97                      | 270.85                      | 286.04               |

|              | 32-to-1 multiplexer (1)                          | 38  | 0                       | 0             | 294.2                | 260.75                      | 228.78                      | 191.02               |

|              | 16-bit counter                                   | 16  | 0                       | 0             | 401.6                | 349.4                       | 310.65                      | 310.65               |

|              | 64-bit counter                                   | 64  | 0                       | 0             | 157.15               | 137.98                      | 126.08                      | 126.27               |

| Parameter    | –6 Speed | Grade (1) | –7 Speed | Grade <i>(2)</i> | –8 Speed | Grade (3) | Unit |

|--------------|----------|-----------|----------|------------------|----------|-----------|------|

| Parameter    | Min      | Max       | Min      | Max              | Min      | Max       | Unit |

| TM4KBEH      | 234      | —         | 267      | _                | 267      | —         | ps   |

|              | _        | —         | 250      | —                | 267      | —         | ps   |

| TM4KDATAASU  | 35       | —         | 46       | —                | 46       | _         | ps   |

|              | —        | _         | 40       | _                | 46       | _         | ps   |

| TM4KDATAAH   | 234      | _         | 267      | _                | 267      | _         | ps   |

|              | _        | _         | 250      | _                | 267      | _         | ps   |

| TM4KADDRASU  | 35       | _         | 46       | _                | 46       | _         | ps   |

|              | —        | _         | 40       | _                | 46       | _         | ps   |

| TM4KADDRAH   | 234      | _         | 267      | _                | 267      | _         | ps   |

|              | _        | _         | 250      | _                | 267      | _         | ps   |

| TM4KDATABSU  | 35       | _         | 46       | _                | 46       | _         | ps   |

|              | _        | _         | 40       | _                | 46       | _         | ps   |

| TM4KDATABH   | 234      | _         | 267      | _                | 267      | _         | ps   |

|              | _        | _         | 250      | _                | 267      | _         | ps   |

| TM4KRADDRBSU | 35       | _         | 46       | _                | 46       | _         | ps   |

|              | _        | _         | 40       | _                | 46       | _         | ps   |

| TM4KRADDRBH  | 234      | _         | 267      | _                | 267      | _         | ps   |

|              | _        | _         | 250      | _                | 267      | _         | ps   |

| TM4KDATACO1  | 466      | 724       | 445      | 826              | 445      | 930       | ps   |

|              | _        | _         | 466      | _                | 466      | _         | ps   |

| TM4KDATACO2  | 2345     | 3680      | 2234     | 4157             | 2234     | 4636      | ps   |

|              | —        | —         | 2345     | —                | 2345     | —         | ps   |

| TM4KCLKH     | 1923     | —         | 2769     | —                | 2769     | —         | ps   |

|              | _        | _         | 2307     | —                | 2769     | _         | ps   |

| TM4KCLKL     | 1923     | —         | 2769     | —                | 2769     | —         | ps   |

|              | _        | _         | 2307     | _                | 2769     | _         | ps   |

| Table 5–56. Maximum DCD for SDR Output on Column I/O       Notes (1), (2)         (Part 2 of 2) |     |     |     |      |  |  |  |  |

|-------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|--|

| Column I/O Output Standard                                                                      | C6  | C7  | C8  | Unit |  |  |  |  |

| 2.5-V                                                                                           | 140 | 140 | 155 | ps   |  |  |  |  |

| 1.8-V                                                                                           | 115 | 115 | 165 | ps   |  |  |  |  |

| 1.5-V                                                                                           | 745 | 745 | 770 | ps   |  |  |  |  |

| SSTL-2 Class I                                                                                  | 60  | 60  | 75  | ps   |  |  |  |  |

| SSTL-2 Class II                                                                                 | 60  | 60  | 80  | ps   |  |  |  |  |

| SSTL-18 Class I                                                                                 | 60  | 130 | 130 | ps   |  |  |  |  |

| SSTL-18 Class II                                                                                | 60  | 135 | 135 | ps   |  |  |  |  |

| HSTL-18 Class I                                                                                 | 60  | 115 | 115 | ps   |  |  |  |  |

| HSTL-18 Class II                                                                                | 75  | 75  | 100 | ps   |  |  |  |  |

| HSTL-15 Class I                                                                                 | 150 | 150 | 150 | ps   |  |  |  |  |

| HSTL-15 Class II                                                                                | 135 | 135 | 155 | ps   |  |  |  |  |

| Differential SSTL-2 Class I                                                                     | 60  | 60  | 75  | ps   |  |  |  |  |

| Differential SSTL-2 Class II                                                                    | 60  | 60  | 80  | ps   |  |  |  |  |

| Differential SSTL-18 Class I                                                                    | 60  | 130 | 130 | ps   |  |  |  |  |

| Differential SSTL-18 Class II                                                                   | 60  | 135 | 135 | ps   |  |  |  |  |

| Differential HSTL-18 Class I                                                                    | 60  | 115 | 115 | ps   |  |  |  |  |

| Differential HSTL-18 Class II                                                                   | 75  | 75  | 100 | ps   |  |  |  |  |

| Differential HSTL-15 Class I                                                                    | 150 | 150 | 150 | ps   |  |  |  |  |

| Differential HSTL-15 Class II                                                                   | 135 | 135 | 155 | ps   |  |  |  |  |

| LVDS                                                                                            | 60  | 60  | 60  | ps   |  |  |  |  |

| Simple RSDS                                                                                     | 60  | 70  | 70  | ps   |  |  |  |  |

| Mini-LVDS                                                                                       | 60  | 60  | 60  | ps   |  |  |  |  |

Notes to Table 5–56:

- (1) The DCD specification is characterized using the maximum drive strength available for each I/O standard.

- (2) Numbers are applicable for commercial, industrial, and automotive devices.

Table 5–57. Maximum for DDIO Output on Row Pins with PLL in the Clock Path Notes (1), (2) (Part 1 of 2) Row Pins with PLL in the Clock Path C6 C7 **C**8 Unit LVCMOS 270 310 310 ps LVTTL 285 305 335 ps 2.5-V 180 180 220 ps 1.8-V 165 175 205 ps

Table 7–2 provides an overview of the Cyclone II PLL features.

| Table 7–2. Cyclone II PLL Features     |                                                |

|----------------------------------------|------------------------------------------------|

| Feature                                | Description                                    |

| Clock multiplication and division      | $m / (n \times \text{post-scale counter})$ (1) |

| Phase shift                            | Down to 125-ps increments (2), (3)             |

| Programmable duty cycle                | $\checkmark$                                   |

| Number of internal clock outputs       | Up to three per PLL (4)                        |

| Number of external clock outputs       | One per PLL (4)                                |

| Locked port can feed logic array       | $\checkmark$                                   |

| PLL clock outputs can feed logic array | $\checkmark$                                   |

| Manual clock switchover                | $\checkmark$                                   |

| Gated lock                             | $\checkmark$                                   |

#### Notes to Table 7–2:

- (1) *m* and post-scale counter values range from 1 to 32. *n* ranges from 1 to 4.

- (2) The smallest phase shift is determined by the voltage control oscillator (VCO) period divided by 8.

- (3) For degree increments, Cyclone II devices can shift output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the VCO frequency.

- (4) The Cyclone II PLL has three output counters that drive the global clock network. One of these output counters (c2) can also drive a dedicated external I/O pin (single ended or differential). This counter output can also drive the external clock output (PLL<#>\_OUT) and internal global clock network at the same time.

# Cyclone II PLL Hardware Overview

Cyclone II devices contain up to four PLLs that are arranged in the four corners of the Cyclone II device as shown in Figure 7–1, which shows a top-level diagram of the Cyclone II device and the PLL locations.

# PLL Specifications

See the *DC* & *Switching Characteristics* chapter in Volume 1 of the *Cyclone II Device Handbook* for information on PLL timing specifications.

# Clocking

Cyclone II devices provide up to 16 dedicated clock pins (CLK[15..0]) that can drive the global clock networks. The smaller Cyclone II devices (EP2C5 and EP2C8 devices) support four dedicated clock pins on each side (left and right) capable of driving a total of eight global clock networks, while the larger devices (EP2C15 devices and larger) support four clock pins on all four sides of the device. These clock pins can drive a total of 16 global clock networks.

Table 7–7 shows the number of global clocks available across the Cyclone II family members.

| Table 7–7. Number of Global Clocks Available in Cyclone II Devices |                         |  |  |  |  |  |

|--------------------------------------------------------------------|-------------------------|--|--|--|--|--|

| Device                                                             | Number of Global Clocks |  |  |  |  |  |

| EP2C5                                                              | 8                       |  |  |  |  |  |

| EP2C8                                                              | 8                       |  |  |  |  |  |

| EP2C15                                                             | 16                      |  |  |  |  |  |

| EP2C20                                                             | 16                      |  |  |  |  |  |

| EP2C35                                                             | 16                      |  |  |  |  |  |

| EP2C50                                                             | 16                      |  |  |  |  |  |

| EP2C70                                                             | 16                      |  |  |  |  |  |

# **Global Clock Network**

Global clocks drive throughout the entire device, feeding all device quadrants. All resources within the device (IOEs, logic array blocks (LABs), dedicated multiplier blocks, and M4K memory blocks) can use the global clock networks as clock sources. These clock network resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed by an external pin. Internal logic can also drive the global clock networks for internally generated global clocks and asynchronous clears, clock enables, or other control signals with high fan-out.

| Table 7–8. Global Clock Network Connections (Part 3 of 3) |   |   |        |                       |         |        |   |   |    |      |       |       |      |      |       |              |

|-----------------------------------------------------------|---|---|--------|-----------------------|---------|--------|---|---|----|------|-------|-------|------|------|-------|--------------|

| Global Clock                                              |   |   |        | Global Clock Networks |         |        |   |   |    |      |       |       |      |      |       |              |

| Network Clock                                             |   |   | All Cy | /clone                | e II De | evices | 5 |   | EP | 2C15 | throu | gh EF | 2C70 | Devi | ces O | nly          |

| Sources                                                   | 0 | 1 | 2      | 3                     | 4       | 5      | 6 | 7 | 8  | 9    | 10    | 11    | 12   | 13   | 14    | 15           |

| DPCLK3 (1)                                                |   |   |        |                       |         |        |   |   |    |      |       |       |      |      |       | $\checkmark$ |

#### Notes to Table 7–8:

See the Cyclone II Architecture chapter in Volume 1 of the Cyclone II Device Handbook for more information on DPCLK pins.

(2) This pin only applies to EP2C5 and EP2C8 devices.

(3) These pins only apply to EP2C15 devices and larger. Only one of the two CDPCLK pins can feed the clock control block. The other pin can be used as a regular I/O pin.

If the dedicated clock pins are not used to feed the global clock networks, they can be used as general-purpose input pins to feed the logic array using the MultiTrack interconnect. However, if they are used as general-purpose input pins, they do not have support for an I/O register and must use LE-based registers in place of an I/O register.

## **Clock Control Block**

Every global clock network is driven by a clock control block residing either on the top, bottom, left, or right side of the Cyclone II device. The global clock network has been optimized for minimum clock skew and delay.

Table 7–9 lists the sources that can feed the clock control block, which in turn feeds the global clock networks.

| Input                                            | Description                                                                                                                                                                                                                           |  |  |  |  |  |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Dedicated clock inputs                           | Dedicated clock input pins can drive clocks or<br>global signals, such as asynchronous clears,<br>presets, or clock enables onto a given global<br>clock network.                                                                     |  |  |  |  |  |  |

| Dual-purpose clock (DPCLK and CDPCLK) I/O inputs | DPCLK and CDPCLK I/O pins are bidirectional<br>dual function pins that can be used for high fan-<br>out control signals, such as protocol signals,<br>TRDY and IRDY signals for PCI, or DQS for<br>DDR, via the global clock network. |  |  |  |  |  |  |

## 3.3-V LVCMOS (EIA/JEDEC Standard JESD8-B)

The 3.3-V LVCMOS I/O standard is a general-purpose, single-ended standard used for 3.3-V applications. The LVCMOS standard defines the DC interface parameters for digital circuits operating from a 3.0- or 3.3-V power supply and driving or being driven by LVCMOS-compatible devices.

The LVCMOS standard specifies the same input voltage requirements as LVTTL ( $-0.3 \text{ V} \leq V_1 \leq 3.9 \text{ V}$ ). The output buffer drives to the rail to meet the minimum high-level output voltage requirements. The 3.3-V I/O standard does not require input reference voltages or board terminations. Cyclone II devices support both input and output levels specified by the 3.3-V LVCMOS I/O standard.

## 3.3-V (PCI Special Interest Group [SIG] PCI Local Bus Specification Revision 3.0)

The PCI local bus specification is used for applications that interface to the PCI local bus, which provides a processor-independent data path between highly integrated peripheral controller components, peripheral add-in boards, and processor/memory systems. The conventional PCI specification revision 3.0 defines the PCI hardware environment including the protocol, electrical, mechanical, and configuration specifications for the PCI devices and expansion boards. This standard requires a 3.3-V V<sub>CCIO</sub>. The 3.3-V PCI standard does not require input reference voltages or board terminations.

The side (left and right) I/O banks on all Cyclone II devices are fully compliant with the 3.3V PCI Local Bus Specification Revision 3.0 and meet 32-bit/66 MHz operating frequency and timing requirements.

Table 10–2 lists the specific Cyclone II devices that support 64- and 32-bit PCI at 66 MHz.

| Table 10–2. Cyclone II 66-MHz PCI Support (Part 1 of 2) |                      |                        |              |  |

|---------------------------------------------------------|----------------------|------------------------|--------------|--|

| Dovico                                                  | Baakaga              | –6 and –7 Speed Grades |              |  |

| Device                                                  | Package              | 64 Bits                | 32 Bits      |  |

| EP2C5                                                   | 144-pin TQFP         |                        |              |  |

|                                                         | 208-pin PQFP         |                        | $\checkmark$ |  |

|                                                         | 256-pin FineLineBGA® |                        | $\checkmark$ |  |

10 - 4

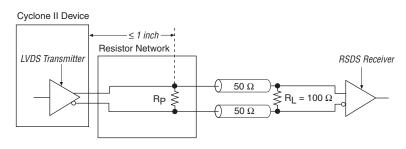

Note to Figure 11–8: (1)  $R_p = 100 \Omega$

### RSDS Software Support

When designing for the RSDS I/O standard, assign the RSDS I/O standard to the I/O pins intended for RSDS in the Quartus<sup>®</sup> II software. Contact Altera Applications for reference designs.

### mini-LVDS Standard Support in Cyclone II Devices

The mini-LVDS specification defines its use in chip-to-chip applications between the timing controller and the column drivers on display panels. Cyclone II devices meet the Texas Instruments mini-LVDS Interface Specification and support the mini-LVDS output standard. Table 11–3 shows the mini-LVDS electrical characteristics for Cyclone II devices.

| Table 11–3. mini-LVDS Electrical Characteristics for Cyclone II Devices       Note (1) |                             |                      |       |      |       |       |

|----------------------------------------------------------------------------------------|-----------------------------|----------------------|-------|------|-------|-------|

| Symbol                                                                                 | Parameters                  | Condition            | Min   | Тур  | Max   | Units |

| V <sub>CCIO</sub>                                                                      | Output supply voltage       |                      | 2.375 | 2.5  | 2.625 | V     |

| V <sub>OD</sub> (2)                                                                    | Differential output voltage | $R_L = 100 \ \Omega$ | 300   |      | 600   | mV    |

| V <sub>OS</sub> (3)                                                                    | Output offset voltage       | $R_L = 100 \Omega$   | 1125  | 1250 | 1375  | mV    |

| T <sub>r</sub> / T <sub>f</sub>                                                        | Transition time             | 20% to 80%           |       |      | 500   | ps    |

#### Notes to Table 11–3:

(1) The V<sub>OD</sub> specifications apply at the resistor network output.

(2)  $V_{OD} = V_{OH} - V_{OL}$ .

(3)  $V_{OS} = (V_{OH} + V_{OL}) / 2.$

See the *Cyclone II Memory Blocks* chapter in Volume 1 of the *Cyclone II Device Handbook* for more information on Cyclone II M4K memory blocks.

Refer to *AN 306: Techniques for Implementing Multipliers in FPGA Devices* for more information on soft multipliers.

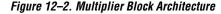

# Architecture

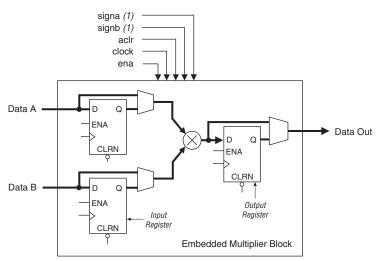

Each embedded multiplier consists of the following elements:

- Multiplier stage

- Input and output registers

- Input and output interfaces

Figure 12–2 shows the multiplier block architecture.

Note to Figure 12-2:

(1) If necessary, you can send these signals through one register to match the data signal path.

## **Input Registers**

You can send each multiplier input signal into an input register or directly into the multiplier in 9- or 18-bit sections depending on the operational mode of the multiplier. You can send each multiplier input signal through a register independently of each other (e.g., you can send the multiplier's

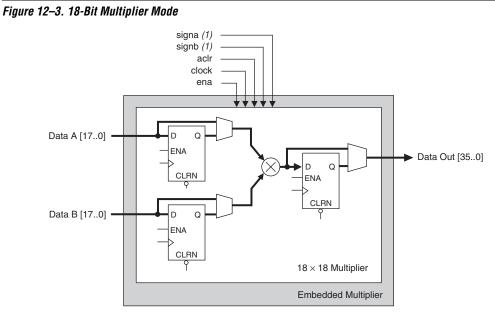

## **18-Bit Multipliers**

Each embedded multiplier can be configured to support a single  $18 \times 18$  multiplier for input widths from 10- to 18-bits. Figure 12–3 shows the embedded multiplier configured to support an 18-bit multiplier.

#### Note to Figure 12–3:

(1) If necessary, you can send these signals through one register to match the data signal path.

All 18-bit multiplier inputs and results can be independently sent through registers. The multiplier inputs can accept signed integers, unsigned integers or a combination of both. Additionally, you can change the signa and signb signals dynamically and can send these signals through dedicated input registers.

## 9-Bit Multipliers

Each embedded multiplier can also be configured to support two  $9 \times 9$  independent multipliers for input widths up to 9-bits. Figure 12–4 shows the embedded multiplier configured to support two 9-bit multipliers.

Serial configuration devices provide a serial interface to access configuration data. During device configuration, Cyclone II devices read configuration data via the serial interface, decompress data if necessary, and configure their SRAM cells. The FPGA controls the configuration interface in the AS configuration scheme, while the external host (e.g., the configuration device or microprocessor) controls the interface in the PS configuration scheme.

The Cyclone II decompression feature is available when configuring your Cyclone II device using AS mode.

Table 13–4 shows the  $\ensuremath{\texttt{MSEL}}$  pin settings when using the AS configuration scheme.

| Table 13–4. Cyclone II Configuration Schemes |       |       |  |  |

|----------------------------------------------|-------|-------|--|--|

| Configuration Scheme                         | MSEL1 | MSELO |  |  |

| AS (20 MHz)                                  | 0     | 0     |  |  |

| Fast AS (40 MHz) (1)                         | 1     | 0     |  |  |

Note to Table 13-4:

Only the EPCS16 and EPCS64 devices support a DCLK up to 40 MHz clock; other EPCS devices support a DCLK up to 20 MHz. Refer to the *Serial Configuration Devices Data Sheet* for more information.

## **Single Device AS Configuration**

Serial configuration devices have a four-pin interface: serial clock input (DCLK), serial data output (DATA), AS data input (ASDI), and an active-low chip select (nCS). This four-pin interface connects to Cyclone II device pins, as shown in Figure 13–3.

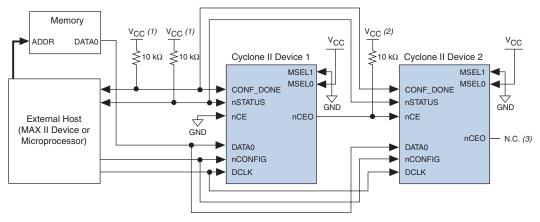

Figure 13–10. Multiple Device PS Configuration Using an External Host

#### Notes to Figure 13–10:

- The pull-up resistor should be connected to a supply that provides an acceptable input signal for all devices in the chain. V<sub>CC</sub> should be high enough to meet the V<sub>IH</sub> specification of the I/O on the devices and the external host.

- (2) Connect the pull-up resistor to the V<sub>CCIO</sub> supply voltage of I/O bank that the nCEO pin resides in.

- (3) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed another device's nCE pin.

In multiple device PS configuration, connect the first Cyclone II device's nCE pin to GND and connect the nCEO pin to the nCE pin of the next Cyclone II device in the chain. Use an external  $10-k\Omega$  pull-up resistor to pull the Cyclone II device's nCEO pin high to its V<sub>CCIO</sub> level to help the internal weak pull-up resistor when the nCEO pin feeds next Cyclone II device's nCE pin. The input to the nCE pin of the last Cyclone II device in the chain comes from the previous Cyclone II device. After the first device completes configuration in a multiple device configuration chain, its nCEO pin transitions low to activate the second device's nCE pin, which prompts the second device to begin configuration. The second device in the chain begins configuration within one clock cycle. Therefore, the MAX II device begins to transfer data to the next Cyclone II device without interruption. The nCEO pin is a dual-purpose pin in Cyclone II devices. You can leave the nCEO pin of the last device unconnected or use it as a user I/O pin after configuration if the last device in chain is a Cyclone II device.

The Quartus II software sets the Cyclone II device nCEO pin as a dedicated output by default. If the nCEO pin feeds the next device's nCE pin, you must make sure that the nCEO pin is not used as a user I/O after configuration. This software setting is in the **Dual-Purpose Pins** tab of the **Device & Pin Options** dialog box in Quartus II software.

Table 13–7 defines the timing parameters for Cyclone II devices for PS configuration.

| Table 13–7. PS Timing Parameters for Cyclone II Devices |                                                   |                                               |               |       |

|---------------------------------------------------------|---------------------------------------------------|-----------------------------------------------|---------------|-------|

| Symbol                                                  | Parameter                                         | Minimum                                       | Maximum       | Units |

| t <sub>POR</sub>                                        | POR delay (1)                                     | 100                                           |               | ms    |

| t <sub>CF2CD</sub>                                      | nCONFIG low to CONF_DONE low                      |                                               | 800           | ns    |

| t <sub>CF2ST0</sub>                                     | nCONFIG low to nSTATUS low                        |                                               | 800           | ns    |

| t <sub>CFG</sub>                                        | nCONFIG low pulse width                           | 2                                             |               | μs    |

| t <sub>status</sub>                                     | nSTATUS low pulse width                           | 10                                            | 40 <i>(2)</i> | μs    |

| t <sub>CF2ST1</sub>                                     | nCONFIG high to nSTATUS high                      |                                               | 40 (2)        | μs    |

| t <sub>CF2CK</sub>                                      | nCONFIG high to first rising edge on DCLK         | 40                                            |               | μs    |

| t <sub>sт2CK</sub>                                      | nSTATUS high to first rising edge on DCLK         | 1                                             |               | μs    |

| t <sub>DSU</sub>                                        | Data setup time before rising edge on DCLK        | 7                                             |               | ns    |

| t <sub>DH</sub>                                         | Data hold time after rising edge on DCLK          | 0                                             |               | ns    |

| t <sub>CH</sub>                                         | DCLK high time                                    | 4                                             |               | ns    |

| t <sub>CL</sub>                                         | DCLK low time                                     | 4                                             |               | ns    |

| t <sub>CLK</sub>                                        | DCLK period                                       | 10                                            |               | ns    |

| f <sub>MAX</sub>                                        | DCLK frequency                                    |                                               | 100           | MHz   |

| t <sub>CD2UM</sub>                                      | CONF_DONE high to user mode (3)                   | 18                                            | 40            | μs    |

| t <sub>CD2CU</sub>                                      | CONF_DONE high to CLKUSR enabled                  | 4 × maximum DCLK period                       |               |       |

| t <sub>сд2имс</sub>                                     | CONF_DONE high to user mode with CLKUSR option on | GR t <sub>CD2CU</sub> + (299 × CLKUSR period) |               |       |

### Notes to Table 13–7:

- (1) The POR delay minimum of 100 ms only applies for non "A" devices.

- (2) This value is applicable if users do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

- (3) The minimum and maximum numbers apply only if the internal oscillator is chosen as the clock source for starting the device.

Device configuration options and how to create configuration files are discussed further in the *Software Settings* section in Volume 2 of the *Configuration Handbook*.

## **PS Configuration Using a Microprocessor**

In the PS configuration scheme, a microprocessor can control the transfer of configuration data from a storage device, such as flash memory, to the target Cyclone II device.

| Pin Name | User<br>Mode | Configuration<br>Scheme | Pin Type                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|--------------|-------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nSTATUS  | N/A          | All                     | Bidirectional open-drain | The Cyclone II device drives nSTATUS low immediately after power-up and releases it after the POR time.                                                                                                                                                                                                                                                                                                                                                         |

|          |              |                         |                          | This pin provides a status output and input for the<br>Cyclone II device. If the Cyclone II device detects an<br>error during configuration, it drives the nSTATUS pin<br>low to stop configuration. If an external source (for<br>example, another Cyclone II device) drives the<br>nSTATUS pin low during configuration or<br>initialization, the target device enters an error state.<br>Driving nSTATUS low after configuration and                         |

|          |              |                         |                          | initialization does not affect the configured device. If<br>your design uses a configuration device, driving<br>nSTATUS low causes the configuration device to<br>attempt to configure the FPGA, but since the FPGA<br>ignores transitions on nSTATUS in user mode, the<br>FPGA does not reconfigure. To initiate a<br>reconfiguration, pull the nCONFIG pin low.                                                                                               |

|          |              |                         |                          | The enhanced configuration devices' and EPC2 devices' OE and nCS pins are connected to the Cyclone II device's nSTATUS and CONF_DONE pins, respectively, and have optional internal programmable pull-up resistors. If you use these internal pull-up resistors on the enhanced configuration device, do not use external 10-k $\Omega$ pull-up resistors on these pins. When using EPC2 devices, you should only use external 10-k $\Omega$ pull-up resistors. |

|          |              |                         |                          | The input buffer on this pin supports hysteresis using Schmitt trigger circuitry.                                                                                                                                                                                                                                                                                                                                                                               |

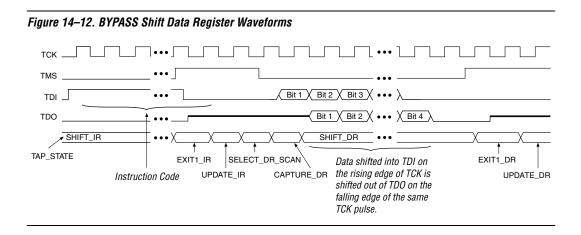

## **IDCODE Instruction Mode**

The IDCODE instruction mode is used to identify the devices in an IEEE Std. 1149.1 chain. When IDCODE is selected, the device identification register is loaded with the 32-bit vendor-defined identification code. The device ID register is connected between the TDI and TDO ports, and the device IDCODE is shifted out. The IDCODE for Cyclone II devices are listed in the *Configuration & Testing* chapter in Volume 1 of the *Cyclone II Device Handbook*.

## **USERCODE Instruction Mode**

The USERCODE instruction mode is used to examine the user electronic signature (UES) within the devices along an IEEE Std. 1149.1 chain. When this instruction is selected, the device identification register is connected between the TDI and TDO ports. The user-defined UES is shifted into the device ID register in parallel from the 32-bit USERCODE register. The UES is then shifted out through the device ID register. The UES value is not user defined until after the device has been configured. Before configuration, the UES value is set to the default value.

## **CLAMP Instruction Mode**

The CLAMP instruction mode is used to allow the boundary-scan register to determine the state of the signals driven from the pins. In CLAMP instruction mode, the bypass register is selected as the serial path between the TDI and TDO ports.