Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                        |

|--------------------------------|--------------------------------------------------------|

| Product Status                 | Active                                                 |

| Number of LABs/CLBs            | 288                                                    |

| Number of Logic Elements/Cells | 4608                                                   |

| Total RAM Bits                 | 119808                                                 |

| Number of I/O                  | 89                                                     |

| Number of Gates                | -                                                      |

| Voltage - Supply               | 1.15V ~ 1.25V                                          |

| Mounting Type                  | Surface Mount                                          |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                        |

| Package / Case                 | 144-LQFP                                               |

| Supplier Device Package        | 144-TQFP (20x20)                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c5t144c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Visual Cue                          | Meaning                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Italic type                         | Internal timing parameters and variables are shown in italic type. Examples: $t_{P A}$ , $n+1$ .                                                                                                                                                                                                                        |

|                                     | Variable names are enclosed in angle brackets (< >) and shown in italic type. Example: <file name="">, <project name="">.pof file.</project></file>                                                                                                                                                                     |

| Initial Capital Letters             | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                  | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                        | Signal and port names are shown in lowercase Courier type. Examples: data1, tdi, input. Active-low signals are denoted by suffix n, e.g., resetn.                                                                                                                                                                       |

|                                     | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc. | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| •••                                 | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| ✓                                   | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

|                                     | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| CAUTION                             | The caution indicates required information that needs special consideration and understanding and should be read prior to starting or continuing with the procedure or process.                                                                                                                                         |

| WARNING                             | The warning indicates information that should be read prior to starting or continuing the procedure or processes                                                                                                                                                                                                        |

| 4                                   | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

| •••                                 | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

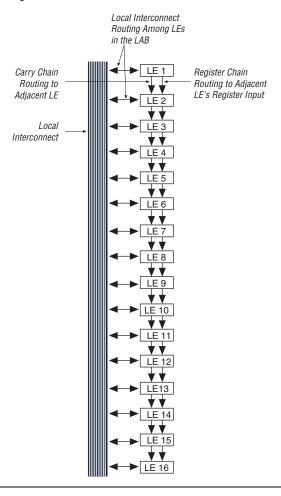

Figure 2-9. Register Chain Interconnects

The C4 interconnects span four LABs, M4K blocks, or embedded multipliers up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–10 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including PLLs, M4K memory blocks, embedded multiplier blocks, and column and row IOEs. For LAB interconnection, a primary LAB or its LAB neighbor (see Figure 2–10) can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

#### I/O Banks

The I/O pins on Cyclone II devices are grouped together into I/O banks and each bank has a separate power bus. EP2C5 and EP2C8 devices have four I/O banks (see Figure 2–28), while EP2C15, EP2C20, EP2C35, EP2C50, and EP2C70 devices have eight I/O banks (see Figure 2–29). Each device I/O pin is associated with one I/O bank. To accommodate voltage-referenced I/O standards, each Cyclone II I/O bank has a VREF bus. Each bank in EP2C5, EP2C8, EP2C15, EP2C20, EP2C35, and EP2C50 devices supports two VREF pins and each bank of EP2C70 supports four VREF pins. When using the VREF pins, each VREF pin must be properly connected to the appropriate voltage level. In the event these pins are not used as VREF pins, they may be used as regular I/O pins.

The top and bottom I/O banks (banks 2 and 4 in EP2C5 and EP2C8 devices and banks 3, 4, 7, and 8 in EP2C15, EP2C20, EP2C35, EP2C50, and EP2C70 devices) support all I/O standards listed in Table 2–17, except the PCI/PCI-X I/O standards. The left and right side I/O banks (banks 1 and 3 in EP2C5 and EP2C8 devices and banks 1, 2, 5, and 6 in EP2C15, EP2C20, EP2C35, EP2C50, and EP2C70 devices) support I/O standards listed in Table 2–17, except SSTL-18 class II, HSTL-18 class II, and HSTL-15 class II I/O standards. See Table 2–17 for a complete list of supported I/O standards.

The top and bottom I/O banks (banks 2 and 4 in EP2C5 and EP2C8 devices and banks 3, 4, 7, and 8 in EP2C15, EP2C20, EP2C35, EP2C50, and EP2C70 devices) support DDR2 memory up to 167 MHz/333 Mbps and QDR memory up to 167 MHz/668 Mbps. The left and right side I/O banks (1 and 3 of EP2C5 and EP2C8 devices and 1, 2, 5, and 6 of EP2C15, EP2C20, EP2C35, EP2C50, and EP2C70 devices) only support SDR and DDR SDRAM interfaces. All the I/O banks of the Cyclone II devices support SDR memory up to 167 MHz/167 Mbps and DDR memory up to 167 MHz/333 Mbps.

DDR2 and QDRII interfaces may be implemented in Cyclone II side banks if the use of class I I/O standard is acceptable.

standards (e.g., SSTL-2) independently. If an I/O bank does not use voltage-referenced standards, the  $\mbox{VREF}$  pins are available as user I/O pins.

Each I/O bank can support multiple standards with the same  $V_{\rm CCIO}$  for input and output pins. For example, when  $V_{\rm CCIO}$  is 3.3-V, a bank can support LVTTL, LVCMOS, and 3.3-V PCI for inputs and outputs. Voltage-referenced standards can be supported in an I/O bank using any number of single-ended or differential standards as long as they use the same  $V_{\rm REF}$  and a compatible  $V_{\rm CCIO}$  value.

### MultiVolt I/O Interface

The Cyclone II architecture supports the MultiVolt I/O interface feature, which allows Cyclone II devices in all packages to interface with systems of different supply voltages. Cyclone II devices have one set of  $V_{CC}$  pins (VCCINT) that power the internal device logic array and input buffers that use the LVPECL, LVDS, HSTL, or SSTL I/O standards. Cyclone II devices also have four or eight sets of VCC pins (VCCIO) that power the I/O output drivers and input buffers that use the LVTTL, LVCMOS, or PCI I/O standards.

The Cyclone II VCCINT pins must always be connected to a 1.2-V power supply. If the  $V_{\rm CCINT}$  level is 1.2 V, then input pins are 1.5-V, 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-V, 1.8-V, 2.5-V, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (i.e., when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3-V and is compatible with 3.3-V systems. Table 2–20 summarizes Cyclone II MultiVolt I/O support.

| Table 2-2             | Table 2–20. Cyclone II MultiVolt I/O Support (Part 1 of 2) Note (1) |          |              |              |              |              |          |       |

|-----------------------|---------------------------------------------------------------------|----------|--------------|--------------|--------------|--------------|----------|-------|

| v (v)                 | Input Signal Output Signal                                          |          |              |              |              |              |          |       |

| V <sub>CCIO</sub> (V) | 1.5 V                                                               | 1.8 V    | 2.5 V        | 3.3 V        | 1.5 V        | 1.8 V        | 2.5 V    | 3.3 V |

| 1.5                   | <b>✓</b>                                                            | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) | <b>✓</b>     |              |          |       |

| 1.8                   | <b>√</b> (4)                                                        | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (3) | <b>✓</b>     |          |       |

| 2.5                   |                                                                     |          | ~            | <b>✓</b>     | <b>√</b> (5) | <b>√</b> (5) | <b>✓</b> |       |

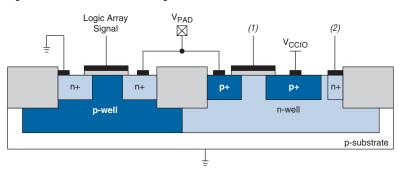

Figure 4–2. Transistor Level Diagram of FPGA Device I/O Buffers

*Notes to Figure 4–2:*

- (1) This is the logic array signal or the larger of either the  $V_{CCIO}$  or  $V_{PAD}$  signal.

- (2) This is the larger of either the  $V_{CCIO}$  or  $V_{PAD}$  signal.

# Power-On Reset Circuitry

Cyclone II devices contain POR circuitry to keep the device in a reset state until the power supply voltage levels have stabilized during power-up. The POR circuit monitors the  $V_{\rm CCINT}$  voltage levels and tri-states all user I/O pins until the  $V_{\rm CC}$  reaches the recommended operating levels. In addition, the POR circuitry also monitors the  $V_{\rm CCIO}$  level of the two I/O banks that contains configuration pins (I/O banks 1 and 3 for EP2C5 and EP2C8, I/O banks 2 and 6 for EP2C15A, EP2C20, EP2C35, EP2C50, and EP2C70) and tri-states all user I/O pins until the  $V_{\rm CC}$  reaches the recommended operating levels.

After the Cyclone II device enters user mode, the POR circuit continues to monitor the  $V_{CCINT}$  voltage level so that a brown-out condition during user mode can be detected. If the  $V_{CCINT}$  voltage sags below the POR trip point during user mode, the POR circuit resets the device. If the  $V_{CCIO}$  voltage sags during user mode, the POR circuit does not reset the device.

### "Wake-up" Time for Cyclone II Devices

In some applications, it may be necessary for a device to wake up very quickly in order to begin operation. The Cyclone II device family offers the Fast-On feature to support fast wake-up time applications. Devices that support the Fast-On feature are designated with an "A" in the ordering code and have stricter power up requirements compared to non-A devices.

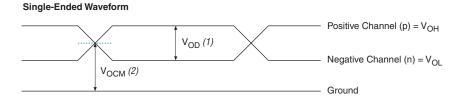

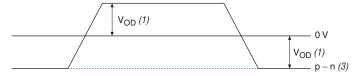

Figure 5–2 shows the transmitter output waveforms for all supported differential output standards (LVDS, mini-LVDS, RSDS, differential 1.5-V HSTL class I and II, differential 1.8-V HSTL class I and II, differential SSTL-2 class I and II, and differential SSTL-18 class I and II).

Figure 5–2. Transmitter Output Waveforms for Differential I/O Standards

#### Differential Waveform (Mathematical Function of Positive and Negative Channel)

#### Notes to Figure 5-2:

- (1)  $V_{OD}$  is the output differential voltage.  $V_{OD} = |p n|$ .

- (2)  $V_{OCM}$  is the output common mode voltage.  $V_{OCM} = (p + n)/2$ .

- (3) The p n waveform is a function of the positive channel (p) and the negative channel (n).

Table 5–9 shows the DC characteristics for user I/O pins with differential I/O standards.

| Table 5–9. DC Cl                                 | Table 5–9. DC Characteristics for User I/O Pins Using Differential I/O Standards Note (1) (Part 1 of 2) |     |                  |                                    |     |       |                     | of 2) |                            |     |     |     |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|------------------|------------------------------------|-----|-------|---------------------|-------|----------------------------|-----|-----|-----|

| I/O Standard                                     | V <sub>OD</sub> (mV)                                                                                    |     | ΔV <sub>OD</sub> | $\Delta V_{OD}$ (mV) $V_{OCM}$ (V) |     |       | V <sub>OH</sub> (V) |       | V <sub>OL</sub> (V)        |     |     |     |

| I/O Standard                                     | Min                                                                                                     | Тур | Max              | Min                                | Max | Min   | Тур                 | Max   | Min                        | Max | Min | Max |

| LVDS                                             | 250                                                                                                     | _   | 600              | _                                  | 50  | 1.125 | 1.25                | 1.375 | _                          | _   | _   | _   |

| mini-LVDS (2)                                    | 300                                                                                                     | _   | 600              | _                                  | 50  | 1.125 | 1.25                | 1.375 | _                          | _   | _   | -   |

| RSDS (2)                                         | 100                                                                                                     | _   | 600              | _                                  | _   | 1.125 | 1.25                | 1.375 | _                          | _   | _   | _   |

| Differential 1.5-V<br>HSTL class I<br>and II (3) | _                                                                                                       | _   |                  | _                                  | _   | _     | _                   | _     | V <sub>CCIO</sub><br>- 0.4 | _   | _   | 0.4 |

| Table 5–30. EP2C35 Row Pins Global Clock Timing Parameters |            |                      |       |          |             |      |

|------------------------------------------------------------|------------|----------------------|-------|----------|-------------|------|

| Doromotor                                                  | Fast (     | Fast Corner –6 Speed |       | -7 Speed | -8 Speed    | Unit |

| Parameter                                                  | Industrial | Commercial           | Grade | Grade    | Grade Grade |      |

| t <sub>CIN</sub>                                           | 1.410      | 1.476                | 2.514 | 2.724    | 2.986       | ns   |

| t <sub>COUT</sub>                                          | 1.412      | 1.478                | 2.530 | 2.737    | 2.994       | ns   |

| t <sub>PLLCIN</sub>                                        | -0.117     | -0.127               | 0.134 | 0.162    | 0.241       | ns   |

| t <sub>PLLCOUT</sub>                                       | -0.115     | -0.125               | 0.15  | 0.175    | 0.249       | ns   |

### EP2C50 Clock Timing Parameters

Tables 5–31 and 5–32 show the clock timing parameters for EP2C50 devices.

| Table 5–31. EP2C50 Column Pins Global Clock Timing Parameters |            |            |          |          |          |       |

|---------------------------------------------------------------|------------|------------|----------|----------|----------|-------|

| Parameter                                                     | Fast (     | Corner     | -6 Speed | -7 Speed | -8 Speed | Unit  |

| Parameter                                                     | Industrial | Commercial | Grade    | Grade    | Grade    | UIIIL |

| t <sub>CIN</sub>                                              | 1.575      | 1.651      | 2.759    | 2.940    | 3.174    | ns    |

| t <sub>COUT</sub>                                             | 1.589      | 1.666      | 2.793    | 2.972    | 3.203    | ns    |

| t <sub>PLLCIN</sub>                                           | -0.149     | -0.158     | 0.113    | 0.075    | 0.089    | ns    |

| t <sub>PLLCOUT</sub>                                          | -0.135     | -0.143     | 0.147    | 0.107    | 0.118    | ns    |

| Table 5–32. EP2C50 Row Pins Global Clock Timing Parameters |            |            |          |          |          |       |  |

|------------------------------------------------------------|------------|------------|----------|----------|----------|-------|--|

| Parameter                                                  | Fast (     | Corner     | -6 Speed | -7 Speed | -8 Speed | Unit  |  |

| raiailletei                                                | Industrial | Commercial | Grade    | Grade    | Grade    | UIIIL |  |

| t <sub>CIN</sub>                                           | 1.463      | 1.533      | 2.624    | 2.791    | 3.010    | ns    |  |

| t <sub>COUT</sub>                                          | 1.465      | 1.535      | 2.640    | 2.804    | 3.018    | ns    |  |

| t <sub>PLLCIN</sub>                                        | -0.261     | -0.276     | -0.022   | -0.074   | -0.075   | ns    |  |

| t <sub>PLLCOUT</sub>                                       | -0.259     | -0.274     | -0.006   | -0.061   | -0.067   | ns    |  |

Table 5–38. Default Loading of Different I/O Standards for Cyclone II Device (Part 2 of 2)

| I/O Standard                    | Capacitive Load | Unit |

|---------------------------------|-----------------|------|

| SSTL_18_CLASS_II                | 0               | pF   |

| 1.5V_HSTL_CLASS_I               | 0               | pF   |

| 1.5V_HSTL_CLASS_II              | 0               | pF   |

| 1.8V_HSTL_CLASS_I               | 0               | pF   |

| 1.8V_HSTL_CLASS_II              | 0               | pF   |

| DIFFERENTIAL_SSTL_2_CLASS_I     | 0               | pF   |

| DIFFERENTIAL_SSTL_2_CLASS_II    | 0               | pF   |

| DIFFERENTIAL_SSTL_18_CLASS_I    | 0               | pF   |

| DIFFERENTIAL_SSTL_18_CLASS_II   | 0               | pF   |

| 1.5V_DIFFERENTIAL_HSTL_CLASS_I  | 0               | pF   |

| 1.5V_DIFFERENTIAL_HSTL_CLASS_II | 0               | pF   |

| 1.8V_DIFFERENTIAL_HSTL_CLASS_I  | 0               | pF   |

| 1.8V_DIFFERENTIAL_HSTL_CLASS_II | 0               | pF   |

| LVDS                            | 0               | pF   |

| 1.2V_HSTL                       | 0               | pF   |

| 1.2V_DIFFERENTIAL_HSTL          | 0               | pF   |

| Table 5–42. Cyclone | II I/O Outp  | ut Delay for t   | Column Pins               | (Part 5 of      | <i>5)</i>      |             |             |                |      |

|---------------------|--------------|------------------|---------------------------|-----------------|----------------|-------------|-------------|----------------|------|

|                     | Drive        | _                | Fast Co                   | rner            | -6             | -7<br>Speed | -7<br>Speed | -8             |      |

| I/O Standard        | Strength     | Parameter        | Industrial/<br>Automotive | Commer<br>-cial | Speed<br>Grade | Grade (2)   | Grade (3)   | Speed<br>Grade | Unit |

| DIFFERENTIAL_       | 6 mA         | t <sub>OP</sub>  | 1472                      | 1544            | 3140           | 3345        | 3542        | 3549           | ps   |

| SSTL_18_CLASS_I     |              | t <sub>DIP</sub> | 1604                      | 1683            | 3310           | 3539        | 3768        | 3768           | ps   |

|                     | 8 mA         | t <sub>OP</sub>  | 1469                      | 1541            | 3086           | 3287        | 3482        | 3489           | ps   |

|                     |              | t <sub>DIP</sub> | 1601                      | 1680            | 3256           | 3481        | 3708        | 3708           | ps   |

|                     | 10 mA        | t <sub>OP</sub>  | 1466                      | 1538            | 2980           | 3171        | 3354        | 3361           | ps   |

|                     |              | t <sub>DIP</sub> | 1598                      | 1677            | 3150           | 3365        | 3580        | 3580           | ps   |

|                     | 12 mA        | t <sub>OP</sub>  | 1466                      | 1538            | 2980           | 3171        | 3354        | 3361           | ps   |

|                     | (1)          | t <sub>DIP</sub> | 1598                      | 1677            | 3150           | 3365        | 3580        | 3580           | ps   |

| DIFFERENTIAL_       | 16 mA        | t <sub>OP</sub>  | 1454                      | 1525            | 2905           | 3088        | 3263        | 3270           | ps   |

| SSTL_18_CLASS_II    |              | t <sub>DIP</sub> | 1586                      | 1664            | 3075           | 3282        | 3489        | 3489           | ps   |

|                     | 18 mA<br>(1) | t <sub>OP</sub>  | 1453                      | 1524            | 2900           | 3082        | 3257        | 3264           | ps   |

|                     |              | t <sub>DIP</sub> | 1585                      | 1663            | 3070           | 3276        | 3483        | 3483           | ps   |

| 1.8V_DIFFERENTIAL   | 8 mA         | t <sub>OP</sub>  | 1460                      | 1531            | 3222           | 3424        | 3618        | 3625           | ps   |

| _HSTL_CLASS_I       |              | t <sub>DIP</sub> | 1592                      | 1670            | 3392           | 3618        | 3844        | 3844           | ps   |

|                     | 10 mA        | t <sub>OP</sub>  | 1462                      | 1534            | 3090           | 3279        | 3462        | 3469           | ps   |

|                     |              | t <sub>DIP</sub> | 1594                      | 1673            | 3260           | 3473        | 3688        | 3688           | ps   |

|                     | 12 mA        | t <sub>OP</sub>  | 1462                      | 1534            | 3090           | 3279        | 3462        | 3469           | ps   |

|                     | (1)          | t <sub>DIP</sub> | 1594                      | 1673            | 3260           | 3473        | 3688        | 3688           | ps   |

| 1.8V_DIFFERENTIAL   | 16 mA        | t <sub>OP</sub>  | 1449                      | 1520            | 2936           | 3107        | 3271        | 3278           | ps   |

| _HSTL_CLASS_II      |              | t <sub>DIP</sub> | 1581                      | 1659            | 3106           | 3301        | 3497        | 3497           | ps   |

|                     | 18 mA        | t <sub>OP</sub>  | 1450                      | 1521            | 2924           | 3101        | 3272        | 3279           | ps   |

|                     |              | t <sub>DIP</sub> | 1582                      | 1660            | 3094           | 3295        | 3498        | 3498           | ps   |

|                     | 20 mA        | t <sub>OP</sub>  | 1452                      | 1523            | 2926           | 3096        | 3259        | 3266           | ps   |

|                     | (1)          | t <sub>DIP</sub> | 1584                      | 1662            | 3096           | 3290        | 3485        | 3485           | ps   |

| 1.5V_DIFFERENTIAL   | 8 mA         | t <sub>OP</sub>  | 1779                      | 1866            | 4292           | 4637        | 4974        | 4981           | ps   |

| _HSTL_CLASS_I       |              | t <sub>DIP</sub> | 1911                      | 2005            | 4462           | 4831        | 5200        | 5200           | ps   |

|                     | 10 mA        | t <sub>OP</sub>  | 1784                      | 1872            | 4031           | 4355        | 4673        | 4680           | ps   |

|                     |              | t <sub>DIP</sub> | 1916                      | 2011            | 4201           | 4549        | 4899        | 4899           | ps   |

|                     | 12 mA        | t <sub>OP</sub>  | 1784                      | 1872            | 4031           | 4355        | 4673        | 4680           | ps   |

|                     | (1)          | t <sub>DIP</sub> | 1916                      | 2011            | 4201           | 4549        | 4899        | 4899           | ps   |

| Table 5–43. Cyc | lone II I/O (     | Output Delay     | for Row Pins                   | s (Part 1 of    | 4)                   |                       |                       |                      |      |

|-----------------|-------------------|------------------|--------------------------------|-----------------|----------------------|-----------------------|-----------------------|----------------------|------|

|                 |                   |                  | Fast (                         | Corner          | c                    | -7                    | -7                    | 0                    |      |

| I/O Standard    | Drive<br>Strength | Parameter        | Industrial<br>/Auto-<br>motive | Commer-<br>cial | -6<br>Speed<br>Grade | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | –8<br>Speed<br>Grade | Unit |

| LVTTL           | 4 mA              | t <sub>OP</sub>  | 1343                           | 1408            | 2539                 | 2694                  | 2885                  | 2891                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1467                           | 1540            | 2747                 | 2931                  | 3158                  | 3158                 | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 1198                           | 1256            | 2411                 | 2587                  | 2756                  | 2762                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1322                           | 1388            | 2619                 | 2824                  | 3029                  | 3029                 | ps   |

|                 | 12 mA             | t <sub>OP</sub>  | 1156                           | 1212            | 2282                 | 2452                  | 2614                  | 2620                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1280                           | 1344            | 2490                 | 2689                  | 2887                  | 2887                 | ps   |

|                 | 16 mA             | t <sub>OP</sub>  | 1124                           | 1178            | 2286                 | 2455                  | 2618                  | 2624                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1248                           | 1310            | 2494                 | 2692                  | 2891                  | 2891                 | ps   |

|                 | 20 mA             | t <sub>OP</sub>  | 1112                           | 1165            | 2245                 | 2413                  | 2574                  | 2580                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1236                           | 1297            | 2453                 | 2650                  | 2847                  | 2847                 | ps   |

|                 | 24 mA             | t <sub>OP</sub>  | 1105                           | 1158            | 2253                 | 2422                  | 2583                  | 2589                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 1229                           | 1290            | 2461                 | 2659                  | 2856                  | 2856                 | ps   |

| LVCMOS          | 4 mA              | t <sub>OP</sub>  | 1200                           | 1258            | 2231                 | 2396                  | 2555                  | 2561                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1324                           | 1390            | 2439                 | 2633                  | 2828                  | 2828                 | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 1125                           | 1179            | 2260                 | 2429                  | 2591                  | 2597                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1249                           | 1311            | 2468                 | 2666                  | 2864                  | 2864                 | ps   |

|                 | 12 mA             | t <sub>OP</sub>  | 1106                           | 1159            | 2217                 | 2383                  | 2543                  | 2549                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 1230                           | 1291            | 2425                 | 2620                  | 2816                  | 2816                 | ps   |

| 2.5V            | 4 mA              | t <sub>OP</sub>  | 1126                           | 1180            | 2350                 | 2477                  | 2598                  | 2604                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1250                           | 1312            | 2558                 | 2714                  | 2871                  | 2871                 | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 1105                           | 1158            | 2177                 | 2296                  | 2409                  | 2415                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 1229                           | 1290            | 2385                 | 2533                  | 2682                  | 2682                 | ps   |

### **PLL Timing Specifications**

Table 5–54 describes the Cyclone II PLL specifications when operating in the commercial junction temperature range (0° to 85° C), the industrial junction temperature range (–40° to 100° C), the automotive junction temperature range (–40° to 125° C), and the extended temperature range (–40° to 125° C). Follow the PLL specifications for –8 speed grade devices when operating in the industrial, automotive, or extended temperature range.

| Symbol                             | Parameter                                                              | Min | Тур | Max     | Unit |

|------------------------------------|------------------------------------------------------------------------|-----|-----|---------|------|

| f <sub>IN</sub>                    | Input clock frequency (–6 speed grade)                                 | 10  | _   | (4)     | MHz  |

|                                    | Input clock frequency (–7 speed grade)                                 | 10  | _   | (4)     | MHz  |

|                                    | Input clock frequency (–8 speed grade)                                 | 10  | _   | (4)     | MHz  |

| f <sub>INPFD</sub>                 | PFD input frequency (-6 speed grade)                                   | 10  | _   | 402.5   | MHz  |

|                                    | PFD input frequency (-7 speed grade)                                   | 10  | _   | 402.5   | MHz  |

|                                    | PFD input frequency (–8 speed grade)                                   | 10  | _   | 402.5   | MHz  |

| f <sub>INDUTY</sub>                | Input clock duty cycle                                                 | 40  | _   | 60      | %    |

| t <sub>INJITTER</sub> (5)          | Input clock period jitter                                              | _   | 200 | _       | ps   |

| f <sub>OUT_EXT</sub> (external     | PLL output frequency (–6 speed grade)                                  | 10  | _   | (4)     | MHz  |

| clock output)                      | PLL output frequency (-7 speed grade)                                  | 10  | _   | (4)     | MHz  |

|                                    | PLL output frequency (–8 speed grade)                                  | 10  | _   | (4)     | MHz  |

| f <sub>OUT</sub> (to global clock) | PLL output frequency (–6 speed grade)                                  | 10  | _   | 500     | MHz  |

|                                    | PLL output frequency (–7 speed grade)                                  | 10  | _   | 450     | MHz  |

|                                    | PLL output frequency (-8 speed grade)                                  | 10  | _   | 402.5   | MHz  |

| toutduty                           | Duty cycle for external clock output (when set to 50%)                 | 45  | _   | 55      | %    |

| t <sub>JITTER</sub> (p-p) (2)      | Period jitter for external clock output f <sub>OUT_EXT</sub> > 100 MHz | _   | _   | 300     | ps   |

|                                    | f <sub>OUT_EXT</sub> ≤100 MHz                                          | _   | _   | 30      | mUI  |

| t <sub>LOCK</sub>                  | Time required to lock from end of device configuration                 | _   | _   | 100 (6) | μs   |

| t <sub>PLL PSERR</sub>             | Accuracy of PLL phase shift                                            | _   | _   | ±60     | ps   |

### PLL Specifications

See the *DC & Switching Characteristics* chapter in Volume 1 of the *Cyclone II Device Handbook* for information on PLL timing specifications.

### **Clocking**

Cyclone II devices provide up to 16 dedicated clock pins (CLK[15..0]) that can drive the global clock networks. The smaller Cyclone II devices (EP2C5 and EP2C8 devices) support four dedicated clock pins on each side (left and right) capable of driving a total of eight global clock networks, while the larger devices (EP2C15 devices and larger) support four clock pins on all four sides of the device. These clock pins can drive a total of 16 global clock networks.

Table 7–7 shows the number of global clocks available across the Cyclone II family members.

| Table 7–7. Number of Global Clocks Available in Cyclone II Devices |    |  |  |  |  |

|--------------------------------------------------------------------|----|--|--|--|--|

| Device Number of Global Clocks                                     |    |  |  |  |  |

| EP2C5                                                              | 8  |  |  |  |  |

| EP2C8                                                              | 8  |  |  |  |  |

| EP2C15                                                             | 16 |  |  |  |  |

| EP2C20                                                             | 16 |  |  |  |  |

| EP2C35                                                             | 16 |  |  |  |  |

| EP2C50                                                             | 16 |  |  |  |  |

| EP2C70                                                             | 16 |  |  |  |  |

#### **Global Clock Network**

Global clocks drive throughout the entire device, feeding all device quadrants. All resources within the device (IOEs, logic array blocks (LABs), dedicated multiplier blocks, and M4K memory blocks) can use the global clock networks as clock sources. These clock network resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed by an external pin. Internal logic can also drive the global clock networks for internally generated global clocks and asynchronous clears, clock enables, or other control signals with high fan-out.

- $4K \times 1$

- $2K \times 2$

- $\blacksquare$  1K × 4

- 512 × 8

- 512 × 9

- 256 × 16

- 256 × 18

- $128 \times 32$

- 128 × 36

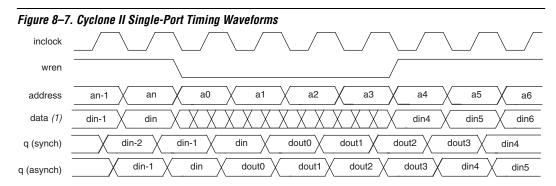

Figure 8–7 shows timing waveforms for read and write operations in single-port mode.

#### Note to Figure 8-7:

(1) The crosses in the data waveform during read mean "don't care."

### **Simple Dual-Port Mode**

Simple dual-port mode supports simultaneous read and write operation. Figure 8–8 shows the simple dual-port memory configuration.

You can use any of the user I/O pins for commands and addresses. Because of the symmetrical setup and hold time for the command and address pins at the memory device, you may need to generate these signals from the negative edge of the system clock.

The clocks to the SDRAM device are called CK and CK#. Use any of the user I/O pins via the DDR registers to generate the CK and CK# signals to meet the  $t_{\rm DQSS}$  requirements of the DDR SDRAM or DDR2 SDRAM device. The memory device's  $t_{\rm DQSS}$  requires the positive edge of the write DQS signal to be within 25% of the positive edge of the DDR SDRAM and DDR2 SDRAM clock input. Because of strict skew requirements between CK and CK# signals, use adjacent pins to generate the clock pair. Surround the pair with buffer pins tied to  $V_{\rm CC}$  and pins tied to ground for better noise immunity from other signals.

### Read & Write Operation

When reading from the memory, DDR and DDR2 SDRAM devices send the data edge-aligned relative to the data strobe. To properly read the data, the data strobe must be center-aligned relative to the data inside the FPGA. Cyclone II devices feature clock delay control circuitry to shift the data strobe to the middle of the data window. Figure 9–1 shows an example of how the memory sends out the data and data strobe for a burst-of-two operation.

| Table 10–2. Cyclone II 66-MHz PCI Support (Part 2 of 2) |                      |                        |         |  |  |

|---------------------------------------------------------|----------------------|------------------------|---------|--|--|

| Davies                                                  | Package -            | –6 and –7 Speed Grades |         |  |  |

| Device                                                  |                      | 64 Bits                | 32 Bits |  |  |

| EP2C8                                                   | 144-pin TQFP         |                        |         |  |  |

|                                                         | 208-pin PQFP         |                        | ✓       |  |  |

|                                                         | 256-pin FineLine BGA |                        | ✓       |  |  |

| EP2C15                                                  | 256-pin FineLine BGA |                        | ✓       |  |  |

|                                                         | 484-pin FineLine BGA | ✓                      | ✓       |  |  |

| EP2C20                                                  | 240-pin PQFP         |                        | ✓       |  |  |

|                                                         | 256-pin FineLine BGA |                        | ✓       |  |  |

|                                                         | 484-pin FineLine BGA | ✓                      | ✓       |  |  |

| EP2C35                                                  | 484-pin FineLine BGA | ✓                      | ✓       |  |  |

|                                                         | 672-pin FineLine BGA | ✓                      | ✓       |  |  |

| EP2C50                                                  | 484-pin FineLine BGA | ✓                      | ✓       |  |  |

|                                                         | 672-pin FineLine BGA | <b>✓</b>               | ✓       |  |  |

| EP2C70                                                  | 672-pin FineLine BGA | <b>✓</b>               | ✓       |  |  |

|                                                         | 896-pin FineLine BGA | ✓                      | ✓       |  |  |

Table 10–3 lists the specific Cyclone II devices that support 64-bit and 32-bit PCI at 33 MHz.

| Table 10–3. Cyclone II 33-MHz PCI Support (Part 1 of 2) |                      |                            |          |  |  |

|---------------------------------------------------------|----------------------|----------------------------|----------|--|--|

| Device                                                  | Package              | –6, –7 and –8 Speed Grades |          |  |  |

|                                                         |                      | 64 Bits                    | 32 Bits  |  |  |

| EP2C5                                                   | 144-pin TQFP         | _                          | _        |  |  |

|                                                         | 208-pin PQFP         | _                          | ✓        |  |  |

|                                                         | 256-pin FineLine BGA | _                          | ✓        |  |  |

| EP2C8                                                   | 144-pin TQFP         | _                          | _        |  |  |

|                                                         | 208-pin PQFP         | _                          | <b>✓</b> |  |  |

|                                                         | 256-pin FineLine BGA | _                          | ✓        |  |  |

| EP2C15                                                  | 256-pin FineLine BGA | _                          | ✓        |  |  |

|                                                         | 484-pin FineLine BGA | ✓                          | <b>✓</b> |  |  |

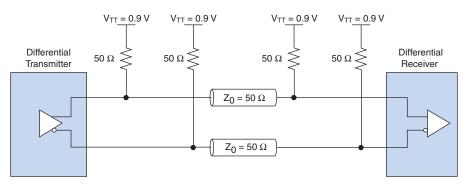

Figure 10-12. 1.8-V Differential HSTL Class II Termination

### 1.5-V LVCMOS (EIA/JEDEC Standard JESD8-11)

The 1.5-V I/O standard is used for 1.5-V applications. This standard defines the DC interface parameters for high-speed, low-voltage, non-terminated digital circuits driving or being driven by other 1.5-V devices.

The 1.5-V standard does not require input reference voltages or board terminations. Cyclone II devices support input and output levels for 1.5-V LVCMOS.

#### 1.5-V HSTL Class I and II

The 1.5-V HSTL standard is formulated under EIA/JEDEC Standard, EIA/JESD8-6: A 1.5V Output Buffer Supply Voltage Based Interface Standard for Digital Integrated Circuits.

The 1.5-V HSTL I/O standard is used for applications designed to operate in the 0.0- to 1.5-V HSTL logic nominal switching range. This standard defines single-ended input and output specifications for all HSTL-compliant digital integrated circuits. The 1.5-V HSTL I/O standard in Cyclone II devices is compatible with the 1.8-V HSTL I/O standard in APEXTM 20KE, APEX 20KC, Stratix  $^{\tiny \odot}$  II, Stratix GX, Stratix, and in Cyclone II devices themselves because the input and output voltage thresholds are compatible. Refer to Figures 10–13 and 10–14. Cyclone II devices support both input and output levels with  $V_{\rm REF}$  and  $V_{\rm TT}$

it feeds the next device's nCE pin. After the first device in the chain completes configuration, its nCEO pin transitions low to activate the second device's nCE pin, which prompts the second device to begin configuration. You can leave the nCEO pin of the last device unconnected or use it as a user I/O pin after configuration. The nCEO pin is a dual-purpose pin in Cyclone II devices.

The Quartus II software sets the Cyclone II device <code>nCEO</code> pin as an output pin driving to ground by default. If the device is in a chain, and the <code>nCEO</code> pin is connected to the next device's <code>nCE</code> pin, you must make sure that the <code>nCEO</code> pin is not used as a user I/O pin after configuration. This software setting is in the <code>Dual-Purpose Pins</code> tab of the <code>Device & Pin Options</code> dialog box in Quartus II software.

Connect all other configuration pins (nconfig, nstatus, dclk, data), and conf\_done) to every Cyclone II device in the chain. The configuration signals may require buffering to ensure signal integrity and prevent clock skew problems. Buffer the DCLK and DATA lines for every fourth device.

When configuring multiple devices, configuration does not begin until all devices release their OE or nSTATUS pins. Similarly, since all device CONF\_DONE pins are tied together, all devices initialize and enter user mode at the same time.

You should not pull CONF\_DONE low to delay initialization. Instead, use the Quartus II software's **User-Supplied Start-Up Clock** option to synchronize the initialization of multiple devices that are not in the same configuration chain. Devices in the same configuration chain initialize together since their CONF\_DONE pins are tied together.

Since all nSTATUS and CONF\_DONE pins are connected, if any device detects an error, configuration stops for the entire chain and the entire chain must be reconfigured. For example, if there is an error when configuring the first Cyclone II device, it resets the chain by pulling its nSTATUS pin low. This low signal drives the OE pin low on the enhanced configuration device and drives nSTATUS low on all FPGAs, which causes them to enter a reset state.

If the **Auto-restart configuration after error** option is turned on, the devices automatically initiate reconfiguration if an error occurs. The FPGAs release their nSTATUS pins after a reset time-out period (40 µs maximum). When all the nSTATUS pins are released and pulled high, the configuration device reconfigures the chain. If the **Auto-restart configuration after error** option is turned off, a microprocessor or controller must monitor the nSTATUS pin for errors and then pulse

## 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices

CII51014-2.1

### Introduction

As printed circuit boards (PCBs) become more complex, the need for thorough testing becomes increasingly important. Advances in surface-mount packaging and PCB manufacturing have resulted in smaller boards, making traditional test methods (e.g., external test probes and "bed-of-nails" test fixtures) harder to implement. As a result, cost savings from PCB space reductions are sometimes offset by cost increases in traditional testing methods.

In the 1980s, the Joint Test Action Group (JTAG) developed a specification for boundary-scan testing that was later standardized as the IEEE Std. 1149.1 specification. This boundary-scan test (BST) architecture offers the capability to efficiently test components on PCBs with tight lead spacing.

This BST architecture tests pin connections without using physical test probes and captures functional data while a device is operating normally. Boundary-scan cells in a device force signals onto pins or capture data from pin or logic array signals. Forced test data is serially shifted into the boundary-scan cells. Captured data is serially shifted out and externally compared with expected results. Figure 14–1 shows the concept of boundary-scan testing.

Serial Data In IC Pin Signal Serial Data Out

Tested Connection JTAG Device 2

Figure 14-1. IEEE Std. 1149.1 Boundary-Scan Testing

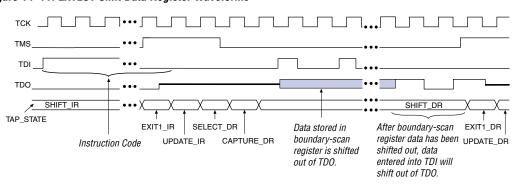

EXTEST selects data differently than SAMPLE/PRELOAD. EXTEST chooses data from the update registers as the source of the output and output enable signals. Once the EXTEST instruction code is entered, the multiplexers select the update register data. Thus, data stored in these registers from a previous EXTEST or SAMPLE/PRELOAD test cycle can be forced onto the pin signals. In the capture phase, the results of this test data are stored in the capture registers, then shifted out of TDO during the shift phase. New test data can then be stored in the update registers during the update phase.

The EXTEST waveform diagram in Figure 14–11 resembles the SAMPLE/PRELOAD waveform diagram, except for the instruction code. The data shifted out of TDO consists of the data that was present in the capture registers after the capture phase. New test data shifted into the TDI pin appears at the TDO pin after being clocked through the entire boundary-scan register.

Figure 14-11. EXTEST Shift Data Register Waveforms

#### **BYPASS Instruction Mode**

The BYPASS mode is activated when an instruction code of all 1's is loaded in the instruction register. The waveforms in Figure 14–12 show how scan data passes through a device once the TAP controller is in the SHIFT\_DR state. In this state, data signals are clocked into the bypass register from TDI on the rising edge of TCK and out of TDO on the falling edge of the same clock pulse.

Table 15–2. Thermal Resistance of Cyclone II Devices for Board Meeting JEDEC Specifications (Part 2 of 2)  $\theta_{JA}$  (° C/W)  $\theta_{JA}$  (° C/W)  $\theta_{JA}$  (° C/W)  $\theta_{JA}$  (° C/W) Pin  $\theta_{\text{JC}}$ Device **Package** Count Still Air 100 ft./min. 200 ft./min. 400 ft./min. (° C/W) EP2C50 484 FineLine BGA 18.4 12.4 10.9 14.4 2.8 484 Ultra FineLine BGA 19.6 15.6 13.6 11.9 4.4 672 FineLine BGA 17.7 13.7 11.8 10.2 2.6 EP2C70 672 FineLine BGA 16.9 13 9.7 2.2 11.1 896 FineLine BGA 16.3 11.9 10.5 2.1 9.1

Table 15–3 provides board dimension information for each package.

| Table 15–3. PCB Dimensions Notes (1), (2) |                  |                        |                              |                            |  |  |

|-------------------------------------------|------------------|------------------------|------------------------------|----------------------------|--|--|

| 2.5 mm<br>Thick                           | Signal<br>Layers | Power/Ground<br>Layers | Package<br>Dimension<br>(mm) | Board<br>Dimension<br>(mm) |  |  |

| F896                                      | 10               | 10                     | 31                           | 91                         |  |  |

| F672                                      | 8                | 8                      | 27                           | 87                         |  |  |

| F672                                      | 7                | 7                      | 27                           | 87                         |  |  |

| F484                                      | 7                | 7                      | 23                           | 83                         |  |  |

| F484                                      | 6                | 6                      | 23                           | 83                         |  |  |

| U484                                      | 7                | 7                      | 19                           | 79                         |  |  |

| U484                                      | 6                | 6                      | 19                           | 79                         |  |  |

| F256                                      | 6                | 6                      | 17                           | 77                         |  |  |

Notes to Table 15-3:

<sup>(1)</sup> Power layer Cu thickness 35 um, Cu 90%

<sup>(2)</sup> Signal layer Cu thickness 17 um, Cu 15%