## Intel - EP2C5T144C8N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                  |

|--------------------------------|---------------------------------------------------------|

| Number of LABs/CLBs            | 288                                                     |

| Number of Logic Elements/Cells | 4608                                                    |

| Total RAM Bits                 | 119808                                                  |

| Number of I/O                  | 89                                                      |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 144-LQFP                                                |

| Supplier Device Package        | 144-TQFP (20x20)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c5t144c8n |

|                                |                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices

| Introduction                                       |       |

|----------------------------------------------------|-------|

| IEEE Std. 1149.1 BST Architecture                  |       |

| IEEE Std. 1149.1 Boundary-Scan Register            |       |

| Boundary-Scan Cells of a Cyclone II Device I/O Pin |       |

| IEEE Std. 1149.1 BST Operation Control             |       |

| SAMPLE/PRELOAD Instruction Mode                    |       |

| Capture Phase                                      | 14–10 |

| Shift & Update Phases                              | 14–10 |

| EXTEST Instruction Mode                            |       |

| Capture Phase                                      |       |

| Shift & Update Phases                              |       |

| BYPASS Instruction Mode                            |       |

| IDCODE Instruction Mode                            |       |

| USERCODE Instruction Mode                          |       |

| CLAMP Instruction Mode                             |       |

| HIGHZ Instruction Mode                             |       |

| I/O Voltage Support in JTAG Chain                  | 14–15 |

| Using IEEE Std. 1149.1 BST Circuitry               | 14–16 |

| BST for Configured Devices                         |       |

| Disabling IEEE Std. 1149.1 BST Circuitry           |       |

|                                                    |       |

A LAB-wide asynchronous load signal to control the logic for the register's preset signal is not available. The register preset is achieved by using a NOT gate push-back technique. Cyclone II devices can only support either a preset or asynchronous clear signal.

In addition to the clear port, Cyclone II devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals.

# MultiTrack Interconnect

In the Cyclone II architecture, connections between LEs, M4K memory blocks, embedded multipliers, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive<sup>™</sup> technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement within the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

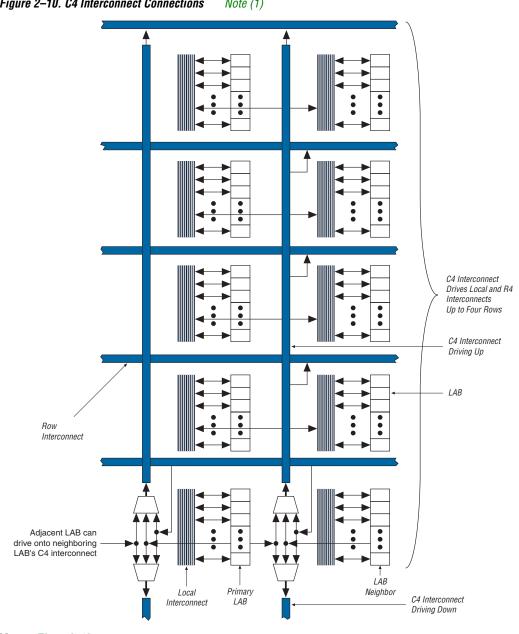

The MultiTrack interconnect consists of row (direct link, R4, and R24) and column (register chain, C4, and C16) interconnects that span fixed distances. A routing structure with fixed-length resources for all devices allows predictable and repeatable performance when migrating through different device densities.

## **Row Interconnects**

Dedicated row interconnects route signals to and from LABs, PLLs, M4K memory blocks, and embedded multipliers within the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks

- R4 interconnects traversing four blocks to the right or left

- R24 interconnects for high-speed access across the length of the device

Figure 2–10. C4 Interconnect Connections Note (1)

Note to Figure 2–10: (1) Each C4 interconnect can drive either up or down four rows.

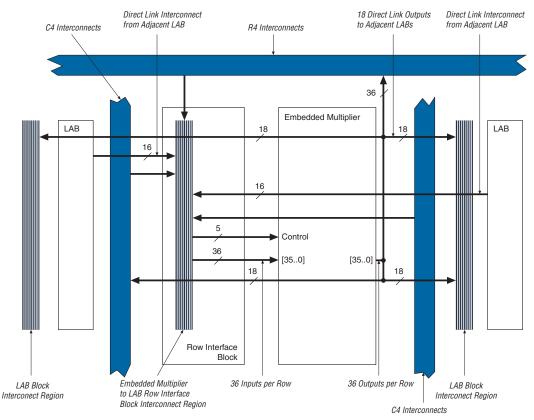

# **Embedded Multiplier Routing Interface**

The R4, C4, and direct link interconnects from adjacent LABs drive the embedded multiplier row interface interconnect. The embedded multipliers can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 16 direct link input connections to the embedded multiplier are possible from the left adjacent LABs and another 16 possible from the right adjacent LABs. Embedded multiplier outputs can also connect to left and right LABs through 18 direct link interconnects each. Figure 2–19 shows the embedded multiplier to logic array interface.

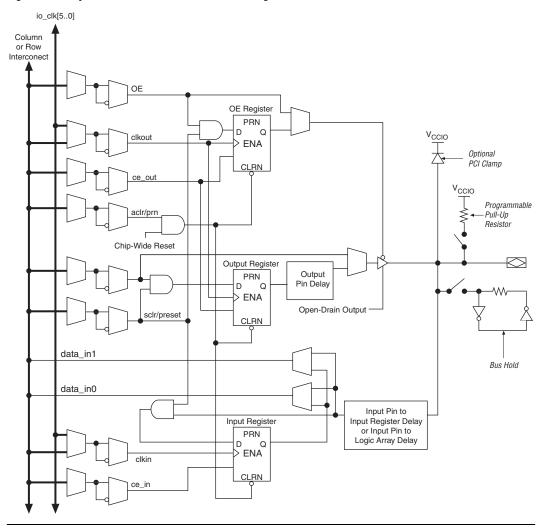

Figure 2–25. Cyclone II IOE in Bidirectional I/O Configuration

The Cyclone II device IOE includes programmable delays to ensure zero hold times, minimize setup times, or increase clock to output times.

A path in which a pin directly drives a register may require a programmable delay to ensure zero hold time, whereas a path in which a pin drives a register through combinational logic may not require the delay. Programmable delays decrease input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time.

| Table 2–15. Cyclone II DQS & DQ Bus Mode Support (Part 2 of 2) Note (1) |                      |                        |                                 |                         |                                  |  |  |  |

|-------------------------------------------------------------------------|----------------------|------------------------|---------------------------------|-------------------------|----------------------------------|--|--|--|

| Device                                                                  | Package              | Number of ×8<br>Groups | Number of ×9<br>Groups (5), (6) | Number of ×16<br>Groups | Number of ×18<br>Groups (5), (6) |  |  |  |

| EP2C35                                                                  | 484-pin FineLine BGA | 16 (4)                 | 8                               | 8                       | 8                                |  |  |  |

|                                                                         | 672-pin FineLine BGA | 20 (4)                 | 8                               | 8                       | 8                                |  |  |  |

| EP2C50                                                                  | 484-pin FineLine BGA | 16 <i>(4)</i>          | 8                               | 8                       | 8                                |  |  |  |

|                                                                         | 672-pin FineLine BGA | 20 (4)                 | 8                               | 8                       | 8                                |  |  |  |

| EP2C70                                                                  | 672-pin FineLine BGA | 20 (4)                 | 8                               | 8                       | 8                                |  |  |  |

|                                                                         | 896-pin FineLine BGA | 20 (4)                 | 8                               | 8                       | 8                                |  |  |  |

#### Notes to Table 2–15:

(1) Numbers are preliminary.

(2) EP2C5 and EP2C8 devices in the 144-pin TQFP package do not have any DQ pin groups in I/O bank 1.

(3) Because of available clock resources, only a total of 6 DQ/DQS groups can be implemented.

(4) Because of available clock resources, only a total of 14 DQ/DQS groups can be implemented.

(5) The ×9 DQS/DQ groups are also used as ×8 DQS/DQ groups. The ×18 DQS/DQ groups are also used as ×16 DQS/DQ groups.

(6) For QDRI implementation, if you connect the D ports (write data) to the Cyclone II DQ pins, the total available ×9 DQS /DQ and ×18 DQS/DQ groups are half of that shown in Table 2–15.

> You can use any of the DQ pins for the parity pins in Cyclone II devices. The Cyclone II device family supports parity in the  $\times 8/\times 9$ , and  $\times 16/\times 18$ mode. There is one parity bit available per eight bits of data pins.

> The data mask, DM, pins are required when writing to DDR SDRAM and DDR2 SDRAM devices. A low signal on the DM pin indicates that the write is valid. If the DM signal is high, the memory masks the DQ signals. In Cyclone II devices, the DM pins are assigned and are the preferred pins. Each group of DQS and DQ signals requires a DM pin.

> When using the Cyclone II I/O banks to interface with the DDR memory, at least one PLL with two clock outputs is needed to generate the system and write clock. The system clock is used to clock the DQS write signals, commands, and addresses. The write clock is shifted by  $-90^{\circ}$  from the system clock and is used to clock the DQ signals during writes.

Figure 2–27 illustrates DDR SDRAM interfacing from the I/O through the dedicated circuitry to the logic array.

# Programmable Drive Strength

The output buffer for each Cyclone II device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL, LVCMOS, SSTL-2 class I and II, SSTL-18 class I and II, HSTL-18 class I and II, and HSTL-1.5 class I and II standards have several levels of drive strength that you can control. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot. Table 2–16 shows the possible settings for the I/O standards with drive strength control.

|                    | I <sub>OH</sub> /I <sub>OL</sub> Current Strer | ngth Setting (mA) |  |  |

|--------------------|------------------------------------------------|-------------------|--|--|

| I/O Standard       | Top & Bottom I/O Pins                          | Side I/O Pins     |  |  |

| /TTL (3.3 V)       | 4                                              | 4                 |  |  |

|                    | 8                                              | 8                 |  |  |

|                    | 12                                             | 12                |  |  |

|                    | 16                                             | 16                |  |  |

|                    | 20                                             | 20                |  |  |

|                    | 24                                             | 24                |  |  |

| /CMOS (3.3 V)      | 4                                              | 4                 |  |  |

|                    | 8                                              | 8                 |  |  |

|                    | 12                                             | 12                |  |  |

|                    | 16                                             |                   |  |  |

|                    | 20                                             |                   |  |  |

|                    | 24                                             |                   |  |  |

| TTL/LVCMOS (2.5 V) | 4                                              | 4                 |  |  |

|                    | 8                                              | 8                 |  |  |

|                    | 12                                             |                   |  |  |

|                    | 16                                             |                   |  |  |

| TTL/LVCMOS (1.8 V) | 2                                              | 2                 |  |  |

|                    | 4                                              | 4                 |  |  |

|                    | 6                                              | 6                 |  |  |

|                    | 8                                              | 8                 |  |  |

|                    | 10                                             | 10                |  |  |

|                    | 12                                             | 12                |  |  |

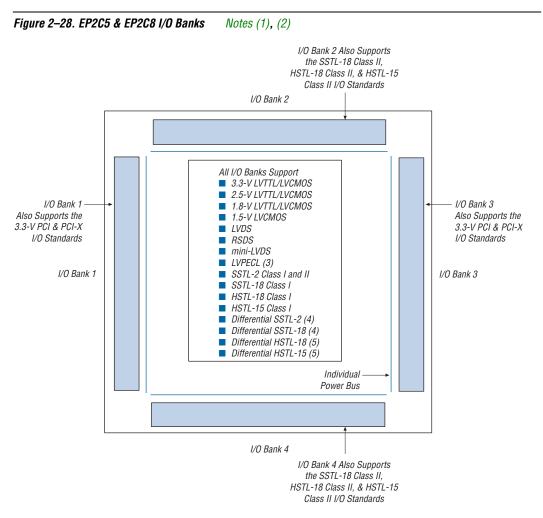

#### Notes to Figure 2–28:

- (1) This is a top view of the silicon die.

- (2) This is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (5) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

| Table 5–11. Bus Hold Para         | nmeters Note (1)                               |      |      |                   |       |     |      |      |

|-----------------------------------|------------------------------------------------|------|------|-------------------|-------|-----|------|------|

|                                   |                                                |      |      | V <sub>ccio</sub> | Level |     |      |      |

| Parameter                         | Conditions                                     | 1.8  | 8 V  | 2.5               | 5 V   | 3.3 | 3 V  | Unit |

|                                   |                                                | Min  | Max  | Min               | Max   | Min | Max  |      |

| Bus-hold low, sustaining current  | V <sub>IN</sub> ><br>V <sub>IL</sub> (maximum) | 30   | _    | 50                | _     | 70  | _    | μA   |

| Bus-hold high, sustaining current | V <sub>IN</sub> <<br>V <sub>IL</sub> (minimum) | -30  | —    | -50               | _     | -70 | —    | μA   |

| Bus-hold low, overdrive current   | $0 V < V_{IN} < V_{CCIO}$                      | —    | 200  |                   | 300   |     | 500  | μA   |

| Bus-hold high, overdrive current  | $0 V < V_{\rm IN} < V_{\rm CCIO}$              | —    | -200 | _                 | -300  | _   | -500 | μA   |

| Bus-hold trip point (2)           | _                                              | 0.68 | 1.07 | 0.7               | 1.7   | 0.8 | 2.0  | V    |

Table 5–11 specifies the bus hold parameters for general I/O pins.

#### Notes to Table 5–11:

(1) There is no specification for bus-hold at  $V_{CCIO}$  = 1.5 V for the HSTL I/O standard.

(2) The bus-hold trip points are based on calculated input voltages from the JEDEC standard.

# **On-Chip Termination Specifications**

Table 5–12 defines the specifications for internal termination resistance tolerance when using series or differential on-chip termination.

| Table 5–1           | Table 5–12. Series On-Chip Termination Specifications                      |                          |                   |                   |                                     |      |  |  |  |  |

|---------------------|----------------------------------------------------------------------------|--------------------------|-------------------|-------------------|-------------------------------------|------|--|--|--|--|

|                     |                                                                            |                          | F                 | Resistance T      | olerance                            |      |  |  |  |  |

| Symbol              | Description                                                                | Conditions               | Commercial<br>Max | Industrial<br>Max | Extended/<br>Automotive<br>Temp Max | Unit |  |  |  |  |

| $25-\Omega R_S$     | Internal series termination without calibration ( $25$ - $\Omega$ setting) | V <sub>CCIO</sub> = 3.3V | ±30               | ±30               | ±40                                 | %    |  |  |  |  |

| 50-Ω R <sub>S</sub> | Internal series termination without calibration ( $50-\Omega$ setting)     | V <sub>CCIO</sub> = 2.5V | ±30               | ±30               | ±40                                 | %    |  |  |  |  |

| $50-\Omega R_S$     | Internal series termination without calibration (50- $\Omega$ setting)     | $V_{CCIO} = 1.8V$        | ±30 (1)           | ±40               | ±50                                 | %    |  |  |  |  |

Note to Table 5–12:

(1) For commercial -8 devices, the tolerance is  $\pm 40\%$ .

|              |                   |                  | Fast Co                   | rner            | -6             | -7<br>Speed<br>Grade<br>(2) | -7<br>Speed<br>Grade<br>(3) | -8             |      |

|--------------|-------------------|------------------|---------------------------|-----------------|----------------|-----------------------------|-----------------------------|----------------|------|

| I/O Standard | Drive<br>Strength | Parameter        | Industrial/<br>Automotive | Commer<br>-cial | Speed<br>Grade |                             |                             | Speed<br>Grade | Unit |

| LVTTL        | 4 mA              | t <sub>OP</sub>  | 1524                      | 1599            | 2903           | 3125                        | 3341                        | 3348           | ps   |

|              |                   | t <sub>DIP</sub> | 1656                      | 1738            | 3073           | 3319                        | 3567                        | 3567           | ps   |

|              | 8 mA              | t <sub>OP</sub>  | 1343                      | 1409            | 2670           | 2866                        | 3054                        | 3061           | ps   |

|              |                   | t <sub>DIP</sub> | 1475                      | 1548            | 2840           | 3060                        | 3280                        | 3280           | ps   |

|              | 12 mA             | t <sub>OP</sub>  | 1287                      | 1350            | 2547           | 2735                        | 2917                        | 2924           | ps   |

|              |                   | t <sub>DIP</sub> | 1419                      | 1489            | 2717           | 2929                        | 3143                        | 3143           | ps   |

|              | 16 mA             | t <sub>OP</sub>  | 1239                      | 1299            | 2478           | 2665                        | 2844                        | 2851           | ps   |

|              |                   | t <sub>DIP</sub> | 1371                      | 1438            | 2648           | 2859                        | 3070                        | 3070           | ps   |

|              | 20 mA             | t <sub>OP</sub>  | 1228                      | 1288            | 2456           | 2641                        | 2820                        | 2827           | ps   |

|              |                   | t <sub>DIP</sub> | 1360                      | 1427            | 2626           | 2835                        | 3046                        | 3046           | ps   |

|              | 24 mA<br>(1)      | t <sub>OP</sub>  | 1220                      | 1279            | 2452           | 2637                        | 2815                        | 2822           | ps   |

|              |                   | t <sub>DIP</sub> | 1352                      | 1418            | 2622           | 2831                        | 3041                        | 3041           | ps   |

| LVCMOS       | 4 mA              | t <sub>OP</sub>  | 1346                      | 1412            | 2509           | 2695                        | 2873                        | 2880           | ps   |

|              |                   | t <sub>DIP</sub> | 1478                      | 1551            | 2679           | 2889                        | 3099                        | 3099           | ps   |

|              | 8 mA              | t <sub>OP</sub>  | 1240                      | 1300            | 2473           | 2660                        | 2840                        | 2847           | ps   |

|              |                   | t <sub>DIP</sub> | 1372                      | 1439            | 2643           | 2854                        | 3066                        | 3066           | ps   |

|              | 12 mA             | t <sub>OP</sub>  | 1221                      | 1280            | 2428           | 2613                        | 2790                        | 2797           | ps   |

|              |                   | t <sub>DIP</sub> | 1353                      | 1419            | 2598           | 2807                        | 3016                        | 3016           | ps   |

|              | 16 mA             | t <sub>OP</sub>  | 1203                      | 1262            | 2403           | 2587                        | 2765                        | 2772           | ps   |

|              |                   | t <sub>DIP</sub> | 1335                      | 1401            | 2573           | 2781                        | 2991                        | 2991           | ps   |

|              | 20 mA             | t <sub>OP</sub>  | 1194                      | 1252            | 2378           | 2562                        | 2738                        | 2745           | ps   |

|              |                   | t <sub>DIP</sub> | 1326                      | 1391            | 2548           | 2756                        | 2964                        | 2964           | ps   |

|              | 24 mA             | t <sub>OP</sub>  | 1192                      | 1250            | 2382           | 2566                        | 2742                        | 2749           | ps   |

|              | (1)               | t <sub>DIP</sub> | 1324                      | 1389            | 2552           | 2760                        | 2968                        | 2968           | ps   |

|              |                   |                  | Fast                           | Corner          | 6                    | -7                    | -7                                    | •                    |      |

|--------------|-------------------|------------------|--------------------------------|-----------------|----------------------|-----------------------|---------------------------------------|----------------------|------|

| I/O Standard | Drive<br>Strength | Parameter        | Industrial<br>/Auto-<br>motive | Commer-<br>cial | –6<br>Speed<br>Grade | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3)                 | –8<br>Speed<br>Grade | Unit |

| 1.8V         | 2 mA              | t <sub>OP</sub>  | 1503                           | 1576            | 3657                 | 3927                  | 4190                                  | 4196                 | ps   |

|              |                   | t <sub>DIP</sub> | 1627                           | 1708            | 3865                 | 4164                  | 4463                                  | 4463                 | ps   |

|              | 4 mA              | t <sub>OP</sub>  | 1400                           | 1468            | 3010                 | 3226                  | 3434                                  | 3440                 | ps   |

|              |                   | t <sub>DIP</sub> | 1524                           | 1600            | 3218                 | 3463                  | 3707                                  | 3707                 | ps   |

|              | 6 mA              | t <sub>OP</sub>  | 1388                           | 1455            | 2857                 | 3050                  | 3236                                  | 3242                 | ps   |

|              |                   | t <sub>DIP</sub> | 1512                           | 1587            | 3065                 | 3287                  | 3509                                  | 3509                 | ps   |

|              | 8 mA              | t <sub>OP</sub>  | 1347                           | 1412            | 2714                 | 2897                  | 3072                                  | 3078                 | ps   |

|              |                   | t <sub>DIP</sub> | 1471                           | 1544            | 2922                 | 3134                  | 3345                                  | 3345                 | ps   |

|              | 10 mA             | t <sub>OP</sub>  | 1347                           | 1412            | 2714                 | 2897                  | 3072                                  | 3078                 | ps   |

|              |                   | t <sub>DIP</sub> | 1471                           | 1544            | 2922                 | 3134                  | 3345                                  | 3345                 | ps   |

|              | 12 mA             | t <sub>OP</sub>  | 1332                           | 1396            | 2678                 | 2856                  | 3028                                  | 3034                 | ps   |

|              | (1)               | t <sub>DIP</sub> | 1456                           | 1528            | 2886                 | 3093                  | 3301                                  | 3301<br>4855         | ps   |

| 1.5V         | 2 mA              | t <sub>OP</sub>  | 1853                           | 1943            | 4127                 | 4492                  | 4849                                  | 4855                 | ps   |

|              |                   | t <sub>DIP</sub> | 1977                           | 2075            | 4335                 | 4729                  | 5122                                  | 5122                 | ps   |

|              | 4 mA              | t <sub>OP</sub>  | 1694                           | 1776            | 3452                 | 3747                  | 4036                                  | 4042                 | ps   |

|              |                   | t <sub>DIP</sub> | 1818                           | 1908            | 3660                 | 3984                  | 4309                                  | 4309                 | ps   |

|              | 6 mA (1)          | t <sub>OP</sub>  | 1694                           | 1776            | 3452                 | 3747                  | 47   4036   4042     84   4309   4309 | ps                   |      |

|              |                   | t <sub>DIP</sub> | 1818                           | 1908            | 3660                 | 3984                  | 4309                                  | 4309                 | ps   |

| SSTL_2_      | 8 mA              | t <sub>OP</sub>  | 1090                           | 1142            | 2152                 | 2268                  | 2376                                  | 2382                 | ps   |

| CLASS_I      |                   | t <sub>DIP</sub> | 1214                           | 1274            | 2360                 | 2505                  | 2649                                  | 2649                 | ps   |

|              | 12 mA             | t <sub>OP</sub>  | 1097                           | 1150            | 2131                 | 2246                  | 2354                                  | 2360                 | ps   |

|              | (1)               | t <sub>DIP</sub> | 1221                           | 1282            | 2339                 | 2483                  | 2627                                  | 2627                 | ps   |

| SSTL_2_      | 16 mA             | t <sub>OP</sub>  | 1068                           | 1119            | 2067                 | 2177                  | 2281                                  | 2287                 | ps   |

| CLASS_II     | (1)               | t <sub>DIP</sub> | 1192                           | 1251            | 2275                 | 2414                  | 2554                                  | 2554                 | ps   |

| SSTL_18_     | 6 mA              | t <sub>OP</sub>  | 1371                           | 1437            | 2828                 | 3018                  | 3200                                  | 3206                 | ps   |

| CLASS_I      |                   | t <sub>DIP</sub> | 1495                           | 1569            | 3036                 | 3255                  | 3473                                  | 3473                 | ps   |

|              | 8 mA              | t <sub>OP</sub>  | 1365                           | 1431            | 2832                 | 3024                  | 3209                                  | 3215                 | ps   |

|              |                   | t <sub>DIP</sub> | 1489                           | 1563            | 3040                 | 3261                  | 3482                                  | 3482                 | ps   |

|              | 10 mA             | t <sub>OP</sub>  | 1374                           | 1440            | 2806                 | 2990                  | 3167                                  | 3173                 | ps   |

|              | (1)               | t <sub>DIP</sub> | 1498                           | 1572            | 3014                 | 3227                  | 3440                                  | 3440                 | ps   |

| Table 7–6. I/O Standards Supported for Cyclone II PLLs (Part 2 of 2) |              |              |              |  |  |  |  |

|----------------------------------------------------------------------|--------------|--------------|--------------|--|--|--|--|

| I/O Standard                                                         | Input        | Ou           | tput         |  |  |  |  |

| i/U Stalluaru                                                        | inclk        | lock         | pll_out      |  |  |  |  |

| SSTL-25 class II                                                     | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |  |  |  |

| RSDS/mini-LVDS (4)                                                   |              | $\checkmark$ | ✓            |  |  |  |  |

#### Notes to Table 7–6:

- (1) The PCI-X I/O standard is supported only on side I/O pins.

- (2) Differential SSTL and HSTL outputs are only supported on the PLL<#>\_OUT pins.

- (3) These I/O standards are only supported on top and bottom I/O pins.

- (4) The RSDS and mini-LVDS pins are only supported on output pins.

# Clock Feedback Modes

Cyclone II PLLs support four clock feedback modes: normal mode, zero delay buffer mode, no compensation mode, and source synchronous mode. Cyclone II PLLs do not have support for external feedback mode. All the supported clock feedback modes allow for multiplication and division, phase shifting, and programmable duty cycle. The phase relationships shown in the waveforms in Figures 7–4 through 7–6 are for the default (zero degree) phase shift setting. Changing the phase-shift setting changes the relationships between the output clocks from the PLL.

# Normal Mode

In normal mode, the PLL phase-aligns the input reference clock with the clock signal at the ports of the registers in the logic array I/O registers to compensate for the internal global clock network delay. Use the altpll megafunction in the Quartus II software to define which internal clock output from the PLL (c0, c1, or c2) to compensate for.

If an external clock output pin (PLL<#>\_OUT) is used in this mode, there is a phase shift with respect to the clock input pin. Similarly, if the internal PLL clock outputs are used to drive general-purpose I/O pins, there is be phase shift with respect to the clock input pin.

Figure 7–4 shows an example waveform of the PLL clocks' phase relationship in this mode.

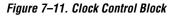

#### Notes to Figure 7–11:

- (1) The CLKSWITCH signal can either be set through the configuration file or dynamically set when using the manual PLL switchover feature. The output of the multiplexer is the input reference clock ( $f_{IN}$ ) for the PLL.

- (2) The CLKSELECT[1..0] signals are fed by internal logic and can be used to dynamically select the clock source for the global clock network when the device is in user mode.

- (3) The static clock select signals are set in the configuration file and cannot be dynamically controlled when the device is in user mode.

- (4) Internal logic can be used to enable or disable the global clock network in user mode.

Each PLL generates three clock outputs through the c[1..0] and c2 counters. Two of these clocks can drive the global clock network through the clock control block.

## **Global Clock Network Clock Source Generation**

There are a total of 8 clock control blocks on the smaller Cyclone II devices (EP2C5 and EP2C8 devices) and a total of 16 clock control blocks on the larger Cyclone II devices (EP2C15 devices and larger). Figure 7–12 shows the Cyclone II clock inputs and the clock control blocks placement.

QDRII SRAM devices use the following clock signals:

- Input clocks K and K#

- Optional output clocks C and C#

- Echo clocks CQ and CQn

Clocks C#, K#, and CQn are logical complements of clocks C, K, and CQ, respectively. Clocks C, C#, K, and K# are inputs to the QDRII SRAM, and clocks CQ and CQn are outputs from the QDRII SRAM. Cyclone II devices use single-clock mode for QDRII SRAM interfacing. The K and K# clocks are used for both read and write operations, and the C and C# clocks are unused.

You can generate C, C#, K, and K# clocks using any of the I/O registers via the DDR registers. Due to strict skew requirements between K and K# signals, use adjacent pins to generate the clock pair. Surround the pair with buffer pins tied to  $V_{CC}$  and pins tied to ground for better noise immunity from other signals.

In Cyclone II devices, another DQS pin implements the CQn pin in the QDRII SRAM memory interface. These pins are denoted by DQS/CQ# in the pin table. Connect CQ and CQn pins to the Cyclone II DQS/CQ and DQS/CQ# pins of the same DQ groups, respectively. You must configure the DQS/CQ and DQS/CQ# as bidirectional pins. However, because CQ and CQn pins are output-only pins from the memory device, the Cyclone II device's QDRII SRAM memory interface requires that you ground the DQS/CQ and DQS/CQ# output enable. To capture data presented by the memory device, connect the shifted CQ signal to register  $C_{\rm I}$  and input register  $A_{\rm I}$ . Connect the shifted CQn to input register  $B_{\rm I}$ . Figure 9–4 shows the CQ and CQn connections for a QDRII SRAM read.

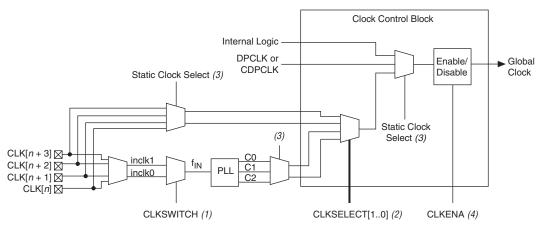

# Pseudo-Differential SSTL-18 Class I and Differential SSTL-18 Class II

The 1.8-V differential SSTL-18 standard is formulated under JEDEC Standard, JESD8-15: Stub Series Terminated Logic for 1.8V (SSTL-18).

The differential SSTL-18 I/O standard is a 1.8-V standard used for applications such as high-speed DDR2 SDRAM interfaces. This standard supports differential signals in systems using the SSTL-18 standard and supplements the SSTL-18 standard for differential clocks. Refer to Figures 10–9 and 10–10 for details on differential SSTL-18 termination.

Cyclone II devices do not support true differential SSTL-18 standards. Cyclone II devices support pseudo-differential SSTL-18 outputs for PLL\_OUT pins and pseudo-differential SSTL-18 inputs for clock pins. Pseudo-differential inputs require an input reference voltage as opposed to the true differential inputs. Refer to Table 10–1 on page 10–2 for information about pseudo-differential SSTL.

Figure 10–9. Differential SSTL-18 Class I Termination

pin+11  $\Sigma~I_{\rm PIN}$  < 240mA per power pair pin

In all cases listed above, the Quartus II software generates an error message for illegally placed pads.

Table 10–12 shows the I/O standard DC current specification.

| L/O Stondord                         | I <sub>PIN</sub> (m  | I <sub>PIN</sub> (mA) |  |  |  |  |

|--------------------------------------|----------------------|-----------------------|--|--|--|--|

| I/O Standard                         | Top and Bottom Banks | Side Banks            |  |  |  |  |

| LVTTL                                | (1)                  | (1)                   |  |  |  |  |

| LVCMOS                               | (1)                  | (1)                   |  |  |  |  |

| 2.5 V                                | (1)                  | (1)                   |  |  |  |  |

| 1.8 V                                | (1)                  | (1)                   |  |  |  |  |

| 1.5 V                                | (1)                  | (1)                   |  |  |  |  |

| 3.3-V PCI                            | Not supported        | 1.5                   |  |  |  |  |

| 3.3-V PCI-X                          | Not supported        | 1.5                   |  |  |  |  |

| SSTL-2 class I                       | 12 (2)               | 12 <i>(2)</i>         |  |  |  |  |

| SSTL-2 class II                      | 24 (2)               | 20 (2)                |  |  |  |  |

| SSTL-18 class I                      | 12 (2)               | 12 <i>(2)</i>         |  |  |  |  |

| SSTL-18 class II                     | 8 (2)                | Not supported         |  |  |  |  |

| 1.8-V HSTL class I                   | 12 (2)               | 12 <i>(2)</i>         |  |  |  |  |

| 1.8-V HSTL class II                  | 20 (2)               | Not supported         |  |  |  |  |

| 1.5-V HSTL class I                   | 12 (2)               | 10 <i>(2)</i>         |  |  |  |  |

| 1.5-V HSTL class II                  | 18 (2)               | Not supported         |  |  |  |  |

| Differential SSTL-2 class I (3)      | 8.1 (4               | 4)                    |  |  |  |  |

| Differential SSTL-2 class II (3)     | 16.4 (               | (4)                   |  |  |  |  |

| Differential SSTL-18 class I (3)     | 6.7 (4               | 4)                    |  |  |  |  |

| Differential SSTL-18 class II (3)    | 13.4 (               | (4)                   |  |  |  |  |

| 1.8-V differential HSTL class I (3)  | 8 (4)                | )                     |  |  |  |  |

| 1.8-V differential HSTL class II (3) | 16 (4                | !)                    |  |  |  |  |

| 1.5-V differential HSTL class I (3)  | 8 (4)                | )                     |  |  |  |  |

| Table 11–1. LVDS I/O Specifications (Part 2 of 2) Note (1) |                                              |                        |     |     |      |       |  |  |  |

|------------------------------------------------------------|----------------------------------------------|------------------------|-----|-----|------|-------|--|--|--|

| Symbol                                                     | Parameter                                    | Condition              | Min | Тур | Max  | Units |  |  |  |

| V <sub>ID</sub>                                            | Input differential voltage (single-ended)    |                        | 0.1 |     | 0.65 | V     |  |  |  |

| VICM                                                       | Input common mode voltage                    |                        | 0.1 |     | 2.0  | V     |  |  |  |

| $\Delta V_{OS}$                                            | Change in V <sub>OS</sub> between<br>H and L | R <sub>L</sub> = 100 Ω |     |     | 50   | mV    |  |  |  |

| RL                                                         | Receiver differential input resistor         |                        | 90  | 100 | 110  | Ω     |  |  |  |

Note to Table 11–1:

(1) The specifications apply at the resistor network output.

LVDS Receiver & Transmitter

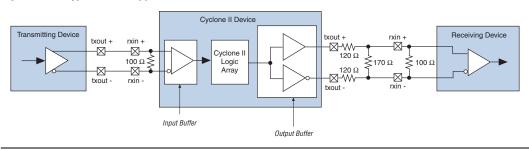

Figure 11–3 shows a simple point-to-point LVDS application where the source of the data is an LVDS transmitter. These LVDS signals are typically transmitted over a pair of printed circuit board (PCB) traces, but a combination of a PCB trace, connectors, and cables is a common application setup.

## Figure 11–3. Typical LVDS Application

Figures 11–4 and 11–5 show the signaling levels for LVDS receiver inputs and transmitter outputs, respectively.

- Maintain equal distance between traces in LVDS pairs, as much as possible. Routing the pair of traces close to each other maximizes the common-mode rejection ratio (CMRR).

- Longer traces have more inductance and capacitance. These traces should be as short as possible to limit signal integrity issues.

- Place termination resistors as close to receiver input pins as possible.

- Use surface mount components.

- Avoid 90° or 45° corners.

- Use high-performance connectors.

- Design backplane and card traces so that trace impedance matches the connector's and/or the termination's impedance.

- Keep equal number of vias for both signal traces.

- Create equal trace lengths to avoid skew between signals. Unequal trace lengths result in misplaced crossing points and decrease system margins as the channel-to-channel skew (TCCS) value increases.

- Limit vias because they cause discontinuities.

- Use the common bypass capacitor values such as 0.001, 0.01, and 0.1 μF to decouple the high-speed PLL power and ground planes.

- Keep switching transistor-to-transistor logic (TTL) signals away from differential signals to avoid possible noise coupling.

- Do not route TTL clock signals to areas under or above the differential signals.

- Analyze system-level signals.

For PCB layout guidelines, see AN 224: High-Speed Board Layout Guidelines.

# Conclusion

Cyclone II differential I/O capabilities enable you to keep pace with increasing design complexity. Support for I/O standards including LVDS, LVPECL, RSDS, mini-LVDS, differential SSTL and differential HSTL allows Cyclone II devices to fit into a wide variety of applications. Taking advantage of these I/O capabilities and Cyclone II pricing allows you to lower your design costs while remaining on the cutting edge of technology.

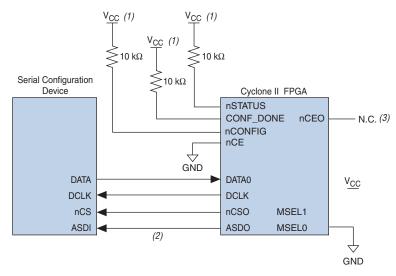

### Figure 13–3. Single Device AS Configuration

#### Notes to Figure 13–3:

- (1) Connect the pull-up resistors to a 3.3-V supply.

- (2) Cyclone II devices use the ASDO to ASDI path to control the configuration device.

- (3) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed another device's nCE pin.

Upon power-up, the Cyclone II device goes through a POR. During POR, the device resets, holds <code>nSTATUS</code> and <code>CONF\_DONE</code> low, and tri-states all user I/O pins. After POR, which typically lasts 100 ms, the Cyclone II device releases <code>nSTATUS</code> and enters configuration mode when the external 10-k $\Omega$  resistor pulls the <code>nSTATUS</code> pin high. Once the FPGA successfully exits POR, all user I/O pins continue to be tri-stated. Cyclone II devices have weak pull-up resistors on the user I/O pins which are on before and during configuration.

The value of the weak pull-up resistors on the I/O pins that are on before and during configuration are available in the *DC Characteristics & Timing Specifications* chapter of the *Cyclone II Device Handbook*.

The configuration cycle consists of the reset, configuration, and initialization stages.

٦

When designing a Cyclone II board for JTAG configuration, use the guidelines in Table 13–10 for the placement of the dedicated configuration pins.

Г

| Signal    | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nCE       | On all Cyclone II devices in the chain, nCE should be driven<br>low by connecting it to ground, pulling it low via a resistor, or<br>driving it by some control circuitry. For devices that are also in<br>multiple device AS, or PS configuration chains, the nCE pins<br>should be connected to GND during JTAG configuration or<br>JTAG configured in the same order as the configuration chain.                                       |

| nCEO      | On all Cyclone II devices in the chain, nCEO can be used as a user I/O or connected to the nCE of the next device. If nCEO is connected to the nCE of the next device, the nCEO pin must be pulled high to $V_{CCIO}$ by an external 10-k $\Omega$ pull-up resistor to help the internal weak pull-up resistor. If the nCEO pin is not connected to the nCE pin of the next device, you can use it as a user I/O pin after configuration. |

| MSEL      | These pins must not be left floating. These pins support<br>whichever non-JTAG configuration is used in production. If<br>only JTAG configuration is used, you should tie these pins to<br>ground.                                                                                                                                                                                                                                        |

| nCONFIG   | Driven high by connecting to V <sub>CC</sub> , pulling up via a resistor, or driven high by some control circuitry.                                                                                                                                                                                                                                                                                                                       |

| nSTATUS   | Pull to $V_{CC}$ via a 10-k $\Omega$ resistor. When configuring multiple devices in the same JTAG chain, each <code>nSTATUS</code> pin should be pulled up to $V_{CC}$ individually. <code>nSTATUS</code> pulling low in the middle of JTAG configuration indicates that an error has occurred.                                                                                                                                           |

| CONF_DONE | Pull to $V_{CC}$ via a 10-k $\Omega$ resistor. When configuring multiple devices in the same JTAG chain, each CONF_DONE pin should be pulled up to $V_{CC}$ individually. CONF_DONE going high at the end of JTAG configuration indicates successful configuration.                                                                                                                                                                       |

| DCLK      | Should not be left floating. Drive low or high, whichever is more convenient on your board.                                                                                                                                                                                                                                                                                                                                               |

Figure 13–23 shows JTAG configuration of a Cyclone II device with a microprocessor.