Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 4276                                                    |

| Number of Logic Elements/Cells | 68416                                                   |

| Total RAM Bits                 | 1152000                                                 |

| Number of I/O                  | 422                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 672-BGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c70f672c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, M4K memory blocks, embedded multipliers, and IOEs. C16 column interconnects drive to other row and column interconnects at every fourth LAB. C16 column interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly. C16 interconnects can drive R24, R4, C16, and C4 interconnects.

### **Device Routing**

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (for example, M4K memory, embedded multiplier, or PLL) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB.

Table 2–1 shows the Cyclone II device's routing scheme.

| Table 2–1. Cy               | Table 2–1. Cyclone II Device Routing Scheme (Part 1 of 2) |                    |                          |                 |                  |                 |                  |          |               |                     |     |            |          |

|-----------------------------|-----------------------------------------------------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|----------|---------------|---------------------|-----|------------|----------|

| Destination                 |                                                           |                    |                          |                 |                  |                 |                  |          |               |                     |     |            |          |

| Source                      | Register Chain                                            | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | 31       | M4K RAM Block | Embedded Multiplier | PLL | Column 10E | Row IOE  |

| Register<br>Chain           |                                                           |                    |                          |                 |                  |                 |                  | <b>~</b> |               |                     |     |            |          |

| Local<br>Interconnect       |                                                           |                    |                          |                 |                  |                 |                  | ~        | ~             | ~                   | ~   | ~          | <b>✓</b> |

| Direct Link<br>Interconnect |                                                           | <b>✓</b>           |                          |                 |                  |                 |                  |          |               |                     |     |            |          |

| R4<br>Interconnect          |                                                           | <b>✓</b>           |                          | <b>✓</b>        | <b>✓</b>         | ~               | <b>✓</b>         |          |               |                     |     |            |          |

| R24<br>Interconnect         |                                                           |                    |                          | <b>✓</b>        | <b>✓</b>         | ~               | <b>✓</b>         |          |               |                     |     |            |          |

| C4<br>Interconnect          |                                                           | <b>✓</b>           |                          | <b>✓</b>        | <b>✓</b>         | <b>~</b>        | <b>✓</b>         |          |               |                     |     |            |          |

| C16<br>Interconnect         |                                                           |                    |                          | <b>✓</b>        | ✓                | <b>✓</b>        | <b>✓</b>         |          |               |                     |     |            |          |

Each M4K block can implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and first-in first-out (FIFO) buffers. The M4K blocks support the following features:

- 4,608 RAM bits

- 250-MHz performance

- True dual-port memory

- Simple dual-port memory

- Single-port memory

- Byte enable

- Parity bits

- Shift register

- FIFO buffer

- ROM

- Various clock modes

- Address clock enable

Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

Table 2–5 shows the capacity and distribution of the M4K memory blocks in each Cyclone II device.

| Table 2–5. M4K Memory Capacity & Distribution in Cyclone II Devices |             |            |                |  |  |  |  |  |

|---------------------------------------------------------------------|-------------|------------|----------------|--|--|--|--|--|

| Device                                                              | M4K Columns | M4K Blocks | Total RAM Bits |  |  |  |  |  |

| EP2C5                                                               | 2           | 26         | 119,808        |  |  |  |  |  |

| EP2C8                                                               | 2           | 36         | 165,888        |  |  |  |  |  |

| EP2C15                                                              | 2           | 52         | 239,616        |  |  |  |  |  |

| EP2C20                                                              | 2           | 52         | 239,616        |  |  |  |  |  |

| EP2C35                                                              | 3           | 105        | 483,840        |  |  |  |  |  |

| EP2C50                                                              | 3           | 129        | 594,432        |  |  |  |  |  |

| EP2C70                                                              | 5           | 250        | 1,152,000      |  |  |  |  |  |

| Table 2–16. Programmable Drive Strength (Part 2 of 2) Note (1) |                                                                |               |  |  |  |  |

|----------------------------------------------------------------|----------------------------------------------------------------|---------------|--|--|--|--|

| I/O Standard                                                   | I <sub>OH</sub> /I <sub>OL</sub> Current Strength Setting (mA) |               |  |  |  |  |

| i/O Stalluaru                                                  | Top & Bottom I/O Pins                                          | Side I/O Pins |  |  |  |  |

| LVCMOS (1.5 V)                                                 | 2                                                              | 2             |  |  |  |  |

|                                                                | 4                                                              | 4             |  |  |  |  |

|                                                                | 6                                                              | 6             |  |  |  |  |

|                                                                | 8                                                              |               |  |  |  |  |

| SSTL-2 class I                                                 | 8                                                              | 8             |  |  |  |  |

|                                                                | 12                                                             | 12            |  |  |  |  |

| SSTL-2 class II                                                | 16                                                             | 16            |  |  |  |  |

|                                                                | 20                                                             |               |  |  |  |  |

|                                                                | 24                                                             |               |  |  |  |  |

| SSTL-18 class I                                                | 6                                                              | 6             |  |  |  |  |

|                                                                | 8                                                              | 8             |  |  |  |  |

|                                                                | 10                                                             | 10            |  |  |  |  |

|                                                                | 12                                                             |               |  |  |  |  |

| SSTL-18 class II                                               | 16                                                             |               |  |  |  |  |

|                                                                | 18                                                             |               |  |  |  |  |

| HSTL-18 class I                                                | 8                                                              | 8             |  |  |  |  |

|                                                                | 10                                                             | 10            |  |  |  |  |

|                                                                | 12                                                             | 12            |  |  |  |  |

| HSTL-18 class II                                               | 16                                                             |               |  |  |  |  |

|                                                                | 18                                                             |               |  |  |  |  |

|                                                                | 20                                                             |               |  |  |  |  |

| HSTL-15 class I                                                | 8                                                              | 8             |  |  |  |  |

|                                                                | 10                                                             |               |  |  |  |  |

|                                                                | 12                                                             |               |  |  |  |  |

| HSTL-15 class II                                               | 16                                                             |               |  |  |  |  |

Note to Table 2–16:

The default current in the Quartus II software is the maximum setting for each I/O standard.

# **Open-Drain Output**

Cyclone II devices provide an optional open-drain (equivalent to an open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (that is, interrupt and write-enable signals) that can be asserted by any of several devices.

# Document Revision History

Table 2–21 shows the revision history for this document.

| Table 2–21. Do                | Table 2–21. Document Revision History                                                                                                                                                                                                                                 |                                                                                                                                                        |  |  |  |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Date &<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                          | Summary of Changes                                                                                                                                     |  |  |  |  |  |  |

| February 2007<br>v3.1         | <ul> <li>Added document revision history.</li> <li>Removed Table 2-1.</li> <li>Updated Figure 2-25.</li> <li>Added new <i>Note</i> (1) to Table 2-17.</li> <li>Added handpara note in "I/O Banks" section.</li> <li>Updated <i>Note</i> (2) to Table 2-20.</li> </ul> | <ul> <li>Removed Drive Strength Control from Figure 2–25.</li> <li>Elaboration of DDR2 and QDRII interfaces supported by I/O bank included.</li> </ul> |  |  |  |  |  |  |

| November 2005<br>v2.1         | <ul> <li>Updated Table 2–7.</li> <li>Updated Figures 2–11 and 2–12.</li> <li>Updated Programmable Drive Strength table.</li> <li>Updated Table 2–16.</li> <li>Updated Table 2–18.</li> <li>Updated Table 2–19.</li> </ul>                                             |                                                                                                                                                        |  |  |  |  |  |  |

| July 2005 v2.0                | <ul> <li>Updated technical content throughout.</li> <li>Updated Table 2–16.</li> </ul>                                                                                                                                                                                |                                                                                                                                                        |  |  |  |  |  |  |

| February 2005<br>v1.2         | Updated figure 2-12.                                                                                                                                                                                                                                                  |                                                                                                                                                        |  |  |  |  |  |  |

| November 2004<br>v1.1         | Updated Table 2–19.                                                                                                                                                                                                                                                   |                                                                                                                                                        |  |  |  |  |  |  |

| June 2004 v1.0                | Added document to the Cyclone II Device Handbook.                                                                                                                                                                                                                     |                                                                                                                                                        |  |  |  |  |  |  |

**Table 5–6. Recommended Operating Conditions for User I/O Pins Using Single-Ended I/O Standards**Note (1) (Part 2 of 2)

| I/O Standard           | V <sub>CCIO</sub> (V) |     |       | V <sub>REF</sub> (V) |      |       | V <sub>IL</sub> (V)                                           | V <sub>IH</sub> (V)                                           |

|------------------------|-----------------------|-----|-------|----------------------|------|-------|---------------------------------------------------------------|---------------------------------------------------------------|

| i/O Stallualu          | Min                   | Тур | Max   | Min                  | Тур  | Max   | Max                                                           | Min                                                           |

| SSTL-18 class II       | 1.7                   | 1.8 | 1.9   | 0.833                | 0.9  | 0.969 | V <sub>REF</sub> - 0.125 (DC)<br>V <sub>REF</sub> - 0.25 (AC) | V <sub>REF</sub> + 0.125 (DC)<br>V <sub>REF</sub> + 0.25 (AC) |

| 1.8-V HSTL<br>class I  | 1.71                  | 1.8 | 1.89  | 0.85                 | 0.9  | 0.95  | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

| 1.8-V HSTL<br>class II | 1.71                  | 1.8 | 1.89  | 0.85                 | 0.9  | 0.95  | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

| 1.5-V HSTL<br>class I  | 1.425                 | 1.5 | 1.575 | 0.71                 | 0.75 | 0.79  | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

| 1.5-V HSTL<br>class II | 1.425                 | 1.5 | 1.575 | 0.71                 | 0.75 | 0.79  | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

*Note to Table 5–6:*

<sup>(1)</sup> Nominal values (Nom) are for  $T_A$  = 25° C,  $V_{CCINT}$  = 1.2 V, and  $V_{CCIO}$  = 1.5, 1.8, 2.5, and 3.3 V.

| Table 5–7. DC Characteristics of User I/O Pins Using Single-Ended Standards         Notes (1), (2)         (Part 1 of 2) |                      |                      |                             |                             |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|-----------------------------|-----------------------------|--|--|--|

| 1/0 0444                                                                                                                 | Test Co              | nditions             | Voltage Thresholds          |                             |  |  |  |

| I/O Standard                                                                                                             | I <sub>OL</sub> (mA) | I <sub>OH</sub> (mA) | Maximum V <sub>OL</sub> (V) | Minimum V <sub>OH</sub> (V) |  |  |  |

| 3.3-V LVTTL                                                                                                              | 4                    | -4                   | 0.45                        | 2.4                         |  |  |  |

| 3.3-V LVCMOS                                                                                                             | 0.1                  | -0.1                 | 0.2                         | V <sub>CCIO</sub> - 0.2     |  |  |  |

| 2.5-V LVTTL and LVCMOS                                                                                                   | 1                    | -1                   | 0.4                         | 2.0                         |  |  |  |

| 1.8-V LVTTL and LVCMOS                                                                                                   | 2                    | -2                   | 0.45                        | V <sub>CCIO</sub> - 0.45    |  |  |  |

| 1.5-V LVTTL and LVCMOS                                                                                                   | 2                    | -2                   | 0.25 × V <sub>CCIO</sub>    | 0.75 × V <sub>CCIO</sub>    |  |  |  |

| PCI and PCI-X                                                                                                            | 1.5                  | -0.5                 | 0.1 × V <sub>CCIO</sub>     | 0.9 × V <sub>CCIO</sub>     |  |  |  |

| SSTL-2 class I                                                                                                           | 8.1                  | -8.1                 | V <sub>TT</sub> – 0.57      | V <sub>TT</sub> + 0.57      |  |  |  |

| SSTL-2 class II                                                                                                          | 16.4                 | -16.4                | V <sub>TT</sub> – 0.76      | V <sub>TT</sub> + 0.76      |  |  |  |

| SSTL-18 class I                                                                                                          | 6.7                  | -6.7                 | V <sub>TT</sub> – 0.475     | V <sub>TT</sub> + 0.475     |  |  |  |

| SSTL-18 class II                                                                                                         | 13.4                 | -13.4                | 0.28                        | V <sub>CCIO</sub> - 0.28    |  |  |  |

| 1.8-V HSTL class I                                                                                                       | 8                    | -8                   | 0.4                         | V <sub>CCIO</sub> - 0.4     |  |  |  |

| 1.8-V HSTL class II                                                                                                      | 16                   | -16                  | 0.4                         | V <sub>CCIO</sub> - 0.4     |  |  |  |

| Table 5–30. EP2C35 Row Pins Global Clock Timing Parameters |            |            |          |          |          |       |  |  |  |

|------------------------------------------------------------|------------|------------|----------|----------|----------|-------|--|--|--|

| Parameter                                                  | Fast (     | Corner     | -6 Speed | -7 Speed | -8 Speed | Unit  |  |  |  |

|                                                            | Industrial | Commercial | Grade    | Grade    | Grade    | UIIIL |  |  |  |

| t <sub>CIN</sub>                                           | 1.410      | 1.476      | 2.514    | 2.724    | 2.986    | ns    |  |  |  |

| t <sub>COUT</sub>                                          | 1.412      | 1.478      | 2.530    | 2.737    | 2.994    | ns    |  |  |  |

| t <sub>PLLCIN</sub>                                        | -0.117     | -0.127     | 0.134    | 0.162    | 0.241    | ns    |  |  |  |

| t <sub>PLLCOUT</sub>                                       | -0.115     | -0.125     | 0.15     | 0.175    | 0.249    | ns    |  |  |  |

# EP2C50 Clock Timing Parameters

Tables 5–31 and 5–32 show the clock timing parameters for EP2C50 devices.

| Table 5–31. EP2C50 Column Pins Global Clock Timing Parameters |            |            |          |          |          |       |  |  |  |

|---------------------------------------------------------------|------------|------------|----------|----------|----------|-------|--|--|--|

| Parameter                                                     | Fast (     | Corner     | -6 Speed | -7 Speed | -8 Speed | Unit  |  |  |  |

|                                                               | Industrial | Commercial | Grade    | Grade    | Grade    | UIIIL |  |  |  |

| t <sub>CIN</sub>                                              | 1.575      | 1.651      | 2.759    | 2.940    | 3.174    | ns    |  |  |  |

| t <sub>COUT</sub>                                             | 1.589      | 1.666      | 2.793    | 2.972    | 3.203    | ns    |  |  |  |

| t <sub>PLLCIN</sub>                                           | -0.149     | -0.158     | 0.113    | 0.075    | 0.089    | ns    |  |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.135     | -0.143     | 0.147    | 0.107    | 0.118    | ns    |  |  |  |

| Table 5–32. EP2C50 Row Pins Global Clock Timing Parameters |            |            |          |          |          |       |  |

|------------------------------------------------------------|------------|------------|----------|----------|----------|-------|--|

| Parameter                                                  | Fast (     | Corner     | -6 Speed | -7 Speed | -8 Speed | Unit  |  |

|                                                            | Industrial | Commercial | Grade    | Grade    | Grade    | UIIIL |  |

| t <sub>CIN</sub>                                           | 1.463      | 1.533      | 2.624    | 2.791    | 3.010    | ns    |  |

| t <sub>COUT</sub>                                          | 1.465      | 1.535      | 2.640    | 2.804    | 3.018    | ns    |  |

| t <sub>PLLCIN</sub>                                        | -0.261     | -0.276     | -0.022   | -0.074   | -0.075   | ns    |  |

| t <sub>PLLCOUT</sub>                                       | -0.259     | -0.274     | -0.006   | -0.061   | -0.067   | ns    |  |

The loop filter converts these up and down signals to a voltage that is used to bias the VCO. If the charge pump receives a logic high on the up signal, current is driven into the loop filter. If the charge pump receives a logic high on the down signal, current is drawn from the loop filter. The loop filter sout glitches from the charge pump and prevents voltage over-shoot, which minimizes the jitter on the VCO.

The voltage from the charge pump determines how fast the VCO operates. The VCO is implemented as an four-stage differential ring oscillator. A divide counter, m, is inserted in the feedback loop to increase the VCO frequency above the input reference frequency, making the VCO frequency  $f_{VCO} = m \times f_{REF}$ . Therefore, the feedback clock,  $f_{FB}$ , applied to one input of the PFD, is locked to the input reference clock,  $f_{REF}$  ( $f_{IN}/n$ ), applied to the other input of the PFD.

The VCO output can feed up to three post-scale counters (c0, c1, and c2). These post-scale counters allow a number of harmonically related frequencies to be produced by the PLL.

Additionally, Cyclone II PLLs have internal delay elements to compensate for routing on the global clock networks and I/O buffers. These internal delays are fixed and not accessible to the user.

Figure 7–2 shows a simplified block diagram of the major components of a Cyclone II device PLL.

### **Independent Clock Mode**

Cyclone II memory blocks can implement independent clock mode for true dual-port memory. In this mode, a separate clock is available for each port (A and B). Clock A controls all registers on the port A side, while clock B controls all registers on the port B side. Each port also supports independent clock enables for port A and B registers. However, ports do not support asynchronous clear signals for the registers.

Figure 8–13 shows a memory block in independent clock mode.

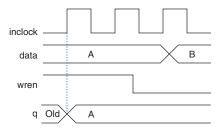

Figure 8–22. Cyclone II Same-Port Read-During-Write Functionality Note (1)

Note to Figure 8-22:

(1) Outputs are not registered.

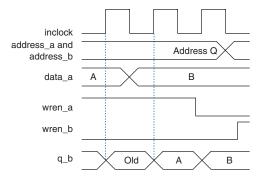

#### **Mixed-Port Read-During-Write Mode**

This mode applies to a RAM in simple or true dual-port mode, which has one port reading and the other port writing to the same address location with the same clock.

In this mode, you also have two output choices: old data or don't care. In Old Data Mode, a read-during-write operation to different ports causes the RAM outputs to reflect the old data at that address location. In Don't Care Mode, the same operation results in a "don't care" or unknown value on the RAM outputs.

Figure 8–23. Cyclone II Mixed-Port Read-During-Write: Old Data Mode Note (1)

Note to Figure 8-23:

(1) Outputs are not registered.

- Cyclone II FPGA (EP2C15 or larger)

- Altera PCI Express Compiler ×1 MegaCore® function

- External PCI Express transceiver/PHY

#### 2.5-V LVTTL (EIA/JEDEC Standard EIA/JESD8-5)

The 2.5-V I/O standard is used for 2.5-V LVTTL applications. This standard defines the DC interface parameters for high-speed, low-voltage, non-terminated digital circuits driving or being driven by other 2.5-V devices.

The 2.5-V standard does not require input reference voltages or board terminations. Cyclone II devices support input and output levels for 2.5-V LVTTL.

#### 2.5-V LVCMOS (EIA/JEDEC Standard EIA/JESD8-5)

The 2.5-V I/O standard is used for 2.5-V LVCMOS applications. This standard defines the DC interface parameters for high-speed, low-voltage, non-terminated digital circuits driving or being driven by other 2.5-V parts.

The 2.5-V standard does not require input reference voltages or board terminations. Cyclone II devices support input and output levels for 2.5-V LVCMOS.

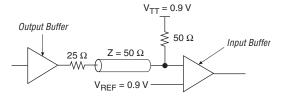

## SSTL-2 Class I and II (EIA/JEDEC Standard JESD8-9A)

The SSTL-2 I/O standard is a 2.5-V memory bus standard used for applications such as high-speed double data rate (DDR) SDRAM interfaces. This standard defines the input and output specifications for devices that operate in the SSTL-2 logic switching range of 0.0 to 2.5 V. This standard improves operations in conditions where a bus must be isolated from large stubs. The SSTL-2 standard specifies an input voltage range of – 0.3 V  $\leq$ V $_{\rm I}$   $\leq$ V $_{\rm CCIO}$  + 0.3 V. SSTL-2 requires a V $_{\rm REF}$  value of 1.25 V and a V $_{\rm TT}$  value of 1.25 V connected to the termination resistors (refer to Figures 10–1 and 10–2).

#### 1.8-V LVCMOS (EIA/JEDEC Standard EIA/JESD8-7)

The 1.8-V I/O standard is used for 1.8-V LVCMOS applications. This standard defines the DC interface parameters for high-speed, low-voltage, non-terminated digital circuits driving or being driven by other 1.8-V parts.

The 1.8-V standard does not require input reference voltages or board terminations. Cyclone II devices support input and output levels for 1.8-V LVCMOS.

#### SSTL-18 Class I and II

The 1.8-V SSTL-18 standard is formulated under JEDEC Standard, JESD815: Stub Series Terminated Logic for 1.8V (SSTL-18).

The SSTL-18 I/O standard is a 1.8-V memory bus standard used for applications such as high-speed DDR2 SDRAM interfaces. This standard is similar to SSTL-2 and defines input and output specifications for devices that are designed to operate in the SSTL-18 logic switching range 0.0 to 1.8 V. SSTL-18 requires a 0.9-V  $\rm V_{REF}$  and a 0.9-V  $\rm V_{TT}$ , with the termination resistors connected to both. There are no class definitions for the SSTL-18 standard in the JEDEC specification. The specification of this I/O standard is based on an environment that consists of both series and parallel terminating resistors. Altera provides solutions to two derived applications in JEDEC specification and names them class I and class II to be consistent with other SSTL standards. Figures 10–5 and 10–6 show SSTL-18 class I and II termination, respectively. Cyclone II devices support both input and output levels.

Figure 10-5. 1.8-V SSTL Class I Termination

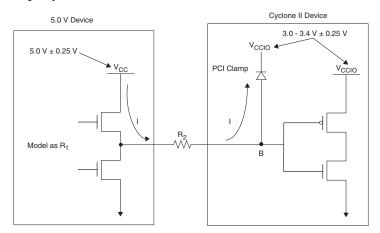

Figure 10-21. Driving a Cyclone II Device with a 5.0-Volt Device

If  $V_{CCIO}$  is between 3.0 V and 3.6 V and the PCI clamping diode is enabled, the voltage at point B in Figure 10–21 is 4.3 V or less. To limit large current draw from the 5.0-V device,  $R_2$  should be small enough for a fast signal rise time and large enough so that it does not violate the high-level output current ( $I_{OH}$ ) specifications of the devices driving the trace. The PCI clamping diode in the Cyclone II device can support 25 mA of current.

To compute the required value of  $R_2$ , first calculate the model of the pull-up transistors on the 5.0-V device. This output resistor ( $R_1$ ) can be modeled by dividing the 5.0-V device supply voltage ( $V_{CC}$ ) by the  $I_{OH}$ :  $R_1 = V_{CC}/I_{OH}$ .

Figure 10–22 shows an example of typical output drive characteristics of a 5.0-V device.

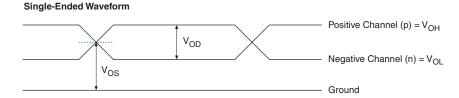

#### RSDS I/O Standard Support in Cyclone II Devices

The RSDS specification is used in chip-to-chip applications between the timing controller and the column drivers on display panels. Cyclone II devices meet the National Semiconductor Corporation RSDS Interface Specification and support the RSDS output standard. Table 11–2 shows the RSDS electrical characteristics for Cyclone II devices.

| Table 11–2. RSDS Electrical Characteristics for Cyclone II Devices Note (1) |                             |                    |       |      |       |      |  |  |

|-----------------------------------------------------------------------------|-----------------------------|--------------------|-------|------|-------|------|--|--|

| Symbol                                                                      | Parameter                   | Condition          | Min   | Тур  | Max   | Unit |  |  |

| V <sub>CCIO</sub>                                                           | Output supply voltage       |                    | 2.375 | 2.5  | 2.625 | V    |  |  |

| V <sub>OD</sub> (2)                                                         | Differential output voltage | $R_L = 100 \Omega$ | 100   |      | 600   | mV   |  |  |

| V <sub>OS</sub> (3)                                                         | Output offset voltage       | $R_L = 100 \Omega$ | 1.125 | 1.25 | 1.375 | V    |  |  |

| T <sub>r</sub> /T <sub>f</sub>                                              | Transition time             | 20% to 80%         |       | 500  |       | ps   |  |  |

Notes to Table 11-2:

- (1) The specifications apply at the resistor network output.

- (2)  $V_{OD} = V_{OH} V_{OL}$ .

- (3)  $V_{OS} = (V_{OH} + V_{OL}) / 2$ .

Figure 11-6 shows the RSDS transmitter output signal waveforms.

Figure 11–6. Transmitter Output Signal Level Waveforms for RSDS Note (1)

#### Differential Waveform (Mathematical Function of Positive & Negative Channel)

Notes to Figure 11–6:

- (1) The V<sub>OD</sub> specifications apply at the resistor network output.

- (2) The p-n waveform is a function of the positive channel (p) and the negative channel (n).

Table 11–5 defines the parameters of the timing diagram shown in Figure 11–16. Figure 11–17 shows the Cyclone II high-speed I/O timing budget.

| Table 11–5. High-Speed I/O Timing Definitions |        |                                                                                                                                                                                                                                      |  |  |  |

|-----------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter                                     | Symbol | Description                                                                                                                                                                                                                          |  |  |  |

| Transmitter channel-to-<br>channel skew (1)   | TCCS   | The timing difference between the fastest and slowest output edges, including $t_{\text{CO}}$ variation and clock skew. The clock is included in the TCCS measurement.                                                               |  |  |  |

| Sampling window                               | SW     | The period of time during which the data must be valid in order for you to capture it correctly. The setup and hold times determine the ideal strobe position within the sampling window. $T_{SW} = T_{SU} + T_{hd} + PLL \ jitter.$ |  |  |  |

| Receiver input skew margin                    | RSKM   | RSKM is defined by the total margin left after accounting for the sampling window and TCCS. The RSKM equation is: RSKM = (TUI – SW – TCCS) / 2.                                                                                      |  |  |  |

| Input jitter tolerance (peak-<br>to-peak)     |        | Allowed input jitter on the input clock to the PLL that is tolerable while maintaining PLL lock.                                                                                                                                     |  |  |  |

| Output jitter (peak-to-peak)                  |        | Peak-to-peak output jitter from the PLL.                                                                                                                                                                                             |  |  |  |

*Note to Table 11–5:*

The TCCS specification applies to the entire bank of LVDS as long as the SERDES logic are placed within the LAB

adjacent to the output pins.

External Input Clock

Internal Clock

Receiver Input Data

Time Unit Interval (TUI)

RSKM Sampling Window (SW)

RSKM VTCCS

Figure 11–16. High-Speed I/O Timing Diagram

# Section VI. Configuration & Test

This section provides configuration information for all of the supported configuration schemes for Cyclone<sup>®</sup> II devices. These configuration schemes use either a microprocessor, configuration device, or download cable. There is detailed information on how to design with Altera<sup>®</sup> configuration devices. The last chapter provides information on JTAG support in Cyclone II devices.

This section includes the following chapters:

- Chapter 13, Configuring Cyclone II Devices

- Chapter 14, IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices

# **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

Altera Corporation Section VI-1

device also pulls nSTATUS and CONF\_DONE low and tri-states all I/O pins. Once the nCONFIG pin returns to a logic high level and the Cyclone II device releases the nSTATUS pin, the MAX II device can begin reconfiguration.

#### Error During Configuration

If an error occurs during configuration, the Cyclone II device transitions its <code>nSTATUS</code> pin low, resetting itself internally. The low signal on the <code>nSTATUS</code> pin tells the MAX II device that there is an error. If you turn on the **Auto-restart configuration after error** option in the Quartus II software, the Cyclone II device releases <code>nSTATUS</code> after a reset time-out period (maximum of 40  $\mu$ s). After <code>nSTATUS</code> is released and pulled high by a pull-up resistor, the MAX II device can try to reconfigure the target device without needing to pulse <code>nCONFIG</code> low. If this option is turned off, the MAX II device must generate a low-to-high transition (with a low pulse of at least 2  $\mu$ s) on <code>nCONFIG</code> to restart the configuration process.

The MAX II device can also monitor the CONF\_DONE and INIT\_DONE pins to ensure successful configuration. The MAX II device must monitor the Cyclone II device's CONF\_DONE pin to detect errors and determine when programming completes. If all configuration data is sent, but CONF\_DONE or INIT\_DONE do not transition high, the MAX II device must reconfigure the target device.

For more information on configuration issues, see the *Debugging Configuration Problems* chapter of the *Configuration Handbook* and the FPGA Configuration Troubleshooter on the Altera web site (www.altera.com).

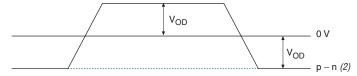

#### Multiple Device PS Configuration Using a MAX II Device as an External Host

Figure 13–10 shows how to configure multiple devices using a MAX II device. This circuit is similar to the PS configuration circuit for a single device, except Cyclone II devices are cascaded for multiple device configuration.

Figure 13–10. Multiple Device PS Configuration Using an External Host

Notes to Figure 13–10:

- (1) The pull-up resistor should be connected to a supply that provides an acceptable input signal for all devices in the chain.  $V_{CC}$  should be high enough to meet the  $V_{IH}$  specification of the I/O on the devices and the external host.

- (2) Connect the pull-up resistor to the V<sub>CCIO</sub> supply voltage of I/O bank that the nCEO pin resides in.

- (3) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed another device's nCE pin.

In multiple device PS configuration, connect the first Cyclone II device's nCE pin to GND and connect the nCEO pin to the nCE pin of the next Cyclone II device in the chain. Use an external 10-k $\Omega$  pull-up resistor to pull the Cyclone II device's nCEO pin high to its V<sub>CCIO</sub> level to help the internal weak pull-up resistor when the nCEO pin feeds next Cyclone II device's nCE pin. The input to the nCE pin of the last Cyclone II device in the chain comes from the previous Cyclone II device. After the first device completes configuration in a multiple device configuration chain, its nCEO pin transitions low to activate the second device's nCE pin, which prompts the second device to begin configuration. The second device in the chain begins configuration within one clock cycle. Therefore, the MAX II device begins to transfer data to the next Cyclone II device without interruption. The nCEO pin is a dual-purpose pin in Cyclone II devices. You can leave the nCEO pin of the last device unconnected or use it as a user I/O pin after configuration if the last device in chain is a Cyclone II device.

The Quartus II software sets the Cyclone II device nCEO pin as a dedicated output by default. If the nCEO pin feeds the next device's nCE pin, you must make sure that the nCEO pin is not used as a user I/O after configuration. This software setting is in the **Dual-Purpose Pins** tab of the **Device & Pin Options** dialog box in Quartus II software.

#### PS Configuration Timing

A PS configuration must meet the setup and hold timing parameters and the maximum clock frequency. When using a microprocessor or another intelligent host to control the PS interface, ensure that you meet these timing requirements.

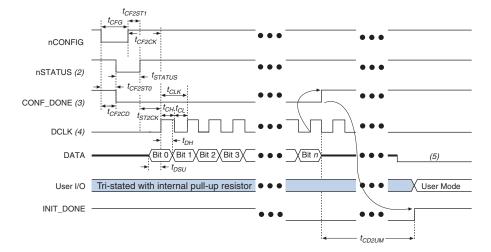

Figure 13–12 shows the timing waveform for PS configuration for Cyclone II devices.

Figure 13–12. PS Configuration Timing Waveform Note (1)

#### Notes to Figure 13–12:

- (1) The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- (2) Upon power-up, the Cyclone II device holds nSTATUS low for the time of the POR delay.

- (3) Upon power-up, before and during configuration, CONF DONE is low.

- (4) In user mode, drive DCLK either high or low when using the PS configuration scheme, whichever is more convenient. When using the AS configuration scheme, DCLK is a Cyclone II output pin and should not be driven externally.

- (5) Do not leave the DATA pin floating after configuration. Drive it high or low, whichever is more convenient.

Table 13–7 defines the timing parameters for Cyclone II devices for PS configuration.

| Table 13–7. PS Timing Parameters for Cyclone II Devices |                                                   |                                            |         |       |

|---------------------------------------------------------|---------------------------------------------------|--------------------------------------------|---------|-------|

| Symbol                                                  | Parameter                                         | Minimum                                    | Maximum | Units |

| t <sub>POR</sub>                                        | POR delay (1)                                     | 100                                        |         | ms    |

| t <sub>CF2CD</sub>                                      | nCONFIG low to CONF_DONE low                      |                                            | 800     | ns    |

| t <sub>CF2ST0</sub>                                     | nCONFIG low to nSTATUS low                        |                                            | 800     | ns    |

| t <sub>CFG</sub>                                        | nCONFIG low pulse width                           | 2                                          |         | μs    |

| t <sub>STATUS</sub>                                     | nSTATUS low pulse width                           | 10                                         | 40 (2)  | μs    |

| t <sub>CF2ST1</sub>                                     | nCONFIG high to nSTATUS high                      |                                            | 40 (2)  | μs    |

| t <sub>CF2CK</sub>                                      | nCONFIG high to first rising edge on DCLK         | 40                                         |         | μs    |

| t <sub>ST2CK</sub>                                      | nSTATUS high to first rising edge on DCLK         | 1                                          |         | μs    |

| t <sub>DSU</sub>                                        | Data setup time before rising edge on DCLK        | 7                                          |         | ns    |

| t <sub>DH</sub>                                         | Data hold time after rising edge on DCLK          | 0                                          |         | ns    |

| t <sub>CH</sub>                                         | DCLK high time                                    | 4                                          |         | ns    |

| t <sub>CL</sub>                                         | DCLK low time                                     | 4                                          |         | ns    |

| t <sub>CLK</sub>                                        | DCLK period                                       | 10                                         |         | ns    |

| f <sub>MAX</sub>                                        | DCLK frequency                                    |                                            | 100     | MHz   |

| t <sub>CD2UM</sub>                                      | CONF_DONE high to user mode (3)                   | 18                                         | 40      | μs    |

| t <sub>CD2CU</sub>                                      | CONF_DONE high to CLKUSR enabled                  | 4 × maximum DCLK period                    |         |       |

| t <sub>CD2UMC</sub>                                     | CONF_DONE high to user mode with CLKUSR option on | $t_{\text{CD2CU}}$ + (299 × CLKUSR period) |         |       |

#### Notes to Table 13-7:

- (1) The POR delay minimum of 100 ms only applies for non "A" devices.

- (2) This value is applicable if users do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

- (3) The minimum and maximum numbers apply only if the internal oscillator is chosen as the clock source for starting the device.

Device configuration options and how to create configuration files are discussed further in the *Software Settings* section in Volume 2 of the *Configuration Handbook*.

# **PS Configuration Using a Microprocessor**

In the PS configuration scheme, a microprocessor can control the transfer of configuration data from a storage device, such as flash memory, to the target Cyclone II device.

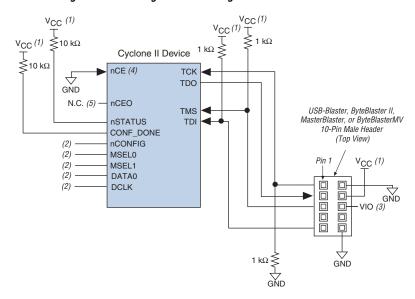

#### Single Device JTAG Configuration

During JTAG configuration, you can use the USB-Blaster, MasterBlaster, ByteBlaster II, or ByteBlasterMV download cable to download data to the device. Configuring Cyclone II devices through a cable is similar to programming devices in system. Figure 13–22 shows JTAG configuration of a single Cyclone II device using a download cable.

Figure 13-22. JTAG Configuration of a Single Device Using a Download Cable

#### Notes to Figure 13-22:

- The pull-up resistor should be connected to the same supply voltage as the USB-Blaster, MasterBlaster (VIO pin), ByteBlaster II, or ByteBlasterMV cable.

- (2) Connect the nCONFIG and MSEL[1..0] pins to support a non-JTAG configuration scheme. If only JTAG configuration is used, connect the nCONFIG pin to V<sub>CC</sub>, and the MSEL[1..0] pins to ground. In addition, pull DCLK and DATAO to either high or low, whichever is convenient on your board.

- (3) Pin 6 of the header is a V<sub>IO</sub> reference voltage for the MasterBlaster output driver. V<sub>IO</sub> should match the device's V<sub>CCIO</sub>. Refer to the MasterBlaster Serial/USB Communications Cable Data Sheet for this value. In the ByteBlasterMV, this pin is a no connect. In the USB-Blaster and ByteBlaster II, this pin is connected to nCE when it is used for AS programming, otherwise it is a no connect.

- (4) nce must be connected to GND or driven low for successful JTAG configuration.

- (5) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

To configure a single device in a JTAG chain, the programming software places all other devices in BYPASS mode. In BYPASS mode, Cyclone II devices pass programming data from the TDI pin to the TDO pin through a single bypass register without being affected internally. This scheme