Welcome to **E-XFL.COM**

### Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 4276                                                    |

| Number of Logic Elements/Cells | 68416                                                   |

| Total RAM Bits                 | 1152000                                                 |

| Number of I/O                  | 422                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 672-BGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c70f672c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Internal Timing                                                                                                                                                                                                                                                                                                                                                                                                         | 5–18                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Cyclone II Clock Timing Parameters                                                                                                                                                                                                                                                                                                                                                                                      |                                                 |

| Clock Network Skew Adders                                                                                                                                                                                                                                                                                                                                                                                               |                                                 |

| IOE Programmable Delay                                                                                                                                                                                                                                                                                                                                                                                                  | 5–30                                            |

| Default Capacitive Loading of Different I/O Standards                                                                                                                                                                                                                                                                                                                                                                   | 5–31                                            |

| I/O Delays                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

| Maximum Input and Output Clock Rate                                                                                                                                                                                                                                                                                                                                                                                     |                                                 |

| High Speed I/O Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |

| External Memory Interface Specifications                                                                                                                                                                                                                                                                                                                                                                                | 5–63                                            |

| JTAG Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

| PLL Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                               | 5–66                                            |

| Duty Cycle Distortion                                                                                                                                                                                                                                                                                                                                                                                                   |                                                 |

| DCD Measurement Techniques                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

| Referenced Documents                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                               |                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |

| Chapter 6. Reference & Ordering Information                                                                                                                                                                                                                                                                                                                                                                             |                                                 |

| Software                                                                                                                                                                                                                                                                                                                                                                                                                | 6–1                                             |

| Device Pin-Outs                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |

| Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                               |                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |

| Section II Clack Management                                                                                                                                                                                                                                                                                                                                                                                             |                                                 |

| Section II. Clock Management Revision History                                                                                                                                                                                                                                                                                                                                                                           | 6–1                                             |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 6–1                                             |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 6–1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices                                                                                                                                                                                                                                                                                                                                                                 |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction                                                                                                                                                                                                                                                                                                                                                   | 7–1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction  Cyclone II PLL Hardware Overview                                                                                                                                                                                                                                                                                                                 | 7–1<br>7–2                                      |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 7–1<br>7–2<br>7–6                               |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 7–1<br>7–2<br>7–6                               |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        |                                                 |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        | 7–1<br>7–2<br>7–10<br>7–10<br>7–10<br>7–11      |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode                                                                                                                                                                                                       | 7–17–27–67–107–117–12                           |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        |                                                 |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                        |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices  Introduction  Cyclone II PLL Hardware Overview  PLL Reference Clock Generation  Clock Feedback Modes  Normal Mode  Zero Delay Buffer Mode  No Compensation Mode  Source-Synchronous Mode  Hardware Features  Clock Multiplication & Division                                                                                                                   |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle                                                                                                     |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation                                                                       |                                                 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals                                                       | 7-1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover                               | 7-1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover Clocking                      | 7-1 7-2 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover Clocking Global Clock Network | 7-1                                             |

| Revision History  Chapter 7. PLLs in Cyclone II Devices Introduction Cyclone II PLL Hardware Overview PLL Reference Clock Generation Clock Feedback Modes Normal Mode Zero Delay Buffer Mode No Compensation Mode Source-Synchronous Mode Hardware Features Clock Multiplication & Division Programmable Duty Cycle Phase-Shifting Implementation Control Signals Manual Clock Switchover Clocking                      | 7-1 7-2 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 7-1 |

| Table 1–2. Cyclo | Table 1–2. Cyclone II Package Options & Maximum User I/O Pins         Notes (1) (2) |                     |                 |                            |                            |                                     |                            |                            |  |

|------------------|-------------------------------------------------------------------------------------|---------------------|-----------------|----------------------------|----------------------------|-------------------------------------|----------------------------|----------------------------|--|

| Device           | 144-Pin<br>TQFP (3)                                                                 | 208-Pin<br>PQFP (4) | 240-Pin<br>PQFP | 256-Pin<br>FineLine<br>BGA | 484-Pin<br>FineLine<br>BGA | 484-Pin<br>Ultra<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 896-Pin<br>FineLine<br>BGA |  |

| EP2C5 (6) (8)    | 89                                                                                  | 142                 | _               | 158 <i>(5)</i>             | _                          | _                                   | _                          | _                          |  |

| EP2C8 (6)        | 85                                                                                  | 138                 | _               | 182                        | _                          | _                                   | _                          | _                          |  |

| EP2C8A (6), (7)  | _                                                                                   | _                   | _               | 182                        | _                          | _                                   | _                          | _                          |  |

| EP2C15A (6), (7) | _                                                                                   | _                   | _               | 152                        | 315                        | _                                   | _                          | _                          |  |

| EP2C20 (6)       | _                                                                                   | _                   | 142             | 152                        | 315                        | _                                   | _                          | _                          |  |

| EP2C20A (6), (7) | _                                                                                   | _                   | _               | 152                        | 315                        | _                                   | _                          | _                          |  |

| EP2C35 (6)       | _                                                                                   | _                   | _               | _                          | 322                        | 322                                 | 475                        | _                          |  |

| EP2C50 (6)       | _                                                                                   | _                   | _               | _                          | 294                        | 294                                 | 450                        | _                          |  |

| EP2C70 (6)       | _                                                                                   | _                   | _               |                            | _                          | _                                   | 422                        | 622                        |  |

#### Notes to Table 1-2:

- Cyclone II devices support vertical migration within the same package (for example, you can migrate between the EP2C20 device in the 484-pin FineLine BGA package and the EP2C35 and EP2C50 devices in the same package).

- (2) The Quartus® II software I/O pin counts include four additional pins, TDI, TDO, TMS, and TCK, which are not available as general purpose I/O pins.

- (3) TQFP: thin quad flat pack.

- (4) PQFP: plastic quad flat pack.

- (5) Vertical migration is supported between the EP2C5F256 and the EP2C8F256 devices. However, not all of the DQ and DQS groups are supported. Vertical migration between the EP2C5 and the EP2C15 in the F256 package is not supported.

- (6) The I/O pin counts for the EP2C5, EP2C8, and EP2C15A devices include 8 dedicated clock pins that can be used for data inputs. The I/O counts for the EP2C20, EP2C35, EP2C50, and EP2C70 devices include 16 dedicated clock pins that can be used for data inputs.

- (7) EP2C8A, EP2C15A, and EP2C20A have a Fast On feature that has a faster POR time. The EP2C15A is only available with the Fast On option.

- (8) The EP2C5 optionally support the Fast On feature, which is designated with an "A" in the device ordering code. The EP2C5A is only available in the automotive speed grade. Refer to the Cyclone II section in the *Automotive-Grade Device Handbook*.

Cyclone II devices support vertical migration within the same package (for example, you can migrate between the EP2C35, EPC50, and EP2C70 devices in the 672-pin FineLine BGA package). The exception to vertical migration support within the Cyclone II family is noted in Table 1–3.

### **PLLs**

Cyclone II PLLs provide general-purpose clocking as well as support for the following features:

- Clock multiplication and division

- Phase shifting

- Programmable duty cycle

- Up to three internal clock outputs

- One dedicated external clock output

- Clock outputs for differential I/O support

- Manual clock switchover

- Gated lock signal

- Three different clock feedback modes

- Control signals

Cyclone II devices contain either two or four PLLs. Table 2–3 shows the PLLs available for each Cyclone II device.

| Table 2–3. Cyclone II Device PLL Availability |          |          |          |      |  |  |

|-----------------------------------------------|----------|----------|----------|------|--|--|

| Device                                        | PLL1     | PLL2     | PLL3     | PLL4 |  |  |

| EP2C5                                         | <b>✓</b> | <b>✓</b> |          |      |  |  |

| EP2C8                                         | ✓        | ✓        |          |      |  |  |

| EP2C15                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> | ✓    |  |  |

| EP2C20                                        | <b>✓</b> | ~        | ✓        | ~    |  |  |

| EP2C35                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> | ✓    |  |  |

| EP2C50                                        | <b>✓</b> | ~        | ✓        | ~    |  |  |

| EP2C70                                        | ✓        | ✓        | ✓        | ✓    |  |  |

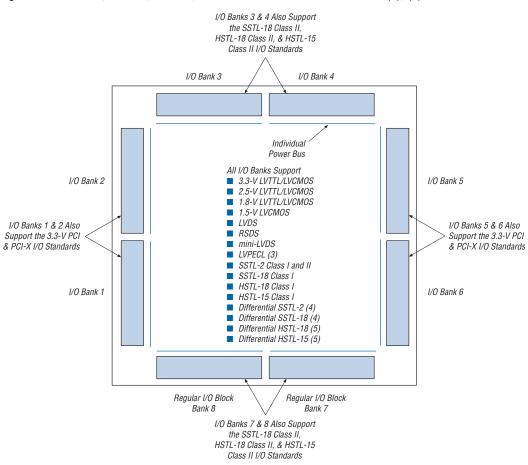

Figure 2–29. EP2C15, EP2C20, EP2C35, EP2C50 & EP2C70 I/O Banks Notes (1), (2)

### Notes to Figure 2–29:

- (1) This is a top view of the silicon die.

- (2) This is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (5) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

Each I/O bank has its own VCCIO pins. A single device can support 1.5-V, 1.8-V, 2.5-V, and 3.3-V interfaces; each individual bank can support a different standard with different I/O voltages. Each bank also has dual-purpose VREF pins to support any one of the voltage-referenced

standards (e.g., SSTL-2) independently. If an I/O bank does not use voltage-referenced standards, the  $\mbox{VREF}$  pins are available as user I/O pins.

Each I/O bank can support multiple standards with the same  $V_{\rm CCIO}$  for input and output pins. For example, when  $V_{\rm CCIO}$  is 3.3-V, a bank can support LVTTL, LVCMOS, and 3.3-V PCI for inputs and outputs. Voltage-referenced standards can be supported in an I/O bank using any number of single-ended or differential standards as long as they use the same  $V_{\rm REF}$  and a compatible  $V_{\rm CCIO}$  value.

### MultiVolt I/O Interface

The Cyclone II architecture supports the MultiVolt I/O interface feature, which allows Cyclone II devices in all packages to interface with systems of different supply voltages. Cyclone II devices have one set of  $V_{CC}$  pins (VCCINT) that power the internal device logic array and input buffers that use the LVPECL, LVDS, HSTL, or SSTL I/O standards. Cyclone II devices also have four or eight sets of VCC pins (VCCIO) that power the I/O output drivers and input buffers that use the LVTTL, LVCMOS, or PCI I/O standards.

The Cyclone II VCCINT pins must always be connected to a 1.2-V power supply. If the  $V_{\rm CCINT}$  level is 1.2 V, then input pins are 1.5-V, 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-V, 1.8-V, 2.5-V, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (i.e., when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3-V and is compatible with 3.3-V systems. Table 2–20 summarizes Cyclone II MultiVolt I/O support.

| Table 2–20. Cyclone II MultiVolt I/O Support (Part 1 of 2) Note (1) |                            |          |              |              |              |              |          |       |

|---------------------------------------------------------------------|----------------------------|----------|--------------|--------------|--------------|--------------|----------|-------|

| v (v)                                                               | Input Signal Output Signal |          |              |              |              |              |          |       |

| V <sub>CCIO</sub> (V)                                               | 1.5 V                      | 1.8 V    | 2.5 V        | 3.3 V        | 1.5 V        | 1.8 V        | 2.5 V    | 3.3 V |

| 1.5                                                                 | <b>✓</b>                   | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) | <b>✓</b>     |              |          |       |

| 1.8                                                                 | <b>√</b> (4)               | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (3) | <b>✓</b>     |          |       |

| 2.5                                                                 |                            |          | ~            | <b>✓</b>     | <b>√</b> (5) | <b>√</b> (5) | <b>✓</b> |       |

the power supply can provide current to the device's  $V_{CC}$  and ground planes. This condition can lead to latch-up and cause a low-impedance path from  $V_{CC}$  to ground within the device. As a result, the device extends a large amount of current, possibly causing electrical damage.

Altera has ensured by design of the I/O buffers and hot-socketing circuitry, that Cyclone II devices are immune to latch-up during hot socketing.

# Hot-Socketing Feature Implementation in Cyclone II Devices

The hot-socketing feature turns off the output buffer during power up (either  $V_{\rm CCINT}$  or  $V_{\rm CCIO}$  supplies) or power down. The hot-socket circuit generates an internal HOTSCKT signal when either  $V_{\rm CCINT}$  or  $V_{\rm CCIO}$  is below the threshold voltage. Designs cannot use the HOTSCKT signal for other purposes. The HOTSCKT signal cuts off the output buffer to ensure that no DC current (except for weak pull-up leakage current) leaks through the pin. When  $V_{\rm CC}$  ramps up slowly,  $V_{\rm CC}$  is still relatively low even after the internal POR signal (not available to the FPGA fabric used by customer designs) is released and the configuration is finished. The CONF\_DONE, nCEO, and nSTATUS pins fail to respond, as the output buffer cannot drive out because the hot-socketing circuitry keeps the I/O pins tristated at this low  $V_{\rm CC}$  voltage. Therefore, the hot-socketing circuit has been removed on these configuration output or bidirectional pins to ensure that they are able to operate during configuration. These pins are expected to drive out during power-up and power-down sequences.

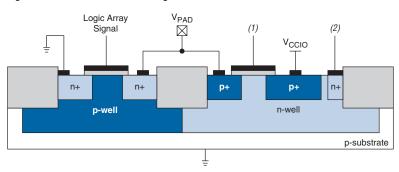

Each I/O pin has the circuitry shown in Figure 4–1.

Figure 4–2. Transistor Level Diagram of FPGA Device I/O Buffers

*Notes to Figure 4–2:*

- (1) This is the logic array signal or the larger of either the  $V_{CCIO}$  or  $V_{PAD}$  signal.

- (2) This is the larger of either the  $V_{CCIO}$  or  $V_{PAD}$  signal.

### Power-On Reset Circuitry

Cyclone II devices contain POR circuitry to keep the device in a reset state until the power supply voltage levels have stabilized during power-up. The POR circuit monitors the  $V_{\rm CCINT}$  voltage levels and tri-states all user I/O pins until the  $V_{\rm CC}$  reaches the recommended operating levels. In addition, the POR circuitry also monitors the  $V_{\rm CCIO}$  level of the two I/O banks that contains configuration pins (I/O banks 1 and 3 for EP2C5 and EP2C8, I/O banks 2 and 6 for EP2C15A, EP2C20, EP2C35, EP2C50, and EP2C70) and tri-states all user I/O pins until the  $V_{\rm CC}$  reaches the recommended operating levels.

After the Cyclone II device enters user mode, the POR circuit continues to monitor the  $V_{CCINT}$  voltage level so that a brown-out condition during user mode can be detected. If the  $V_{CCINT}$  voltage sags below the POR trip point during user mode, the POR circuit resets the device. If the  $V_{CCIO}$  voltage sags during user mode, the POR circuit does not reset the device.

### "Wake-up" Time for Cyclone II Devices

In some applications, it may be necessary for a device to wake up very quickly in order to begin operation. The Cyclone II device family offers the Fast-On feature to support fast wake-up time applications. Devices that support the Fast-On feature are designated with an "A" in the ordering code and have stricter power up requirements compared to non-A devices.

|                 |                 | Ma                   | aximum               | Output (             | Clock To             | ggle Rat             | e Derati             | ing Facto                  | ors (ps/p            | ıF)                  |

|-----------------|-----------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------------|----------------------|----------------------|

| I/O Standard    | Drive           | Column I/O Pins      |                      | Drive                |                      |                      | ns                   | Dedicated Clock<br>Outputs |                      |                      |

| J. C            | Strength        | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade       | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade |

| SSTL_2_CLASS_I  | OCT_50<br>_OHMS | 67                   | 69                   | 70                   | 25                   | 42                   | 60                   | 25                         | 42                   | 60                   |

| SSTL_18_CLASS_I | OCT_50<br>OHMS  | 30                   | 33                   | 36                   | 47                   | 49                   | 51                   | 47                         | 49                   | 51                   |

### **High Speed I/O Timing Specifications**

The timing analysis for LVDS, mini-LVDS, and RSDS is different compared to other I/O standards because the data communication is source-synchronous.

You should also consider board skew, cable skew, and clock jitter in your calculation. This section provides details on the timing parameters for high-speed I/O standards in Cyclone II devices.

Table 5–47 defines the parameters of the timing diagram shown in Figure 5–3.

| Table 5–47. High-Speed I/O Timing Definitions (Part 1 of 2) |                     |                                                                                                                                                                                                        |  |  |

|-------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                                                   | Symbol              | Description                                                                                                                                                                                            |  |  |

| High-speed clock                                            | f <sub>HSCKLK</sub> | High-speed receiver and transmitter input and output clock frequency.                                                                                                                                  |  |  |

| Duty cycle                                                  | t <sub>DUTY</sub>   | Duty cycle on high-speed transmitter output clock.                                                                                                                                                     |  |  |

| High-speed I/O data rate                                    | HSIODR              | High-speed receiver and transmitter input and output data rate.                                                                                                                                        |  |  |

| Time unit interval                                          | TUI                 | TUI = 1/HSIODR.                                                                                                                                                                                        |  |  |

| Channel-to-channel skew                                     | TCCS                | The timing difference between the fastest and slowest output edges, including $t_{CO}$ variation and clock skew. The clock is included in the TCCS measurement.<br>TCCS = TUI – SW – $(2 \times RSKM)$ |  |  |

| Table 5–54. PLL Speci | fications Note (1) (Part 2 of 2)      |     |     |       |      |

|-----------------------|---------------------------------------|-----|-----|-------|------|

| Symbol                | Parameter                             | Min | Тур | Max   | Unit |

| f <sub>VCO</sub> (3)  | PLL internal VCO operating range      | 300 | _   | 1,000 | MHz  |

| t <sub>ARESET</sub>   | Minimum pulse width on areset signal. | 10  | 1   | _     | ns   |

#### Notes to Table 5-54:

- (1) These numbers are preliminary and pending silicon characterization.

- (2) The t<sub>||TTER</sub> specification for the PLL[4..1]\_OUT pins are dependent on the I/O pins in its VCCIO bank, how many of them are switching outputs, how much they toggle, and whether or not they use programmable current strength.

- (3) If the VCO post-scale counter = 2, a 300- to 500-MHz internal VCO frequency is available.

- (4) This parameter is limited in the Quartus II software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

- (5) Cyclone II PLLs can track a spread-spectrum input clock that has an input jitter within ±200 ps.

- (6) For extended temperature devices, the maximum lock time is 500 us.

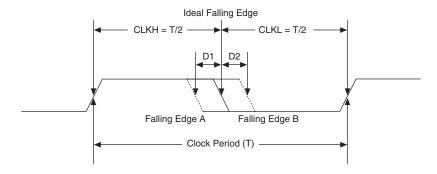

### Duty Cycle Distortion

Duty cycle distortion (DCD) describes how much the falling edge of a clock is off from its ideal position. The ideal position is when both the clock high time (CLKH) and the clock low time (CLKL) equal half of the clock period (T), as shown in Figure 5–8. DCD is the deviation of the non-ideal falling edge from the ideal falling edge, such as D1 for the falling edge A and D2 for the falling edge B (Figure 5–8). The maximum DCD for a clock is the larger value of D1 and D2.

Figure 5-8. Duty Cycle Distortion

DCD expressed in absolution derivation, for example, D1 or D2 in Figure 5–8, is clock-period independent. DCD can also be expressed as a percentage, and the percentage number is clock-period dependent. DCD as a percentage is defined as:

Section III-2 Altera Corporation

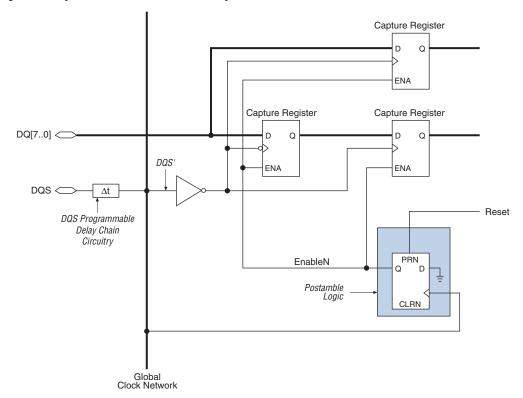

Figure 9-9. Cyclone II DQS Postamble Circuitry Connection

Figure 9–10 shows the timing waveform for Figure 9–9. When the postamble logic detects the falling DQS edge at the start of postamble, it sends out a signal to disable the capture registers to prevent any accidental latching.

| Table 10–6. Programmable Drive Strength (Part 2 of 2) |                                                                |               |  |  |  |  |

|-------------------------------------------------------|----------------------------------------------------------------|---------------|--|--|--|--|

| I/O Standard                                          | I <sub>OH</sub> /I <sub>OL</sub> Current Strength Setting (mA) |               |  |  |  |  |

| I/O Standard                                          | Top and Bottom I/O Pins                                        | Side I/O Pins |  |  |  |  |

| SSTL-2 class I                                        | 8                                                              | 8             |  |  |  |  |

|                                                       | 12                                                             | 12            |  |  |  |  |

| SSTL-2 class II                                       | 16                                                             | 16            |  |  |  |  |

|                                                       | 20                                                             | _             |  |  |  |  |

|                                                       | 24                                                             | _             |  |  |  |  |

| SSTL-18 class I                                       | 6                                                              | 6             |  |  |  |  |

|                                                       | 8                                                              | 8             |  |  |  |  |

|                                                       | 10                                                             | 10            |  |  |  |  |

|                                                       | 12                                                             | _             |  |  |  |  |

| SSTL-18 class II                                      | 16                                                             | _             |  |  |  |  |

|                                                       | 18                                                             | _             |  |  |  |  |

| HSTL-18 class I                                       | 8                                                              | 8             |  |  |  |  |

|                                                       | 10                                                             | 10            |  |  |  |  |

|                                                       | 12                                                             | 12            |  |  |  |  |

| HSTL-18 class II                                      | 16                                                             | N/A           |  |  |  |  |

|                                                       | 18                                                             | _             |  |  |  |  |

|                                                       | 20                                                             | _             |  |  |  |  |

| HSTL-15 class I                                       | 8                                                              | 8             |  |  |  |  |

|                                                       | 10                                                             | _             |  |  |  |  |

|                                                       | 12                                                             | _             |  |  |  |  |

| HSTL-15 class II                                      | 16                                                             | N/A           |  |  |  |  |

These drive-strength settings are programmable on a per-pin basis using the Quartus II software.

After applying the equation above, apply one of the equations in Table 10–9, depending on the package type.

| Table 10–9. Bidirectional Pad Limitation Formulas (Where $V_{\it REF}$ Inputs Exist) |                                                                     |  |  |  |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|

| Package Type                                                                         | Formula                                                             |  |  |  |

| FineLine BGA                                                                         | (Total number of bidirectional pads) ≤9 (per VCCIO and ground pair) |  |  |  |

| QFP                                                                                  | (Total number of bidirectional pads) ≤5 (per VCCIO and ground pair) |  |  |  |

When at least one additional output exists but no voltage referenced inputs exist, apply the appropriate formula from Table 10–10.

| Table 10–10. Bidirectional Pad Limitation Formulas (Where $V_{REF}$ Outputs Exist) |                                                                                                                                                                                             |  |  |  |  |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Package Type Formula                                                               |                                                                                                                                                                                             |  |  |  |  |

| FineLine BGA                                                                       | (Total number of bidirectional pads) + (Total number of additional output pads) − (Total number of pads from the smallest group of pads controlled by an OE) ≤9 (per VCCIO and ground pair) |  |  |  |  |

| QFP                                                                                | (Total number of bidirectional pads) + (Total number of additional output pads) − (Total number of pads from the smallest group of pads controlled by an OE) ≤5 (per VCCIO and ground pair) |  |  |  |  |

When additional voltage referenced inputs and other outputs exist in the same  $V_{REF}$  bank, the bidirectional pad limitation must again simultaneously adhere to the input and output limitations. As such, the following rules apply:

Total number of bidirectional pads + total number of input pads  $\leq$ 30 (15 on each side of your V<sub>REF</sub> pad) for Fineline BGA packages

Total number of bidirectional pads + total number of input pads  $\leq$ 0 (10 on each side of your  $V_{REF}$  pad) for QFP packages

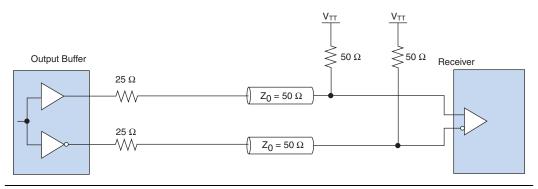

Figure 11-12. Differential SSTL Class I Interface

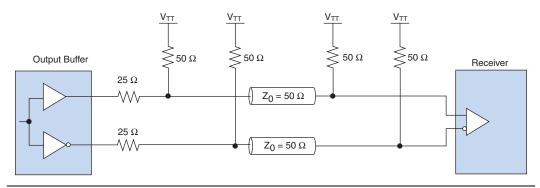

Figure 11–13. Differential SSTL Class II Interface

### **Differential HSTL Support in Cyclone II Devices**

The differential HSTL AC and DC specifications are the same as the HSTL single-ended specifications. The differential HSTL I/O standard is available on the GCLK pins only, treating differential inputs as two single-ended HSTL, and only decoding one of them. The differential HSTL output I/O standard is only supported at the PLLCLKOUT pins using two single-ended HSTL output buffers with the second output programmed as inverted. The standard requires two differential inputs with an external termination voltage ( $V_{\rm TT}$ ) of  $0.5 \times V_{\rm CCIO}$  to which termination resistors are connected.

For the HSTL signaling characteristics, see the *DC Characteristics & Timing Specifications* chapter and the *Selectable I/O Standards in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

## Document Revision History

Table 12–4 shows the revision history for this document.

| Table 12–4. Document Revision History |                                                                                                   |                                                                                          |  |  |

|---------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|

| Date &<br>Document<br>Version         | Changes Made                                                                                      | Summary of Changes                                                                       |  |  |

| February 2007<br>v1.2                 | <ul> <li>Added document revision history.</li> <li>Updated "Software Support" section.</li> </ul> | Removed reference to<br>third-party synthesis tool:<br>LeonardoSpectrum and<br>Synplify. |  |  |

| November 2005<br>v2.1                 | Updated Introduction.                                                                             |                                                                                          |  |  |

| June 2004 v1.0                        | Added document to the Cyclone II Device Handbook.                                                 |                                                                                          |  |  |

Serial configuration devices provide a serial interface to access configuration data. During device configuration, Cyclone II devices read configuration data via the serial interface, decompress data if necessary, and configure their SRAM cells. The FPGA controls the configuration interface in the AS configuration scheme, while the external host (e.g., the configuration device or microprocessor) controls the interface in the PS configuration scheme.

The Cyclone II decompression feature is available when configuring your Cyclone II device using AS mode.

Table 13–4 shows the  ${\tt MSEL}$  pin settings when using the AS configuration scheme.

| Table 13–4. Cyclone II Configuration Schemes |       |       |  |  |  |

|----------------------------------------------|-------|-------|--|--|--|

| Configuration Scheme                         | MSEL1 | MSELO |  |  |  |

| AS (20 MHz)                                  | 0     | 0     |  |  |  |

| Fast AS (40 MHz) (1)                         | 1     | 0     |  |  |  |

*Note to Table 13–4:*

### Single Device AS Configuration

Serial configuration devices have a four-pin interface: serial clock input (DCLK), serial data output (DATA), AS data input (ASDI), and an active-low chip select (nCS). This four-pin interface connects to Cyclone II device pins, as shown in Figure 13-3.

<sup>(1)</sup> Only the EPCS16 and EPCS64 devices support a DCLK up to 40 MHz clock; other EPCS devices support a DCLK up to 20 MHz. Refer to the Serial Configuration Devices Data Sheet for more information.

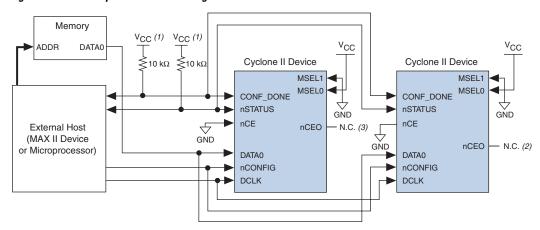

If your system has multiple Cyclone II devices (in the same density and package) with the same configuration data, you can configure them in one configuration cycle by connecting all device's nCE pins to ground and connecting all the Cyclone II device's configuration pins (nCONFIG, nSTATUS, DCLK, DATAO, and CONF\_DONE) together. You can also use the nCEO pin as a user I/O pin after configuration. The configuration signals may require buffering to ensure signal integrity and prevent clock skew problems. Make sure the DCLK and DATA lines are buffered for every fourth device. All devices start and complete configuration at the same time. Figure 13–11 shows multiple device PS configuration when both Cyclone II devices are receiving the same configuration data.

Figure 13-11. Multiple Device PS Configuration When Both FPGAs Receive the Same Data

#### *Notes to Figure 13–11:*

- (1) The pull-up resistor should be connected to a supply that provides an acceptable input signal for all devices in the chain. V<sub>CC</sub> should be high enough to meet the V<sub>IH</sub> specification of the I/O on the devices and the external host.

- (2) The nCEO pins of both devices can be left unconnected or used as user I/O pins when configuring the same configuration data into multiple devices.

You can use a single configuration chain to configure Cyclone II devices with other Altera devices. Connect all the Cyclone II device's and all other Altera device's CONF\_DONE and nSTATUS pins together so all devices in the chain complete configuration at the same time or that an error reported by one device initiates reconfiguration in all devices.

For more information on configuring multiple Altera devices in the same configuration chain, see *Configuring Mixed Altera FPGA Chains* in the *Configuration Handbook*.

### PS Configuration Timing

A PS configuration must meet the setup and hold timing parameters and the maximum clock frequency. When using a microprocessor or another intelligent host to control the PS interface, ensure that you meet these timing requirements.

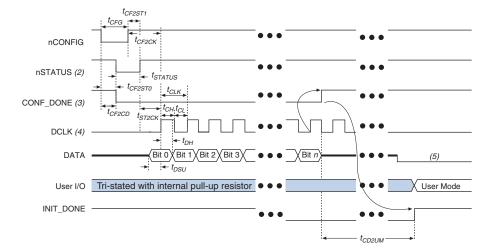

Figure 13–12 shows the timing waveform for PS configuration for Cyclone II devices.

Figure 13–12. PS Configuration Timing Waveform Note (1)

### Notes to Figure 13–12:

- (1) The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- (2) Upon power-up, the Cyclone II device holds nSTATUS low for the time of the POR delay.

- (3) Upon power-up, before and during configuration, CONF DONE is low.

- (4) In user mode, drive DCLK either high or low when using the PS configuration scheme, whichever is more convenient. When using the AS configuration scheme, DCLK is a Cyclone II output pin and should not be driven externally.

- (5) Do not leave the DATA pin floating after configuration. Drive it high or low, whichever is more convenient.

# 15. Package Information for Cyclone II Devices

CII51015-2.3

### Introduction

This chapter provides package information for Altera® Cyclone® II devices, including:

- Device and package cross reference

- Thermal resistance values

- Package outlines

Table 15–1 shows Cyclone II device package options.

| Table 15-1. | Table 15–1. Cyclone II Device Package Options |      |  |  |  |

|-------------|-----------------------------------------------|------|--|--|--|

| Device      | Package                                       | Pins |  |  |  |

| EP2C5       | Plastic Thin Quad Flat Pack (TQFP) – Wirebond | 144  |  |  |  |

|             | Plastic Quad Flat Pack (PQFP) - Wirebond      | 208  |  |  |  |

|             | Low profile FineLine BGA® – Wirebond          | 256  |  |  |  |

| EP2C8       | TQFP – Wirebond                               | 144  |  |  |  |

|             | PQFP – Wirebond                               | 208  |  |  |  |

|             | Low profile FineLine BGA – Wirebond           | 256  |  |  |  |

| EP2C15      | Low profile FineLine BGA, Option 2 – Wirebond | 256  |  |  |  |

|             | FineLine BGA, Option 3– Wirebond              | 484  |  |  |  |

| EP2C20      | PQFP – Wirebond                               | 240  |  |  |  |

|             | Low profile FineLine BGA, Option 2 – Wirebond | 256  |  |  |  |

|             | FineLine BGA, Option 3– Wirebond              | 484  |  |  |  |

| EP2C35      | FineLine BGA, Option 3 – Wirebond             | 484  |  |  |  |

|             | Ultra FineLine BGA – Wirebond                 | 484  |  |  |  |

|             | FineLine BGA, Option 3 – Wirebond             | 672  |  |  |  |

| EP2C50      | FineLine BGA, Option 3 – Wirebond             | 484  |  |  |  |

|             | Ultra FineLine BGA – Wirebond                 | 484  |  |  |  |

|             | FineLine BGA, Option 3 – Wirebond             | 672  |  |  |  |

| EP2C70      | FineLine BGA, Option 3 – Wirebond             | 672  |  |  |  |

|             | FineLine BGA – Wirebond                       | 896  |  |  |  |

### 484-Pin Ultra FineLine BGA - Wirebond

- All dimensions and tolerances conform to ASME Y14.5M 1994.

- Controlling dimension is in millimeters.

- Pin A1 may be indicated by an ID dot, or a special feature, in its proximity on package surface.

Tables 15–15 and 15–16 show the package information and package outline figure references, respectively, for the 484-pin Ultra FineLine BGA package.

| Table 15–15. 484-Pin Ultra FineLine BGA Package Information |                                                           |  |  |  |

|-------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

| Description                                                 | Specification                                             |  |  |  |

| Ordering Code Reference                                     | U                                                         |  |  |  |

| Package Acronym                                             | UBGA                                                      |  |  |  |

| Substrate Material                                          | ВТ                                                        |  |  |  |

| Solder Ball Composition                                     | Regular: 63Sn:37Pb (Typ.)<br>Pb-free: Sn:3Ag:0.5Cu (Typ.) |  |  |  |

| JEDEC Outline Reference                                     | MO-216 Variation: BAP-2                                   |  |  |  |

| Maximum Lead Coplanarity                                    | 0.005 inches (0.12mm)                                     |  |  |  |

| Weight                                                      | 1.8 g                                                     |  |  |  |

| Moisture Sensitivity Level                                  | Printed on moisture barrier bag                           |  |  |  |

| Table 15–16. 484-Pin Ultra FineLine BGA Package Outline Dimensions |            |      |      |  |  |

|--------------------------------------------------------------------|------------|------|------|--|--|

| Symbol                                                             | Millimeter |      |      |  |  |

|                                                                    | Min.       | Nom. | Max. |  |  |

| А                                                                  | -          | -    | 2.20 |  |  |

| A1                                                                 | 0.20       | _    | -    |  |  |

| A2                                                                 | 0.65       | -    | _    |  |  |

| A3                                                                 | 0.80 TYP   |      |      |  |  |

| D                                                                  | 19.00 BSC  |      |      |  |  |

| E                                                                  | 19.00 BSC  |      |      |  |  |

| b                                                                  | 0.40       | 0.50 | 0.60 |  |  |

| е                                                                  | 0.80 BSC   |      |      |  |  |