Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 4276                                                    |

| Number of Logic Elements/Cells | 68416                                                   |

| Total RAM Bits                 | 1152000                                                 |

| Number of I/O                  | 622                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 896-BGA                                                 |

| Supplier Device Package        | 896-FBGA (31x31)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c70f896c7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Guidelines for IEEE Std. 1149.1 Boundary-Scan Testing  | 14–18 |

|--------------------------------------------------------|-------|

| Boundary-Scan Description Language (BSDL) Support      | 14–19 |

| Conclusion                                             | 14–19 |

| References                                             | 14–19 |

| Document Revision History                              | 14–20 |

| ·                                                      |       |

|                                                        |       |

| Costion VII DCD Loveut Cuidelines                      |       |

| Section VII. PCB Layout Guidelines                     |       |

| Revision History                                       | 14–1  |

|                                                        |       |

| Chapter 15. Package Information for Cyclone II Devices |       |

| Introduction                                           | 15–1  |

| Thermal Resistance                                     |       |

| Package Outlines                                       |       |

| 144-Pin Plastic Thin Quad Flat Pack (TQFP) – Wirebond  | 15–4  |

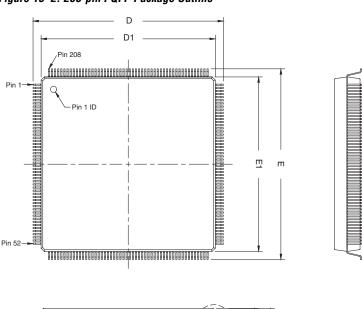

| 208-Pin Plastic Quad Flat Pack (PQFP) – Wirebond       |       |

| 240-Pin Plastic Quad Flat Pack (PQFP)                  |       |

| 256-Pin FineLine Ball-Grid Array, Option 2 – Wirebond  |       |

| 484-Pin FineLine BGA, Option 3 – Wirebond              |       |

| 484-Pin Ultra FineLine BGA – Wirebond                  |       |

| 672-Pin FineLine BGA Package, Option 3 – Wirebond      |       |

| σ                                                      |       |

phase-align double data rate (DDR) signals) provide interface support for external memory devices such as DDR, DDR2, and single data rate (SDR) SDRAM, and QDRII SRAM devices at up to 167 MHz.

Figure 2–1 shows a diagram of the Cyclone II EP2C20 device.

PLL IOEs PLL Embedded Multipliers Logic Logic Logic Logic **IOEs IOEs** Array Array Array Array M4K Blocks M4K Blocks PLL **IOEs PLL**

Figure 2–1. Cyclone II EP2C20 Device Block Diagram

The number of M4K memory blocks, embedded multiplier blocks, PLLs, rows, and columns vary per device.

### **Logic Elements**

The smallest unit of logic in the Cyclone II architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE features:

- A four-input look-up table (LUT), which is a function generator that can implement any function of four variables

- A programmable register

- A carry chain connection

- A register chain connection

- The ability to drive all types of interconnects: local, row, column, register chain, and direct link interconnects

- Support for register packing

- Support for register feedback

| Table 2–1. Cy           | Table 2–1. Cyclone II Device Routing Scheme (Part 2 of 2) |                    |                          |                 |                  |                 |                  |    |               |                     |     |            |         |

|-------------------------|-----------------------------------------------------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|----|---------------|---------------------|-----|------------|---------|

|                         |                                                           | Destination        |                          |                 |                  |                 |                  |    |               |                     |     |            |         |

| Source                  | Register Chain                                            | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | 31 | M4K RAM Block | Embedded Multiplier | PLL | Column 10E | Row IOE |

| LE                      | <b>✓</b>                                                  | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |    |               |                     |     |            |         |

| M4K memory<br>Block     |                                                           | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |    |               |                     |     |            |         |

| Embedded<br>Multipliers |                                                           | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |    |               |                     |     |            |         |

| PLL                     |                                                           |                    | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |    |               |                     |     |            |         |

| Column IOE              |                                                           |                    |                          |                 |                  | ~               | <b>✓</b>         |    |               |                     |     |            |         |

| Row IOE                 |                                                           |                    | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        |                  |    |               |                     |     |            |         |

## Global Clock Network & Phase-Locked Loops

Cyclone II devices provide global clock networks and up to four PLLs for a complete clock management solution. Cyclone II clock network features include:

- Up to 16 global clock networks

- Up to four PLLs

- Global clock network dynamic clock source selection

- Global clock network dynamic enable and disable

| Table 5–9. DC Cl                                 | Table 5–9. DC Characteristics for User I/O Pins Using Differential I/O Standards Note (1) (Part 2 of 2) |     |     |                      |     |                                          |                            |                                          |                            | of 2) |                     |                         |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|-----|----------------------|-----|------------------------------------------|----------------------------|------------------------------------------|----------------------------|-------|---------------------|-------------------------|

| I/O Otomdovd                                     | V <sub>OD</sub> (mV)                                                                                    |     |     | $\Delta V_{0D}$ (mV) |     | V <sub>OCM</sub> (V)                     |                            |                                          | V <sub>OH</sub> (V)        |       | V <sub>OL</sub> (V) |                         |

| I/O Standard                                     | Min                                                                                                     | Тур | Max | Min                  | Max | Min                                      | Тур                        | Max                                      | Min                        | Max   | Min                 | Max                     |

| Differential 1.8-V<br>HSTL class I<br>and II (3) | _                                                                                                       | _   | _   | _                    | _   | _                                        | _                          | _                                        | V <sub>CCIO</sub><br>- 0.4 | _     | _                   | 0.4                     |

| Differential<br>SSTL-2 class I                   | _                                                                                                       |     | _   | _                    | _   | _                                        |                            | _                                        | V <sub>TT</sub> + 0.57     | _     |                     | V <sub>TT</sub> – 0.57  |

| Differential<br>SSTL-2 class II<br>(4)           | _                                                                                                       | _   | _   | _                    | _   | _                                        |                            | _                                        | V <sub>TT</sub> + 0.76     | _     | _                   | V <sub>TT</sub> – 0.76  |

| Differential<br>SSTL-18 class I<br>(4)           | _                                                                                                       |     | _   | _                    | _   | 0.5 x<br>V <sub>CCIO</sub><br>-<br>0.125 | 0.5 ×<br>V <sub>CCIO</sub> | 0.5 ×<br>V <sub>CCIO</sub><br>+<br>0.125 | V <sub>TT</sub> + 0.475    | _     |                     | V <sub>TT</sub> – 0.475 |

| Differential<br>SSTL-18 class II                 | _                                                                                                       | _   | _   | _                    |     | 0.5 ×<br>V <sub>CCIO</sub><br>-<br>0.125 | 0.5 ×<br>V <sub>CCIO</sub> | 0.5 ×<br>V <sub>CCIO</sub><br>+<br>0.125 | V <sub>CCIO</sub> – 0.28   | _     | _                   | 0.28                    |

#### Notes to Table 5-9:

- (1) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (2) The RSDS and mini-LVDS I/O standards are only supported on output pins.

- (3) The differential 1.8-V HSTL and differential 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

- (4) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

## DC Characteristics for Different Pin Types

Table 5–10 shows the types of pins that support bus hold circuitry.

| Table 5–10. Bus Hold Support              |          |  |  |  |  |  |

|-------------------------------------------|----------|--|--|--|--|--|

| Pin Type                                  | Bus Hold |  |  |  |  |  |

| I/O pins using single-ended I/O standards | Yes      |  |  |  |  |  |

| I/O pins using differential I/O standards | No       |  |  |  |  |  |

| Dedicated clock pins                      | No       |  |  |  |  |  |

| JTAG                                      | No       |  |  |  |  |  |

| Configuration pins                        | No       |  |  |  |  |  |

You should select power supplies and regulators that can supply the amount of current required when designing with Cyclone II devices.

Altera recommends using the Cyclone II PowerPlay Early Power Estimator to estimate the user-mode  $I_{CCINT}$  consumption and then select power supplies or regulators based on the values obtained.

# Timing Specifications

The DirectDrive<sup>TM</sup> technology and MultiTrack<sup>TM</sup> interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Cyclone II device densities and speed grades. This section describes and specifies the performance, internal, external, high-speed I/O, JTAG, and PLL timing specifications.

This section shows the timing models for Cyclone II devices. Commercial devices meet this timing over the commercial temperature range. Industrial devices meet this timing over the industrial temperature range. Automotive devices meet this timing over the automotive temperature range. Extended devices meet this timing over the extended temperature range. All specifications are representative of worst-case supply voltage and junction temperature conditions.

#### Preliminary and Final Timing Specifications

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 5–14 shows the status of the Cyclone II device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Table 5-42. Cyclone II I/O Output Delay for Column Pins (Part 6 of 6) **Fast Corner** -7 -7 -6 -8 Drive Speed Speed Speed I/O Standard **Parameter** Speed Unit Industrial/ Commer Strength Grade Grade Grade Grade **Automotive** -cial (2) (3) 1.5V\_DIFFERENTIAL 16 mA 1750 1836 3844 4125 4399 4406 t<sub>OP</sub> ps \_HSTL\_CLASS\_II (1) 1882 1975 4014 4319 4625 4625 ps  $t_{DIP}$ **LVDS**  $t_{OP}$ 1258 1319 2243 2344 2438 2445 ps 2538 1390 1458 2413 2664 2664 ps  $t_{DIP}$ **RSDS** 1319 2344  $t_{OP}$ 1258 2243 2438 2445 ps 2413 2538 1390 1458 2664 2664  $t_{DIP}$ ps MINI\_LVDS 1258 2344 1319 2243 2438 2445  $t_{OP}$ ps 1390 1458 2413 2538 2664 2664  $t_{DIP}$ ps SIMPLE\_RSDS 1221 1280 2258 2435 2605 2612  $t_{OP}$ ps 1353 1419 2428 2629 2831 2831 ps  $t_{DIP}$ 1.2V\_HSTL 2403 2522 4635 5344 6046 6053  $t_{OP}$ ps 2535 2661 4805 5538 6272 6272  $t_{DIP}$ ps 1.2V DIFFERENTIAL 2522 4635 5344  $t_{OP}$ 2403 6046 6053 ps \_HSTL 2535 2661 4805 5538 6272 6272  $t_{DIP}$ ps

#### Notes to Table 5–42:

- (1) This is the default setting in the Quartus II software.

- (2) These numbers are for commercial devices.

- (3) These numbers are for automotive devices.

### 7. PLLs in Cyclone II Devices

CII51007-3.1

#### Introduction

Cyclone<sup>®</sup> II devices have up to four phase-locked loops (PLLs) that provide robust clock management and synthesis for device clock management, external system clock management, and I/O interfaces. Cyclone II PLLs are versatile and can be used as a zero delay buffer, a jitter attenuator, a low skew fan out buffer, or a frequency synthesizer.

Each Cyclone II device has up to four PLLs, supporting advanced capabilities such as clock switchover and programmable switchover. These PLLs offer clock multiplication and division, phase shifting, and programmable duty cycle and can be used to minimize clock delay and clock skew, and to reduce or adjust clock-to-out ( $t_{CO}$ ) and set-up ( $t_{SU}$ ) times.

Cyclone II devices also support a power-down mode where unused clock networks can be turned off. The Altera<sup>®</sup> Quartus<sup>®</sup> II software enables the PLLs and their features without requiring any external devices.

Cyclone II PLLs have been characterized to operate in the commercial junction temperature range (0° to 85° C), the industrial junction temperature range (-40° to 100° C) and the extended temperature range (-40° to 125° C).

Table 7–1 shows the PLLs available in each Cyclone II device.

| Table 7–1. Cyclone II Device PLL Availability |          |          |          |      |  |  |  |  |

|-----------------------------------------------|----------|----------|----------|------|--|--|--|--|

| Device                                        | PLL1     | PLL2     | PLL3     | PLL4 |  |  |  |  |

| EP2C5                                         | <b>✓</b> | <b>✓</b> |          |      |  |  |  |  |

| EP2C8                                         | <b>✓</b> | ✓        |          |      |  |  |  |  |

| EP2C15                                        | ✓        | ✓        | <b>✓</b> | ✓    |  |  |  |  |

| EP2C20                                        | ✓        | ✓        | <b>✓</b> | ✓    |  |  |  |  |

| EP2C35                                        | ✓        | ✓        | <b>✓</b> | ✓    |  |  |  |  |

| EP2C50                                        | ✓        | <b>✓</b> | <b>✓</b> | ✓    |  |  |  |  |

| EP2C70                                        | ✓        | ✓        | ✓        | ✓    |  |  |  |  |

| Table 7–9. Clock Control Block Inputs (Part 2 of 2) |                                                                                                                                                           |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Input Description                                   |                                                                                                                                                           |  |  |  |  |

| PLL outputs                                         | The PLL counter outputs can drive the global clock network.                                                                                               |  |  |  |  |

| Internal logic                                      | The global clock network can also be driven through the logic array routing to enable internal logic (LEs) to drive a high fan-out, low skew signal path. |  |  |  |  |

In Cyclone II devices, the dedicated clock input pins, PLL counter outputs, dual-purpose clock I/O inputs, and internal logic can all feed the clock control block for each global clock network. The output from the clock control block in turn feeds the corresponding global clock network. The clock control blocks are arranged on the device periphery and there are a maximum of 16 clock control blocks available per Cyclone II device.

The control block has two functions:

- Dynamic global clock network clock source selection

- Global clock network power-down (dynamic enable and disable)

Figure 7–11 shows the clock control block.

#### **VCCA & GNDA**

Each Cyclone II PLL uses separate VCC and ground pin pairs for their analog circuitry. The analog circuit power and ground pin for each PLL is called VCCA\_PLL</br>

PLL

<

- Use separate VCCA power planes

- Use a partitioned VCCA island within the VCCINT plane

- Use thick VCCA traces

#### Separate VCCA Power Plane

A mixed signal system is already partitioned into analog and digital sections, each with its own power planes on the board. To isolate the VCCA pin using a separate VCCA power plane, connect the VCCA pin to the analog 1.2-V power plane.

#### Partitioned VCCA Island Within the VCCINT Plane

Fully digital systems do not have a separate analog power plane on the board. Since it is expensive to add new planes to the board, you can create islands for VCCA\_PLL. Figure 7–16 shows an example board layout with an analog power island. The dielectric boundary that creates the island should be 25 mils thick. Figure 7–16 shows a partitioned plane within  $V_{\rm CCINT}$  for VCCA.

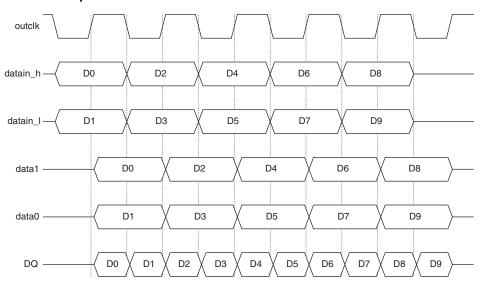

Figure 9-15. DDR Output Waveforms

#### **Bidirectional DDR Registers**

Figure 9–16 shows a bidirectional DDR interface constructed using the DDR input and DDR output examples described in the previous two sections. As with the DDR input and DDR output examples, the bidirectional DDR pin can be any available user I/O pin. The registers that implement DDR bidirectional logic are LEs in the LAB adjacent to that pin. The tri-state buffer controls when the device drives data onto the bidirectional DDR pin.

#### 3.3-V LVCMOS (EIA/JEDEC Standard JESD8-B)

The 3.3-V LVCMOS I/O standard is a general-purpose, single-ended standard used for 3.3-V applications. The LVCMOS standard defines the DC interface parameters for digital circuits operating from a 3.0- or 3.3-V power supply and driving or being driven by LVCMOS-compatible devices.

The LVCMOS standard specifies the same input voltage requirements as LVTTL ( $-0.3~\rm V \le \!\! V_I \le \!\! 3.9~\rm V$ ). The output buffer drives to the rail to meet the minimum high-level output voltage requirements. The 3.3-V I/O standard does not require input reference voltages or board terminations. Cyclone II devices support both input and output levels specified by the 3.3-V LVCMOS I/O standard.

## 3.3-V (PCI Special Interest Group [SIG] PCI Local Bus Specification Revision 3.0)

The PCI local bus specification is used for applications that interface to the PCI local bus, which provides a processor-independent data path between highly integrated peripheral controller components, peripheral add-in boards, and processor/memory systems. The conventional PCI specification revision 3.0 defines the PCI hardware environment including the protocol, electrical, mechanical, and configuration specifications for the PCI devices and expansion boards. This standard requires a 3.3-V  $\rm V_{\rm CCIO}$ . The 3.3-V PCI standard does not require input reference voltages or board terminations.

The side (left and right) I/O banks on all Cyclone II devices are fully compliant with the 3.3V PCI Local Bus Specification Revision 3.0 and meet 32-bit/66 MHz operating frequency and timing requirements.

Table 10–2 lists the specific Cyclone II devices that support 64- and 32-bit PCI at 66 MHz.

| Table 10–2. Cyclone II 66-MHz PCI Support (Part 1 of 2) |                      |                        |         |  |  |  |  |

|---------------------------------------------------------|----------------------|------------------------|---------|--|--|--|--|

| Device                                                  | Package              | –6 and –7 Speed Grades |         |  |  |  |  |

| Device                                                  | rackaye              | 64 Bits                | 32 Bits |  |  |  |  |

| EP2C5                                                   | 144-pin TQFP         |                        |         |  |  |  |  |

|                                                         | 208-pin PQFP         |                        | ✓       |  |  |  |  |

|                                                         | 256-pin FineLineBGA® |                        | ✓       |  |  |  |  |

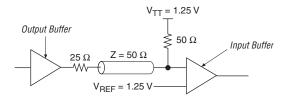

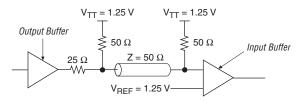

Figure 10-1. SSTL-2 Class I Termination

Figure 10-2. SSTL-2 Class II Termination

Cyclone II devices support both input and output SSTL-2 class I and II levels.

#### Pseudo-Differential SSTL-2

The differential SSTL-2 I/O standard (EIA/JEDEC standard JESD8-9A) is a 2.5-V standard used for applications such as high-speed DDR SDRAM clock interfaces. This standard supports differential signals in systems using the SSTL-2 standard and supplements the SSTL-2 standard for differential clocks. The differential SSTL-2 standard specifies an input voltage range of – 0.3 V  $\leq$ V $_{\rm I}$   $\leq$ V $_{\rm CCIO}$  + 0.3 V. The differential SSTL-2 standard does not require an input reference voltage. Refer to Figures 10–3 and 10–4 for details on differential SSTL-2 terminations.

Cyclone II devices do not support true differential SSTL-2 standards. Cyclone II devices support pseudo-differential SSTL-2 outputs for PLL\_OUT pins and pseudo-differential SSTL-2 inputs for clock pins. Pseudo-differential inputs require an input reference voltage as opposed to the true differential inputs. Refer to Table 10–1 on page 10–2 for information about pseudo-differential SSTL.

#### **V**<sub>REF</sub> Pad Placement Guidelines

To maintain an acceptable noise level on the  $V_{CCIO}$  supply and to prevent output switching noise from shifting the  $V_{REF}$  rail, there are restrictions on the placement of single-ended voltage referenced I/Os with respect to  $V_{REF}$  pads and VCCIO and ground pairs. Use the following guidelines for placing single-ended pads in Cyclone II devices.

The Quartus II software automatically does all the calculations in this section.

#### Input Pads

Each  $V_{REF}$  pad supports up to 15 input pads on each side of the  $V_{REF}$  pad for FineLine BGA devices. Each  $V_{REF}$  pad supports up to 10 input pads on each side of the  $V_{REF}$  pad for quad flat pack (QFP) devices. This is irrespective of VCCIO and ground pairs, and is guaranteed by the Cyclone II architecture.

#### Output Pads

When a voltage referenced input or bidirectional pad does not exist in a bank, there is no limit to the number of output pads that can be implemented in that bank. When a voltage referenced input exists, each VCCIO and ground pair supports 9 output pins for Fineline BGA packages (not more than 9 output pins per 12 consecutive row I/O pins) or 5 output pins for QFP packages (not more than 5 output pins per 12 consecutive row I/O pins or 8 consecutive column I/O pins). Any non-SSTL and non-HSTL output can be no closer than two pads away from a  $V_{\rm REF}$  pad. Altera recommends that any SSTL or HSTL output, except for pintable defined DQ and DQS outputs, to be no closer than two pads away from a  $V_{\rm REF}$  pad to maintain acceptable noise levels.

Quartus II software will not check for the SSTL and HSTL output pads placement rule.

Refer to "DDR and QDR Pads" on page 10–32 for details about guidelines for DQ and DQS pads placement.

#### Bidirectional Pads

Bidirectional pads must satisfy input and output guidelines simultaneously.

Refer to "DDR and QDR Pads" on page 10–32 for details about guidelines for DQ and DQS pads placement.

You can use a single configuration chain to configure Cyclone II devices with other Altera devices. To ensure that all devices in the chain complete configuration at the same time or that an error flagged by one device initiates reconfiguration in all devices, connect all the Cyclone II device CONF\_DONE pins and connect all Cyclone II device nSTATUS pins together.

For more information on configuring multiple Altera devices in the same configuration chain, see the *Configuring Mixed Altera FPGA Chains* chapter in the *Configuration Handbook*.

During PS configuration, the design must meet the setup and hold timing parameters and maximum DCLK frequency. The enhanced configuration and EPC2 devices are designed to meet these interface timing specifications.

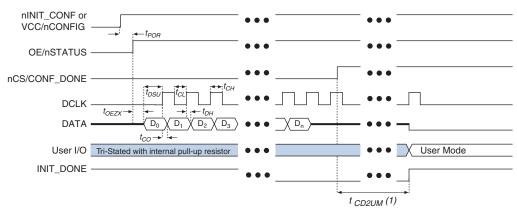

Figure 13–18 shows the timing waveform for the PS configuration scheme using a configuration device.

Figure 13–18. Cyclone II PS Configuration Using a Configuration Device Timing Waveform

Note to Figure 13-18:

(1) Cyclone II devices enter user mode 299 clock cycles after CONF\_DONE goes high. The initialization clock can come from the Cyclone II internal oscillator or the CLKUSR pin.

For timing information, refer to the *Enhanced Configuration Devices* (EPC4, EPC8, and EPC16) Data Sheet or the Configuration Devices for SRAM-based LUT Devices Data Sheet in the Configuration Handbook.

For more information on device configuration options and how to create configuration files, see the *Software Settings* section in Volume 2 of the *Configuration Handbook*.

enables the programming software to program or verify the target device. Configuration data driven into the target device appears on the TDO pin one clock cycle later.

The Quartus II software verifies successful JTAG configuration upon completion. At the end of configuration, the software checks the CONF\_DONE pin through the JTAG port. When the Quartus II software generates a JAM file for a multiple device chain, it contains instructions so that all the devices in the chain are initialized at the same time. If CONF\_DONE is not high, the Quartus II software indicates that configuration has failed. If the CONF\_DONE pin transitions high, the software indicates that configuration was successful. After the configuration bitstream is transmitted serially via the JTAG TDI port, the TCK port is clocked an additional 299 cycles to perform Cyclone II device initialization.

The Enable user-supplied start-up clock (CLKUSR) option has no affect on the device initialization since this option is disabled in the SOF when configuring the FPGA in JTAG using the Quartus II programmer and download cable. Therefore, if you turn on the CLKUSR option, you do not need to provide a clock on CLKUSR when you are configuring the FPGA with the Quartus II programmer and a download cable.

Cyclone II devices have dedicated JTAG pins that always function as JTAG pins. You can perform JTAG testing on Cyclone II devices before, after, and during configuration. Cyclone II devices support the BYPASS, IDCODE and SAMPLE instructions during configuration without interruption. All other JTAG instructions may only be issued by first interrupting configuration and reprogramming I/O pins using the CONFIG IO instruction.

The <code>CONFIG\_IO</code> instruction allows I/O buffers to be configured via the JTAG port. The <code>CONFIG\_IO</code> instruction interrupts configuration. This instruction allows you to perform board-level testing before configuring the Cyclone II device or waiting for a configuration device to complete configuration. If you interrupt configuration, the Cyclone II device must be reconfigured via <code>JTAG</code> (<code>PULSE\_CONFIG</code> instruction) or by pulsing <code>nCONFIG</code> low after <code>JTAG</code> testing is complete.

For more information, see the *MorphIO: An I/O Reconfiguration Solution* for Altera White Paper.

The chip-wide reset (DEV\_CLRn) and chip-wide output enable (DEV\_OE) pins on Cyclone II devices do not affect JTAG boundary-scan or programming operations. Toggling these pins does not affect JTAG operations (other than the usual boundary-scan operation).

| Table 13–11. Dedicated Configuration Pins on the Cyclone II Device (Part 4 of 5) |                                                          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|----------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name                                                                         | User<br>Mode                                             | Configuration<br>Scheme | Pin Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| nCEO                                                                             | N/A if option is on. I/O if option is off.               | All                     | Output   | This pin is an output that drives low when device configuration is complete. In single device configuration, you can leave this pin floating or use it as a user I/O pin after configuration. In multiple device configuration, this pin inputs the next device's $n\text{CE}$ pin. The $n\text{CEO}$ of the last device in the chain can be left floating or used as a user I/O pin after configuration. If you use the $n\text{CEO}$ pin to feed next device's $n\text{CE}$ pin, use an external 10-k $\Omega$ pull-up resistor to pull the $n\text{CEO}$ pin high to the $V_{\text{CCIO}}$ voltage of its I/O bank to help the internal weak pull-up resistor. |  |  |  |  |  |

|                                                                                  |                                                          |                         |          | Use the Quartus II software to make this pin a user I/O pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| ASDO                                                                             | N/A in<br>AS<br>mode<br>I/O in<br>PS and<br>JTAG<br>mode | AS                      | Output   | This pin sends a control signal from the Cyclone II device to the serial configuration device in AS mode and is used to read out configuration data.  In AS mode, ASDO has an internal pull-up that is always active.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| nCSO                                                                             | N/A in<br>AS<br>mode<br>I/O in<br>PS and<br>JTAG<br>mode | AS                      | Output   | This pin sends an output control signal from the Cyclone II device to the serial configuration device in AS mode that enables the configuration device.  In AS mode, nCSO has an internal pull-up resistor that is always active.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

frequency (up to 40 MHz), which reduces your configuration time. In addition, Cyclone II devices can receive a compressed configuration bitstream and decompress this data on-the-fly in the AS or PS configuration scheme, which further reduces storage requirements and configuration time.

## 14. IEEE 1149.1 (JTAG) Boundary-Scan Testing for Cyclone II Devices

CII51014-2.1

#### Introduction

As printed circuit boards (PCBs) become more complex, the need for thorough testing becomes increasingly important. Advances in surface-mount packaging and PCB manufacturing have resulted in smaller boards, making traditional test methods (e.g., external test probes and "bed-of-nails" test fixtures) harder to implement. As a result, cost savings from PCB space reductions are sometimes offset by cost increases in traditional testing methods.

In the 1980s, the Joint Test Action Group (JTAG) developed a specification for boundary-scan testing that was later standardized as the IEEE Std. 1149.1 specification. This boundary-scan test (BST) architecture offers the capability to efficiently test components on PCBs with tight lead spacing.

This BST architecture tests pin connections without using physical test probes and captures functional data while a device is operating normally. Boundary-scan cells in a device force signals onto pins or capture data from pin or logic array signals. Forced test data is serially shifted into the boundary-scan cells. Captured data is serially shifted out and externally compared with expected results. Figure 14–1 shows the concept of boundary-scan testing.

Serial Data In IC Pin Signal Serial Data Out

Tested Connection JTAG Device 2

Figure 14-1. IEEE Std. 1149.1 Boundary-Scan Testing

# Thermal Resistance

Thermal resistance values for Cyclone II devices are provided for a board meeting JEDEC specifications and for a typical board. The values provided are as follows:

- θ<sub>JA</sub> (°C/W) Still Air—Junction-to-ambient thermal resistance with no airflow when a heat sink is not being used.

- $\theta_{JA}$  (° C/W) 100 ft./minute—Junction-to-ambient thermal resistance with 100 ft./minute airflow when a heat sink is not being used.

- $\theta_{JA}$  (° C/W) 200 ft./minute—Junction-to-ambient thermal resistance with 200 ft./minute airflow when a heat sink is not being used.

- $\theta_{JA}$  (° C/W) 400 ft./minute—Junction-to-ambient thermal resistance with 400 ft./minute airflow when a heat sink is not being used.

- $\theta_{IC}$  (°C/W)—Junction-to-case thermal resistance for device.

- $\theta_{JB}$  (° C/W)—Junction-to-board thermal resistance for specific board being used.

Table 15–2 provides  $\theta_{JA}$  (junction-to-ambient thermal resistance) values and  $\theta_{JC}$  (junction-to-case thermal resistance) values for Cyclone II devices on a board meeting JEDEC specifications for thermal resistance calculation. The JEDEC board specifications require two signal and two power/ground planes and are available at **www.jedec.org**.

| Table 15–2. Thermal Resistance of Cyclone II Devices for Board Meeting JEDEC Specifications (Part 1 of 2) |              |                    |                                      |                                         |      |                                         |                                    |  |  |  |

|-----------------------------------------------------------------------------------------------------------|--------------|--------------------|--------------------------------------|-----------------------------------------|------|-----------------------------------------|------------------------------------|--|--|--|

| Device                                                                                                    | Pin<br>Count | Package            | θ <sub>JA</sub> (° C/W)<br>Still Air | θ <sub>JA</sub> (° C/W)<br>100 ft./min. | • ,  | θ <sub>JA</sub> (° C/W)<br>400 ft./min. | θ <sub>JC</sub><br>(° <b>C/W</b> ) |  |  |  |

| EP2C5                                                                                                     | 144          | TQFP               | 31                                   | 29.3                                    | 27.9 | 25.5                                    | 10                                 |  |  |  |

|                                                                                                           | 208          | PQFP               | 30.4                                 | 29.2                                    | 27.3 | 22.3                                    | 5.5                                |  |  |  |

|                                                                                                           | 256          | FineLine BGA       | 30.2                                 | 26.1                                    | 23.6 | 21.7                                    | 8.7                                |  |  |  |

| EP2C8                                                                                                     | 144          | TQFP               | 29.8                                 | 28.3                                    | 26.9 | 24.9                                    | 9.9                                |  |  |  |

|                                                                                                           | 208          | PQFP               | 30.2                                 | 28.8                                    | 26.9 | 21.7                                    | 5.4                                |  |  |  |

|                                                                                                           | 256          | FineLine BGA       | 27                                   | 23                                      | 20.5 | 18.5                                    | 7.1                                |  |  |  |

| EP2C15                                                                                                    | 256          | FineLine BGA       | 24.2                                 | 20                                      | 17.8 | 16                                      | 5.5                                |  |  |  |

|                                                                                                           | 484          | FineLine BGA       | 21                                   | 17                                      | 14.8 | 13.1                                    | 4.2                                |  |  |  |

| EP2C20                                                                                                    | 240          | PQFP               | 26.6                                 | 24                                      | 21.4 | 17.4                                    | 4.2                                |  |  |  |

|                                                                                                           | 256          | FineLine BGA       | 24.2                                 | 20                                      | 17.8 | 16                                      | 5.5                                |  |  |  |

|                                                                                                           | 484          | FineLine BGA       | 21                                   | 17                                      | 14.8 | 13.1                                    | 4.2                                |  |  |  |

| EP2C35                                                                                                    | 484          | FineLine BGA       | 19.4                                 | 15.4                                    | 13.3 | 11.7                                    | 3.3                                |  |  |  |

|                                                                                                           | 484          | Ultra FineLine BGA | 20.6                                 | 16.6                                    | 14.5 | 12.8                                    | 5                                  |  |  |  |

|                                                                                                           | 672          | FineLine BGA       | 18.6                                 | 14.6                                    | 12.6 | 11.1                                    | 3.1                                |  |  |  |

| Table 15–8. 208-Pin PQFP Package Outline Dimensions (Part 2 of 2) |            |      |      |  |  |  |

|-------------------------------------------------------------------|------------|------|------|--|--|--|

| Cumbal                                                            | Millimeter |      |      |  |  |  |

| Symbol                                                            | Min.       | Nom. | Max. |  |  |  |

| е                                                                 | 0.50 BSC   |      |      |  |  |  |

| q                                                                 | 0° 3.5° 8° |      |      |  |  |  |

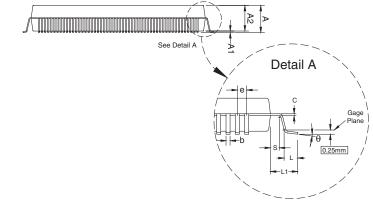

Figure 15–2 shows a 208-pin PQFP package outline.

Figure 15-2. 208-pin PQFP Package Outline