Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 4276                                                     |

| Number of Logic Elements/Cells | 68416                                                    |

| Total RAM Bits                 | 1152000                                                  |

| Number of I/O                  | 622                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 896-BGA                                                  |

| Supplier Device Package        | 896-FBGA (31x31)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c70f896c8n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

R24 row interconnects span 24 LABs and provide the fastest resource for long row connections between non-adjacent LABs, M4K memory blocks, dedicated multipliers, and row IOEs. R24 row interconnects drive to other row or column interconnects at every fourth LAB. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects and do not drive directly to LAB local interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

#### **Column Interconnects**

The column interconnect operates similar to the row interconnect. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs, M4K memory blocks, embedded multipliers, and row and column IOEs. These column resources include:

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four blocks in an up and down direction

- C16 interconnects for high-speed vertical routing through the device

Cyclone II devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using register chain connections. The register chain connection allows the register output of one LE to connect directly to the register input of the next LE in the LAB for fast shift registers. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–9 shows the register chain interconnects.

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, M4K memory blocks, embedded multipliers, and IOEs. C16 column interconnects drive to other row and column interconnects at every fourth LAB. C16 column interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly. C16 interconnects can drive R24, R4, C16, and C4 interconnects.

## **Device Routing**

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (for example, M4K memory, embedded multiplier, or PLL) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB.

Table 2–1 shows the Cyclone II device's routing scheme.

| Table 2–1. Cy               | Table 2–1. Cyclone II Device Routing Scheme (Part 1 of 2) |                    |                          |                 |                  |                 |                  |          |               |                     |     |            |          |

|-----------------------------|-----------------------------------------------------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|----------|---------------|---------------------|-----|------------|----------|

|                             |                                                           | Destination        |                          |                 |                  |                 |                  |          |               |                     |     |            |          |

| Source                      | Register Chain                                            | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | 31       | M4K RAM Block | Embedded Multiplier | PLL | Column 10E | Row IOE  |

| Register<br>Chain           |                                                           |                    |                          |                 |                  |                 |                  | <b>~</b> |               |                     |     |            |          |

| Local<br>Interconnect       |                                                           |                    |                          |                 |                  |                 |                  | ~        | ~             | ~                   | ~   | <b>✓</b>   | <b>✓</b> |

| Direct Link<br>Interconnect |                                                           | <b>✓</b>           |                          |                 |                  |                 |                  |          |               |                     |     |            |          |

| R4<br>Interconnect          |                                                           | <b>✓</b>           |                          | <b>✓</b>        | <b>✓</b>         | ~               | <b>✓</b>         |          |               |                     |     |            |          |

| R24<br>Interconnect         |                                                           |                    |                          | <b>✓</b>        | <b>✓</b>         | ~               | <b>✓</b>         |          |               |                     |     |            |          |

| C4<br>Interconnect          |                                                           | <b>✓</b>           |                          | <b>✓</b>        | <b>✓</b>         | ~               | <b>✓</b>         |          |               |                     |     |            |          |

| C16<br>Interconnect         |                                                           |                    |                          | <b>✓</b>        | ✓                | <b>✓</b>        | <b>✓</b>         |          |               |                     |     |            |          |

#### Global Clock Network

The 16 or 8 global clock networks drive throughout the entire device. Dedicated clock pins (CLK[]), PLL outputs, the logic array, and dual-purpose clock (DPCLK[]) pins can also drive the global clock network.

The global clock network can provide clocks for all resources within the device, such as IOEs, LEs, memory blocks, and embedded multipliers. The global clock lines can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin, or DQS signals for DDR SDRAM or QDRII SRAM interfaces. Internal logic can also drive the global clock network for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fan-out.

#### Clock Control Block

There is a clock control block for each global clock network available in Cyclone II devices. The clock control blocks are arranged on the device periphery and there are a maximum of 16 clock control blocks available per Cyclone II device. The larger Cyclone II devices (EP2C15 devices and larger) have 16 clock control blocks, four on each side of the device. The smaller Cyclone II devices (EP2C5 and EP2C8 devices) have eight clock control blocks, four on the left and right sides of the device.

The control block has these functions:

- Dynamic global clock network clock source selection

- Dynamic enable/disable of the global clock network

In Cyclone II devices, the dedicated CLK[] pins, PLL counter outputs, DPCLK[] pins, and internal logic can all feed the clock control block. The output from the clock control block in turn feeds the corresponding global clock network.

The following sources can be inputs to a given clock control block:

- Four clock pins on the same side as the clock control block

- Three PLL clock outputs from a PLL

- Four DPCLK pins (including CDPCLK pins) on the same side as the clock control block

- Four internally-generated signals

#### **Clock Modes**

Table 2–8 summarizes the different clock modes supported by the M4K memory.

| Table 2–8. M4K Clock Modes |                                                                                                                                                                                                 |  |  |  |  |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Clock Mode                 | Description                                                                                                                                                                                     |  |  |  |  |  |  |

| Independent                | In this mode, a separate clock is available for each port (ports A and B). Clock A controls all registers on the port A side, while clock B controls all registers on the port B side.          |  |  |  |  |  |  |

| Input/output               | On each of the two ports, A or B, one clock controls all registers for inputs into the memory block: data input, wren, and address. The other clock controls the block's data output registers. |  |  |  |  |  |  |

| Read/write                 | Up to two clocks are available in this mode. The write clock controls the block's data inputs, wraddress, and wren. The read clock controls the data output, rdaddress, and rden.               |  |  |  |  |  |  |

| Single                     | In this mode, a single clock, together with clock enable, is used to control all registers of the memory block. Asynchronous clear signals for the registers are not supported.                 |  |  |  |  |  |  |

Table 2–9 shows which clock modes are supported by all M4K blocks when configured in the different memory modes.

| Table 2–9. Cyclone II M4K Memory Clock Modes |                        |                          |                  |  |  |  |  |  |

|----------------------------------------------|------------------------|--------------------------|------------------|--|--|--|--|--|

| Clocking Modes                               | True Dual-Port<br>Mode | Simple Dual-Port<br>Mode | Single-Port Mode |  |  |  |  |  |

| Independent                                  | <b>✓</b>               |                          |                  |  |  |  |  |  |

| Input/output                                 | <b>✓</b>               | ✓                        | <b>✓</b>         |  |  |  |  |  |

| Read/write                                   |                        | ✓                        |                  |  |  |  |  |  |

| Single clock                                 | <b>✓</b>               | <b>✓</b>                 | <b>✓</b>         |  |  |  |  |  |

## **M4K Routing Interface**

The R4, C4, and direct link interconnects from adjacent LABs drive the M4K block local interconnect. The M4K blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 16 direct link input connections to the M4K block are possible from the left adjacent LAB and another 16 possible from the right adjacent LAB. M4K block outputs can also connect to left and right LABs through each 16 direct link interconnects. Figure 2–17 shows the M4K block to logic array interface.

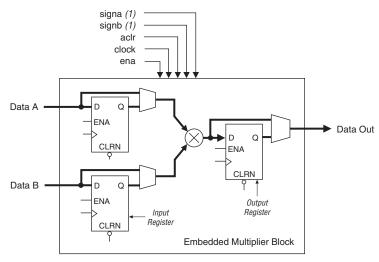

Figure 2-18. Multiplier Block Architecture

Note to Figure 2–18:

(1) If necessary, these signals can be registered once to match the data signal path.

Each multiplier operand can be a unique signed or unsigned number. Two signals, signa and signb, control the representation of each operand respectively. A logic 1 value on the signa signal indicates that data A is a signed number while a logic 0 value indicates an unsigned number. Table 2–11 shows the sign of the multiplication result for the various operand sign representations. The result of the multiplication is signed if any one of the operands is a signed value.

| Table 2–11. Multiplier Sign Representation |                      |          |  |  |  |  |  |

|--------------------------------------------|----------------------|----------|--|--|--|--|--|

| Data A (signa Value)                       | Data B (signb Value) | Result   |  |  |  |  |  |

| Unsigned                                   | Unsigned             | Unsigned |  |  |  |  |  |

| Unsigned                                   | Signed               | Signed   |  |  |  |  |  |

| Signed                                     | Unsigned             | Signed   |  |  |  |  |  |

| Signed                                     | Signed               | Signed   |  |  |  |  |  |

There are five dynamic control input signals that feed the embedded multiplier: signa, signb, clk, clkena, and aclr. signa and signb can be registered to match the data signal input path. The same clk, clkena, and aclr signals feed all registers within a single embedded multiplier.

For more information on Cyclone II embedded multipliers, see the *Embedded Multipliers in Cyclone II Devices* chapter.

# I/O Structure & Features

IOEs support many features, including:

- Differential and single-ended I/O standards

- 3.3-V, 64- and 32-bit, 66- and 33-MHz PCI compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- Output drive strength control

- Weak pull-up resistors during configuration

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors in user mode

- Programmable input and output delays

- Open-drain outputs

- DQ and DQS I/O pins

- V<sub>REF</sub> pins

Cyclone II device IOEs contain a bidirectional I/O buffer and three registers for complete embedded bidirectional single data rate transfer. Figure 2–20 shows the Cyclone II IOE structure. The IOE contains one input register, one output register, and one output enable register. You can use the input registers for fast setup times and output registers for fast clock-to-output times. Additionally, you can use the output enable (OE) register for fast clock-to-output enable timing. The Quartus II software automatically duplicates a single OE register that controls multiple output or bidirectional pins. You can use IOEs as input, output, or bidirectional pins.

**Table 5–6. Recommended Operating Conditions for User I/O Pins Using Single-Ended I/O Standards**Note (1) (Part 2 of 2)

| I/O Standard           | V <sub>CCIO</sub> (V) V <sub>REF</sub> (V) |     |       | V <sub>IL</sub> (V) | V <sub>IH</sub> (V) |       |                                                               |                                                               |

|------------------------|--------------------------------------------|-----|-------|---------------------|---------------------|-------|---------------------------------------------------------------|---------------------------------------------------------------|

| i/O Stallualu          | Min                                        | Тур | Max   | Min                 | Тур                 | Max   | Max                                                           | Min                                                           |

| SSTL-18 class II       | 1.7                                        | 1.8 | 1.9   | 0.833               | 0.9                 | 0.969 | V <sub>REF</sub> - 0.125 (DC)<br>V <sub>REF</sub> - 0.25 (AC) | V <sub>REF</sub> + 0.125 (DC)<br>V <sub>REF</sub> + 0.25 (AC) |

| 1.8-V HSTL<br>class I  | 1.71                                       | 1.8 | 1.89  | 0.85                | 0.9                 | 0.95  | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

| 1.8-V HSTL<br>class II | 1.71                                       | 1.8 | 1.89  | 0.85                | 0.9                 | 0.95  | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

| 1.5-V HSTL<br>class I  | 1.425                                      | 1.5 | 1.575 | 0.71                | 0.75                | 0.79  | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

| 1.5-V HSTL<br>class II | 1.425                                      | 1.5 | 1.575 | 0.71                | 0.75                | 0.79  | V <sub>REF</sub> - 0.1 (DC)<br>V <sub>REF</sub> - 0.2 (AC)    | V <sub>REF</sub> + 0.1 (DC)<br>V <sub>REF</sub> + 0.2 (AC)    |

*Note to Table 5–6:*

<sup>(1)</sup> Nominal values (Nom) are for  $T_A$  = 25° C,  $V_{CCINT}$  = 1.2 V, and  $V_{CCIO}$  = 1.5, 1.8, 2.5, and 3.3 V.

| Table 5–7. DC Characteristics of User I/O Pins Using Single-Ended Standards Notes (1), (2) (Part 1 of 2) |                      |                      |                             |                             |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|----------------------|----------------------|-----------------------------|-----------------------------|--|--|--|--|

| 1/0 0444                                                                                                 | Test Co              | nditions             | Voltage Thresholds          |                             |  |  |  |  |

| I/O Standard                                                                                             | I <sub>OL</sub> (mA) | I <sub>OH</sub> (mA) | Maximum V <sub>OL</sub> (V) | Minimum V <sub>OH</sub> (V) |  |  |  |  |

| 3.3-V LVTTL                                                                                              | 4                    | -4                   | 0.45                        | 2.4                         |  |  |  |  |

| 3.3-V LVCMOS                                                                                             | 0.1                  | -0.1                 | 0.2                         | V <sub>CCIO</sub> - 0.2     |  |  |  |  |

| 2.5-V LVTTL and LVCMOS                                                                                   | 1                    | -1                   | 0.4                         | 2.0                         |  |  |  |  |

| 1.8-V LVTTL and LVCMOS                                                                                   | 2                    | -2                   | 0.45                        | V <sub>CCIO</sub> - 0.45    |  |  |  |  |

| 1.5-V LVTTL and LVCMOS                                                                                   | 2                    | -2                   | 0.25 × V <sub>CCIO</sub>    | 0.75 × V <sub>CCIO</sub>    |  |  |  |  |

| PCI and PCI-X                                                                                            | 1.5                  | -0.5                 | 0.1 × V <sub>CCIO</sub>     | 0.9 × V <sub>CCIO</sub>     |  |  |  |  |

| SSTL-2 class I                                                                                           | 8.1                  | -8.1                 | V <sub>TT</sub> – 0.57      | V <sub>TT</sub> + 0.57      |  |  |  |  |

| SSTL-2 class II                                                                                          | 16.4                 | -16.4                | V <sub>TT</sub> – 0.76      | V <sub>TT</sub> + 0.76      |  |  |  |  |

| SSTL-18 class I                                                                                          | 6.7                  | -6.7                 | V <sub>TT</sub> – 0.475     | V <sub>TT</sub> + 0.475     |  |  |  |  |

| SSTL-18 class II                                                                                         | 13.4                 | -13.4                | 0.28                        | V <sub>CCIO</sub> - 0.28    |  |  |  |  |

| 1.8-V HSTL class I                                                                                       | 8                    | -8                   | 0.4                         | V <sub>CCIO</sub> - 0.4     |  |  |  |  |

| 1.8-V HSTL class II                                                                                      | 16                   | -16                  | 0.4                         | V <sub>CCIO</sub> - 0.4     |  |  |  |  |

| Table 5-37                       | Table 5–37. Cyclone II IOE Programmable Delay on Row Pins Notes (1), (2) (Part 2 of 2) |                 |               |                   |               |                       |               |                |               |      |    |

|----------------------------------|----------------------------------------------------------------------------------------|-----------------|---------------|-------------------|---------------|-----------------------|---------------|----------------|---------------|------|----|

| Parameter Paths<br>Affected      | Number<br>of<br>Settings                                                               | Fast Corner (3) |               | -6 Speed<br>Grade |               | -7 Speed<br>Grade (4) |               | -8 Speed Grade |               | Unit |    |

|                                  |                                                                                        | Min<br>Offset   | Max<br>Offset | Min<br>Offset     | Max<br>Offset | Min<br>Offset         | Max<br>Offset | Min<br>Offset  | Max<br>Offset | Unit |    |

| Input Delay                      | Pad ->                                                                                 | 8               | 0             | 2669              | 0             | 4482                  | 0             | 4834           | 0             | 4859 | ps |

| from Pin to<br>Input<br>Register | I/O input<br>register                                                                  |                 | 0             | 2802              | _             |                       | 0             | 4671           | _             | _    | ps |

| Delay from                       | I/O                                                                                    | 2               | 0             | 308               | 0             | 572                   | 0             | 648            | 0             | 682  | ps |

| Output Register to Output Pin    | output<br>register -<br>> Pad                                                          |                 | 0             | 324               | _             | _                     | 0             | 626            | _             | _    | ps |

#### Notes to Table 5–37:

- The incremental values for the settings are generally linear. For exact values of each setting, use the latest version

of the Quartus II software.

- (2) The minimum and maximum offset timing numbers are in reference to setting "0" as available in the Quartus II software.

- (3) The value in the first row represents the fast corner timing parameter for industrial and automotive devices. The second row represents the fast corner timing parameter for commercial devices.

- (4) The value in the first row is for automotive devices. The second row is for commercial devices.

## Default Capacitive Loading of Different I/O Standards

Refer to Table 5–38 for default capacitive loading of different I/O standards.

| Table 5–38. Default Loading of Different I/O Standards for Cyclone II Device (Part 1 of 2) |                 |      |  |  |  |  |  |

|--------------------------------------------------------------------------------------------|-----------------|------|--|--|--|--|--|

| I/O Standard                                                                               | Capacitive Load | Unit |  |  |  |  |  |

| LVTTL                                                                                      | 0               | pF   |  |  |  |  |  |

| LVCMOS                                                                                     | 0               | pF   |  |  |  |  |  |

| 2.5V                                                                                       | 0               | pF   |  |  |  |  |  |

| 1.8V                                                                                       | 0               | pF   |  |  |  |  |  |

| 1.5V                                                                                       | 0               | pF   |  |  |  |  |  |

| PCI                                                                                        | 10              | pF   |  |  |  |  |  |

| PCI-X                                                                                      | 10              | pF   |  |  |  |  |  |

| SSTL_2_CLASS_I                                                                             | 0               | pF   |  |  |  |  |  |

| SSTL_2_CLASS_II                                                                            | 0               | pF   |  |  |  |  |  |

| SSTL_18_CLASS_I                                                                            | 0               | pF   |  |  |  |  |  |

| Table 5–42. Cyclone II I/O Output Delay for Column Pins (Part 5 of 6) |          |                  |                           |                 |                |             |             |                |      |

|-----------------------------------------------------------------------|----------|------------------|---------------------------|-----------------|----------------|-------------|-------------|----------------|------|

|                                                                       | Drive    | _                | Fast Corner               |                 |                | -7<br>Speed | -7<br>Speed | -8             |      |

| I/O Standard                                                          | Strength | Parameter        | Industrial/<br>Automotive | Commer<br>-cial | Speed<br>Grade | Grade (2)   | Grade (3)   | Speed<br>Grade | Unit |

| DIFFERENTIAL_                                                         | 6 mA     | t <sub>OP</sub>  | 1472                      | 1544            | 3140           | 3345        | 3542        | 3549           | ps   |

| SSTL_18_CLASS_I                                                       |          | t <sub>DIP</sub> | 1604                      | 1683            | 3310           | 3539        | 3768        | 3768           | ps   |

|                                                                       | 8 mA     | t <sub>OP</sub>  | 1469                      | 1541            | 3086           | 3287        | 3482        | 3489           | ps   |

|                                                                       |          | t <sub>DIP</sub> | 1601                      | 1680            | 3256           | 3481        | 3708        | 3708           | ps   |

|                                                                       | 10 mA    | t <sub>OP</sub>  | 1466                      | 1538            | 2980           | 3171        | 3354        | 3361           | ps   |

|                                                                       |          | t <sub>DIP</sub> | 1598                      | 1677            | 3150           | 3365        | 3580        | 3580           | ps   |

|                                                                       | 12 mA    | t <sub>OP</sub>  | 1466                      | 1538            | 2980           | 3171        | 3354        | 3361           | ps   |

|                                                                       | (1)      | t <sub>DIP</sub> | 1598                      | 1677            | 3150           | 3365        | 3580        | 3580           | ps   |

| DIFFERENTIAL_                                                         | 16 mA    | t <sub>OP</sub>  | 1454                      | 1525            | 2905           | 3088        | 3263        | 3270           | ps   |

| SSTL_18_CLASS_II                                                      |          | t <sub>DIP</sub> | 1586                      | 1664            | 3075           | 3282        | 3489        | 3489           | ps   |

|                                                                       | 18 mA    | t <sub>OP</sub>  | 1453                      | 1524            | 2900           | 3082        | 3257        | 3264           | ps   |

|                                                                       | (1)      | t <sub>DIP</sub> | 1585                      | 1663            | 3070           | 3276        | 3483        | 3483           | ps   |

| 1.8V_DIFFERENTIAL                                                     | 8 mA     | t <sub>OP</sub>  | 1460                      | 1531            | 3222           | 3424        | 3618        | 3625           | ps   |

| _HSTL_CLASS_I                                                         |          | t <sub>DIP</sub> | 1592                      | 1670            | 3392           | 3618        | 3844        | 3844           | ps   |

|                                                                       | 10 mA    | t <sub>OP</sub>  | 1462                      | 1534            | 3090           | 3279        | 3462        | 3469           | ps   |

|                                                                       |          | t <sub>DIP</sub> | 1594                      | 1673            | 3260           | 3473        | 3688        | 3688           | ps   |

|                                                                       | 12 mA    | t <sub>OP</sub>  | 1462                      | 1534            | 3090           | 3279        | 3462        | 3469           | ps   |

|                                                                       | (1)      | t <sub>DIP</sub> | 1594                      | 1673            | 3260           | 3473        | 3688        | 3688           | ps   |

| 1.8V_DIFFERENTIAL                                                     | 16 mA    | t <sub>OP</sub>  | 1449                      | 1520            | 2936           | 3107        | 3271        | 3278           | ps   |

| _HSTL_CLASS_II                                                        |          | t <sub>DIP</sub> | 1581                      | 1659            | 3106           | 3301        | 3497        | 3497           | ps   |

|                                                                       | 18 mA    | t <sub>OP</sub>  | 1450                      | 1521            | 2924           | 3101        | 3272        | 3279           | ps   |

|                                                                       |          | t <sub>DIP</sub> | 1582                      | 1660            | 3094           | 3295        | 3498        | 3498           | ps   |

|                                                                       | 20 mA    | t <sub>OP</sub>  | 1452                      | 1523            | 2926           | 3096        | 3259        | 3266           | ps   |

|                                                                       | (1)      | t <sub>DIP</sub> | 1584                      | 1662            | 3096           | 3290        | 3485        | 3485           | ps   |

| 1.5V_DIFFERENTIAL                                                     | 8 mA     | t <sub>OP</sub>  | 1779                      | 1866            | 4292           | 4637        | 4974        | 4981           | ps   |

| _HSTL_CLASS_I                                                         |          | t <sub>DIP</sub> | 1911                      | 2005            | 4462           | 4831        | 5200        | 5200           | ps   |

|                                                                       | 10 mA    | t <sub>OP</sub>  | 1784                      | 1872            | 4031           | 4355        | 4673        | 4680           | ps   |

|                                                                       |          | t <sub>DIP</sub> | 1916                      | 2011            | 4201           | 4549        | 4899        | 4899           | ps   |

|                                                                       | 12 mA    | t <sub>OP</sub>  | 1784                      | 1872            | 4031           | 4355        | 4673        | 4680           | ps   |

|                                                                       | (1)      | t <sub>DIP</sub> | 1916                      | 2011            | 4201           | 4549        | 4899        | 4899           | ps   |

Each output port has a unique post-scale counter to divide down the high-frequency VCO. There are three post-scale counters (c0, c1, and c2), which range from 1 to 32. The following equations show the frequencies for the three post-scale counters:

$$f_{C0} = \frac{f_{VCO}}{C0} = f_{IN} \frac{m}{n \times C0}$$

$$f_{C1} = \frac{f_{VCO}}{C1} = f_{IN} \frac{m}{n \times C1}$$

$$f_{C2} = \frac{f_{VCO}}{C2} = f_{IN} \frac{m}{n \times C2}$$

All three output counters can drive the global clock network. The c2 output counter can also drive a dedicated external I/O pin (single ended or differential). This counter output can drive a dedicated external clock output pin (PLL<#>\_OUT) and the global clock network at the same time.

For multiple PLL outputs with different frequencies, the VCO is set to the least common multiple of the output frequencies that meets the VCO frequency specifications. Then, the post-scale counters scale down the VCO frequency for each PLL clock output port. For example, if clock output frequencies required from one PLL are 33 and 66 MHz, the VCO is set to 330 MHz (the least common multiple in the VCO's range).

## **Programmable Duty Cycle**

The programmable duty cycle feature allows you to set the PLL clock output duty cycles. The duty cycle is the ratio of the clock output high and low time to the total clock cycle time, expressed as a percentage of high time. This feature is supported on all three PLL post-scale counters, c0, c1, and c2, and when using all clock feedback modes.

The duty cycle is set by using a low- and high-time count setting for the post-scale counters. The Quartus II software uses the input frequency and target multiply/divide ratio to select the post-scale counter. The granularity of the duty cycle is determined by the post-scale counter value chosen on a PLL clock output and is defined as  $50\% \div \text{post-scale}$  counter value. For example, if the post-scale counter value is 3, then the allowable duty cycle precision would be  $50\% \div 3 = 16.67\%$ . Because the altpl1 megafunction does not accept non-integer values for the duty cycle values, the allowable duty cycles are 17% 33% 50% and 67%. For example, if the c0 counter is 10, then steps of 5% are possible for duty cycle choices between 5 to 90%.

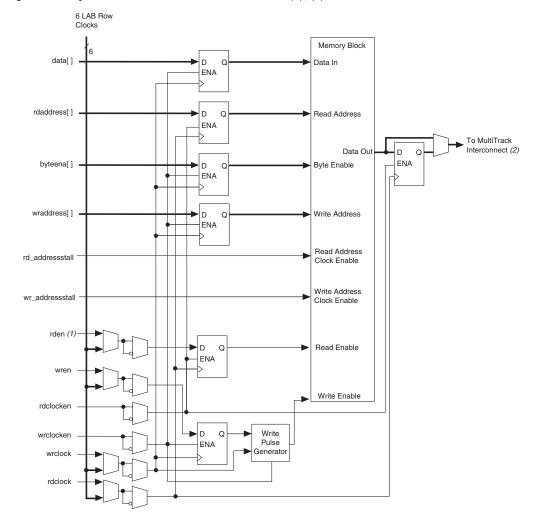

Figure 8–17. Cyclone II Read/Write Clock Mode Notes (1), (2)

#### Notes to Figure 8–17:

- (1) Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

- (2) For more information about the MultiTract interconnect, refer to Cyclone II Device Family Data Sheet in volume 1 of the Cyclone II Device Handbook.

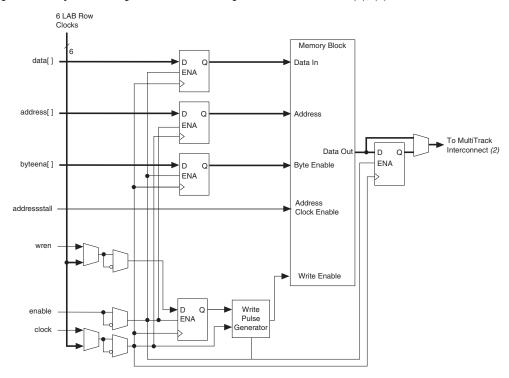

Figure 8–20. Cyclone II Single-Clock Mode in Single-Port Mode Notes (1), (2)

Notes to Figure 8-20:

- (1) Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

- (2) See the Cyclone II Device Family Data Sheet in Volume 1 of the Cyclone II Device Handbook for more information on the MultiTrack interconnect.

## **Power-Up Conditions & Memory Initialization**

The Cyclone II memory block outputs always power-up to zero, regardless of whether the output registers are used or bypassed. Even if an MIF pre-loads the contents of the memory block, the outputs still power up cleared. For example, if address 0 is pre-initialized to FF, M4K blocks power up with the output at 00. A subsequent read after power up from address 0 outputs the pre-initialized value of FF.

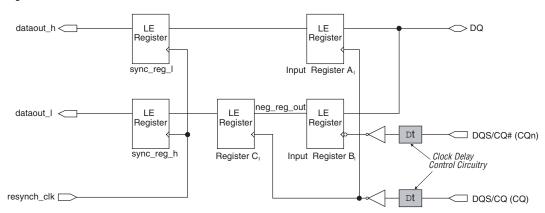

Figure 9-4. CQ & CQn Connection for QDRII SRAM Read

#### Read & Write Operation

Figure 9–5 shows the data and clock relationships in QDRII SRAM devices at the memory pins during reads. QDRII SRAM devices send data within  $t_{CO}$  time after each rising edge of the read clock C or C# in multiclock mode or the input clock K or K# in single clock mode. Data is valid until  $t_{\rm DOH}$  time after each rising edge of the read clock C or C# in multiclock mode or the input clock K or K# in single clock mode. The CQ and CQn clocks are edge-aligned with the read data signal. These clocks accompany the read data for data capture in Cyclone II devices.

For example, to implement a 72-bit wide SDRAM memory interface in Cyclone II devices, use 5 DQS/DQ groups in the top I/O bank and 4 DQS/DQ groups in the bottom I/O bank, or vice-versa. In this case, if DQS0T or DQS1T is used for the fifth DQS signal, the DQS2R or DQS2L pins become regular I/O pins and are unavailable for DQS signals in memory interface. For detailed information about the global clock network, refer to the Global Clock Network & Phase Locked Loops section in the Cyclone II Architecture chapter of the Cyclone II Device Handbook.

You must configure the DQ and DQS pins as bidirectional DDR pins on all the I/O banks of the device. Use the altdq and altdqs megafunctions to configure the DQ and DQS paths, respectively. If you only want to use the DQ or DQS pins as inputs, for instance in the QDRII memory interface where DQ and DQS are unidirectional read data and read clock, set the output enable of the DQ or DQS pins to ground. For further information, please refer to the section "QDRII SRAM" on page 9–5 of this handbook.

## Clock, Command & Address Pins

You can use any of the user I/O pins on all the I/O banks (that support the external memory's I/O standard) of the device to generate clocks and command and address signals to the memory device.

## Parity, DM & ECC Pins

You can use any of the DQ pins for the parity pins in Cyclone II devices. Cyclone II devices support parity in the  $\times 8/\times 9$  and  $\times 16/\times 18$  modes. There is one parity bit available per 8 bits of data pins.

The data mask (DM) pins are required when writing to DDR SDRAM and DDR2 SDRAM devices. A low signal on the DM pin indicates that the write is valid. If the DM signal is high, the memory masks the DQ signals. In Cyclone II devices, the DM pins are pre-assigned in the device pin outs, and these are the preferred pins. Each group of DQS and DQ signals requires a DM pin. Similar to the DQ output signals, the DM signals are clocked by the  $-90^{\circ}$  shifted clock.

Some DDR SDRAM and DDR2 SDRAM devices support error correction coding (ECC) or parity. Parity bit checking is a way to detect errors, but it has no correction capabilities. ECC can detect and automatically correct errors in data transmission. In 72-bit DDR SDRAM, there are 8 ECC pins on top of the 64 data pins. Connect the DDR and DDR2 SDRAM ECC pins to a Cyclone II device's DQS/DQ group. The memory controller needs extra logic to encode and decode the ECC data.

### 1.8-V LVCMOS (EIA/JEDEC Standard EIA/JESD8-7)

The 1.8-V I/O standard is used for 1.8-V LVCMOS applications. This standard defines the DC interface parameters for high-speed, low-voltage, non-terminated digital circuits driving or being driven by other 1.8-V parts.

The 1.8-V standard does not require input reference voltages or board terminations. Cyclone II devices support input and output levels for 1.8-V LVCMOS.

#### SSTL-18 Class I and II

The 1.8-V SSTL-18 standard is formulated under JEDEC Standard, JESD815: Stub Series Terminated Logic for 1.8V (SSTL-18).

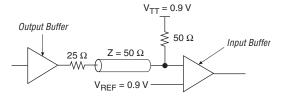

The SSTL-18 I/O standard is a 1.8-V memory bus standard used for applications such as high-speed DDR2 SDRAM interfaces. This standard is similar to SSTL-2 and defines input and output specifications for devices that are designed to operate in the SSTL-18 logic switching range 0.0 to 1.8 V. SSTL-18 requires a 0.9-V  $\rm V_{REF}$  and a 0.9-V  $\rm V_{TT}$ , with the termination resistors connected to both. There are no class definitions for the SSTL-18 standard in the JEDEC specification. The specification of this I/O standard is based on an environment that consists of both series and parallel terminating resistors. Altera provides solutions to two derived applications in JEDEC specification and names them class I and class II to be consistent with other SSTL standards. Figures 10–5 and 10–6 show SSTL-18 class I and II termination, respectively. Cyclone II devices support both input and output levels.

Figure 10-5. 1.8-V SSTL Class I Termination

| November 2005<br>v2.1 | <ul> <li>Updated Tables 10–2 and 10–3.</li> <li>Added PCI Express information.</li> <li>Updated Table 10–6.</li> </ul> | _ |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|---|

| July 2005 v2.0        | Updated Table 10-1.                                                                                                    | _ |

| November 2004<br>v1.1 | Updated Table 10-7.                                                                                                    | _ |

| June 2004 v1.0        | Added document to the Cyclone II Device Handbook.                                                                      | _ |

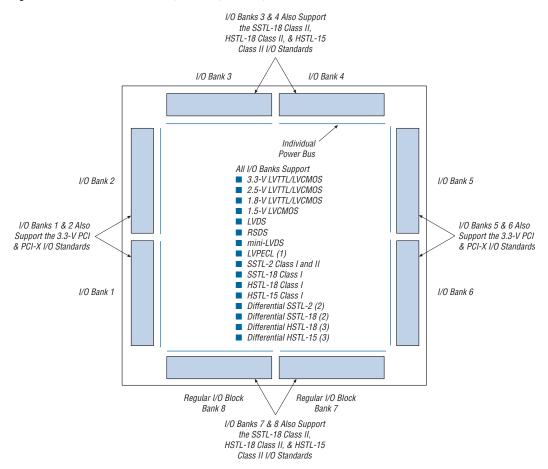

Figure 11–2. I/O Banks in EP2C15, EP2C20, EP2C35, EP2C50 & EP2C70 Devices

#### Notes to Figure 11-2:

- The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (2) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (3) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

## Cyclone II High-Speed I/O Interface

Cyclone II devices provide a multi-protocol interface that allows communication between a variety of I/O standards, including LVDS, LVPECL, RSDS, mini-LVDS, differential HSTL, and differential SSTL. This feature makes the Cyclone II device family ideal for applications that require multiple I/O standards, such as protocol translation.

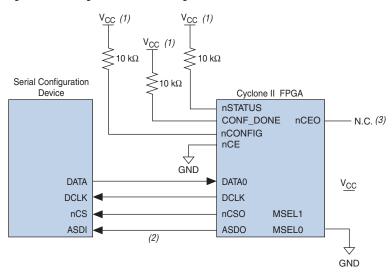

Figure 13–3. Single Device AS Configuration

#### Notes to Figure 13-3:

- (1) Connect the pull-up resistors to a 3.3-V supply.

- (2) Cyclone II devices use the ASDO to ASDI path to control the configuration device.

- (3) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed another device's nCE pin.

Upon power-up, the Cyclone II device goes through a POR. During POR, the device resets, holds <code>nSTATUS</code> and <code>CONF\_DONE</code> low, and tri-states all user I/O pins. After POR, which typically lasts 100 ms, the Cyclone II device releases <code>nSTATUS</code> and enters configuration mode when the external 10-k $\Omega$  resistor pulls the <code>nSTATUS</code> pin high. Once the FPGA successfully exits POR, all user I/O pins continue to be tri-stated. Cyclone II devices have weak pull-up resistors on the user I/O pins which are on before and during configuration.

The value of the weak pull-up resistors on the I/O pins that are on before and during configuration are available in the *DC Characteristics & Timing Specifications* chapter of the *Cyclone II Device Handbook*.

The configuration cycle consists of the reset, configuration, and initialization stages.

| Table 13–11. | Table 13–11. Dedicated Configuration Pins on the Cyclone II Device (Part 3 of 5) |                         |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------|-------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name     | User<br>Mode                                                                     | Configuration<br>Scheme | Pin Type                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| CONF_DONE    | N/A                                                                              | All                     | Bidirectional open-drain | This pin is a status output and input. The target Cyclone II device drives the <code>CONF_DONE</code> pin low before and during configuration. Once the Cyclone II device receives all the configuration data without error and the initialization cycle starts, it releases <code>CONF_DONE</code> . Driving <code>CONF_DONE</code> low during user mode does not affect the configured device. Do not drive <code>CONF_DONE</code> low before the device enters user mode.  After the Cyclone II device receives all the data, the <code>CONF_DONE</code> pin transitions high, and the device initializes and enters user mode. The <code>CONF_DONE</code> pin must have an external 10-k $\Omega$ pull-up resistor in order for the device to initialize.  Driving <code>CONF_DONE</code> low after configuration and initialization does not affect the configured device.  The enhanced configuration devices' and <code>EPC2</code> devices' <code>OE</code> and <code>nCS</code> pins are connected to the Cyclone II device's <code>nstatus</code> and <code>CONF_DONE</code> pins, respectively, and have optional internal programmable pull-up resistors. If internal pull-up resistors on the enhanced configuration device are used, external 10-k $\Omega$ pull-up resistors should not be used on these pins. When using <code>EPC2</code> devices, you should only use external 10-k $\Omega$ pull-up resistors.  The input buffer on this pin supports hysteresis using <code>Schmitt</code> trigger circuitry. |  |  |  |  |  |

| nCE          | N/A                                                                              | All                     | Input                    | This pin is an active-low chip enable. The nCE pin activates the device with a low signal to allow configuration. The nCE pin must be held low during configuration, initialization, and user mode. In single device configuration, it should be tied low. In multiple device configuration, nCE of the first device is tied low while its nCEO pin is connected to nCE of the next device in the chain.  The nCE pin must also be held low for successful JTAG programming of the FPGA.  The input buffer on this pin supports hysteresis using Schmitt trigger circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

Section VII-2 Altera Corporation