Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                        |

|--------------------------------|--------------------------------------------------------|

| Product Status                 | Active                                                 |

| Number of LABs/CLBs            | 516                                                    |

| Number of Logic Elements/Cells | 8256                                                   |

| Total RAM Bits                 | 165888                                                 |

| Number of I/O                  | 182                                                    |

| Number of Gates                | -                                                      |

| Voltage - Supply               | 1.15V ~ 1.25V                                          |

| Mounting Type                  | Surface Mount                                          |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                        |

| Package / Case                 | 256-LBGA                                               |

| Supplier Device Package        | 256-FBGA (17x17)                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c8f256c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Introduction

CII51001-3.2

# Introduction

Following the immensely successful first-generation Cyclone® device family, Altera® Cyclone II FPGAs extend the low-cost FPGA density range to 68,416 logic elements (LEs) and provide up to 622 usable I/O pins and up to 1.1 Mbits of embedded memory. Cyclone II FPGAs are manufactured on 300-mm wafers using TSMC's 90-nm low-k dielectric process to ensure rapid availability and low cost. By minimizing silicon area, Cyclone II devices can support complex digital systems on a single chip at a cost that rivals that of ASICs. Unlike other FPGA vendors who compromise power consumption and performance for low-cost, Altera's latest generation of low-cost FPGAs—Cyclone II FPGAs, offer 60% higher performance and half the power consumption of competing 90-nm FPGAs. The low cost and optimized feature set of Cyclone II FPGAs make them ideal solutions for a wide array of automotive, consumer, communications, video processing, test and measurement, and other end-market solutions. Reference designs, system diagrams, and IP, found at www.altera.com, are available to help you rapidly develop complete end-market solutions using Cyclone II FPGAs.

# **Low-Cost Embedded Processing Solutions**

Cyclone II devices support the Nios II embedded processor which allows you to implement custom-fit embedded processing solutions. Cyclone II devices can also expand the peripheral set, memory, I/O, or performance of embedded processors. Single or multiple Nios II embedded processors can be designed into a Cyclone II device to provide additional co-processing power or even replace existing embedded processors in your system. Using Cyclone II and Nios II together allow for low-cost, high-performance embedded processing solutions, which allow you to extend your product's life cycle and improve time to market over standard product solutions.

#### **Low-Cost DSP Solutions**

Use Cyclone II FPGAs alone or as DSP co-processors to improve price-to-performance ratios for digital signal processing (DSP) applications. You can implement high-performance yet low-cost DSP systems with the following Cyclone II features and design support:

- Up to  $150 18 \times 18$  multipliers

- Up to 1.1 Mbit of on-chip embedded memory

- High-speed interfaces to external memory

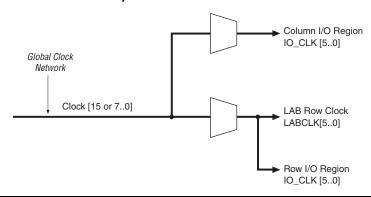

#### **Global Clock Network Distribution**

Cyclone II devices contains 16 global clock networks. The device uses multiplexers with these clocks to form six-bit buses to drive column IOE clocks, LAB row clocks, or row IOE clocks (see Figure 2–14). Another multiplexer at the LAB level selects two of the six LAB row clocks to feed the LE registers within the LAB.

Figure 2-14. Global Clock Network Multiplexers

LAB row clocks can feed LEs, M4K memory blocks, and embedded multipliers. The LAB row clocks also extend to the row I/O clock regions.

IOE clocks are associated with row or column block regions. Only six global clock resources feed to these row and column regions. Figure 2–15 shows the I/O clock regions.

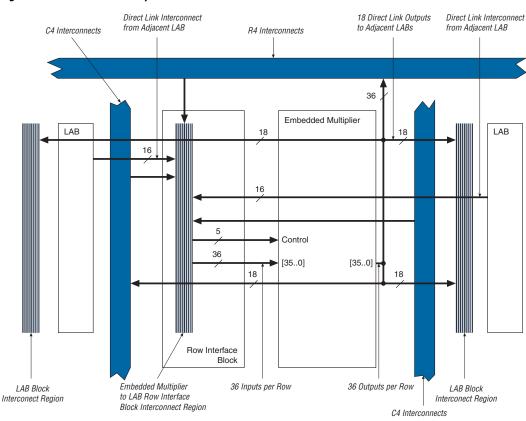

### **Embedded Multiplier Routing Interface**

The R4, C4, and direct link interconnects from adjacent LABs drive the embedded multiplier row interface interconnect. The embedded multipliers can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 16 direct link input connections to the embedded multiplier are possible from the left adjacent LABs and another 16 possible from the right adjacent LAB. Embedded multiplier outputs can also connect to left and right LABs through 18 direct link interconnects each. Figure 2–19 shows the embedded multiplier to logic array interface.

Figure 2-19. Embedded Multiplier LAB Row Interface

standards (e.g., SSTL-2) independently. If an I/O bank does not use voltage-referenced standards, the  $\mbox{VREF}$  pins are available as user I/O pins.

Each I/O bank can support multiple standards with the same  $V_{\rm CCIO}$  for input and output pins. For example, when  $V_{\rm CCIO}$  is 3.3-V, a bank can support LVTTL, LVCMOS, and 3.3-V PCI for inputs and outputs. Voltage-referenced standards can be supported in an I/O bank using any number of single-ended or differential standards as long as they use the same  $V_{\rm REF}$  and a compatible  $V_{\rm CCIO}$  value.

#### MultiVolt I/O Interface

The Cyclone II architecture supports the MultiVolt I/O interface feature, which allows Cyclone II devices in all packages to interface with systems of different supply voltages. Cyclone II devices have one set of  $V_{CC}$  pins (VCCINT) that power the internal device logic array and input buffers that use the LVPECL, LVDS, HSTL, or SSTL I/O standards. Cyclone II devices also have four or eight sets of VCC pins (VCCIO) that power the I/O output drivers and input buffers that use the LVTTL, LVCMOS, or PCI I/O standards.

The Cyclone II VCCINT pins must always be connected to a 1.2-V power supply. If the  $V_{\rm CCINT}$  level is 1.2 V, then input pins are 1.5-V, 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-V, 1.8-V, 2.5-V, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (i.e., when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3-V and is compatible with 3.3-V systems. Table 2–20 summarizes Cyclone II MultiVolt I/O support.

| Table 2–20. Cyclone II MultiVolt I/O Support (Part 1 of 2) Note (1) |              |          |              |              |              |              |          |       |

|---------------------------------------------------------------------|--------------|----------|--------------|--------------|--------------|--------------|----------|-------|

| v (v)                                                               |              | Input    | Signal       |              | Output       | Signal       |          |       |

| V <sub>CCIO</sub> (V)                                               | 1.5 V        | 1.8 V    | 2.5 V        | 3.3 V        | 1.5 V        | 1.8 V        | 2.5 V    | 3.3 V |

| 1.5                                                                 | <b>✓</b>     | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) | <b>✓</b>     |              |          |       |

| 1.8                                                                 | <b>√</b> (4) | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (3) | <b>✓</b>     |          |       |

| 2.5                                                                 |              |          | ~            | <b>✓</b>     | <b>√</b> (5) | <b>√</b> (5) | <b>✓</b> |       |

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| Table 5–14. Cyclone II Device Timing Model Status |                       |             |       |  |  |  |

|---------------------------------------------------|-----------------------|-------------|-------|--|--|--|

| Device                                            | Speed Grade           | Preliminary | Final |  |  |  |

| EP2C5/A                                           | Commercial/Industrial | _           | ✓     |  |  |  |

|                                                   | Automotive            | ✓           | _     |  |  |  |

| EP2C8/A                                           | Commercial/Industrial | _           | ✓     |  |  |  |

|                                                   | Automotive            | ✓           | _     |  |  |  |

| EP2C15A                                           | Commercial/Industrial | _           | ✓     |  |  |  |

|                                                   | Automotive            | ✓           | _     |  |  |  |

| EP2C20/A                                          | Commercial/Industrial | _           | ✓     |  |  |  |

|                                                   | Automotive            | ✓           | _     |  |  |  |

| EP2C35                                            | Commercial/Industrial | _           | ✓     |  |  |  |

| EP2C50                                            | Commercial/Industrial | _           | ✓     |  |  |  |

| EP2C70                                            | Commercial/Industrial | _           | ✓     |  |  |  |

# **Performance**

Table 5–15 shows Cyclone II performance for some common designs. All performance values were obtained with Quartus II software compilation of LPM, or MegaCore functions for the FIR and FFT designs.

| Table 5–15. Cyclone II Performance (Part 1 of 4) |                         |     |                         |               |                      |                      |                      |                      |  |

|--------------------------------------------------|-------------------------|-----|-------------------------|---------------|----------------------|----------------------|----------------------|----------------------|--|

| Applications                                     |                         | R   | esources L              | Jsed          | Performance (MHz)    |                      |                      |                      |  |

|                                                  |                         | LEs | M4K<br>Memory<br>Blocks | DSP<br>Blocks | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade |  |

| LE                                               | 16-to-1 multiplexer (1) | 21  | 0                       | 0             | 385.35               | 313.97               | 270.85               | 286.04               |  |

|                                                  | 32-to-1 multiplexer (1) | 38  | 0                       | 0             | 294.2                | 260.75               | 228.78               | 191.02               |  |

|                                                  | 16-bit counter          | 16  | 0                       | 0             | 401.6                | 349.4                | 310.65               | 310.65               |  |

|                                                  | 64-bit counter          | 64  | 0                       | 0             | 157.15               | 137.98               | 126.08               | 126.27               |  |

| Table 5-37                       | Table 5–37. Cyclone II IOE Programmable Delay on Row Pins Notes (1), (2) (Part 2 of 2) |              |                 |               |                   |               |                              |               |                |               |      |

|----------------------------------|----------------------------------------------------------------------------------------|--------------|-----------------|---------------|-------------------|---------------|------------------------------|---------------|----------------|---------------|------|

| Donomoton                        | Paths                                                                                  | Number<br>of | Fast Corner (3) |               | –6 Speed<br>Grade |               | -7 Speed<br>Grade <i>(4)</i> |               | -8 Speed Grade |               | Unit |

| Parameter                        | Affected                                                                               | Settings     | Min<br>Offset   | Max<br>Offset | Min<br>Offset     | Max<br>Offset | Min<br>Offset                | Max<br>Offset | Min<br>Offset  | Max<br>Offset | UIII |

| Input Delay                      | Pad ->                                                                                 | 8            | 0               | 2669          | 0                 | 4482          | 0                            | 4834          | 0              | 4859          | ps   |

| from Pin to<br>Input<br>Register | I/O input<br>register                                                                  |              | 0               | 2802          | _                 |               | 0                            | 4671          | _              | _             | ps   |

| Delay from                       | I/O                                                                                    | 2            | 0               | 308           | 0                 | 572           | 0                            | 648           | 0              | 682           | ps   |

| Output Register to Output Pin    | output<br>register -<br>> Pad                                                          |              | 0               | 324           | _                 |               | 0                            | 626           | _              | _             | ps   |

#### Notes to Table 5–37:

- The incremental values for the settings are generally linear. For exact values of each setting, use the latest version

of the Quartus II software.

- (2) The minimum and maximum offset timing numbers are in reference to setting "0" as available in the Quartus II software.

- (3) The value in the first row represents the fast corner timing parameter for industrial and automotive devices. The second row represents the fast corner timing parameter for commercial devices.

- (4) The value in the first row is for automotive devices. The second row is for commercial devices.

# Default Capacitive Loading of Different I/O Standards

Refer to Table 5–38 for default capacitive loading of different I/O standards.

| Table 5–38. Default Loading of Different I/O Standards for Cyclone II Device<br>(Part 1 of 2) |                 |      |  |  |  |

|-----------------------------------------------------------------------------------------------|-----------------|------|--|--|--|

| I/O Standard                                                                                  | Capacitive Load | Unit |  |  |  |

| LVTTL                                                                                         | 0               | pF   |  |  |  |

| LVCMOS                                                                                        | 0               | pF   |  |  |  |

| 2.5V                                                                                          | 0               | pF   |  |  |  |

| 1.8V                                                                                          | 0               | pF   |  |  |  |

| 1.5V                                                                                          | 0               | pF   |  |  |  |

| PCI                                                                                           | 10              | pF   |  |  |  |

| PCI-X                                                                                         | 10              | pF   |  |  |  |

| SSTL_2_CLASS_I                                                                                | 0               | pF   |  |  |  |

| SSTL_2_CLASS_II                                                                               | 0               | pF   |  |  |  |

| SSTL_18_CLASS_I                                                                               | 0               | pF   |  |  |  |

| Table 5–42. Cyclone II I/O Output Delay for Column Pins (Part 2 of 6) |                   |                  |                           |                 |                      |                      |                      |                |      |

|-----------------------------------------------------------------------|-------------------|------------------|---------------------------|-----------------|----------------------|----------------------|----------------------|----------------|------|

|                                                                       |                   |                  | Fast Co                   | rner            | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8             |      |

| I/O Standard                                                          | Drive<br>Strength | Parameter        | Industrial/<br>Automotive | Commer<br>-cial |                      |                      |                      | Speed<br>Grade | Unit |

| 2.5V                                                                  | 4 mA              | t <sub>OP</sub>  | 1208                      | 1267            | 2478                 | 2614                 | 2743                 | 2750           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1340                      | 1406            | 2648                 | 2808                 | 2969                 | 2969           | ps   |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 1190                      | 1248            | 2307                 | 2434                 | 2554                 | 2561           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1322                      | 1387            | 2477                 | 2628                 | 2780                 | 2780           | ps   |

|                                                                       | 12 mA             | t <sub>OP</sub>  | 1154                      | 1210            | 2192                 | 2314                 | 2430                 | 2437           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1286                      | 1349            | 2362                 | 2508                 | 2656                 | 2656           | ps   |

|                                                                       | 16 mA             | t <sub>OP</sub>  | 1140                      | 1195            | 2152                 | 2263                 | 2375                 | 2382           | ps   |

|                                                                       | (1)               | t <sub>DIP</sub> | 1272                      | 1334            | 2322                 | 2457                 | 2601                 | 2601           | ps   |

| 1.8V                                                                  | 2 mA              | t <sub>OP</sub>  | 1682                      | 1765            | 3988                 | 4279                 | 4563                 | 4570           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1814                      | 1904            | 4158                 | 4473                 | 4789                 | 4789           | ps   |

|                                                                       | 4 mA              | t <sub>OP</sub>  | 1567                      | 1644            | 3301                 | 3538                 | 3768                 | 3775           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1699                      | 1783            | 3471                 | 3732                 | 3994                 | 3994           | ps   |

|                                                                       | 6 mA              | t <sub>OP</sub>  | 1475                      | 1547            | 2993                 | 3195                 | 3391                 | 3398           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1607                      | 1686            | 3163                 | 3389                 | 3617                 | 3617           | ps   |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 1451                      | 1522            | 2882                 | 3074                 | 3259                 | 3266           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1583                      | 1661            | 3052                 | 3268                 | 3485                 | 3485           | ps   |

|                                                                       | 10 mA             | t <sub>OP</sub>  | 1438                      | 1508            | 2853                 | 3041                 | 3223                 | 3230           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1570                      | 1647            | 3023                 | 3235                 | 3449                 | 3449           | ps   |

|                                                                       | 12 mA             | t <sub>OP</sub>  | 1438                      | 1508            | 2853                 | 3041                 | 3223                 | 3230           | ps   |

|                                                                       | (1)               | t <sub>DIP</sub> | 1570                      | 1647            | 3023                 | 3235                 | 3449                 | 3449           | ps   |

| 1.5V                                                                  | 2 mA              | t <sub>OP</sub>  | 2083                      | 2186            | 4477                 | 4870                 | 5256                 | 5263           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 2215                      | 2325            | 4647                 | 5064                 | 5482                 | 5482           | ps   |

|                                                                       | 4 mA              | t <sub>OP</sub>  | 1793                      | 1881            | 3649                 | 3965                 | 4274                 | 4281           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1925                      | 2020            | 3819                 | 4159                 | 4500                 | 4500           | ps   |

|                                                                       | 6 mA              | t <sub>OP</sub>  | 1770                      | 1857            | 3527                 | 3823                 | 4112                 | 4119           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 1902                      | 1996            | 3697                 | 4017                 | 4338                 | 4338           | ps   |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 1703                      | 1787            | 3537                 | 3827                 | 4111                 | 4118           | ps   |

|                                                                       | (1)               | t <sub>DIP</sub> | 1835                      | 1926            | 3707                 | 4021                 | 4337                 | 4337           | ps   |

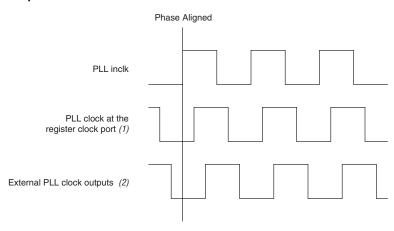

Figure 7–6. Phase Relationship between Cyclone II PLL Clocks in No Compensation Mode

Notes to Figure 7-6:

- (1) Internal clocks fed by the PLL are in phase with each other.

- (2) The external clock outputs can lead or lag the PLL internal clocks.

# Source-Synchronous Mode

If data and clock arrive at the same time at the input pins, they are guaranteed to keep the same phase relationship at the clock and data ports of any IOE input register. Figure 7–7 shows an example waveform of the clock and data in this mode. This mode is recommended for source-synchronous data transfer. Data and clock signals at the IOE experience similar buffer delays as long as the same I/O standard is used.

clock sources and the clkena signals for the global clock network multiplexers can be set through the Quartus II software using the altclkctrl megafunction.

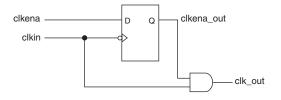

#### clkena signals

In Cyclone II devices, the clkena signals are supported at the clock network level. Figure 7–14 shows how the clkena is implemented. This allows you to gate off the clock even when a PLL is not being used. Upon re-enabling the output clock, the PLL does not need a resynchronization or relock period because the clock is gated off at the clock network level. Also, the PLL can remain locked independent of the clkena signals since the loop-related counters are not affected.

Figure 7-14. clkena Implementation

Figure 7–15 shows the waveform example for a clock output enable. clkena is synchronous to the falling edge of the clock (clkin).

This feature is useful for applications that require a low power or sleep mode. The exact amount of power saved when using this feature is pending device characterization.

# Input/Output Clock Mode

Cyclone II memory blocks can implement the input/output clock mode for true and simple dual-port memory. On each of the two ports, A and B, one clock controls all registers for the data, write enable, and address inputs into the memory block. The other clock controls the blocks' data output registers. Each memory block port also supports independent clock enables for input and output registers. Asynchronous clear signals for the registers are not supported.

Figures 8–14 through 8–16 show the memory block in input/output clock mode for true dual-port, simple dual-port, and single-port modes, respectively.

Figure 9–13 shows waveforms of the circuit shown in Figure 9–11. The first set of waveforms in Figure 9–13 shows the edge-aligned relationship between the DQ and DQS signals at the Cyclone II device pins. The second set of waveforms in Figure 9–13 shows what happens if the shifted DQS signal is not inverted. In this case, the last data,  $Q_{\rm n}$ , does not get latched into the logic array as DQS goes to tri-state after the read postamble time. The third set of waveforms in Figure 9–13 shows a proper read operation with the DQS signal inverted after the 90° shift. The last data,  $Q_{\rm n}$ , does get latched. In this case the outputs of register  $A_{\rm I}$  and register  $C_{\rm I}$ , which correspond to dataout\_h and dataout\_l ports, are now switched because of the DQS inversion. Register  $A_{\rm I}$ , register  $B_{\rm I}$ , and register  $C_{\rm I}$  refer to the nomenclature in Figure 9–11.

Figure 9–13. DQ Captures With Noninverted & Inverted Shifted DQS DQ & DQS Signals  $Q_{\mathsf{n}}$ DQ at the Pin DQS at the Pin Shifted DQS Signal is Not Inverted DQS Shifted by 90° Output of Register AI (dataout\_h) Q<sub>n - 1</sub> Output of Register B<sub>I</sub> Qn - 2 Output of Register C<sub>I</sub> (dataout\_I) Q<sub>n - 2</sub> Shifted DQS Signal is Inverted DQS Inverted and Shifted by 90° Output of Register A Qn - 2 (dataout\_h) Output of Register B<sub>I</sub> Q<sub>n - 1</sub> Output of Register Ci Q<sub>n - 3</sub> Q<sub>n - 1</sub> (dataout I)

9–20 Cyclone II Device Handbook, Volume 1

#### **V**<sub>REF</sub> Pad Placement Guidelines

To maintain an acceptable noise level on the  $V_{CCIO}$  supply and to prevent output switching noise from shifting the  $V_{REF}$  rail, there are restrictions on the placement of single-ended voltage referenced I/Os with respect to  $V_{REF}$  pads and VCCIO and ground pairs. Use the following guidelines for placing single-ended pads in Cyclone II devices.

The Quartus II software automatically does all the calculations in this section.

#### Input Pads

Each  $V_{REF}$  pad supports up to 15 input pads on each side of the  $V_{REF}$  pad for FineLine BGA devices. Each  $V_{REF}$  pad supports up to 10 input pads on each side of the  $V_{REF}$  pad for quad flat pack (QFP) devices. This is irrespective of VCCIO and ground pairs, and is guaranteed by the Cyclone II architecture.

#### Output Pads

When a voltage referenced input or bidirectional pad does not exist in a bank, there is no limit to the number of output pads that can be implemented in that bank. When a voltage referenced input exists, each VCCIO and ground pair supports 9 output pins for Fineline BGA packages (not more than 9 output pins per 12 consecutive row I/O pins) or 5 output pins for QFP packages (not more than 5 output pins per 12 consecutive row I/O pins or 8 consecutive column I/O pins). Any non-SSTL and non-HSTL output can be no closer than two pads away from a  $V_{\rm REF}$  pad. Altera recommends that any SSTL or HSTL output, except for pintable defined DQ and DQS outputs, to be no closer than two pads away from a  $V_{\rm REF}$  pad to maintain acceptable noise levels.

Quartus II software will not check for the SSTL and HSTL output pads placement rule.

Refer to "DDR and QDR Pads" on page 10–32 for details about guidelines for DQ and DQS pads placement.

#### Bidirectional Pads

Bidirectional pads must satisfy input and output guidelines simultaneously.

Refer to "DDR and QDR Pads" on page 10–32 for details about guidelines for DQ and DQS pads placement.

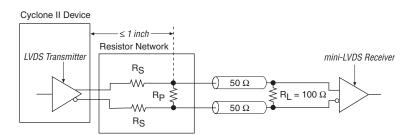

Figure 11-10. mini-LVDS Resistor Network

Note to Figure 11–10:

(1)  $R_S = 120 \Omega \text{ and } R_P = 170 \Omega$

#### mini-LVDS Software Support

When designing for the mini-LVDS I/O standard, assign the mini-LVDS I/O standard to the I/O pins intended for mini-LVDS in the Quartus II software. Contact Altera Applications for reference designs.

#### LVPECL Support in Cyclone II

The LVPECL I/O standard is a differential interface standard requiring a 3.3-V  $\rm V_{\rm CCIO}$  and is used in applications involving video graphics, telecommunications, data communications, and clock distribution. The high-speed, low-voltage swing LVPECL I/O standard uses a positive power supply and is similar to LVDS. However, LVPECL has a larger differential output voltage swing than LVDS. Cyclone II devices support the LVPECL input standard at the clock input pins only. Table 11–4 shows the LVPECL electrical characteristics for Cyclone II devices. Figure 11–11 shows the LVPECL I/O interface.

| Table 11–4. LVPECL Electrical Characteristics for Cyclone II Devices |                            |              |       |     |       |       |  |

|----------------------------------------------------------------------|----------------------------|--------------|-------|-----|-------|-------|--|

| Symbol                                                               | Parameters                 | Condition    | Min   | Тур | Max   | Units |  |

| V <sub>CCIO</sub>                                                    | Output supply voltage      |              | 3.135 | 3.3 | 3.465 | V     |  |

| V <sub>IH</sub>                                                      | Input high voltage         |              | 2,100 |     | 2,880 | mV    |  |

| V <sub>IL</sub>                                                      | Input low voltage          |              | 0     |     | 2,200 | mV    |  |

| V <sub>ID</sub>                                                      | Differential input voltage | Peak to peak | 100   | 600 | 950   | mV    |  |

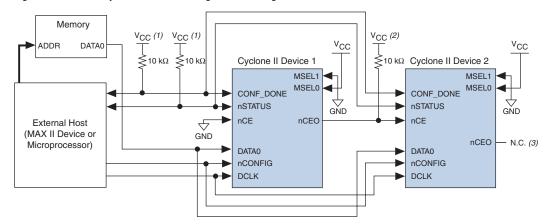

Figure 13–10. Multiple Device PS Configuration Using an External Host

Notes to Figure 13–10:

- (1) The pull-up resistor should be connected to a supply that provides an acceptable input signal for all devices in the chain.  $V_{CC}$  should be high enough to meet the  $V_{IH}$  specification of the I/O on the devices and the external host.

- (2) Connect the pull-up resistor to the V<sub>CCIO</sub> supply voltage of I/O bank that the nCEO pin resides in.

- (3) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed another device's nCE pin.

In multiple device PS configuration, connect the first Cyclone II device's nCE pin to GND and connect the nCEO pin to the nCE pin of the next Cyclone II device in the chain. Use an external 10-k $\Omega$  pull-up resistor to pull the Cyclone II device's nCEO pin high to its V<sub>CCIO</sub> level to help the internal weak pull-up resistor when the nCEO pin feeds next Cyclone II device's nCE pin. The input to the nCE pin of the last Cyclone II device in the chain comes from the previous Cyclone II device. After the first device completes configuration in a multiple device configuration chain, its nCEO pin transitions low to activate the second device's nCE pin, which prompts the second device to begin configuration. The second device in the chain begins configuration within one clock cycle. Therefore, the MAX II device begins to transfer data to the next Cyclone II device without interruption. The nCEO pin is a dual-purpose pin in Cyclone II devices. You can leave the nCEO pin of the last device unconnected or use it as a user I/O pin after configuration if the last device in chain is a Cyclone II device.

The Quartus II software sets the Cyclone II device nCEO pin as a dedicated output by default. If the nCEO pin feeds the next device's nCE pin, you must make sure that the nCEO pin is not used as a user I/O after configuration. This software setting is in the **Dual-Purpose Pins** tab of the **Device & Pin Options** dialog box in Quartus II software.

V<sub>CC</sub> (1) Vcc (1) Enhanced Configuration ≥10 kΩ  $\leq$  10 k $\Omega$ Cyclone II FPGA Device DCLK DATA0 DATA OE (3) nSTATUS CONF\_DONE nCS (3) nINIT\_CONF (2) nCONFIG V<sub>CC</sub> - N.C. (4) nCEO MSFI 0 MSEL1 GND GND

Figure 13–13. Single Device PS Configuration Using an Enhanced Configuration Device

*Notes to Figure 13–13:*

- (1) The pull-up resistor should be connected to the same supply voltage as the configuration device. This pull-up resistor is  $10~k\Omega$

- (2) The ninit\_conf pin is available on enhanced configuration devices and has an internal pull-up resistor that is always active, meaning an external pull-up resistor should not be used on the ninit\_conf to nconfig line. The ninit\_conf pin does not need to be connected if its functionality is not used. If ninit\_conf is not used, nconfig must be pulled to V<sub>CC</sub> either directly or through a resistor (if reconfiguration is required, a resistor is necessary).

- (3) The enhanced configuration devices' OE and nCS pins have internal programmable pull-up resistors. If internal pull-up resistors are used, external pull-up resistors should not be used on these pins. The internal pull-up resistors are used by default in the Quartus II software. To turn off the internal pull-up resistors, check the **Disable nCS and OE pull-ups on configuration device** option when generating programming files.

- (4) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

The value of the internal pull-up resistors on the enhanced configuration devices and EPC2 devices can be found in the *Enhanced Configuration Devices* (EPC4, EPC8, & EPC16) Data Sheet or the Configuration Devices for SRAM-based LUT Devices Data Sheet.

When using enhanced configuration devices or EPC2 devices, you can connect the Cyclone II <code>nconfig</code> pin to the configuration device <code>ninit\_conf</code> pin, which allows the <code>init\_conf</code> JTAG instruction to initiate FPGA configuration. You do not need to connect the <code>ninit\_conf</code> pin if you are not using it. If <code>ninit\_conf</code> is not used or not available (e.g., on EPC1 devices), pull the <code>nconfig</code> signal to  $V_{CC}$  either directly or through a resistor (if reconfiguration is required, a resistor is necessary). An internal pull-up resistor on the <code>ninit\_conf</code> pin is always active in enhanced configuration devices and EPC2 devices. Therefore, you do not need an external pull-up if <code>nconfig</code> is connected to <code>ninit\_conf</code>.

DATA3, you can leave the corresponding bit 3 line blank in the Quartus II software. On the printed circuit board (PCB), leave the DATA3 line from the enhanced configuration device unconnected. Use the Quartus II **Convert Programming Files** window (Tools menu) setup for this scheme.

You can also connect two FPGAs to one of the configuration device's DATA pins while the other DATA pins drive one device each. For example, you could use the 2-bit PS mode to drive two FPGAs with DATA bit 0 (two EP2C5 devices) and the third device (an EP2C8 device) with DATA bit 1. In this example, the memory space required for DATA bit 0 is the sum of the SOF file size for the two EP2C5 devices.

1,223,980 bits + 1,223,980 bits = 2,447,960 bits

The memory space required for DATA bit 1 is the SOF file size for on EP2C8 device (1,983,792 bits). Since the memory space required for DATA bit 0 is larger than the memory space required for DATA bit 1, the size of the POF file is  $2 \times 2,447,960 = 4,895,920$ .

For more information on using *n*-bit PS modes with enhanced configuration devices, see the *Using Altera Enhanced Configuration Devices* in the *Configuration Handbook*.

When configuring SRAM-based devices using n-bit PS modes, use Table 13–8 to select the appropriate configuration mode for the fastest configuration times.

| Table 13–8. Recommended Configuration Using n-Bit PS Modes |                                |  |  |  |  |

|------------------------------------------------------------|--------------------------------|--|--|--|--|

| Number of Devices (1)                                      | Recommended Configuration Mode |  |  |  |  |

| 1                                                          | 1-bit PS                       |  |  |  |  |

| 2                                                          | 2-bit PS                       |  |  |  |  |

| 3                                                          | 4-bit PS                       |  |  |  |  |

| 4                                                          | 4-bit PS                       |  |  |  |  |

| 5                                                          | 8-bit PS                       |  |  |  |  |

| 6                                                          | 8-bit PS                       |  |  |  |  |

| 7                                                          | 8-bit PS                       |  |  |  |  |

| 8                                                          | 8-bit PS                       |  |  |  |  |

Note to Table 13-8:

Assume that each DATA line is only configuring one device, not a daisy chain of devices. feature. To use this feature successfully, set the MSEL[1..0] pins of the master Cyclone II device to select the AS configuration scheme or fast AS configuration scheme (see Table 13–1).

The Quartus II software version 4.1 and higher supports serial configuration device ISP through an FPGA JTAG interface using a JIC file.

The serial configuration device in-system programming through the Cyclone II JTAG interface has three stages, which are described in the following sections.

#### Loading the Serial Flash Loader Design

The serial flash loader design is a design inside the Cyclone II device that bridges the JTAG interface and AS interface inside the Cyclone II device using glue logic.

The intelligent host uses the JTAG interface to configure the master Cyclone II device with a serial flash loader design. The serial flash loader design allows the master Cyclone II device to control the access of four serial configuration device pins, also known as the Active Serial Memory Interface (ASMI) pins, through the JTAG interface. The ASMI pins are the serial clock input (DCLK), serial data output (DATA), AS data input (ASDI), and an active-low chip select (nCS) pins.

If you configure a master Cyclone II device with a serial flash loader design, the master Cyclone II device can enter user mode even though the slave devices in the multiple device chain are not being configured. The master Cyclone II device can enter user mode with a serial flash loader design even though the CONF\_DONE signal is externally held low by the other slave devices in chain. Figure 13–25 shows the JTAG configuration of a single Cyclone II device with a serial flash loader design.

- Perform a SAMPLE/PRELOAD test cycle prior to the first EXTEST test cycle to ensure that known data is present at the device pins when the EXTEST mode is entered. If the OEJ update register contains a 0, the data in the OUTJ update register is driven out. The state must be known and correct to avoid contention with other devices in the system.

- Do not perform EXTEST testing during ICR. This instruction is supported before or after ICR, but not during ICR. Use the CONFIG\_IO instruction to interrupt configuration, then perform testing, or wait for configuration to complete.

- If performing testing before configuration, hold the nCONFIG pin low.

- After configuration, any pins in a differential pin pair cannot be tested. Therefore, performing BST after configuration requires editing BSC group definitions that correspond to these differential pin pairs. The BSC group should be redefined as an internal cell. See the BSDL file for more information on editing.

For more information on boundary scan testing, contact Altera Applications.

# Boundary-Scan Description Language (BSDL) Support

The Boundary-Scan Description Language (BSDL), a subset of VHDL, provides a syntax that allows you to describe the features of an IEEE Std. 1149.1 BST-capable device that can be tested. Test software development systems then use the BSDL files for test generation, analysis, and failure diagnostics. For more information, or to receive BSDL files for IEEE Std. 1149.1-compliant Cyclone II devices, visit the Altera web site at www.altera.com.

# **Conclusion**

The IEEE Std. 1149.1 BST circuitry available in Cyclone II devices provides a cost-effective and efficient way to test systems that contain devices with tight lead spacing. Circuit boards with Altera and other IEEE Std. 1149.1-compliant devices can use the EXTEST, SAMPLE/PRELOAD, BYPASS, IDCODE, USERCODE, CLAMP, and HIGHZ modes to create serial patterns that internally test the pin connections between devices and check device operation.

# References

Bleeker, H., P. van den Eijnden, and F. de Jong. *Boundary-Scan Test: A Practical Approach*. Eindhoven, The Netherlands: Kluwer Academic Publishers, 1993.

Institute of Electrical and Electronics Engineers, Inc. *IEEE Standard Test Access Port and Boundary-Scan Architecture* (IEEE Std 1149.1-2001). New York: Institute of Electrical and Electronics Engineers, Inc., 2001.