Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                        |

|--------------------------------|--------------------------------------------------------|

| Product Status                 | Active                                                 |

| Number of LABs/CLBs            | 516                                                    |

| Number of Logic Elements/Cells | 8256                                                   |

| Total RAM Bits                 | 165888                                                 |

| Number of I/O                  | 182                                                    |

| Number of Gates                | -                                                      |

| Voltage - Supply               | 1.15V ~ 1.25V                                          |

| Mounting Type                  | Surface Mount                                          |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                        |

| Package / Case                 | 256-LBGA                                               |

| Supplier Device Package        | 256-FBGA (17x17)                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c8f256c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

R24 row interconnects span 24 LABs and provide the fastest resource for long row connections between non-adjacent LABs, M4K memory blocks, dedicated multipliers, and row IOEs. R24 row interconnects drive to other row or column interconnects at every fourth LAB. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects and do not drive directly to LAB local interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

### **Column Interconnects**

The column interconnect operates similar to the row interconnect. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs, M4K memory blocks, embedded multipliers, and row and column IOEs. These column resources include:

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four blocks in an up and down direction

- C16 interconnects for high-speed vertical routing through the device

Cyclone II devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using register chain connections. The register chain connection allows the register output of one LE to connect directly to the register input of the next LE in the LAB for fast shift registers. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–9 shows the register chain interconnects.

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, M4K memory blocks, embedded multipliers, and IOEs. C16 column interconnects drive to other row and column interconnects at every fourth LAB. C16 column interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly. C16 interconnects can drive R24, R4, C16, and C4 interconnects.

## **Device Routing**

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (for example, M4K memory, embedded multiplier, or PLL) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB.

Table 2–1 shows the Cyclone II device's routing scheme.

| Table 2–1. Cy               | Table 2–1. Cyclone II Device Routing Scheme (Part 1 of 2) |                    |                          |                 |                  |                 |                  |          |               |                     |          |            |          |

|-----------------------------|-----------------------------------------------------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|----------|---------------|---------------------|----------|------------|----------|

|                             |                                                           | Destination        |                          |                 |                  |                 |                  |          |               |                     |          |            |          |

| Source                      | Register Chain                                            | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | 31       | M4K RAM Block | Embedded Multiplier | PLL      | Column 10E | Row IOE  |

| Register<br>Chain           |                                                           |                    |                          |                 |                  |                 |                  | <b>~</b> |               |                     |          |            |          |

| Local<br>Interconnect       |                                                           |                    |                          |                 |                  |                 |                  | ~        | ~             | ~                   | <b>✓</b> | ~          | <b>✓</b> |

| Direct Link<br>Interconnect |                                                           | ~                  |                          |                 |                  |                 |                  |          |               |                     |          |            |          |

| R4<br>Interconnect          |                                                           | ~                  |                          | <b>✓</b>        | ~                | ~               | <b>✓</b>         |          |               |                     |          |            |          |

| R24<br>Interconnect         |                                                           |                    |                          | <b>✓</b>        | ~                | ~               | <b>✓</b>         |          |               |                     |          |            |          |

| C4<br>Interconnect          |                                                           | ~                  |                          | <b>✓</b>        | ~                | ~               | <b>✓</b>         |          |               |                     |          |            |          |

| C16<br>Interconnect         |                                                           |                    |                          | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>         |          |               |                     |          |            |          |

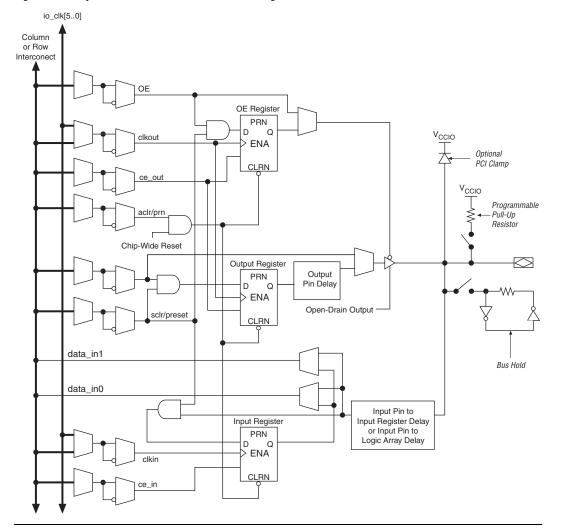

Figure 2–25. Cyclone II IOE in Bidirectional I/O Configuration

The Cyclone II device IOE includes programmable delays to ensure zero hold times, minimize setup times, or increase clock to output times.

A path in which a pin directly drives a register may require a programmable delay to ensure zero hold time, whereas a path in which a pin drives a register through combinational logic may not require the delay. Programmable delays decrease input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time.

## Slew Rate Control

Slew rate control is performed by using programmable output drive strength.

#### **Bus Hold**

Each Cyclone II device user I/O pin provides an optional bus-hold feature. The bus-hold circuitry can hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not necessary to hold a signal level when the bus is tri-stated.

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. You can select this feature individually for each I/O pin. The bus-hold output drives no higher than  $V_{\text{CCIO}}$  to prevent overdriving signals.

If the bus-hold feature is enabled, the device cannot use the programmable pull-up option. Disable the bus-hold feature when the I/O pin is configured for differential signals. Bus hold circuitry is not available on the dedicated clock pins.

The bus-hold circuitry is only active after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

The bus-hold circuitry uses a resistor with a nominal resistance ( $R_{BH}$ ) of approximately 7 k $\Omega$  to pull the signal level to the last-driven state. Refer to the DC Characteristics & Timing Specifications chapter in Volume 1 of the Cyclone II Device Handbook for the specific sustaining current for each  $V_{CCIO}$  voltage level driven through the resistor and overdrive current used to identify the next driven input level.

# Programmable Pull-Up Resistor

Each Cyclone II device I/O pin provides an optional programmable pull-up resistor during user mode. If you enable this feature for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) holds the output to the V<sub>CCIO</sub> level of the output pin's bank.

If the programmable pull-up is enabled, the device cannot use the bus-hold feature. The programmable pull-up resistors are not supported on the dedicated configuration, JTAG, and dedicated clock pins.

## **IOE Programmable Delay**

Refer to Table 5–36 and 5–37 for IOE programmable delay.

| Table 5-36                       | Table 5–36. Cyclone II IOE Programmable Delay on Column Pins Notes (1), (2) |               |               |               |                   |               |                          |               |                   |      |      |

|----------------------------------|-----------------------------------------------------------------------------|---------------|---------------|---------------|-------------------|---------------|--------------------------|---------------|-------------------|------|------|

| Parameter Paths Affected         | Paths Affected                                                              | Number<br>of  | Fast Corner   |               | –6 Speed<br>Grade |               | -7 Speed<br>Grade<br>(4) |               | –8 Speed<br>Grade |      | Unit |

|                                  | Settings                                                                    | Min<br>Offset | Max<br>Offset | Min<br>Offset | Max<br>Offset     | Min<br>Offset | Max<br>Offset            | Min<br>Offset | Max<br>Offset     |      |      |

| Input Delay                      | •                                                                           | 7             | 0             | 2233          | 0                 | 3827          | 0                        | 4232          | 0                 | 4349 | ps   |

| from Pin to<br>Internal<br>Cells | dataout to core                                                             |               | 0             | 2344          | _                 | _             | 0                        | 4088          | _                 | _    | ps   |

| Input Delay                      | Pad -> I/O                                                                  | 8             | 0             | 2656          | 0                 | 4555          | 0                        | 4914          | 0                 | 4940 | ps   |

| from Pin to<br>Input<br>Register | input register                                                              |               | 0             | 2788          | _                 | _             | 0                        | 4748          | _                 | _    | ps   |

| Delay from                       | I/O output                                                                  | 2             | 0             | 303           | 0                 | 563           | 0                        | 638           | 0                 | 670  | ps   |

| Output Register to Output Pin    | register -> Pad                                                             |               | 0             | 318           | _                 | _             | 0                        | 617           | _                 |      | ps   |

#### *Notes to Table 5–36:*

- (1) The incremental values for the settings are generally linear. For exact values of each setting, use the latest version of the Quartus II software.

- (2) The minimum and maximum offset timing numbers are in reference to setting "0" as available in the Quartus II software.

- (3) The value in the first row for each parameter represents the fast corner timing parameter for industrial and automotive devices. The second row represents the fast corner timing parameter for commercial devices.

- (4) The value in the first row is for automotive devices. The second row is for commercial devices.

| Table 5-37                       | Table 5–37. Cyclone II IOE Programmable Delay on Row Pins Notes (1), (2) (Part 1 of 2) |            |                 |               |                   |               |                              |               |                |               |      |

|----------------------------------|----------------------------------------------------------------------------------------|------------|-----------------|---------------|-------------------|---------------|------------------------------|---------------|----------------|---------------|------|

| Parameter                        | Paths<br>Affected                                                                      | Number     | Fast Corner (3) |               | –6 Speed<br>Grade |               | -7 Speed<br>Grade <i>(4)</i> |               | -8 Speed Grade |               |      |

|                                  |                                                                                        | d Settings | Min<br>Offset   | Max<br>Offset | Min<br>Offset     | Max<br>Offset | Min<br>Offset                | Max<br>Offset | Min<br>Offset  | Max<br>Offset | Unit |

| Input Delay                      | Pad ->                                                                                 | 7          | 0               | 2240          | 0                 | 3776          | 0                            | 4174          | 0              | 4290          | ps   |

| from Pin to<br>Internal<br>Cells | I/O<br>dataout<br>to core                                                              |            | 0               | 2352          |                   |               | 0                            | 4033          | _              | _             | ps   |

| Table 5–40. Cyclone II I/O Inpu | t Delay for Co     | olumn Pins (              | Part 2 of 3     | )              |                       |                       |                |      |

|---------------------------------|--------------------|---------------------------|-----------------|----------------|-----------------------|-----------------------|----------------|------|

|                                 |                    | Fast Co                   | rner            | -6             | -7                    | -7                    | -8             |      |

| I/O Standard                    | Parameter          | Industrial/<br>Automotive | Commer<br>-cial | Speed<br>Grade | Speed<br>Grade<br>(1) | Speed<br>Grade<br>(2) | Speed<br>Grade | Unit |

| 1.5V_HSTL_CLASS_I               | t <sub>P1</sub>    | 589                       | 617             | 1145           | 1176                  | 1208                  | 1208           | ps   |

|                                 | t <sub>PCOUT</sub> | 375                       | 393             | 683            | 731                   | 780                   | 780            | ps   |

| 1.5V_HSTL_CLASS_II              | t <sub>P1</sub>    | 589                       | 617             | 1145           | 1176                  | 1208                  | 1208           | ps   |

|                                 | $t_{PCOUT}$        | 375                       | 393             | 683            | 731                   | 780                   | 780            | ps   |

| 1.8V_HSTL_CLASS_I               | t <sub>P1</sub>    | 577                       | 605             | 1027           | 1035                  | 1045                  | 1045           | ps   |

|                                 | t <sub>PCOUT</sub> | 363                       | 381             | 565            | 590                   | 617                   | 617            | ps   |

| 1.8V_HSTL_CLASS_II              | t <sub>P1</sub>    | 577                       | 605             | 1027           | 1035                  | 1045                  | 1045           | ps   |

|                                 | t <sub>PCOUT</sub> | 363                       | 381             | 565            | 590                   | 617                   | 617            | ps   |

| DIFFERENTIAL_SSTL_2_            | t <sub>P1</sub>    | 533                       | 558             | 990            | 1015                  | 1040                  | 1040           | ps   |

| CLASS_I                         | t <sub>PCOUT</sub> | 319                       | 334             | 528            | 570                   | 612                   | 612            | ps   |

| DIFFERENTIAL_SSTL_2_            | t <sub>P1</sub>    | 533                       | 558             | 990            | 1015                  | 1040                  | 1040           | ps   |

| CLASS_II                        | t <sub>PCOUT</sub> | 319                       | 334             | 528            | 570                   | 612                   | 612            | ps   |

| DIFFERENTIAL_SSTL_18_           | t <sub>P1</sub>    | 577                       | 605             | 1027           | 1035                  | 1045                  | 1045           | ps   |

| CLASS_I                         | t <sub>PCOUT</sub> | 363                       | 381             | 565            | 590                   | 617                   | 617            | ps   |

| DIFFERENTIAL_SSTL_18_           | t <sub>P1</sub>    | 577                       | 605             | 1027           | 1035                  | 1045                  | 1045           | ps   |

| CLASS_II                        | t <sub>PCOUT</sub> | 363                       | 381             | 565            | 590                   | 617                   | 617            | ps   |

| 1.8V_DIFFERENTIAL_HSTL_         | t <sub>Pl</sub>    | 577                       | 605             | 1027           | 1035                  | 1045                  | 1045           | ps   |

| CLASS_I                         | t <sub>PCOUT</sub> | 363                       | 381             | 565            | 590                   | 617                   | 617            | ps   |

| 1.8V_DIFFERENTIAL_HSTL_         | t <sub>Pl</sub>    | 577                       | 605             | 1027           | 1035                  | 1045                  | 1045           | ps   |

| CLASS_II                        | t <sub>PCOUT</sub> | 363                       | 381             | 565            | 590                   | 617                   | 617            | ps   |

| 1.5V_DIFFERENTIAL_HSTL_         | t <sub>Pl</sub>    | 589                       | 617             | 1145           | 1176                  | 1208                  | 1208           | ps   |

| CLASS_I                         | t <sub>PCOUT</sub> | 375                       | 393             | 683            | 731                   | 780                   | 780            | ps   |

| 1.5V_DIFFERENTIAL_HSTL_         | t <sub>P1</sub>    | 589                       | 617             | 1145           | 1176                  | 1208                  | 1208           | ps   |

| CLASS_II                        | t <sub>PCOUT</sub> | 375                       | 393             | 683            | 731                   | 780                   | 780            | ps   |

| LVDS                            | t <sub>P1</sub>    | 623                       | 653             | 1072           | 1075                  | 1078                  | 1078           | ps   |

|                                 | t <sub>PCOUT</sub> | 409                       | 429             | 610            | 630                   | 650                   | 650            | ps   |

| 1.2V_HSTL                       | t <sub>P1</sub>    | 570                       | 597             | 1263           | 1324                  | 1385                  | 1385           | ps   |

|                                 | t <sub>PCOUT</sub> | 356                       | 373             | 801            | 879                   | 957                   | 957            | ps   |

| Table 5-48                         | Table 5–48. RSDS Transmitter Timing Specification (Part 2 of 2) |                |     |        |                |     |        |                |     |        |           |

|------------------------------------|-----------------------------------------------------------------|----------------|-----|--------|----------------|-----|--------|----------------|-----|--------|-----------|

|                                    | Conditions                                                      | -6 Speed Grade |     |        | -7 Speed Grade |     |        | -8 Speed Grade |     |        | I I m i A |

| Symbol                             | Conditions                                                      | Min            | Тур | Max(1) | Min            | Тур | Max(1) | Min            | Тур | Max(1) | Unit      |

| TCCS                               | _                                                               | _              | _   | 200    | _              | _   | 200    | _              | _   | 200    | ps        |

| Output<br>jitter (peak<br>to peak) | _                                                               | _              | _   | 500    | _              | _   | 500    | _              | _   | 500    | ps        |

| t <sub>RISE</sub>                  | 20–80%,<br>C <sub>LOAD</sub> = 5 pF                             | _              | 500 | _      | _              | 500 | _      |                | 500 | _      | ps        |

| t <sub>FALL</sub>                  | 80–20%,<br>C <sub>LOAD</sub> = 5 pF                             | _              | 500 | _      | _              | 500 | _      | _              | 500 | _      | ps        |

| t <sub>LOCK</sub>                  | _                                                               | _              |     | 100    | _              |     | 100    | _              | _   | 100    | μs        |

#### Note to Table 5-48:

(1) These specifications are for a three-resistor RSDS implementation. For single-resistor RSDS in ×10 through ×2 modes, the maximum data rate is 170 Mbps and the corresponding maximum input clock frequency is 85 MHz. For single-resistor RSDS in ×1 mode, the maximum data rate is 170 Mbps, and the maximum input clock frequency is 170 MHz. For more information about the different RSDS implementations, refer to the *High-Speed Differential Interfaces in Cyclone II Devices* chapter of the Cyclone II Device Handbook.

In order to determine the transmitter timing requirements, RSDS receiver timing requirements on the other end of the link must be taken into consideration. RSDS receiver timing parameters are typically defined as  $t_{SU}$  and  $t_{H}$  requirements. Therefore, the transmitter timing parameter specifications are  $t_{CO}$  (minimum) and  $t_{CO}$  (maximum). Refer to Figure 5–4 for the timing budget.

The AC timing requirements for RSDS are shown in Figure 5–5.

Tables 7–4 and 7–5 describe the Cyclone II PLL input and output ports.

| Port      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Source                     | Destination        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------|

| inclk[10] | Primary and secondary clock inputs to the PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Dedicated clock input pins | n counter          |

| pllena    | pllena is an active high signal that acts as an enable and reset signal for the PLL. It can be used for enabling or disabling each PLL. When pllena transitions low, the PLL clock output ports are driven to GND and the PLL loses lock. Once pllena transitions high again, the lock process begins and the PLL re-synchronizes to its input reference clock. The pllena port can be driven by an LE output or any general-purpose I/O pin.                                                                                                                            | Logic array or input pin   | PLL control signal |

| areset    | areset is an active high signal that resets all PLL counters to their initial values. When this signal is driven high the PLL resets its counters, clears the PLL outputs and loses lock. Once this signal is driven low again, the lock process begins and the PLL re-synchronizes to its input reference clock. The areset port can be driven by an LE output or any general-purpose I/O pin.                                                                                                                                                                          | Logic array or input pin   | PLL control signal |

| pfdena    | pfdena is an active high signal that enables or disables the up/down output signals from the PFD. When pfdena is driven low, the PFD is disabled, while the VCO continues to operate. The PLL clock outputs continue to toggle regardless of the input clock, but may experience some long-term drift. Because the output clock frequency does not change for some time, you can use the pfdena port as a shutdown or cleanup function when a reliable input clock is no longer available. The pfdena port can be driven by an LE output or any general-purpose I/O pin. | Logic array or input pin   | PFD                |

| clkswitch | clkswitch is an active high switchover signal used to initiate manual clock switchover.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Logic array or input pin   | PLL control signal |

| Table 8–1. Summary of M4K Memory Features (Part 2 of 2) |                                           |  |  |  |  |  |

|---------------------------------------------------------|-------------------------------------------|--|--|--|--|--|

| Feature                                                 | M4K Blocks                                |  |  |  |  |  |

| Packed mode                                             | ✓                                         |  |  |  |  |  |

| Address clock enable                                    | ✓                                         |  |  |  |  |  |

| Single-port mode                                        | ✓                                         |  |  |  |  |  |

| Simple dual-port mode                                   | ✓                                         |  |  |  |  |  |

| True dual-port mode                                     | ✓                                         |  |  |  |  |  |

| Embedded shift register mode (2)                        | ✓                                         |  |  |  |  |  |

| ROM mode                                                | ✓                                         |  |  |  |  |  |

| FIFO buffer (2)                                         | ✓                                         |  |  |  |  |  |

| Simple dual-port mixed width support                    | ✓                                         |  |  |  |  |  |

| True dual-port mixed width support                      | ✓                                         |  |  |  |  |  |

| Memory Initialization File (.mif)                       | ✓                                         |  |  |  |  |  |

| Mixed-clock mode                                        | ✓                                         |  |  |  |  |  |

| Power-up condition                                      | Outputs cleared                           |  |  |  |  |  |

| Register clears                                         | Output registers only                     |  |  |  |  |  |

| Same-port read-during-write                             | New data available at positive clock edge |  |  |  |  |  |

| Mixed-port read-during-write                            | Old data available at positive clock edge |  |  |  |  |  |

#### Notes to Table 8-1:

- (1) Maximum performance information is preliminary until device characterization.

- (2) FIFO buffers and embedded shift registers require external logic elements (LEs) for implementing control logic.

Table 8–2 shows the capacity and distribution of the M4K memory blocks in each Cyclone II device family member.

| Table 8–2. Number | Table 8–2. Number of M4K Blocks in Cyclone II Devices (Part 1 of 2) |                |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------|----------------|--|--|--|--|--|--|

| Device            | M4K Blocks                                                          | Total RAM Bits |  |  |  |  |  |  |

| EP2C5             | 26                                                                  | 119,808        |  |  |  |  |  |  |

| EP2C8             | 36                                                                  | 165,888        |  |  |  |  |  |  |

| EP2C15            | 52                                                                  | 239,616        |  |  |  |  |  |  |

| EP2C20            | 52                                                                  | 239,616        |  |  |  |  |  |  |

| EP2C35            | 105                                                                 | 483,840        |  |  |  |  |  |  |

# Cyclone II DDR Memory Support Overview

Table 9-1 shows the external memory interfaces supported in Cyclone II devices.

| Table 9–1. External Memory Support in Cyclone II Devices         Note (1) |                         |                      |                                          |                                          |  |  |  |

|---------------------------------------------------------------------------|-------------------------|----------------------|------------------------------------------|------------------------------------------|--|--|--|

| Memory Standard                                                           | I/O Standard            | Maximum Bus<br>Width | Maximum Clock<br>Rate Supported<br>(MHz) | Maximum Data<br>Rate Supported<br>(Mbps) |  |  |  |

| DDR SDRAM                                                                 | SSTL-2 class I (2)      | 72                   | 167                                      | 333 (1)                                  |  |  |  |

|                                                                           | SSTL-2 class II (2)     | 72                   | 133                                      | 267 (1)                                  |  |  |  |

| DDR2 SDRAM                                                                | SSTL-18 class I (2)     | 72                   | 167                                      | 333 (1)                                  |  |  |  |

|                                                                           | SSTL-18 class II (3)    | 72                   | 125                                      | 250 (1)                                  |  |  |  |

| QDRII SRAM (4)                                                            | 1.8-V HSTL class I (2)  | 36                   | 167                                      | 667 (1)                                  |  |  |  |

|                                                                           | 1.8-V HSTL class II (3) | 36                   | 100                                      | 400 (1)                                  |  |  |  |

### Notes to Table 9-1:

- (1) The data rate is for designs using the clock delay control circuitry.

- (2) These I/O standards are supported on all the I/O banks of the Cyclone II device.

- (3) These I/O standards are supported only on the I/O banks on the top and bottom of the Cyclone II device.

- (4) For maximum performance, Altera recommends using the 1.8-V HSTL I/O standard because of higher I/O drive strength. QDRII SRAM devices also support the 1.5-V HSTL I/O standard.

Cyclone II devices support the data strobe or read clock signal (DQS) used in DDR SDRAM with the clock delay control circuitry that can shift the incoming DQS signals to center them within the data window. To achieve DDR operation, the DDR input and output registers are implemented using the internal logic element (LE) registers. You should use the altdqs and altdq megafunctions in the Quartus II software to implement the DDR registers used for DQS and DQ signals, respectively.

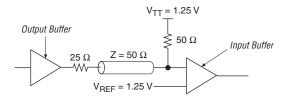

Figure 10-1. SSTL-2 Class I Termination

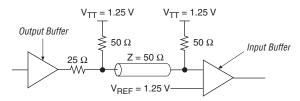

Figure 10-2. SSTL-2 Class II Termination

Cyclone II devices support both input and output SSTL-2 class I and II levels.

## Pseudo-Differential SSTL-2

The differential SSTL-2 I/O standard (EIA/JEDEC standard JESD8-9A) is a 2.5-V standard used for applications such as high-speed DDR SDRAM clock interfaces. This standard supports differential signals in systems using the SSTL-2 standard and supplements the SSTL-2 standard for differential clocks. The differential SSTL-2 standard specifies an input voltage range of – 0.3 V  $\leq$ V $_{\rm I}$   $\leq$ V $_{\rm CCIO}$  + 0.3 V. The differential SSTL-2 standard does not require an input reference voltage. Refer to Figures 10–3 and 10–4 for details on differential SSTL-2 terminations.

Cyclone II devices do not support true differential SSTL-2 standards. Cyclone II devices support pseudo-differential SSTL-2 outputs for PLL\_OUT pins and pseudo-differential SSTL-2 inputs for clock pins. Pseudo-differential inputs require an input reference voltage as opposed to the true differential inputs. Refer to Table 10–1 on page 10–2 for information about pseudo-differential SSTL.

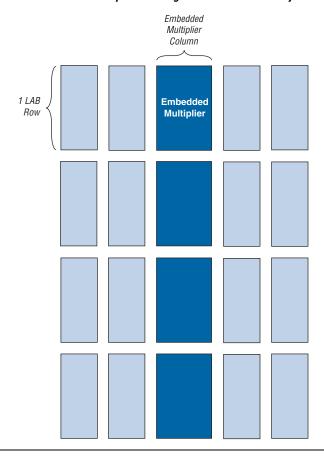

# Embedded Multiplier Block Overview

Each Cyclone II device has one to three columns of embedded multipliers that implement multiplication functions. Figure 12–1 shows one of the embedded multiplier columns with the surrounding LABs. Each embedded multiplier can be configured to support one  $18 \times 18$  multiplier or two  $9 \times 9$  multipliers.

Figure 12–1. Embedded Multipliers Arranged in Columns with Adjacent LABs

Section VI-2 Altera Corporation

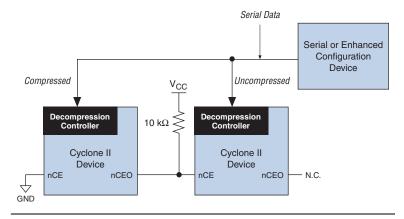

When multiple Cyclone II devices are cascaded, the compression feature can be selectively enabled for each device in the chain. Figure 13–2 depicts a chain of two Cyclone II devices. The first Cyclone II device has compression enabled and therefore receives a compressed bitstream from the configuration device. The second Cyclone II device has the compression feature disabled and receives uncompressed data.

Figure 13–2. Compressed & Uncompressed Configuration Data in a Programming File

You can generate programming files (for example, POF files) for this setup in the Quartus II software.

Active Serial Configuration (Serial Configuration Devices)

In the AS configuration scheme, Cyclone II devices are configured using a serial configuration device. These configuration devices are low-cost devices with non-volatile memory that feature a simple, four-pin interface and a small form factor. These features make serial configuration devices an ideal low-cost configuration solution.

For more information on serial configuration devices, see the *Serial Configuration Devices Data Sheet* in the Configuration Handbook.

configuration device. The configuration device then provides data on its serial data output (DATA) pin, which connects to the DATAO input of the Cyclone II device.

After the Cyclone II device receives all the configuration bits, it releases the open-drain CONF\_DONE pin, which is then pulled high by an external  $10\text{-k}\Omega$  resistor. Also, the Cyclone II device stops driving the DCLK signal. Initialization begins only after the CONF\_DONE signal reaches a logic high level. The CONF\_DONE pin must have an external  $10\text{-k}\Omega$  pull-up resistor in order for the device to initialize. All AS configuration pins (DATAO, DCLK, nCSO, and ASDO) have weak internal pull-up resistors which are always active. After configuration, these pins are set as input tri-stated and are pulled high by the internal weak pull-up resistors.

## Initialization Stage

In Cyclone II devices, the initialization clock source is either the Cyclone II 10-MHz (typical) internal oscillator (separate from the AS internal oscillator) or the optional CLKUSR pin. The internal oscillator is the default clock source for initialization. If the internal oscillator is used, the Cyclone II device provides itself with enough clock cycles for proper initialization. The advantage of using the internal oscillator is you do not need to send additional clock cycles from an external source to the CLKUSR pin during the initialization stage. Additionally, you can use the CLKUSR pin as a user I/O pin.

If you want to delay the initialization of the device, you can use the CLKUSR pin option. Using the CLKUSR pin allows you to control when your device enters user mode. The device can be delayed from entering user mode for an indefinite amount of time. When you enable the **User Supplied Start-Up Clock** option, the CLKUSR pin is the initialization clock source. Supplying a clock on CLKUSR does not affect the configuration process. After all configuration data has been accepted and CONF\_DONE goes high, Cyclone II devices require 299 clock cycles to initialize properly and support a CLKUSR  $f_{\rm MAX}$  of 100 MHz.

If your design has multiple Cyclone II devices of the same density and package that contain the same configuration data, connect the nCE inputs to GND and leave the nCEO pins floating. You can also use the nCEO pin as a user I/O pin. Connect the configuration device nCONFIG, nSTATUS, DCLK, DATAO, and CONF\_DONE pins to each Cyclone II device in the chain. The configuration signals may require buffering to ensure signal integrity and prevent clock skew problems. Make sure that the DCLK and DATA lines are buffered for every fourth device. All devices start and complete configuration at the same time. Figure 13–16 shows multiple device PS configuration when the Cyclone II devices are receiving the same configuration data.

## **PS Configuration Using a Download Cable**

In PS configuration, an intelligent host (e.g., a PC) can use a download cable to transfer data from a storage device to the Cyclone II device. You can use the Altera USB-Blaster universal serial bus (USB) port download cable, MasterBlaster<sup>TM</sup> serial/USB communications cable, ByteBlaster II parallel port download cable, or the ByteBlasterMV<sup>TM</sup> parallel port as a download cable.

Upon power up, the Cyclone II device goes through POR, which lasts approximately 100 ms for non "A" devices. During POR, the device resets, holds nSTATUS low, and tri-states all user I/O pins. Once the FPGA successfully exits POR, the nSTATUS pin is released and all user I/O pins continue to be tri-stated.

The value of the weak pull-up resistors on the I/O pins that are on before and during configuration can be found in the *Cyclone II Device Handbook*.

The configuration cycle consists of three stages: reset, configuration, and initialization. While the nCONFIG or nSTATUS pins are low, the device is in reset. To initiate configuration in this scheme, the download cable generates a low-to-high transition on the nCONFIG pin.

Make sure  $V_{\text{CCINT}}$  and  $V_{\text{CCIO}}$  for the banks where the configuration and JTAG pins reside are powered to the appropriate voltage levels in order to begin the configuration process.

When nconfig transitions high, the Cyclone II device comes out of reset and begins configuration. The Cyclone II device releases the open-drain nstatus pin, which is then pulled high by an external 10-k  $\Omega$  pull-up resistor. Once nstatus transitions high, the Cyclone II device is ready to receive configuration data. The programming hardware or download cable then transmits the configuration data one bit at a time to the device's Datao pin. The configuration data is clocked into the target device until Conf\_done goes high. The Conf\_done pin must have an external 10-k  $\Omega$  pull-up resistor in order for the device to initialize.

When using a download cable, you cannot use the **Auto-restart configuration after error** option. You must manually restart configuration in the Quartus II software when an error occurs. Additionally, you cannot use the **Enable user-supplied start-up clock (CLKUSR)** option when programming the FPGA using the Quartus II programmer and download cable. This option is disabled in the SOF. Therefore, if you turn on the CLKUSR option, you do not need to provide a clock on CLKUSR when you are configuring the FPGA with the

## Reconfiguration

After all the configuration data is written into the serial configuration device successfully, the Cyclone II device does not reconfigure by itself. The intelligent host issues the <code>PULSE\_NCONFIG</code> JTAG instruction to initialize the reconfiguration process. During reconfiguration, the master Cyclone II device is reset and the serial flash loader design no longer exists in the Cyclone II device and the serial configuration device configures all the devices in the chain with your user design.

# Device Configuration Pins

This section describes the connections and functionality of all the configuration related pins on the Cyclone II device. Table 13–11 describes the dedicated configuration pins, which are required to be connected properly on your board for successful configuration. Some of these pins may not be required for your configuration schemes.

| Table 13–11. | Table 13–11. Dedicated Configuration Pins on the Cyclone II Device (Part 1 of 5) |                         |          |                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------|-------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name     | User<br>Mode                                                                     | Configuration<br>Scheme | Pin Type | Description                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| MSEL[10]     | N/A                                                                              | All                     | Input    | This pin is a two-bit configuration input that sets the Cyclone II device configuration scheme. See Table 13–1 for the appropriate settings.<br>You must connect these pins to $V_{\rm CCIO}$ or ground.<br>The MSEL [10] pins have 9-k $\Omega$ internal pull-down resistors that are always active.                                                                                      |  |  |  |  |  |

| nCONFIG      | N/A                                                                              | All                     | Input    | This pin is a configuration control input. If this pin is pulled low during user mode, the FPGA loses its configuration data, enters a reset state, and tri-states all I/O pins. Transitioning this pin high initiates a reconfiguration.  If your configuration scheme uses an enhanced configuration device or EPC2 device, you can connect the nconfiguration directly to Vcc or to the |  |  |  |  |  |

|              |                                                                                  |                         |          | configuration device's nINIT_CONF pin.  The input buffer on this pin supports hysteresis using Schmitt trigger circuitry.                                                                                                                                                                                                                                                                  |  |  |  |  |  |

# Document Revision History

Table 13–14 shows the revision history for this document.

| Table 13–14. De               | Table 13–14. Document Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Date &<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Summary of Changes                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| February 2007<br>v3.1         | <ul> <li>Added document revision history.</li> <li>Added Note (1) to Table 13–1.</li> <li>Added Note (1) to Table 13–4.</li> <li>Updated Figure 13–3.</li> <li>Updated Figures 13–6 and 13–7.</li> <li>Updated Note (2) to Figure 13–13.</li> <li>Updated "Single Device PS Configuration Using a Configuration Device" section.</li> <li>Updated Note (2) to Figure 13–14.</li> <li>Updated Note (2) to Figure 13–15.</li> <li>Updated Note (2) to Figure 13–16.</li> <li>Updated Note (2) to Figure 13–17.</li> <li>Updated Note (4) to Figure 13–21.</li> <li>Updated Note (2) to Figure 13–25.</li> </ul>                                                                                                       | <ul> <li>Changed unit 'kw' to 'kΩ' in Figures 13–6 and 13–7.</li> <li>Added note about serial configuration devices supporting 20 MHz and 40 MHz DCLK.</li> <li>Added infomation about the need for a resistor on nCONFIG if reconfiguration is required.</li> <li>Added information about MSEL [10] internal pull-down resistor value.</li> </ul> |  |  |  |  |  |  |

| July 2005 v2.0                | <ul> <li>Updated "Configuration Stage" section.</li> <li>Updated "PS Configuration Using a Download Cable" section.</li> <li>Updated Figures 13–8, 13–12, and 13–18.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| November 2004<br>v1.1         | <ul> <li>Updated "Configuration Stage" section in "Single Device AS Configuration" section.</li> <li>Updated "Initialization Stage" section in "Single Device AS Configuration" section.</li> <li>Updated Figure 13-8.</li> <li>Updated "Initialization Stage" section in "Single Device PS Configuration Using a MAX II Device as an External Host" section.</li> <li>Updated Table 13-7.</li> <li>Updated "Single Device PS Configuration Using a Configuration Device" section.</li> <li>Updated "Initialization Stage" section in "Single Device PS Configuration Using a Configuration Device" section.</li> <li>Updated Figure 13-18.</li> <li>Updated "Single Device JTAG Configuration" section.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| June 2004 v1.0                | Added document to the Cyclone II Device Handbook.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

# Thermal Resistance

Thermal resistance values for Cyclone II devices are provided for a board meeting JEDEC specifications and for a typical board. The values provided are as follows:

- θ<sub>JA</sub> (°C/W) Still Air—Junction-to-ambient thermal resistance with no airflow when a heat sink is not being used.

- $\theta_{JA}$  (° C/W) 100 ft./minute—Junction-to-ambient thermal resistance with 100 ft./minute airflow when a heat sink is not being used.

- $\theta_{JA}$  (° C/W) 200 ft./minute—Junction-to-ambient thermal resistance with 200 ft./minute airflow when a heat sink is not being used.

- $\theta_{JA}$  (° C/W) 400 ft./minute—Junction-to-ambient thermal resistance with 400 ft./minute airflow when a heat sink is not being used.

- $\theta_{IC}$  (°C/W)—Junction-to-case thermal resistance for device.

- $\theta_{JB}$  (° C/W)—Junction-to-board thermal resistance for specific board being used.

Table 15–2 provides  $\theta_{JA}$  (junction-to-ambient thermal resistance) values and  $\theta_{JC}$  (junction-to-case thermal resistance) values for Cyclone II devices on a board meeting JEDEC specifications for thermal resistance calculation. The JEDEC board specifications require two signal and two power/ground planes and are available at **www.jedec.org**.

| Table 15–2. Thermal Resistance of Cyclone II Devices for Board Meeting JEDEC Specifications (Part 1 of 2) |              |                    |                                      |                                         |                                         |                                         |                            |

|-----------------------------------------------------------------------------------------------------------|--------------|--------------------|--------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------|

| Device                                                                                                    | Pin<br>Count | Package            | θ <sub>JA</sub> (° C/W)<br>Still Air | θ <sub>JA</sub> (° C/W)<br>100 ft./min. | θ <sub>JA</sub> (° C/W)<br>200 ft./min. | θ <sub>JA</sub> (° C/W)<br>400 ft./min. | θ <sub>JC</sub><br>(° C/W) |

| EP2C5                                                                                                     | 144          | TQFP               | 31                                   | 29.3                                    | 27.9                                    | 25.5                                    | 10                         |

|                                                                                                           | 208          | PQFP               | 30.4                                 | 29.2                                    | 27.3                                    | 22.3                                    | 5.5                        |

|                                                                                                           | 256          | FineLine BGA       | 30.2                                 | 26.1                                    | 23.6                                    | 21.7                                    | 8.7                        |

| EP2C8                                                                                                     | 144          | TQFP               | 29.8                                 | 28.3                                    | 26.9                                    | 24.9                                    | 9.9                        |

|                                                                                                           | 208          | PQFP               | 30.2                                 | 28.8                                    | 26.9                                    | 21.7                                    | 5.4                        |

|                                                                                                           | 256          | FineLine BGA       | 27                                   | 23                                      | 20.5                                    | 18.5                                    | 7.1                        |

| EP2C15                                                                                                    | 256          | FineLine BGA       | 24.2                                 | 20                                      | 17.8                                    | 16                                      | 5.5                        |

|                                                                                                           | 484          | FineLine BGA       | 21                                   | 17                                      | 14.8                                    | 13.1                                    | 4.2                        |

| EP2C20                                                                                                    | 240          | PQFP               | 26.6                                 | 24                                      | 21.4                                    | 17.4                                    | 4.2                        |

|                                                                                                           | 256          | FineLine BGA       | 24.2                                 | 20                                      | 17.8                                    | 16                                      | 5.5                        |

|                                                                                                           | 484          | FineLine BGA       | 21                                   | 17                                      | 14.8                                    | 13.1                                    | 4.2                        |

| EP2C35                                                                                                    | 484          | FineLine BGA       | 19.4                                 | 15.4                                    | 13.3                                    | 11.7                                    | 3.3                        |

|                                                                                                           | 484          | Ultra FineLine BGA | 20.6                                 | 16.6                                    | 14.5                                    | 12.8                                    | 5                          |

|                                                                                                           | 672          | FineLine BGA       | 18.6                                 | 14.6                                    | 12.6                                    | 11.1                                    | 3.1                        |