Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                        |

|--------------------------------|--------------------------------------------------------|

| Product Status                 | Active                                                 |

| Number of LABs/CLBs            | 516                                                    |

| Number of Logic Elements/Cells | 8256                                                   |

| Total RAM Bits                 | 165888                                                 |

| Number of I/O                  | 182                                                    |

| Number of Gates                | -                                                      |

| Voltage - Supply               | 1.15V ~ 1.25V                                          |

| Mounting Type                  | Surface Mount                                          |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                     |

| Package / Case                 | 256-LBGA                                               |

| Supplier Device Package        | 256-FBGA (17x17)                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c8f256i8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 133-MHz PCI-X 1.0 specification compatibility

- High-speed external memory support, including DDR, DDR2, and SDR SDRAM, and QDRII SRAM supported by drop in Altera IP MegaCore functions for ease of use

- Three dedicated registers per I/O element (IOE): one input register, one output register, and one output-enable register

- Programmable bus-hold feature

- Programmable output drive strength feature

- Programmable delays from the pin to the IOE or logic array

- I/O bank grouping for unique VCCIO and/or VREF bank settings

- MultiVolt<sup> $\mathbb{M}$ </sup> I/O standard support for 1.5-, 1.8-, 2.5-, and 3.3-interfaces

- Hot-socketing operation support

- Tri-state with weak pull-up on I/O pins before and during configuration

- Programmable open-drain outputs

- Series on-chip termination support

#### Flexible clock management circuitry

- Hierarchical clock network for up to 402.5-MHz performance

- Up to four PLLs per device provide clock multiplication and division, phase shifting, programmable duty cycle, and external clock outputs, allowing system-level clock management and skew control

- Up to 16 global clock lines in the global clock network that drive throughout the entire device

#### Device configuration

- Fast serial configuration allows configuration times less than 100 ms

- Decompression feature allows for smaller programming file storage and faster configuration times

- Supports multiple configuration modes: active serial, passive serial, and JTAG-based configuration

- Supports configuration through low-cost serial configuration devices

- Device configuration supports multiple voltages (either 3.3, 2.5, or 1.8 V)

#### Intellectual property

Altera megafunction and Altera MegaCore function support, and Altera Megafunctions Partners Program (AMPP<sup>SM</sup>) megafunction support, for a wide range of embedded processors, on-chip and off-chip interfaces, peripheral functions, DSP functions, and communications functions and

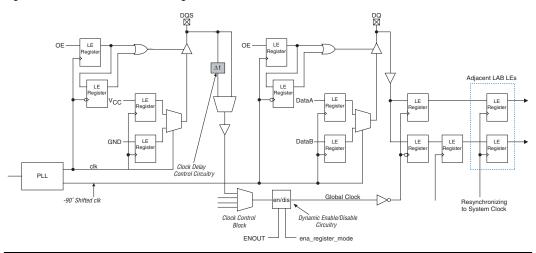

Figure 2-27. DDR SDRAM Interfacing

For more information on Cyclone II external memory interfaces, see the *External Memory Interfaces* chapter in Volume 1 of the *Cyclone II Device Handbook*.

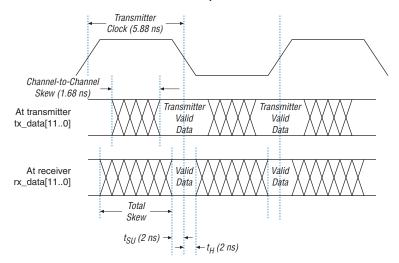

Figure 5-5. RSDS Transmitter Clock to Data Relationship

Table 5–49 shows the mini-LVDS transmitter timing budget for Cyclone II devices at 311 Mbps. Cyclone II devices cannot receive mini-LVDS data because the devices are intended for applications where they will be driving display drivers. A maximum mini-LVDS data rate of 311 Mbps is supported for Cyclone II devices using DDIO registers. Cyclone II devices support mini-LVDS only in the commercial temperature range.

| Table 5–49. Mini-LVDS Transmitter Timing Specification (Part 1 of 2) |            |                |     |                |     |     |                |     |     |       |      |

|----------------------------------------------------------------------|------------|----------------|-----|----------------|-----|-----|----------------|-----|-----|-------|------|

| Symbol                                                               | Conditions | –6 Speed Grade |     | -7 Speed Grade |     |     | –8 Speed Grade |     |     | 1114  |      |

|                                                                      | Conditions | Min            | Тур | Max            | Min | Тур | Max            | Min | Тур | Max   | Unit |

| f <sub>HSCLK</sub>                                                   | ×10        | 10             | _   | 155.5          | 10  | _   | 155.5          | 10  | _   | 155.5 | MHz  |

| (input<br>clock<br>frequency)                                        | ×8         | 10             | _   | 155.5          | 10  | _   | 155.5          | 10  | _   | 155.5 | MHz  |

|                                                                      | ×7         | 10             | _   | 155.5          | 10  | _   | 155.5          | 10  | _   | 155.5 | MHz  |

|                                                                      | ×4         | 10             | _   | 155.5          | 10  | _   | 155.5          | 10  | _   | 155.5 | MHz  |

|                                                                      | ×2         | 10             | _   | 155.5          | 10  | _   | 155.5          | 10  | _   | 155.5 | MHz  |

|                                                                      | ×1         | 10             | _   | 311            | 10  | _   | 311            | 10  | _   | 311   | MHz  |

# **PLL Timing Specifications**

Table 5–54 describes the Cyclone II PLL specifications when operating in the commercial junction temperature range (0° to 85° C), the industrial junction temperature range (–40° to 100° C), the automotive junction temperature range (–40° to 125° C), and the extended temperature range (–40° to 125° C). Follow the PLL specifications for –8 speed grade devices when operating in the industrial, automotive, or extended temperature range.

| Symbol                                       | Parameter                                                              | Min | Тур | Max     | Unit |

|----------------------------------------------|------------------------------------------------------------------------|-----|-----|---------|------|

| f <sub>IN</sub>                              | Input clock frequency (–6 speed grade)                                 | 10  | _   | (4)     | MHz  |

|                                              | Input clock frequency (–7 speed grade)                                 | 10  | _   | (4)     | MHz  |

|                                              | Input clock frequency (–8 speed grade)                                 | 10  | _   | (4)     | MHz  |

| f <sub>INPFD</sub>                           | PFD input frequency (-6 speed grade)                                   | 10  | _   | 402.5   | MHz  |

|                                              | PFD input frequency (-7 speed grade)                                   | 10  | _   | 402.5   | MHz  |

|                                              | PFD input frequency (–8 speed grade)                                   | 10  | _   | 402.5   | MHz  |

| f <sub>INDUTY</sub>                          | Input clock duty cycle                                                 | 40  | _   | 60      | %    |

| t <sub>INJITTER</sub> (5)                    | Input clock period jitter                                              | _   | 200 | _       | ps   |

| f <sub>OUT_EXT</sub> (external clock output) | PLL output frequency (–6 speed grade)                                  | 10  | _   | (4)     | MHz  |

|                                              | PLL output frequency (-7 speed grade)                                  | 10  | _   | (4)     | MHz  |

|                                              | PLL output frequency (–8 speed grade)                                  | 10  | _   | (4)     | MHz  |

| f <sub>OUT</sub> (to global clock)           | PLL output frequency (–6 speed grade)                                  | 10  | _   | 500     | MHz  |

|                                              | PLL output frequency (-7 speed grade)                                  | 10  | _   | 450     | MHz  |

|                                              | PLL output frequency (-8 speed grade)                                  | 10  | _   | 402.5   | MHz  |

| toutduty                                     | Duty cycle for external clock output (when set to 50%)                 | 45  | _   | 55      | %    |

| t <sub>JITTER</sub> (p-p) (2)                | Period jitter for external clock output f <sub>OUT_EXT</sub> > 100 MHz | _   | _   | 300     | ps   |

|                                              | f <sub>OUT_EXT</sub> ≤100 MHz                                          | _   | _   | 30      | mUI  |

| t <sub>LOCK</sub>                            | Time required to lock from end of device configuration                 | _   | _   | 100 (6) | μs   |

| t <sub>PLL PSERR</sub>                       | Accuracy of PLL phase shift                                            | _   | _   | ±60     | ps   |

# Section II. Clock Management

This section provides information on the phase-locked loops (PLLs). Cyclone® II PLLs offer general-purpose clock management with multiplication and phase shifting and also have the ability to drive off chip to control system-level clock networks. This section contains detailed information on the features, the interconnections to the logic array and off chip, and the specifications for Cyclone II PLLs.

This section includes the following chapter:

■ Chapter 7, PLLs in Cyclone II Devices

# **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

Altera Corporation Section II–1

Table 7–2 provides an overview of the Cyclone II PLL features.

| Table 7–2. Cyclone II PLL Features     |                                         |  |  |  |  |  |

|----------------------------------------|-----------------------------------------|--|--|--|--|--|

| Feature                                | Description                             |  |  |  |  |  |

| Clock multiplication and division      | $m / (n \times post-scale counter)$ (1) |  |  |  |  |  |

| Phase shift                            | Down to 125-ps increments (2), (3)      |  |  |  |  |  |

| Programmable duty cycle                | <b>✓</b>                                |  |  |  |  |  |

| Number of internal clock outputs       | Up to three per PLL (4)                 |  |  |  |  |  |

| Number of external clock outputs       | One per PLL (4)                         |  |  |  |  |  |

| Locked port can feed logic array       | ~                                       |  |  |  |  |  |

| PLL clock outputs can feed logic array | <b>✓</b>                                |  |  |  |  |  |

| Manual clock switchover                | ✓                                       |  |  |  |  |  |

| Gated lock                             | ✓                                       |  |  |  |  |  |

#### Notes to Table 7–2:

- (1) *m* and post-scale counter values range from 1 to 32. *n* ranges from 1 to 4.

- (2) The smallest phase shift is determined by the voltage control oscillator (VCO) period divided by 8.

- (3) For degree increments, Cyclone II devices can shift output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the VCO frequency.

- (4) The Cyclone II PLL has three output counters that drive the global clock network. One of these output counters (c2) can also drive a dedicated external I/O pin (single ended or differential). This counter output can also drive the external clock output (PLL<#>\_OUT) and internal global clock network at the same time.

# Cyclone II PLL Hardware Overview

Cyclone II devices contain up to four PLLs that are arranged in the four corners of the Cyclone II device as shown in Figure 7–1, which shows a top-level diagram of the Cyclone II device and the PLL locations.

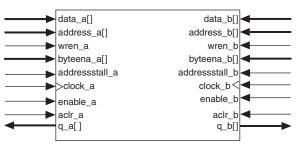

Figure 8–10. Cyclone II True Dual-Port Mode Note (1)

Note to Figure 8-10:

True dual-port memory supports input and output clock mode in addition to the independent clock mode shown.

The widest bit configuration of the M4K blocks in true dual-port mode is  $256 \times 16$ -bit (18-bit with parity).

The  $128 \times 32$ -bit (36-bit with parity) configuration of the M4K block is unavailable because the number of output drivers is equivalent to the maximum bit width. The maximum width of the true dual-port RAM equals half of the total number of output drivers because true dual-port RAM has outputs on two ports. Table 8–6 lists the possible M4K block mixed-port width configurations.

| Read Port | Write Port |          |          |          |          |          |          |  |  |  |  |  |

|-----------|------------|----------|----------|----------|----------|----------|----------|--|--|--|--|--|

|           | 4K×1       | 2K × 2   | 1K × 4   | 512 × 8  | 256 × 16 | 512 × 9  | 256 × 18 |  |  |  |  |  |

| 4K × 1    | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |  |  |  |

| 2K × 2    | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |  |  |  |

| 1K × 4    | <b>✓</b>   | <b>✓</b> | <b>✓</b> | ~        | <b>✓</b> |          |          |  |  |  |  |  |

| 512 × 8   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |  |  |  |

| 256 × 16  | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |  |  |  |

| 512 × 9   |            |          |          |          |          | <b>✓</b> | ✓        |  |  |  |  |  |

| 256 × 18  |            |          |          |          |          | <b>✓</b> | <b>✓</b> |  |  |  |  |  |

In true dual-port configuration, the RAM outputs are in read-during-write mode. This means that during a write operation, data being written to the A or B port of the RAM flows through to the A or B

QDRII SRAM devices use the following clock signals:

- Input clocks K and K#

- Optional output clocks C and C#

- Echo clocks CQ and CQn

Clocks C#, K#, and CQn are logical complements of clocks C, K, and CQ, respectively. Clocks C, C#, K, and K# are inputs to the QDRII SRAM, and clocks CQ and CQn are outputs from the QDRII SRAM. Cyclone II devices use single-clock mode for QDRII SRAM interfacing. The K and K# clocks are used for both read and write operations, and the C and C# clocks are unused.

You can generate C, C#, K, and K# clocks using any of the I/O registers via the DDR registers. Due to strict skew requirements between K and K# signals, use adjacent pins to generate the clock pair. Surround the pair with buffer pins tied to  $V_{CC}$  and pins tied to ground for better noise immunity from other signals.

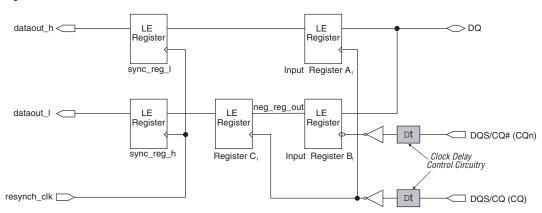

In Cyclone II devices, another DQS pin implements the CQn pin in the QDRII SRAM memory interface. These pins are denoted by DQS/CQ# in the pin table. Connect CQ and CQn pins to the Cyclone II DQS/CQ and DQS/CQ# pins of the same DQ groups, respectively. You must configure the DQS/CQ and DQS/CQ# as bidirectional pins. However, because CQ and CQn pins are output-only pins from the memory device, the Cyclone II device's QDRII SRAM memory interface requires that you ground the DQS/CQ and DQS/CQ# output enable. To capture data presented by the memory device, connect the shifted CQ signal to register  $\mathtt{C}_\mathtt{I}$  and input register  $\mathtt{A}_\mathtt{I}$ . Connect the shifted CQn to input register  $\mathtt{B}_\mathtt{I}$ . Figure 9–4 shows the CQ and CQn connections for a QDRII SRAM read.

Figure 9-4. CQ & CQn Connection for QDRII SRAM Read

#### Read & Write Operation

Figure 9–5 shows the data and clock relationships in QDRII SRAM devices at the memory pins during reads. QDRII SRAM devices send data within  $t_{\rm CO}$  time after each rising edge of the read clock C or C# in multiclock mode or the input clock K or K# in single clock mode. Data is valid until  $t_{\rm DOH}$  time after each rising edge of the read clock C or C# in multiclock mode or the input clock K or K# in single clock mode. The CQ and CQn clocks are edge-aligned with the read data signal. These clocks accompany the read data for data capture in Cyclone II devices.

| Table 10–1. Cyclone II Supported I/O Standards and Constraints (Part 2 of 2) |                            |                                     |        |                               |                  |               |              |                  |  |

|------------------------------------------------------------------------------|----------------------------|-------------------------------------|--------|-------------------------------|------------------|---------------|--------------|------------------|--|

| I/O Standard                                                                 | Туре                       | V <sub>CCIO</sub> Level             |        | Top and<br>Bottom I/O<br>Pins |                  | Side I/O Pins |              |                  |  |

|                                                                              |                            | Input                               | Output | CLK,<br>DQS                   | User I/O<br>Pins | CLK,<br>DQS   | PLL_OUT      | User I/O<br>Pins |  |

| Differential HSTL-15 class I                                                 | Pseudo<br>differential (3) | (4)                                 | 1.5 V  | _                             | _                | _             | <b>√</b> (6) | _                |  |

| or class II                                                                  |                            | 1.5 V                               | (4)    | <b>(</b> 5)                   | _                | <b>(</b> 5)   | _            | _                |  |

| Differential HSTL-18 class I                                                 | Pseudo<br>differential (3) | (4)                                 | 1.8 V  | _                             | _                | _             | <b>√</b> (6) | _                |  |

| or class II                                                                  |                            | 1.8 V                               | (4)    | <b>(</b> 5)                   | _                | <b>(</b> 5)   | _            | _                |  |

| LVDS                                                                         | Differential               | 2.5 V                               | 2.5 V  | <b>✓</b>                      | <b>✓</b>         | <b>✓</b>      | <b>✓</b>     | ✓                |  |

| RSDS and mini-LVDS (7)                                                       | Differential               | (4)                                 | 2.5 V  | _                             | <b>✓</b>         | _             | <b>✓</b>     | ✓                |  |

| LVPECL (8)                                                                   | Differential               | 3.3 V/<br>2.5 V/<br>1.8 V/<br>1.5 V | (4)    | <b>~</b>                      | _                | <b>✓</b>      | _            | _                |  |

#### Notes to Table 10-1:

- (1) These pins support SSTL-18 class II and 1.8- and 1.5-V HSTL class II inputs.

- (2) PCI-X does not meet the IV curve requirement at the linear region. PCI-clamp diode is not available on top and bottom I/O pins.

- (3) Pseudo-differential HSTL and SSTL outputs use two single-ended outputs with the second output programmed as inverted. Pseudo-differential HSTL and SSTL inputs treat differential inputs as two single-ended HSTL and SSTL inputs and only decode one of them.

- (4) This I/O standard is not supported on these I/O pins.

- (5) This I/O standard is only supported on the dedicated clock pins.

- (6) PLL OUT does not support differential SSTL-18 class II and differential 1.8 and 1.5-V HSTL class II.

- (7) mini-LVDS and RSDS are only supported on output pins.

- (8) LVPECL is only supported on clock inputs, not DQS and dual-purpose clock pins.

## 3.3-V LVTTL (EIA/JEDEC Standard JESD8-B)

The 3.3-V LVTTL I/O standard is a general-purpose, single-ended standard used for 3.3-V applications. The LVTTL standard defines the DC interface parameters for digital circuits operating from a 3.0-/3.3-V power supply and driving or being driven by LVTTL-compatible devices.

The LVTTL input standard specifies a wider input voltage range of  $-0.3 \text{ V} \leq V_I \leq 3.9 \text{ V}$ . Altera recommends an input voltage range of  $-0.5 \text{ V} \leq V_I \leq 4.1 \text{ V}$ .

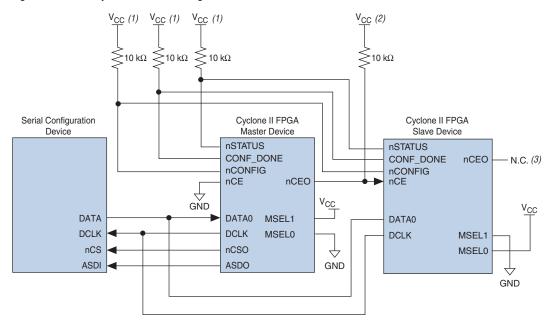

Figure 13-4. Multiple Device AS Configuration

#### Notes to Figure 13-4:

- Connect the pull-up resistors to a 3.3-V supply.

- (2) Connect the pull-up resistor to the V<sub>CCIO</sub> supply voltage of I/O bank that the nCEO pin resides in.

- (3) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed another device's nCE pin.

As shown in Figure 13–4, the nSTATUS and CONF\_DONE pins on all target FPGAs are connected together with external pull-up resistors. These pins are open-drain bidirectional pins on the FPGAs. When the first device asserts nCEO (after receiving all of its configuration data), it releases its CONF\_DONE pin. However, the subsequent devices in the chain keep the CONF\_DONE signal low until they receive their configuration data. When all the target FPGAs in the chain have received their configuration data and have released CONF\_DONE, the pull-up resistor pulls this signal high, and all devices simultaneously enter initialization mode.

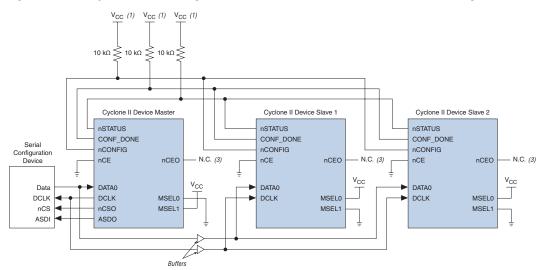

#### Single SOF

The second method configures both the master and slave Cyclone II devices with the same SOF. The serial configuration device stores one copy of the SOF file. This setup is shown in Figure 13–6 where the master is setup in AS mode, and the slave devices are setup in PS mode (MSEL=01). You could setup one or more slave devices in the chain and all the slave devices are setup in the same way as shown in Figure 13–6.

Figure 13-6. Multiple Device AS Configuration When FPGAS Receive the Same Data with a Single SOF

#### *Notes to Figure 13–6:*

- Connect the pull-up resistors to a 3.3-V supply.

- (2) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed another device's nCE pin.

In this setup, all the Cyclone II devices in the chain are connected for concurrent configuration. This can reduce the AS configuration time because all the Cyclone II devices are configured in one configuration cycle. Connect the nCE input pins of all the Cyclone II devices to ground. You can either leave the nCEO output pins on all the Cyclone II devices unconnected or use the nCEO output pins as normal user I/O pins. The DATA and DCLK pins are connected in parallel to all the Cyclone II devices.

Upon power-up, the Cyclone II device goes through a POR. During POR, the device reset, holds <code>nSTATUS</code> and <code>CONF\_DONE</code> low, and tri-states all user I/O pins. After POR, which typically lasts 100 ms, the Cyclone II FPGA releases <code>nSTATUS</code> and enters configuration mode when this signal is pulled high by the external 10-k $\Omega$ resistor. Once the FPGA successfully exits POR, all user I/O pins continue to be tri-stated. Cyclone II devices have weak pull-up resistors on the user I/O pins which are on before and during configuration.

The configuration device also goes through a POR delay to allow the power supply to stabilize. The maximum POR time for EPC2 or EPC1 devices is 200 ms. The POR time for enhanced configuration devices can be set to 100 ms or 2 ms, depending on the enhanced configuration device's PORSEL pin setting. If the PORSEL pin is connected to ground, the POR delay is 100 ms. If the PORSEL pin is connected to  $V_{CC}$ , the POR delay is 2 ms. You must power the Cyclone II device before or during the enhanced configuration device POR time. During POR, the configuration device transitions its OE pin low. This low signal delays configuration because the OE pin is connected to the target device's nSTATUS pin. When the target and configuration devices complete POR, they both release the nSTATUS to OE line, which is then pulled high by a pull-up resistor.

When the power supplies have reached the appropriate operating voltages, the target FPGA senses the low-to-high transition on nconfig and initiates the configuration cycle. The configuration cycle consists of three stages: reset, configuration, and initialization.

The Cyclone II device does not have a PORSEL pin.

#### Reset Stage

While nCONFIG or nSTATUS is low, the device is in reset. You can delay configuration by holding the nCONFIG or nSTATUS pin low.

$V_{\rm CCINT}$  and  $V_{\rm CCIO}$  of the banks where the configuration and JTAG pins reside need to be fully powered to the appropriate voltage levels in order to begin the configuration process.

When the nconfig signal goes high, the device comes out of reset and releases the nstatus pin, which is pulled high by a pull-up resistor. Enhanced configuration and EPC2 devices have an optional internal pull-up resistor on the OE pin. You can turn on this option in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box. If this internal pull-up resistor is not used, you need to connect an external  $10\text{-k}\Omega$  pull-up resistor to the OE and nstatus line. Once nstatus is released, the FPGA is ready to receive configuration data and the configuration stage begins.

<code>nconfig</code> is low and during the beginning of configuration. Once the optional bit to enable <code>Init\_done</code> is programmed into the device (during the first frame of configuration data), the <code>Init\_done</code> pin goes low. When initialization is complete, the <code>Init\_done</code> pin is released and pulled high. This low-to-high transition signals that the FPGA has entered user mode. If you do not use the <code>Init\_done</code> pin, the initialization period is complete after the <code>Conf\_done</code> signal transitions high and 299 clock cycles are sent to the <code>Clkusr</code> pin or after the time  $t_{CF2UM}$  (see Table 13–7) if the Cyclone II device uses the internal oscillator.

After successful configuration, if you intend to synchronize the initialization of multiple devices that are not in the same configuration chain, your system must not pull the CONF\_DONE signal low to delay initialization. Instead, use the optional CLKUSR pin to synchronize the initialization of multiple devices that are not in the same configuration chain. Devices in the same configuration chain initialize together if their CONF DONE pins are tied together.

If the optional CLKUSR pin is being used and nCONFIG is pulled low to restart configuration during device initialization, you need to ensure that CLKUSR continues toggling during the time nSTATUS is low (maximum of  $40~\mu s$ ).

#### User Mode

When initialization is complete, the FPGA enters user mode. In user mode, the user I/O pins do not have weak pull-up resistors and function as assigned in your design. Enhanced configuration devices and EPC2 devices drive DCLK low and DATA0 high (EPC1 devices drive the DCLK pin low and tri-state the DATA pin) at the end of configuration.

When the FPGA is in user mode, pull the nconfig pin low to begin reconfiguration. The nconfig pin should be low for at least 2 µs. When nconfig transitions low, the Cyclone II device also pulls the nstatus and conf\_done pins low and all I/O pins are tri-stated. Because conf\_done transitions low, this activates the configuration device since it will see its ncs pin transition low. Once nconfig returns to a logic high level and nstatus is released by the FPGA, reconfiguration begins.

### Error During Configuration

If an error occurs during configuration, the Cyclone II drives its nSTATUS pin low, resetting itself internally. Since the nSTATUS pin is tied to OE, the configuration device is also reset. If you turn on the **Auto-restart configuration after error** option in the Quartus II software from the **General** tab of the **Device & Pin Options** dialog box, the FPGA automatically initiates reconfiguration if an error occurs. The Cyclone II

devices and to the slave configuration devices. Connect the first configuration device's nCS pin to all the Cyclone II device's CONF\_DONE pins, and connect the nCASC pin to the nCS pin of the next configuration device in the chain. Leave the nCASC pin of the last configuration device floating. When the master configuration device sends all the data to the Cyclone II device, the configuration device transitions the nCASC pin low, which drives nCS on the next configuration device. Because a configuration device requires less than one clock cycle to activate a subsequent configuration device, the data stream is uninterrupted.

Enhanced configuration devices (EPC16, EPC8, and EPC4 devices) cannot be cascaded.

Since all nSTATUS and CONF\_DONE pins are connected, if any device detects an error, the master configuration device stops configuration for the entire chain and the entire chain must be reconfigured. For example, if the master configuration device does not detect the Cyclone II device's CONF\_DONE pin transitioning high at the end of configuration, it resets the entire chain by transitioning its OE pin low. This low signal drives the OE pin low on the slave configuration device(s) and drives nSTATUS low on all Cyclone II devices, causing them to enter a reset state. This behavior is similar to the FPGA detecting an error in the configuration data.

Figure 13–17 shows how to configure multiple devices using cascaded EPC2 or EPC1 devices.

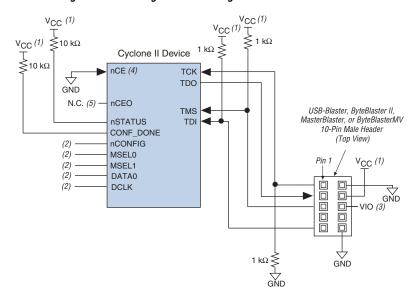

### Single Device JTAG Configuration

During JTAG configuration, you can use the USB-Blaster, MasterBlaster, ByteBlaster II, or ByteBlasterMV download cable to download data to the device. Configuring Cyclone II devices through a cable is similar to programming devices in system. Figure 13–22 shows JTAG configuration of a single Cyclone II device using a download cable.

Figure 13-22. JTAG Configuration of a Single Device Using a Download Cable

#### Notes to Figure 13-22:

- The pull-up resistor should be connected to the same supply voltage as the USB-Blaster, MasterBlaster (VIO pin), ByteBlaster II, or ByteBlasterMV cable.

- (2) Connect the nCONFIG and MSEL[1..0] pins to support a non-JTAG configuration scheme. If only JTAG configuration is used, connect the nCONFIG pin to V<sub>CC</sub>, and the MSEL[1..0] pins to ground. In addition, pull DCLK and DATAO to either high or low, whichever is convenient on your board.

- (3) Pin 6 of the header is a V<sub>IO</sub> reference voltage for the MasterBlaster output driver. V<sub>IO</sub> should match the device's V<sub>CCIO</sub>. Refer to the MasterBlaster Serial/USB Communications Cable Data Sheet for this value. In the ByteBlasterMV, this pin is a no connect. In the USB-Blaster and ByteBlaster II, this pin is connected to nCE when it is used for AS programming, otherwise it is a no connect.

- (4) nce must be connected to GND or driven low for successful JTAG configuration.

- (5) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

To configure a single device in a JTAG chain, the programming software places all other devices in BYPASS mode. In BYPASS mode, Cyclone II devices pass programming data from the TDI pin to the TDO pin through a single bypass register without being affected internally. This scheme

operate the TAP controller, and the  $\mathtt{TDI}$  and  $\mathtt{TDO}$  pins provide the serial path for the data registers. The  $\mathtt{TDI}$  pin also provides data to the instruction register, which then generates control logic for the data registers.

# IEEE Std. 1149.1 Boundary-Scan Register

The boundary-scan register is a large serial shift register that uses the TDI pin as an input and the TDO pin as an output. The boundary-scan register consists of 3-bit peripheral elements that are associated with Cyclone II I/O pins. You can use the boundary-scan register to test external pin connections or to capture internal data.

See the *Configuration & Testing* chapter in Volume 1 of the *Cyclone II Device Handbook* for the Cyclone II device boundary-scan register lengths.

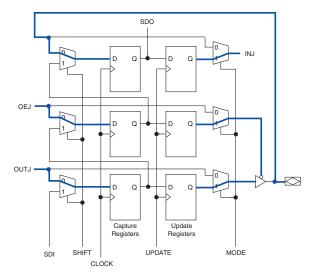

Figure 14–3 shows how test data is serially shifted around the periphery of the IEEE Std. 1149.1 device.

Figure 14-3. Boundary-Scan Register

# Boundary-Scan Cells of a Cyclone II Device I/O Pin

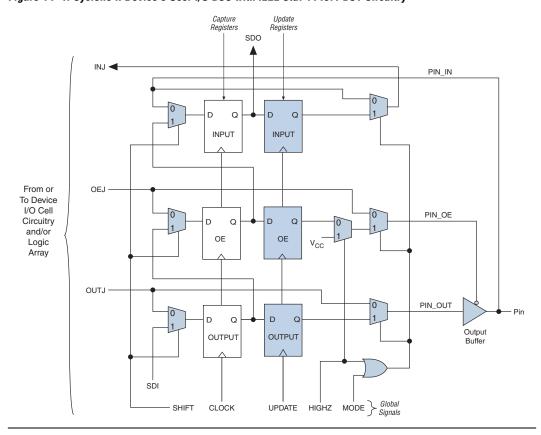

The Cyclone II device 3-bit boundary-scan cell (BSC) consists of a set of capture registers and a set of update registers. The capture registers can connect to internal device data via the OUTJ and OEJ signals, and connect

to external device data via the PIN\_IN signal, while the update registers connect to external data through the PIN\_OUT and PIN\_OE signals. The global control signals for the IEEE Std. 1149.1 BST registers (for example, shift, clock, and update) are generated internally by the TAP controller. The MODE signal is generated by a decode of the instruction register. The data signal path for the boundary-scan register runs from the serial data in (SDI) signal to the serial data out (SDO) signal. The scan register begins at the TDI pin and ends at the TDO pin of the device.

Figure 14–4 shows the Cyclone II device's user I/O boundary-scan cell.

Figure 14-4. Cyclone II Device's User I/O BSC with IEEE Std. 1149.1 BST Circuitry

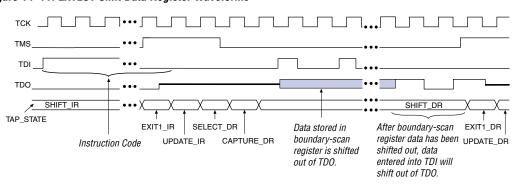

Figure 14–10 shows the capture, shift, and update phases of the EXTEST mode.

Figure 14-10. IEEE Std. 1149.1 BST EXTEST Mode

### **Capture Phase**

In the capture phase, the signals at the pin, OEJ and OUTJ, are loaded into the capture registers. The CLOCK signals are supplied by the TAP controller's CLOCKDR output. Previously retained data in the update registers drive the PIN\_IN, INJ, and allows the I/O pin to tri-state or drive a signal out.

A "1" in the OEJ update register tri-states the output buffer.

# **Shift & Update Phases**

In the shift phase, the previously captured signals at the pin, OEJ and OUTJ, are shifted out of the boundary-scan register via the TDO pin using CLOCK. As data is shifted out, the patterns for the next test can be shifted in via the TDI pin.

In the update phase, data is transferred from the capture registers to the update registers using the UPDATE clock. The update registers then drive the PIN\_IN, INJ, and allow the I/O pin to tristate or drive a signal out.

EXTEST selects data differently than SAMPLE/PRELOAD. EXTEST chooses data from the update registers as the source of the output and output enable signals. Once the EXTEST instruction code is entered, the multiplexers select the update register data. Thus, data stored in these registers from a previous EXTEST or SAMPLE/PRELOAD test cycle can be forced onto the pin signals. In the capture phase, the results of this test data are stored in the capture registers, then shifted out of TDO during the shift phase. New test data can then be stored in the update registers during the update phase.

The EXTEST waveform diagram in Figure 14–11 resembles the SAMPLE/PRELOAD waveform diagram, except for the instruction code. The data shifted out of TDO consists of the data that was present in the capture registers after the capture phase. New test data shifted into the TDI pin appears at the TDO pin after being clocked through the entire boundary-scan register.

Figure 14-11. EXTEST Shift Data Register Waveforms

#### **BYPASS Instruction Mode**

The BYPASS mode is activated when an instruction code of all 1's is loaded in the instruction register. The waveforms in Figure 14–12 show how scan data passes through a device once the TAP controller is in the SHIFT\_DR state. In this state, data signals are clocked into the bypass register from TDI on the rising edge of TCK and out of TDO on the falling edge of the same clock pulse.