Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 516                                                     |

| Number of Logic Elements/Cells | 8256                                                    |

| Total RAM Bits                 | 165888                                                  |

| Number of I/O                  | 182                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                      |

| Package / Case                 | 256-LBGA                                                |

| Supplier Device Package        | 256-FBGA (17x17)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c8f256i8n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1. Introduction

CII51001-3.2

#### Introduction

Following the immensely successful first-generation Cyclone® device family, Altera® Cyclone II FPGAs extend the low-cost FPGA density range to 68,416 logic elements (LEs) and provide up to 622 usable I/O pins and up to 1.1 Mbits of embedded memory. Cyclone II FPGAs are manufactured on 300-mm wafers using TSMC's 90-nm low-k dielectric process to ensure rapid availability and low cost. By minimizing silicon area, Cyclone II devices can support complex digital systems on a single chip at a cost that rivals that of ASICs. Unlike other FPGA vendors who compromise power consumption and performance for low-cost, Altera's latest generation of low-cost FPGAs—Cyclone II FPGAs, offer 60% higher performance and half the power consumption of competing 90-nm FPGAs. The low cost and optimized feature set of Cyclone II FPGAs make them ideal solutions for a wide array of automotive, consumer, communications, video processing, test and measurement, and other end-market solutions. Reference designs, system diagrams, and IP, found at www.altera.com, are available to help you rapidly develop complete end-market solutions using Cyclone II FPGAs.

#### **Low-Cost Embedded Processing Solutions**

Cyclone II devices support the Nios II embedded processor which allows you to implement custom-fit embedded processing solutions. Cyclone II devices can also expand the peripheral set, memory, I/O, or performance of embedded processors. Single or multiple Nios II embedded processors can be designed into a Cyclone II device to provide additional co-processing power or even replace existing embedded processors in your system. Using Cyclone II and Nios II together allow for low-cost, high-performance embedded processing solutions, which allow you to extend your product's life cycle and improve time to market over standard product solutions.

#### **Low-Cost DSP Solutions**

Use Cyclone II FPGAs alone or as DSP co-processors to improve price-to-performance ratios for digital signal processing (DSP) applications. You can implement high-performance yet low-cost DSP systems with the following Cyclone II features and design support:

- Up to  $150 18 \times 18$  multipliers

- Up to 1.1 Mbit of on-chip embedded memory

- High-speed interfaces to external memory

#### **Dedicated Clock Pins**

Larger Cyclone II devices (EP2C15 and larger devices) have 16 dedicated clock pins (CLK [15..0], four pins on each side of the device). Smaller Cyclone II devices (EP2C5 and EP2C8 devices) have eight dedicated clock pins (CLK [7..0], four pins on left and right sides of the device). These CLK pins drive the global clock network (GCLK), as shown in Figures 2–11 and 2–12.

If the dedicated clock pins are not used to feed the global clock networks, they can be used as general-purpose input pins to feed the logic array using the MultiTrack interconnect. However, if they are used as general-purpose input pins, they do not have support for an I/O register and must use LE-based registers in place of an I/O register.

#### **Dual-Purpose Clock Pins**

Cyclone II devices have either 20 dual-purpose clock pins, DPCLK [19..0] or 8 dual-purpose clock pins, DPCLK [7..0]. In the larger Cyclone II devices (EP2C15 devices and higher), there are 20 DPCLK pins; four on the left and right sides and six on the top and bottom of the device. The corner CDPCLK pins are first multiplexed before they drive into the clock control block. Since the signals pass through a multiplexer before feeding the clock control block, these signals incur more delay to the clock control block than other DPCLK pins that directly feed the clock control block. In the smaller Cyclone II devices (EP2C5 and EP2C8 devices), there are eight DPCLK pins; two on each side of the device (see Figures 2–11 and 2–12).

A programmable delay chain is available from the DPCLK pin to its fanout destinations. To set the propagation delay from the DPCLK pin to its fan-out destinations, use the **Input Delay from Dual-Purpose Clock Pin to Fan-Out Destinations** assignment in the Quartus II software.

These dual-purpose pins can connect to the global clock network for high-fanout control signals such as clocks, asynchronous clears, presets, and clock enables, or protocol control signals such as TRDY and IRDY for PCI, or DQS signals for external memory interfaces.

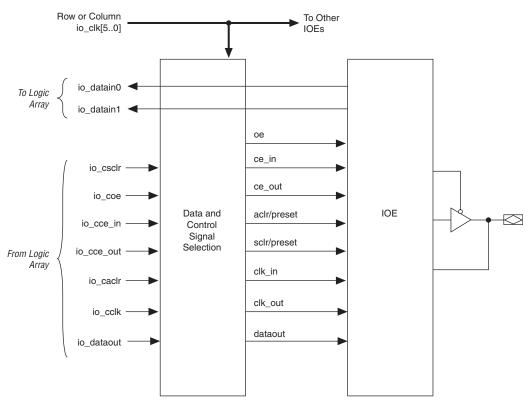

The pin's datain signals can drive the logic array. The logic array drives the control and data signals, providing a flexible routing resource. The row or column IOE clocks, io\_clk[5..0], provide a dedicated routing resource for low-skew, high-speed clocks. The global clock network generates the IOE clocks that feed the row or column I/O regions (see "Global Clock Network & Phase-Locked Loops" on page 2–16). Figure 2–23 illustrates the signal paths through the I/O block.

Figure 2-23. Signal Path Through the I/O Block

Each IOE contains its own control signal selection for the following control signals: oe, ce\_in, ce\_out, aclr/preset, sclr/preset, clk\_in, and clk\_out. Figure 2–24 illustrates the control signal selection.

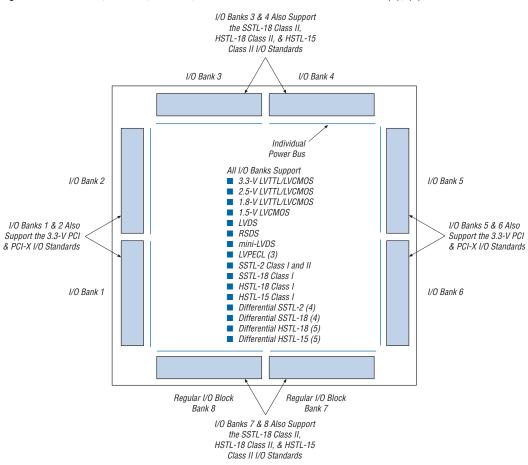

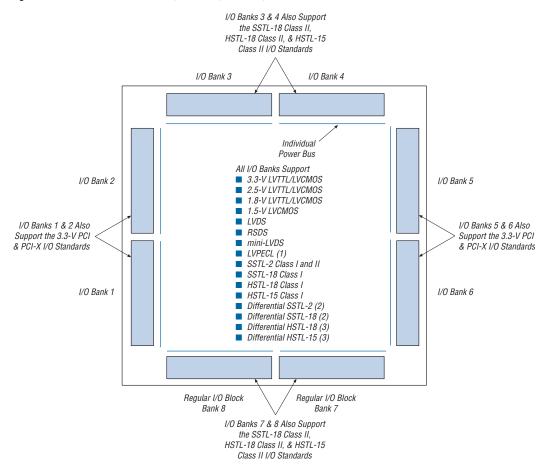

Figure 2–29. EP2C15, EP2C20, EP2C35, EP2C50 & EP2C70 I/O Banks Notes (1), (2)

#### Notes to Figure 2–29:

- (1) This is a top view of the silicon die.

- (2) This is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (5) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

Each I/O bank has its own VCCIO pins. A single device can support 1.5-V, 1.8-V, 2.5-V, and 3.3-V interfaces; each individual bank can support a different standard with different I/O voltages. Each bank also has dual-purpose VREF pins to support any one of the voltage-referenced

#### **Devices Can Be Driven before Power-Up**

You can drive signals into the I/O pins, dedicated input pins, and dedicated clock pins of Cyclone II devices before or during power-up or power-down without damaging the device. Cyclone II devices support any power-up or power-down sequence ( $V_{\text{CCIO}}$  and  $V_{\text{CCINT}}$ ) to simplify system level design.

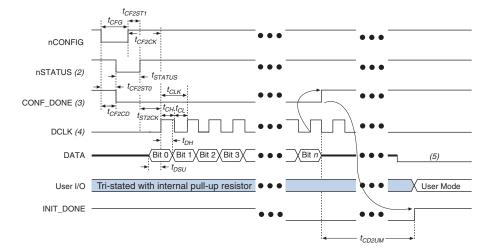

#### I/O Pins Remain Tri-Stated during Power-Up

A device that does not support hot socketing may interrupt system operation or cause contention by driving out before or during power-up. In a hot-socketing situation, the Cyclone II device's output buffers are turned off during system power-up or power-down. The Cyclone II device also does not drive out until the device is configured and has attained proper operating conditions. The I/O pins are tri-stated until the device enters user mode with a weak pull-up resistor (R) to 3.3V. Refer to Figure 4–1 for more information.

You can power up or power down the  $V_{\rm CCIO}$  and  $V_{\rm CCINT}$  pins in any sequence. The  $V_{\rm CCIO}$  and  $V_{\rm CCINT}$  must have monotonic rise to their steady state levels. (Refer to Figure 4–3 for more information.) The power supply ramp rates can range from 100  $\mu s$  to 100 ms for non "A" devices. Both  $V_{\rm CC}$  supplies must power down within 100 ms of each other to prevent I/O pins from driving out. During hot socketing, the I/O pin capacitance is less than 15 pF and the clock pin capacitance is less than 20 pF. Cyclone II devices meet the following hot-socketing specification.

- The hot-socketing DC specification is  $|I_{IOPIN}| < 300 \,\mu\text{A}$ .

- The hot-socketing AC specification is  $\mid$  I<sub>IOPIN</sub>  $\mid$  < 8 mA for 10 ns or less.

This specification takes into account the pin capacitance but not board trace and external loading capacitance. You must consider additional capacitance for trace, connector, and loading separately.

$I_{IOPIN}$  is the current at any user I/O pin on the device. The DC specification applies when all  $V_{CC}$  supplies to the device are stable in the powered-up or powered-down conditions. For the AC specification, the peak current duration due to power-up transients is 10 ns or less.

A possible concern for semiconductor devices in general regarding hot socketing is the potential for latch-up. Latch-up can occur when electrical subsystems are hot socketed into an active system. During hot socketing, the signal pins may be connected and driven by the active system before

| Table 5–42. Cyclone | Table 5–42. Cyclone II I/O Output Delay for Column Pins (Part 5 of 6) |                  |                           |                 |                      |             |             |                |      |

|---------------------|-----------------------------------------------------------------------|------------------|---------------------------|-----------------|----------------------|-------------|-------------|----------------|------|

|                     | Drive                                                                 | _                | Fast Co                   | rner            | –6<br>Speed<br>Grade | -7<br>Speed | -7<br>Speed | -8             |      |

| I/O Standard        | Strength                                                              | Parameter        | Industrial/<br>Automotive | Commer<br>-cial |                      | Grade (2)   | Grade St    | Speed<br>Grade | Unit |

| DIFFERENTIAL_       | 6 mA                                                                  | t <sub>OP</sub>  | 1472                      | 1544            | 3140                 | 3345        | 3542        | 3549           | ps   |

| SSTL_18_CLASS_I     |                                                                       | t <sub>DIP</sub> | 1604                      | 1683            | 3310                 | 3539        | 3768        | 3768           | ps   |

|                     | 8 mA                                                                  | t <sub>OP</sub>  | 1469                      | 1541            | 3086                 | 3287        | 3482        | 3489           | ps   |

|                     |                                                                       | t <sub>DIP</sub> | 1601                      | 1680            | 3256                 | 3481        | 3708        | 3708           | ps   |

|                     | 10 mA                                                                 | t <sub>OP</sub>  | 1466                      | 1538            | 2980                 | 3171        | 3354        | 3361           | ps   |

|                     |                                                                       | t <sub>DIP</sub> | 1598                      | 1677            | 3150                 | 3365        | 3580        | 3580           | ps   |

|                     | 12 mA                                                                 | t <sub>OP</sub>  | 1466                      | 1538            | 2980                 | 3171        | 3354        | 3361           | ps   |

|                     | (1)                                                                   | t <sub>DIP</sub> | 1598                      | 1677            | 3150                 | 3365        | 3580        | 3580           | ps   |

| DIFFERENTIAL_       | 16 mA                                                                 | t <sub>OP</sub>  | 1454                      | 1525            | 2905                 | 3088        | 3263        | 3270           | ps   |

| SSTL_18_CLASS_II    |                                                                       | t <sub>DIP</sub> | 1586                      | 1664            | 3075                 | 3282        | 3489        | 3489           | ps   |

|                     | 18 mA<br>(1)                                                          | t <sub>OP</sub>  | 1453                      | 1524            | 2900                 | 3082        | 3257        | 3264           | ps   |

|                     |                                                                       | t <sub>DIP</sub> | 1585                      | 1663            | 3070                 | 3276        | 3483        | 3483           | ps   |

| 1.8V_DIFFERENTIAL   | 8 mA                                                                  | t <sub>OP</sub>  | 1460                      | 1531            | 3222                 | 3424        | 3618        | 3625           | ps   |

| _HSTL_CLASS_I       |                                                                       | t <sub>DIP</sub> | 1592                      | 1670            | 3392                 | 3618        | 3844        | 3844           | ps   |

|                     | 10 mA                                                                 | t <sub>OP</sub>  | 1462                      | 1534            | 3090                 | 3279        | 3462        | 3469           | ps   |

|                     |                                                                       | t <sub>DIP</sub> | 1594                      | 1673            | 3260                 | 3473        | 3688        | 3688           | ps   |

|                     | 12 mA                                                                 | t <sub>OP</sub>  | 1462                      | 1534            | 3090                 | 3279        | 3462        | 3469           | ps   |

|                     | (1)                                                                   | t <sub>DIP</sub> | 1594                      | 1673            | 3260                 | 3473        | 3688        | 3688           | ps   |

| 1.8V_DIFFERENTIAL   | 16 mA                                                                 | t <sub>OP</sub>  | 1449                      | 1520            | 2936                 | 3107        | 3271        | 3278           | ps   |

| _HSTL_CLASS_II      |                                                                       | t <sub>DIP</sub> | 1581                      | 1659            | 3106                 | 3301        | 3497        | 3497           | ps   |

|                     | 18 mA                                                                 | t <sub>OP</sub>  | 1450                      | 1521            | 2924                 | 3101        | 3272        | 3279           | ps   |

|                     |                                                                       | t <sub>DIP</sub> | 1582                      | 1660            | 3094                 | 3295        | 3498        | 3498           | ps   |

|                     | 20 mA                                                                 | t <sub>OP</sub>  | 1452                      | 1523            | 2926                 | 3096        | 3259        | 3266           | ps   |

|                     | (1)                                                                   | t <sub>DIP</sub> | 1584                      | 1662            | 3096                 | 3290        | 3485        | 3485           | ps   |

| 1.5V_DIFFERENTIAL   | 8 mA                                                                  | t <sub>OP</sub>  | 1779                      | 1866            | 4292                 | 4637        | 4974        | 4981           | ps   |

| _HSTL_CLASS_I       |                                                                       | t <sub>DIP</sub> | 1911                      | 2005            | 4462                 | 4831        | 5200        | 5200           | ps   |

|                     | 10 mA                                                                 | t <sub>OP</sub>  | 1784                      | 1872            | 4031                 | 4355        | 4673        | 4680           | ps   |

|                     |                                                                       | t <sub>DIP</sub> | 1916                      | 2011            | 4201                 | 4549        | 4899        | 4899           | ps   |

|                     | 12 mA                                                                 | t <sub>OP</sub>  | 1784                      | 1872            | 4031                 | 4355        | 4673        | 4680           | ps   |

|                     | (1)                                                                   | t <sub>DIP</sub> | 1916                      | 2011            | 4201                 | 4549        | 4899        | 4899           | ps   |

| Table 5–45. Maximum Output Clock Toggle Rate on Cyclone II Devices (Part 4 of 4) |                 |                                                              |                      |                      |                      |                      |                      |                            |                      |                      |

|----------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------------|----------------------|----------------------|

|                                                                                  |                 | Maximum Output Clock Toggle Rate on Cyclone II Devices (MHz) |                      |                      |                      |                      |                      |                            |                      | VIHz)                |

| I/O Standard                                                                     | Drive           | Column I/O Pins (1)                                          |                      |                      | Row                  | / I/O Pin            | s (1)                | Dedicated Clock<br>Outputs |                      |                      |

| ·                                                                                | Strength        | -6<br>Speed<br>Grade                                         | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade       | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade |

| 1.5V_                                                                            | 8 mA            | 210                                                          | 170                  | 140                  | 210                  | 170                  | 140                  | 210                        | 170                  | 140                  |

| DIFFERENTIAL_HSTL<br>_CLASS_I                                                    | 10 mA           | 220                                                          | 180                  | 150                  | _                    | _                    | _                    | _                          | _                    | _                    |

| _0LA00_1                                                                         | 12 mA           | 230                                                          | 190                  | 160                  | _                    | _                    | _                    | _                          | _                    | _                    |

| 1.5V_<br>DIFFERENTIAL_HSTL<br>_CLASS_II                                          | 16 mA           | 210                                                          | 170                  | 140                  | _                    | _                    | _                    | _                          | _                    | _                    |

| LVDS                                                                             | _               | 400                                                          | 340                  | 280                  | 400                  | 340                  | 280                  | 400                        | 340                  | 280                  |

| RSDS                                                                             | _               | 400                                                          | 340                  | 280                  | 400                  | 340                  | 280                  | 400                        | 340                  | 280                  |

| MINI_LVDS                                                                        | _               | 400                                                          | 340                  | 280                  | 400                  | 340                  | 280                  | 400                        | 340                  | 280                  |

| SIMPLE_RSDS                                                                      | _               | 380                                                          | 320                  | 260                  | 380                  | 320                  | 260                  | 380                        | 320                  | 260                  |

| 1.2V_HSTL                                                                        | _               | 80                                                           | 80                   | 80                   | _                    | _                    | _                    | _                          | _                    | _                    |

| 1.2V_<br>DIFFERENTIAL_HSTL                                                       | _               | 80                                                           | 80                   | 80                   | _                    | _                    | _                    | _                          | _                    | _                    |

| PCI                                                                              | _               | _                                                            | _                    | _                    | 350                  | 315                  | 280                  | 350                        | 315                  | 280                  |

| PCI-X                                                                            | _               | _                                                            | _                    | _                    | 350                  | 315                  | 280                  | 350                        | 315                  | 280                  |

| LVTTL                                                                            | OCT_25_<br>OHMS | 360                                                          | 300                  | 250                  | 360                  | 300                  | 250                  | 360                        | 300                  | 250                  |

| LVCMOS                                                                           | OCT_25_<br>OHMS | 360                                                          | 300                  | 250                  | 360                  | 300                  | 250                  | 360                        | 300                  | 250                  |

| 2.5V                                                                             | OCT_50_<br>OHMS | 240                                                          | 200                  | 160                  | 240                  | 200                  | 160                  | 240                        | 200                  | 160                  |

| 1.8V                                                                             | OCT_50_<br>OHMS | 290                                                          | 240                  | 200                  | 290                  | 240                  | 200                  | 290                        | 240                  | 200                  |

| SSTL_2_CLASS_I                                                                   | OCT_50_<br>OHMS | 240                                                          | 200                  | 160                  | 240                  | 200                  | 160                  | _                          | _                    | _                    |

| SSTL_18_CLASS_I                                                                  | OCT_50_<br>OHMS | 290                                                          | 240                  | 200                  | 290                  | 240                  | 200                  | _                          | _                    | _                    |

Note to Table 5–45:

(1) This is based on single data rate I/Os.

| Table 5–46. Maximum Output Clock Toggle Rate Derating Factors (Part 2 of 4) |          |                                                           |                      |                      |                      |                      |                      |                            |                      |                      |  |

|-----------------------------------------------------------------------------|----------|-----------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------------|----------------------|----------------------|--|

|                                                                             |          | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |                      |                      |                      |                      |                      |                            |                      |                      |  |

| I/O Standard                                                                | Drive    | Column I/O Pins                                           |                      |                      | Row I/O Pins         |                      |                      | Dedicated Clock<br>Outputs |                      |                      |  |

|                                                                             | Strength | –6<br>Speed<br>Grade                                      | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade       | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade |  |

| SSTL_2_CLASS_II                                                             | 16 mA    | 42                                                        | 43                   | 45                   | 15                   | 29                   | 42                   | 15                         | 29                   | 42                   |  |

|                                                                             | 20 mA    | 41                                                        | 42                   | 44                   | _                    | _                    | _                    | _                          | _                    | _                    |  |

|                                                                             | 24 mA    | 40                                                        | 42                   | 43                   | _                    | _                    | _                    | _                          | _                    | _                    |  |

| SSTL_18_                                                                    | 6 mA     | 20                                                        | 22                   | 24                   | 46                   | 47                   | 49                   | 46                         | 47                   | 49                   |  |

| CLASS_I                                                                     | 8 mA     | 20                                                        | 22                   | 24                   | 47                   | 49                   | 51                   | 47                         | 49                   | 51                   |  |

|                                                                             | 10 mA    | 20                                                        | 22                   | 25                   | 23                   | 25                   | 27                   | 23                         | 25                   | 27                   |  |

|                                                                             | 12 mA    | 19                                                        | 23                   | 26                   | _                    | _                    | _                    | _                          | _                    |                      |  |

| SSTL_18_ CLASS_II                                                           | 16 mA    | 30                                                        | 33                   | 36                   | _                    | _                    | _                    | _                          | _                    | _                    |  |

|                                                                             | 18 mA    | 29                                                        | 29                   | 29                   | _                    | _                    | _                    | _                          | _                    | _                    |  |

| 1.8V_HSTL_ CLASS_I                                                          | 8 mA     | 26                                                        | 28                   | 29                   | 59                   | 61                   | 63                   | 59                         | 61                   | 63                   |  |

|                                                                             | 10 mA    | 46                                                        | 47                   | 48                   | 65                   | 66                   | 68                   | 65                         | 66                   | 68                   |  |

|                                                                             | 12 mA    | 67                                                        | 67                   | 67                   | 71                   | 71                   | 72                   | 71                         | 71                   | 72                   |  |

| 1.8V_HSTL_ CLASS_II                                                         | 16 mA    | 62                                                        | 65                   | 68                   | _                    | _                    | _                    | _                          | _                    | _                    |  |

|                                                                             | 18 mA    | 59                                                        | 62                   | 65                   | _                    | _                    | _                    | _                          | _                    | _                    |  |

|                                                                             | 20 mA    | 57                                                        | 59                   | 62                   | _                    | _                    | _                    | _                          | _                    | _                    |  |

| 1.5V_HSTL_ CLASS_I                                                          | 8 mA     | 40                                                        | 40                   | 41                   | 28                   | 32                   | 36                   | 28                         | 32                   | 36                   |  |

|                                                                             | 10 mA    | 41                                                        | 42                   | 42                   | _                    | _                    | _                    | _                          | _                    | _                    |  |

|                                                                             | 12 mA    | 43                                                        | 43                   | 43                   | _                    | _                    | _                    | _                          | _                    | _                    |  |

| 1.5V_HSTL_ CLASS_II                                                         | 16 mA    | 18                                                        | 20                   | 21                   | _                    | _                    | _                    | _                          | _                    | _                    |  |

| DIFFERENTIAL_SSTL_2                                                         | 8 mA     | 46                                                        | 47                   | 49                   | 25                   | 40                   | 56                   | 25                         | 40                   | 56                   |  |

| _CLASS_I                                                                    | 12 mA    | 67                                                        | 69                   | 70                   | 23                   | 42                   | 60                   | 23                         | 42                   | 60                   |  |

| DIFFERENTIAL_SSTL_2                                                         | 16 mA    | 42                                                        | 43                   | 45                   | 15                   | 29                   | 42                   | 15                         | 29                   | 42                   |  |

| _CLASS_II                                                                   | 20 mA    | 41                                                        | 42                   | 44                   |                      |                      | _                    |                            |                      |                      |  |

|                                                                             | 24 mA    | 40                                                        | 42                   | 43                   | _                    |                      | _                    |                            |                      | _                    |  |

| DIFFERENTIAL_SSTL_                                                          | 6 mA     | 20                                                        | 22                   | 24                   | 46                   | 47                   | 49                   | 46                         | 47                   | 49                   |  |

| 18_CLASS_I                                                                  | 8 mA     | 20                                                        | 22                   | 24                   | 47                   | 49                   | 51                   | 47                         | 49                   | 51                   |  |

|                                                                             | 10 mA    | 20                                                        | 22                   | 25                   | 23                   | 25                   | 27                   | 23                         | 25                   | 27                   |  |

|                                                                             | 12 mA    | 19                                                        | 23                   | 26                   | _                    | _                    | _                    | _                          | _                    | _                    |  |

Tables 7–4 and 7–5 describe the Cyclone II PLL input and output ports.

| Port      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Source                     | Destination        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------|

| inclk[10] | Primary and secondary clock inputs to the PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Dedicated clock input pins | n counter          |

| pllena    | pllena is an active high signal that acts as an enable and reset signal for the PLL. It can be used for enabling or disabling each PLL. When pllena transitions low, the PLL clock output ports are driven to GND and the PLL loses lock. Once pllena transitions high again, the lock process begins and the PLL re-synchronizes to its input reference clock. The pllena port can be driven by an LE output or any general-purpose I/O pin.                                                                                                                            | Logic array or input pin   | PLL control signal |

| areset    | areset is an active high signal that resets all PLL counters to their initial values. When this signal is driven high the PLL resets its counters, clears the PLL outputs and loses lock. Once this signal is driven low again, the lock process begins and the PLL re-synchronizes to its input reference clock. The areset port can be driven by an LE output or any general-purpose I/O pin.                                                                                                                                                                          | Logic array or input pin   | PLL control signal |

| pfdena    | pfdena is an active high signal that enables or disables the up/down output signals from the PFD. When pfdena is driven low, the PFD is disabled, while the VCO continues to operate. The PLL clock outputs continue to toggle regardless of the input clock, but may experience some long-term drift. Because the output clock frequency does not change for some time, you can use the pfdena port as a shutdown or cleanup function when a reliable input clock is no longer available. The pfdena port can be driven by an LE output or any general-purpose I/O pin. | Logic array or input pin   | PFD                |

| clkswitch | clkswitch is an active high switchover signal used to initiate manual clock switchover.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Logic array or input pin   | PLL control signal |

| Table 7–6. I/O Standards Supported for Cyclone II PLLs (Part 2 of 2) |          |      |         |  |  |

|----------------------------------------------------------------------|----------|------|---------|--|--|

| Input Output                                                         |          |      |         |  |  |

| I/O Standard                                                         | inclk    | lock | pll_out |  |  |

| SSTL-25 class II                                                     | <b>✓</b> | ✓    | ✓       |  |  |

| RSDS/mini-LVDS (4)                                                   |          | ✓    | ✓       |  |  |

#### Notes to Table 7-6:

- (1) The PCI-X I/O standard is supported only on side I/O pins.

- (2) Differential SSTL and HSTL outputs are only supported on the PLL<#>\_OUT pins.

- (3) These I/O standards are only supported on top and bottom I/O pins.

- (4) The RSDS and mini-LVDS pins are only supported on output pins.

### Clock Feedback Modes

Cyclone II PLLs support four clock feedback modes: normal mode, zero delay buffer mode, no compensation mode, and source synchronous mode. Cyclone II PLLs do not have support for external feedback mode. All the supported clock feedback modes allow for multiplication and division, phase shifting, and programmable duty cycle. The phase relationships shown in the waveforms in Figures 7–4 through 7–6 are for the default (zero degree) phase shift setting. Changing the phase-shift setting changes the relationships between the output clocks from the PLL.

#### **Normal Mode**

In normal mode, the PLL phase-aligns the input reference clock with the clock signal at the ports of the registers in the logic array I/O registers to compensate for the internal global clock network delay. Use the altpl1 megafunction in the Quartus II software to define which internal clock output from the PLL (c0, c1, or c2) to compensate for.

If an external clock output pin (PLL<#>\_OUT) is used in this mode, there is a phase shift with respect to the clock input pin. Similarly, if the internal PLL clock outputs are used to drive general-purpose I/O pins, there is be phase shift with respect to the clock input pin.

Figure 7–4 shows an example waveform of the PLL clocks' phase relationship in this mode.

#### Manual Clock Switchover

The Cyclone II PLLs support manual switchover of the reference clock through internal logic. This enables you to switch between two reference input clocks. Use this feature for a dual clock domain application such as in a system that turns on the redundant clock if the primary clock stops running.

Figure 7–10 shows how the PLL input clock ( $f_{\rm IN}$ ) is generated from one of four possible clock sources. The first stage multiplexing consists of two dedicated multiplexers that generate two single-ended or two differential clocks from four dedicated clock pins. These clock signals are then multiplexed to generate  $f_{\rm IN}$  by using another dedicated 2-to-1 multiplexer. The first stage multiplexers are controlled by configuration bit settings in the configuration file generated by the Quartus II software, while the second stage multiplexer is either controlled by the configuration bit settings or logic array signal to allow the  $f_{\rm IN}$  to be controlled dynamically. This allows the implementation of a manual clock switchover circuit where the PLL reference clock can be switched during user mode for applications that requires clock redundancy.

$\begin{array}{c} \text{CLK}[n+3] \\ \text{CLK}[n+2] \\ \text{CLK}[n+1] \\ \text{CLK}[n] \end{array}$

Figure 7-10. Cyclone II PLL Input Clock Generation

Notes to Figure 7-10:

- (1) This select line is set through the configuration file.

- (2) This select line can either be set through the configuration file or it can be dynamically set in user mode when using the manual switchover feature.

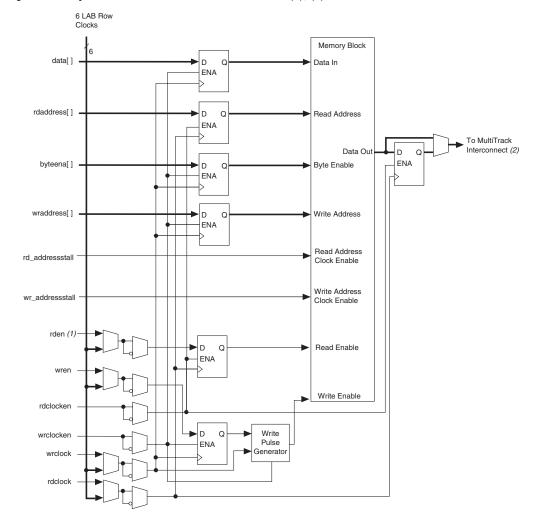

Figure 8–17. Cyclone II Read/Write Clock Mode Notes (1), (2)

#### Notes to Figure 8–17:

- (1) Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

- (2) For more information about the MultiTract interconnect, refer to Cyclone II Device Family Data Sheet in volume 1 of the Cyclone II Device Handbook.

#### Single-Clock Mode

Cyclone II memory blocks support single-clock mode for true dual-port, simple dual-port, and single-port memory. In this mode, a single clock, together with a clock enable, controls all registers of the memory block. This mode does not support asynchronous clear signals for the registers. Figures 8–18 through 8–20 show the memory block in single-clock mode for true dual-port, simple dual-port, and single-port modes, respectively.

The DQS pins are listed in the Cyclone II pin tables as DQS[1..0]T, DQS[1..0]B, DQS[1..0]B, DQS[1..0]B, and DQS[1..0]B for the EP2C5 and EP2C8 devices and DQS[5..0]T, DQS[5..0]B, DQS[3..0]L, and DQS[3..0]B for the larger devices. The T denotes pins on the top of the device, the B denotes pins on the bottom of the device, the L denotes pins on the left of the device, and the R denotes pins on the right of the device. The corresponding DQ pins are marked as DQ[5..0]T[8..0], where [5..0] indicates which DQS group the pins belong to.

In the Cyclone II pinouts, the DQ groups with 9 DQ pins are also used in the  $\times 8$  mode with the corresponding DQS pins, leaving the unused DQ pin available as a regular I/O pin. The DQ groups that have 18 DQ pins are also used in the  $\times 16$  mode with the corresponding DQS pins, leaving the two unused DQ pins available as regular I/O pins. For example, DQ1T[8..0] can be used in the  $\times 8$  mode, provided it is used with DQS1T. The remaining unused DQ pin, DQ1T8, is available as a regular I/O pin.

When not used as DQ or DQS pins, these pins are available as regular I/O pins. Table 9–3 shows the number of DQS pins supported in each I/O bank in each Cyclone II device density.

| Table 9–3. Available DQS Pins in Each I/O Bank & Each Device       Note (1) |              |                 |               |                |  |  |  |

|-----------------------------------------------------------------------------|--------------|-----------------|---------------|----------------|--|--|--|

| Device                                                                      | Top I/O Bank | Bottom I/O Bank | Left I/O Bank | Right I/O Bank |  |  |  |

| EP2C5, EP2C8                                                                | DQS[10]T     | DQS[10]B        | DQS[10]L      | DQS[10]R       |  |  |  |

| EP2C15, EP2C20,<br>EP2C35, EP2C50,<br>EP2C70                                | DQS[50]B     | DQS[50]T        | DQS[30]L      | DQS[30]R       |  |  |  |

Note to Table 9-3:

(1) Numbers are preliminary.

The DQ pin numbering is based on ×8/×9 mode. There are up to 8 DQS/DQ groups in ×8 mode or 4 DQS/DQ groups in ×9 mode in I/O banks for EP2C5 and EP2C8. For the larger devices, there are up to 20 DQS/DQ groups in ×8 mode or 8 DQS/DQ groups in ×9 mode. Although there are up to 20 DQS/DQ groups in the ×8 mode available in the larger Cyclone II devices, but because of the available clock resources in the Cyclone II devices, only 16 DQS/DQ groups can be utilized for the external memory interface. There is a total of 16 global clock buses available for routing DQS signals but 2 of them are needed for routing the –90° write clock and the system clock to the external memory devices. This reduces the global clock resources to 14 global clock buses for routing DQS signals. Incoming DQS signals are all routed to the clock control block, and are then routed to the global clock bus to clock the DDR LE registers. For EP2C5 and EP2C8 devices, the DQS signals are routed

# Document Revision History

Table 9–4 shows the revision history for this document.

| Table 9–4. Document Revision History |                                                                                                                                                                                                                                          |                                                                                |  |  |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|

| Date &<br>Document<br>Version        | Changes Made                                                                                                                                                                                                                             | Summary of Changes                                                             |  |  |  |  |

| February 2007<br>v3.1                | <ul> <li>Added document revision history.</li> <li>Added handpara note in "Data &amp; Data Strobe Pins" section.</li> <li>Updated "DDR Output Registers" section.</li> </ul>                                                             | Elaboration of DDR2 and<br>QDRII interfaces supported<br>by I/O bank included. |  |  |  |  |

| November<br>2005, v2.1               | <ul><li>Introduction</li><li>Updated Table 9–2.</li><li>Updated Figure 9–7.</li></ul>                                                                                                                                                    |                                                                                |  |  |  |  |

| July 2005, v2.0                      | Updated Table 9–2.                                                                                                                                                                                                                       |                                                                                |  |  |  |  |

| November<br>2004, v1.1               | <ul> <li>Moved the "External Memory Interface Standards" section to follow the "Introduction" section.</li> <li>Updated the "Data &amp; Data Strobe Pins" section.</li> <li>Updated Figures 9–11, 9–12, 9–15, 9–16, and 9–17.</li> </ul> |                                                                                |  |  |  |  |

| June 2004, v1.0                      | Added document to the Cyclone II Device Handbook.                                                                                                                                                                                        |                                                                                |  |  |  |  |

## Referenced Documents

This chapter references the following documents:

- Altera Reliability Report

- AN 75: High-Speed Board Designs

- Cyclone II Architecture chapter in volume 1 of the Cyclone II Device Handbook

- Cyclone II Device Family Data Sheet, section 1 of the Cyclone II Device Handbook

- DC Characteristics and Timing Specifications chapter in volume 1 of the Cyclone II Device Handbook

- External Memory Interfaces chapter in volume 1 of the Cyclone II Device Handbook

- High Speed Differential Interfaces in Cyclone II Devices chapter in volume 1 of the Cyclone II Device Handbook

- Hot Socketing & Power-On Reset chapter in volume 1 of the Cyclone II Device Handbook

- I/O Management chapter in volume 2 of the Quartus II Handbook

## Document Revision History

Table 10–13 shows the revision history for this document.

| Table 10-13. D                  | Table 10–13. Document Revision History                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                 | Summary of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| February 2008<br>v2.4           | <ul> <li>Added "Referenced Documents" section.</li> <li>Updated "Differential Pad Placement<br/>Guidelines" section.</li> </ul>                                                                                                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| February 2007<br>v2.3           | <ul> <li>Added document revision history.</li> <li>Updated "Introduction" and its feetpara note.</li> <li>Updated Note (2) in Table 10–4.</li> <li>Updated "Differential LVPECL" section.</li> <li>Updated "Differential Pad Placement Guidelines" section.</li> <li>Updated "Output Pads" section.</li> <li>Added new section "5.0-V Device Compatibility" with two new figures.</li> </ul> | <ul> <li>Added reference detail for ESD specifications.</li> <li>Added information about differential placement restrictions applying only to pins in the same bank.</li> <li>Added information that Cyclone II device supports LVDS on clock inputs at 3.3V V<sub>CCIO</sub>.</li> <li>Added more information on DC placement guidelines.</li> <li>Added information stating SSTL and HSTL outputs can be closer than 2 pads from V<sub>REF</sub>.</li> <li>Added 5.0 Device tolerence solution.</li> </ul> |  |  |  |  |  |  |

Figure 11–2. I/O Banks in EP2C15, EP2C20, EP2C35, EP2C50 & EP2C70 Devices

#### Notes to Figure 11-2:

- The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (2) The differential SSTL-18 and SSTL-2 I/O standards are only supported on clock input pins and PLL output clock pins.

- (3) The differential 1.8-V and 1.5-V HSTL I/O standards are only supported on clock input pins and PLL output clock pins.

## Cyclone II High-Speed I/O Interface

Cyclone II devices provide a multi-protocol interface that allows communication between a variety of I/O standards, including LVDS, LVPECL, RSDS, mini-LVDS, differential HSTL, and differential SSTL. This feature makes the Cyclone II device family ideal for applications that require multiple I/O standards, such as protocol translation.

#### PS Configuration Timing

A PS configuration must meet the setup and hold timing parameters and the maximum clock frequency. When using a microprocessor or another intelligent host to control the PS interface, ensure that you meet these timing requirements.

Figure 13–12 shows the timing waveform for PS configuration for Cyclone II devices.

Figure 13–12. PS Configuration Timing Waveform Note (1)

#### Notes to Figure 13–12:

- (1) The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- (2) Upon power-up, the Cyclone II device holds nSTATUS low for the time of the POR delay.

- (3) Upon power-up, before and during configuration, CONF DONE is low.

- (4) In user mode, drive DCLK either high or low when using the PS configuration scheme, whichever is more convenient. When using the AS configuration scheme, DCLK is a Cyclone II output pin and should not be driven externally.

- (5) Do not leave the DATA pin floating after configuration. Drive it high or low, whichever is more convenient.

| Table 13–11. | Dedicated    | d Configuration         | Pins on the Cyc          | lone II Device (Part 2 of 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|--------------|-------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name     | User<br>Mode | Configuration<br>Scheme | Pin Type                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| nSTATUS      | N/A          | All                     | Bidirectional open-drain | The Cyclone II device drives nSTATUS low immediately after power-up and releases it after the POR time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              |              |                         |                          | This pin provides a status output and input for the Cyclone II device. If the Cyclone II device detects an error during configuration, it drives the nSTATUS pin low to stop configuration. If an external source (for example, another Cyclone II device) drives the nSTATUS pin low during configuration or initialization, the target device enters an error state.  Driving nSTATUS low after configuration and initialization does not affect the configured device. If your design uses a configuration device, driving nSTATUS low causes the configuration device to attempt to configure the FPGA, but since the FPGA ignores transitions on nSTATUS in user mode, the |

|              |              |                         |                          | FPGA does not reconfigure. To initiate a reconfiguration, pull the nCONFIG pin low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              |              |                         |                          | The enhanced configuration devices' and EPC2 devices' OE and nCS pins are connected to the Cyclone II device's nSTATUS and CONF_DONE pins, respectively, and have optional internal programmable pull-up resistors. If you use these internal pull-up resistors on the enhanced configuration device, do not use external 10-k $\Omega$ pull-up resistors on these pins. When using EPC2 devices, you should only use external 10-k $\Omega$ pull-up resistors.                                                                                                                                                                                                                 |

|              |              |                         |                          | The input buffer on this pin supports hysteresis using Schmitt trigger circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |