Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                        |

|--------------------------------|--------------------------------------------------------|

| Product Status                 | Active                                                 |

| Number of LABs/CLBs            | 516                                                    |

| Number of Logic Elements/Cells | 8256                                                   |

| Total RAM Bits                 | 165888                                                 |

| Number of I/O                  | 85                                                     |

| Number of Gates                | -                                                      |

| Voltage - Supply               | 1.15V ~ 1.25V                                          |

| Mounting Type                  | Surface Mount                                          |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                        |

| Package / Case                 | 144-LQFP                                               |

| Supplier Device Package        | 144-TQFP (20x20)                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2c8t144c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Another special packing mode allows the register output to feed back into the LUT of the same LE so that the register is packed with its own fan-out LUT, providing another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

In addition to the three general routing outputs, the LEs within an LAB have register chain outputs. Register chain outputs allow registers within the same LAB to cascade together. The register chain output allows an LAB to use LUTs for a single combinational function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources. See "MultiTrack Interconnect" on page 2–10 for more information on register chain connections.

### **LE Operating Modes**

The Cyclone II LE operates in one of the following modes:

- Normal mode

- Arithmetic mode

Each mode uses LE resources differently. In each mode, six available inputs to the LE—the four data inputs from the LAB local interconnect, the LAB carry-in from the previous carry-chain LAB, and the register chain connection—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, synchronous clear, synchronous load, and clock enable control for the register. These LAB-wide signals are available in all LE modes.

The Quartus® II software, in conjunction with parameterized functions such as library of parameterized modules (LPM) functions, automatically chooses the appropriate mode for common functions such as counters, adders, subtractors, and arithmetic functions. If required, you can also create special-purpose functions that specify which LE operating mode to use for optimal performance.

#### Normal Mode

The normal mode is suitable for general logic applications and combinational functions. In normal mode, four data inputs from the LAB local interconnect are inputs to a four-input LUT (see Figure 2–3). The Quartus II Compiler automatically selects the carry-in or the data3 signal as one of the inputs to the LUT. LEs in normal mode support packed registers and register feedback.

The direct link interconnect allows an LAB, M4K memory block, or embedded multiplier block to drive into the local interconnect of its left and right neighbors. Only one side of a PLL block interfaces with direct link and row interconnects. The direct link interconnect provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

The R4 interconnects span four LABs, three LABs and one M4K memory block, or three LABs and one embedded multiplier to the right or left of a source LAB. These resources are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–8 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by LABs, M4K memory blocks, embedded multipliers, PLLs, and row IOEs. For LAB interfacing, a primary LAB or LAB neighbor (see Figure 2–8) can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnects can drive other R4 interconnects to extend the range of LABs they can drive. Additionally, R4 interconnects can drive R24 interconnects, C4, and C16 interconnects for connections from one row to another.

Adjacent LAB can Drive onto Another LAB's R4 Interconnect Driving Left

R4 Interconnect Driving Left

R4 Interconnect Driving Left

R5 Interconnect Driving Left

R6 Interconnect Driving Left

R7 Interconnect Driving Left

R8 Interconnect Driving Left

R9 Interconnect Driving Right

Figure 2-8. R4 Interconnect Connections

*Notes to Figure 2–8:*

- (1) C4 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

Column I/O Clock Region IO\_CLK[5..0] I/O Clock Regions Cyclone Logic Array LAB Row Clocks LAB Row Clocks labclk[5..0] labclk[5..0] LAB Row Clocks LAB Row Clocks labclk[5..0] labclk[5..0] Global Clock Network Row I/O Clock 8 or 16 Region IO\_CLK[5..0] LAB Row Clocks LAB Row Clocks labclk[5..0] labclk[5..0] I/O Clock Regions 6 Column I/O Clock Region

IO\_CLK[5..0]

Figure 2-15. LAB & I/O Clock Regions

For more information on the global clock network and the clock control block, see the *PLLs in Cyclone II Devices* chapter in Volume 1 of the *Cyclone II Device Handbook*.

Each M4K block can implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and first-in first-out (FIFO) buffers. The M4K blocks support the following features:

- 4,608 RAM bits

- 250-MHz performance

- True dual-port memory

- Simple dual-port memory

- Single-port memory

- Byte enable

- Parity bits

- Shift register

- FIFO buffer

- ROM

- Various clock modes

- Address clock enable

Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

Table 2–5 shows the capacity and distribution of the M4K memory blocks in each Cyclone II device.

| Table 2–5. M4K Memory Capacity & Distribution in Cyclone II Devices |             |            |                |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|-------------|------------|----------------|--|--|--|--|--|--|--|

| Device                                                              | M4K Columns | M4K Blocks | Total RAM Bits |  |  |  |  |  |  |  |

| EP2C5                                                               | 2           | 26         | 119,808        |  |  |  |  |  |  |  |

| EP2C8                                                               | 2           | 36         | 165,888        |  |  |  |  |  |  |  |

| EP2C15                                                              | 2           | 52         | 239,616        |  |  |  |  |  |  |  |

| EP2C20                                                              | 2           | 52         | 239,616        |  |  |  |  |  |  |  |

| EP2C35                                                              | 3           | 105        | 483,840        |  |  |  |  |  |  |  |

| EP2C50                                                              | 3           | 129        | 594,432        |  |  |  |  |  |  |  |

| EP2C70                                                              | 5           | 250        | 1,152,000      |  |  |  |  |  |  |  |

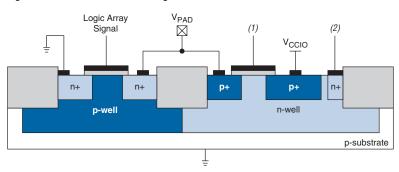

Figure 4–2. Transistor Level Diagram of FPGA Device I/O Buffers

*Notes to Figure 4–2:*

- (1) This is the logic array signal or the larger of either the  $V_{CCIO}$  or  $V_{PAD}$  signal.

- (2) This is the larger of either the  $V_{CCIO}$  or  $V_{PAD}$  signal.

# Power-On Reset Circuitry

Cyclone II devices contain POR circuitry to keep the device in a reset state until the power supply voltage levels have stabilized during power-up. The POR circuit monitors the  $V_{\rm CCINT}$  voltage levels and tri-states all user I/O pins until the  $V_{\rm CC}$  reaches the recommended operating levels. In addition, the POR circuitry also monitors the  $V_{\rm CCIO}$  level of the two I/O banks that contains configuration pins (I/O banks 1 and 3 for EP2C5 and EP2C8, I/O banks 2 and 6 for EP2C15A, EP2C20, EP2C35, EP2C50, and EP2C70) and tri-states all user I/O pins until the  $V_{\rm CC}$  reaches the recommended operating levels.

After the Cyclone II device enters user mode, the POR circuit continues to monitor the  $V_{CCINT}$  voltage level so that a brown-out condition during user mode can be detected. If the  $V_{CCINT}$  voltage sags below the POR trip point during user mode, the POR circuit resets the device. If the  $V_{CCIO}$  voltage sags during user mode, the POR circuit does not reset the device.

# "Wake-up" Time for Cyclone II Devices

In some applications, it may be necessary for a device to wake up very quickly in order to begin operation. The Cyclone II device family offers the Fast-On feature to support fast wake-up time applications. Devices that support the Fast-On feature are designated with an "A" in the ordering code and have stricter power up requirements compared to non-A devices.

| Table 5-          | Table 5–15. Cyclone II Performance (Part 3 of 4)                                                            |      |                         |               |                      |                      |                      |                      |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------|------|-------------------------|---------------|----------------------|----------------------|----------------------|----------------------|--|--|

|                   |                                                                                                             | Re   | esources U              | lsed          | F                    | Performan            | ice (MHz)            | )                    |  |  |

| Applications      |                                                                                                             | LEs  | M4K<br>Memory<br>Blocks | DSP<br>Blocks | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade |  |  |

| Larger<br>Designs | 8-bit, 1024 pt, Quad Output,<br>1 Parallel FFT Engine, Burst,<br>4 Mults/2 Adders FFT function              | 2400 | 10                      | 12            | 235.07               | 195.0                | 140.11               | 163.02               |  |  |

|                   | 8-bit, 1024 pt, Quad Output,<br>2 Parallel FFT Engines, Burst,<br>3 Mults/5 Adders FFT function             | 4343 | 14                      | 18            | 200.0                | 195.0                | 152.67               | 163.02               |  |  |

|                   | 8-bit, 1024 pt, Quad Output,<br>2 Parallel FFT Engines, Burst,<br>4 Mults/2 Adders FFT function             | 4043 | 14                      | 24            | 200.0                | 195.0                | 149.72               | 163.02               |  |  |

|                   | 8-bit, 1024 pt, Quad Output,<br>4 Parallel FFT Engines, Burst,<br>3 Mults/5 Adders FFT function             | 7496 | 28                      | 36            | 200.0                | 195.0                | 150.01               | 163.02               |  |  |

|                   | 8-bit, 1024 pt, Quad Output,<br>4 Parallel FFT Engines, Burst,<br>4 Mults/2 Adders FFT function             | 6896 | 28                      | 48            | 200.0                | 195.0                | 151.33               | 163.02               |  |  |

|                   | 8-bit, 1024 pt, Quad Output,<br>1 Parallel FFT Engine, Buffered<br>Burst,<br>3 Mults/5 Adders FFT function  | 2934 | 18                      | 9             | 235.07               | 195.0                | 148.89               | 163.02               |  |  |

|                   | 8-bit, 1024 pt, Quad Output,<br>1 Parallel FFT Engine, Buffered<br>Burst,<br>4 Mults/2 Adders FFT function  | 2784 | 18                      | 12            | 235.07               | 195.0                | 151.51               | 163.02               |  |  |

|                   | 8-bit, 1024 pt, Quad Output,<br>2 Parallel FFT Engines, Buffered<br>Burst,<br>3 Mults/5 Adders FFT function | 4720 | 30                      | 18            | 200.0                | 195.0                | 149.76               | 163.02               |  |  |

|                   | 8-bit, 1024 pt, Quad Output,<br>2 Parallel FFT Engines, Buffered<br>Burst,<br>4 Mults/2 Adders FFT function | 4420 | 30                      | 24            | 200.0                | 195.0                | 151.08               | 163.02               |  |  |

| Table 5–16. LE_FF Internal Timing Microparameters (Part 2 of 2) |          |           |          |           |          |      |        |  |  |  |  |  |

|-----------------------------------------------------------------|----------|-----------|----------|-----------|----------|------|--------|--|--|--|--|--|

| D                                                               | -6 Speed | Grade (1) | -7 Speed | Grade (2) | –8 Speed | Heit |        |  |  |  |  |  |

| Parameter                                                       | Min      | Max       | Min Max  |           | Min Max  |      | - Unit |  |  |  |  |  |

| TPRE                                                            | 191      | _         | 244      | _         | 244      | _    | ps     |  |  |  |  |  |

|                                                                 | _        | _         | 217      | _         | 244      | _    | ps     |  |  |  |  |  |

| TCLKL                                                           | 1000     | _         | 1242     | _         | 1242     | _    | ps     |  |  |  |  |  |

|                                                                 | _        | _         | 1111     | _         | 1242     | _    | ps     |  |  |  |  |  |

| TCLKH                                                           | 1000     | _         | 1242     | _         | 1242     | _    | ps     |  |  |  |  |  |

|                                                                 | _        | _         | 1111     | _         | 1242     | _    | ps     |  |  |  |  |  |

| tLUT                                                            | 180      | 438       | 172      | 545       | 172      | 651  | ps     |  |  |  |  |  |

|                                                                 | _        | _         | 180      | _         | 180      | _    | ps     |  |  |  |  |  |

#### Notes to Table 5-16:

- (1) For the -6 speed grades, the minimum timing is for the commercial temperature grade. The -7 speed grade devices offer the automotive temperature grade. The -8 speed grade devices offer the industrial temperature grade.

- For each parameter of the -7 speed grade columns, the value in the first row represents the minimum timing parameter for automotive devices. The second row represents the minimum timing parameter for commercial

- (3) For each parameter of the -8 speed grade columns, the value in the first row represents the minimum timing parameter for industrial devices. The second row represents the minimum timing parameter for commercial

| Table 5–17. IOE Internal Timing Microparameters (Part 1 of 2) |          |           |          |           |          |      |      |  |  |  |  |  |

|---------------------------------------------------------------|----------|-----------|----------|-----------|----------|------|------|--|--|--|--|--|

| Davamatar                                                     | -6 Speed | Grade (1) | -7 Speed | Grade (2) | -8 Speed | 1114 |      |  |  |  |  |  |

| Parameter                                                     | Min Max  |           | Min Max  |           | Min Max  |      | Unit |  |  |  |  |  |

| TSU                                                           | 76       | _         | 101      | _         | 101      | _    | ps   |  |  |  |  |  |

|                                                               | _        | _         | 89       | _         | 101      | _    | ps   |  |  |  |  |  |

| TH                                                            | 88       | _         | 106      | _         | 106      | _    | ps   |  |  |  |  |  |

|                                                               | _        | _         | 97       | _         | 106      | _    | ps   |  |  |  |  |  |

| TCO                                                           | 99       | 155       | 95       | 171       | 95       | 187  | ps   |  |  |  |  |  |

|                                                               | _        | _         | 99       | _         | 99       | _    | ps   |  |  |  |  |  |

| TPIN2COMBOUT_R                                                | 384      | 762       | 366      | 784       | 366      | 855  | ps   |  |  |  |  |  |

|                                                               | _        | _         | 384      | _         | 384      | _    | ps   |  |  |  |  |  |

| TPIN2COMBOUT_C                                                | 385      | 760       | 367      | 783       | 367      | 854  | ps   |  |  |  |  |  |

|                                                               | _        | _         | 385      | _         | 385      | _    | ps   |  |  |  |  |  |

| TCOMBIN2PIN_R                                                 | 1344     | 2490      | 1280     | 2689      | 1280     | 2887 | ps   |  |  |  |  |  |

|                                                               | _        | _         | 1344     | _         | 1344     | _    | ps   |  |  |  |  |  |

= 1000 / (1000/toggle rate at default load + derating factor \* load value in pF/1000)

For example, the output toggle rate at 0 pF (default) load for SSTL-18 Class II 18mA I/O standard is 270 MHz on a -6 device column I/O pin. The derating factor is 29 ps/pF. For a 10pF load, the toggle rate is calculated as:

$1000 / (1000/270 + 29 \times 10/1000) = 250 (MHz)$

Tables 5–44 through 5–46 show the I/O toggle rates for Cyclone II devices.

| Table 5–44. Maximum Input Clock Toggle Rate on Cyclone II Devices (Part 1 of 2) |                                                             |                      |                      |                      |                      |                      |                           |                      |                      |  |  |  |

|---------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------------|----------------------|----------------------|--|--|--|

|                                                                                 | Maximum Input Clock Toggle Rate on Cyclone II Devices (MHz) |                      |                      |                      |                      |                      |                           |                      |                      |  |  |  |

| I/O Standard                                                                    | Column I/O Pins                                             |                      |                      | Row I/O Pins         |                      |                      | Dedicated Clock<br>Inputs |                      |                      |  |  |  |

| ·                                                                               | -6<br>Speed<br>Grade                                        | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade      | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade |  |  |  |

| LVTTL                                                                           | 450                                                         | 405                  | 360                  | 450                  | 405                  | 360                  | 420                       | 380                  | 340                  |  |  |  |

| 2.5V                                                                            | 450                                                         | 405                  | 360                  | 450                  | 405                  | 360                  | 450                       | 405                  | 360                  |  |  |  |

| 1.8V                                                                            | 450                                                         | 405                  | 360                  | 450                  | 405                  | 360                  | 450                       | 405                  | 360                  |  |  |  |

| 1.5V                                                                            | 300                                                         | 270                  | 240                  | 300                  | 270                  | 240                  | 300                       | 270                  | 240                  |  |  |  |

| LVCMOS                                                                          | 450                                                         | 405                  | 360                  | 450                  | 405                  | 360                  | 420                       | 380                  | 340                  |  |  |  |

| SSTL_2_CLASS_I                                                                  | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |  |

| SSTL_2_CLASS_II                                                                 | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |  |

| SSTL_18_CLASS_I                                                                 | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |  |

| SSTL_18_CLASS_II                                                                | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |  |

| 1.5V_HSTL_CLASS_I                                                               | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |  |

| 1.5V_HSTL_CLASS_II                                                              | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |  |

| 1.8V_HSTL_CLASS_I                                                               | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |  |

| 1.8V_HSTL_CLASS_II                                                              | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |  |

| PCI                                                                             | _                                                           | _                    | _                    | 350                  | 315                  | 280                  | 350                       | 315                  | 280                  |  |  |  |

| PCI-X                                                                           | _                                                           | _                    | _                    | 350                  | 315                  | 280                  | 350                       | 315                  | 280                  |  |  |  |

| DIFFERENTIAL_SSTL_2_<br>CLASS_I                                                 | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |  |

| DIFFERENTIAL_SSTL_2_<br>CLASS_II                                                | 500                                                         | 500                  | 500                  | 500                  | 500                  | 500                  | 500                       | 500                  | 500                  |  |  |  |

|                 |                 | Ma                           | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |                      |                      |                            |                      |                      |                      |                      |  |  |

|-----------------|-----------------|------------------------------|-----------------------------------------------------------|----------------------|----------------------|----------------------------|----------------------|----------------------|----------------------|----------------------|--|--|

| I/O Standard    | Drive           | Column I/O Pins Row I/O Pins |                                                           |                      | ns                   | Dedicated Clock<br>Outputs |                      |                      |                      |                      |  |  |

| <b>3.</b> C     | Strength        |                              | -7<br>Speed<br>Grade                                      | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade       | –8<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | –8<br>Speed<br>Grade |  |  |

| SSTL_2_CLASS_I  | OCT_50<br>_OHMS | 67                           | 69                                                        | 70                   | 25                   | 42                         | 60                   | 25                   | 42                   | 60                   |  |  |

| SSTL_18_CLASS_I | OCT_50<br>OHMS  | 30                           | 33                                                        | 36                   | 47                   | 49                         | 51                   | 47                   | 49                   | 51                   |  |  |

# **High Speed I/O Timing Specifications**

The timing analysis for LVDS, mini-LVDS, and RSDS is different compared to other I/O standards because the data communication is source-synchronous.

You should also consider board skew, cable skew, and clock jitter in your calculation. This section provides details on the timing parameters for high-speed I/O standards in Cyclone II devices.

Table 5–47 defines the parameters of the timing diagram shown in Figure 5–3.

| Table 5–47. High-Speed I/O Timing Definitions (Part 1 of 2) |                     |                                                                                                                                                                                                        |  |  |  |  |  |  |

|-------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Parameter                                                   | Symbol              | Description                                                                                                                                                                                            |  |  |  |  |  |  |

| High-speed clock                                            | f <sub>HSCKLK</sub> | High-speed receiver and transmitter input and output clock frequency.                                                                                                                                  |  |  |  |  |  |  |

| Duty cycle                                                  | t <sub>DUTY</sub>   | Duty cycle on high-speed transmitter output clock.                                                                                                                                                     |  |  |  |  |  |  |

| High-speed I/O data rate                                    | HSIODR              | High-speed receiver and transmitter input and output data rate.                                                                                                                                        |  |  |  |  |  |  |

| Time unit interval                                          | TUI                 | TUI = 1/HSIODR.                                                                                                                                                                                        |  |  |  |  |  |  |

| Channel-to-channel skew                                     | TCCS                | The timing difference between the fastest and slowest output edges, including $t_{CO}$ variation and clock skew. The clock is included in the TCCS measurement.<br>TCCS = TUI – SW – $(2 \times RSKM)$ |  |  |  |  |  |  |

| Table 5-48                         | Table 5–48. RSDS Transmitter Timing Specification (Part 2 of 2) |     |                |        |     |                |        |     |                |        |      |  |

|------------------------------------|-----------------------------------------------------------------|-----|----------------|--------|-----|----------------|--------|-----|----------------|--------|------|--|

| Cumbal                             | Combal Conditions                                               |     | -6 Speed Grade |        |     | -7 Speed Grade |        |     | -8 Speed Grade |        |      |  |

| Symbol                             | Conditions                                                      | Min | Тур            | Max(1) | Min | Тур            | Max(1) | Min | Тур            | Max(1) | Unit |  |

| TCCS                               | _                                                               | _   | _              | 200    | _   | _              | 200    | _   | _              | 200    | ps   |  |

| Output<br>jitter (peak<br>to peak) | _                                                               | _   | _              | 500    | _   | _              | 500    | _   | _              | 500    | ps   |  |

| t <sub>RISE</sub>                  | 20–80%,<br>C <sub>LOAD</sub> = 5 pF                             | _   | 500            | _      | _   | 500            | _      | _   | 500            | _      | ps   |  |

| t <sub>FALL</sub>                  | 80–20%,<br>C <sub>LOAD</sub> = 5 pF                             | _   | 500            | _      | _   | 500            | _      | _   | 500            | _      | ps   |  |

| t <sub>LOCK</sub>                  | _                                                               | _   |                | 100    | _   |                | 100    | _   | _              | 100    | μs   |  |

#### Note to Table 5-48:

(1) These specifications are for a three-resistor RSDS implementation. For single-resistor RSDS in ×10 through ×2 modes, the maximum data rate is 170 Mbps and the corresponding maximum input clock frequency is 85 MHz. For single-resistor RSDS in ×1 mode, the maximum data rate is 170 Mbps, and the maximum input clock frequency is 170 MHz. For more information about the different RSDS implementations, refer to the *High-Speed Differential Interfaces in Cyclone II Devices* chapter of the Cyclone II Device Handbook.

In order to determine the transmitter timing requirements, RSDS receiver timing requirements on the other end of the link must be taken into consideration. RSDS receiver timing parameters are typically defined as  $t_{SU}$  and  $t_{H}$  requirements. Therefore, the transmitter timing parameter specifications are  $t_{CO}$  (minimum) and  $t_{CO}$  (maximum). Refer to Figure 5–4 for the timing budget.

The AC timing requirements for RSDS are shown in Figure 5–5.

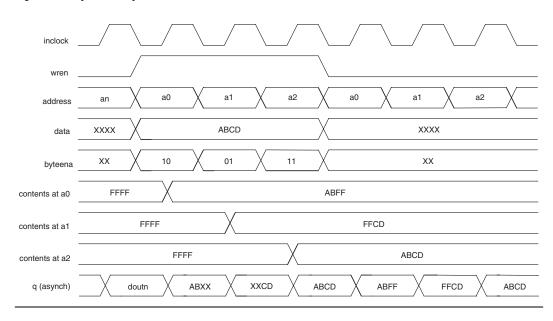

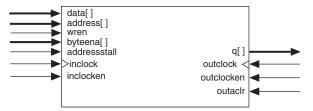

Figure 8–2. Cyclone II Byte Enable Functional Waveform

# **Packed Mode Support**

Cyclone II M4K memory blocks support packed mode. You can implement two single-port memory blocks in a single block under the following conditions:

- Each of the two independent block sizes is less than or equal to half of the M4K block size. The maximum data width for each independent block is 18 bits wide.

- Each of the single-port memory blocks is configured in single-clock mode.

See "Single-Port Mode" on page 8–9 and "Single-Clock Mode" on page 8–24 for more information.

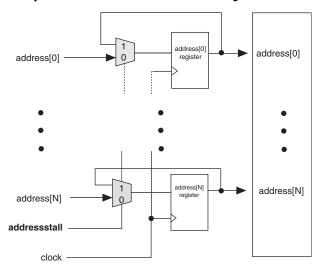

#### **Address Clock Enable**

Cyclone II M4K memory blocks support address clock enables, which holds the previous address value until needed. When the memory blocks are configured in dual-port mode, each port has its own independent address clock enable.

Figure 8–3 shows an address clock enable block diagram. The address register output is fed back to its input via a multiplexer. The multiplexer output is selected by the address clock enable (addressstall) signal. Address latching is enabled when the addressstall signal goes high (active high). The output of the address register is then continuously fed into the input of the register until the addressstall signal goes low.

Figure 8-3. Cyclone II Address Clock Enable Block Diagram

The address clock enable is typically used for cache memory applications to improve efficiency during a cache-miss. The default value for the address clock enable signals is low (disabled). Figures 8–4 and 8–5 show the address clock enable waveforms during the read and write cycles, respectively.

M4K memory blocks do not support asynchronous memory (unregistered inputs).

The M4K memory blocks support the following modes:

- Single-port

- Simple dual-port

- True dual-port (bidirectional dual-port)

- Shift register

- ROM

- FIFO buffers

Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

# Single-Port Mode

Single-port mode supports non-simultaneous read and write operations. Figure 8–6 shows the single-port memory configuration for Cyclone II memory blocks.

Figure 8–6. Single-Port Mode Note (1)

*Note to Figure 8–6:*

Two single-port memory blocks can be implemented in a single M4K block in packed mode.

In single-port mode, the outputs are in read-during-write mode, which means that during the write operation, data written to the RAM flows through to the RAM outputs. When the output registers are bypassed, the new data is available on the rising edge of the same clock cycle on which it was written.

See "Read-During- Write Operation at the Same Address" on page 8–28 for more information about read-during-write mode.

The port width configurations for M4K blocks in single-port mode are as follows:

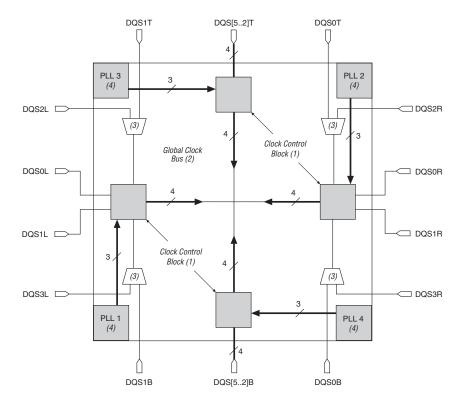

directly to the clock control block. For the larger Cyclone II devices, the corner DQS signals are multiplexed before they are routed to the clock control block. When you use the corner DQS pins for DDR implementation, there is a degradation in the performance of the memory interface. The clock control block is used to select from a number of input clock sources, in this case either PLL clock outputs or DQS pins, to drive onto the global clock bus. Figure 9–7 shows the corner DQS signal mappings for EP2C15 through EP2C70 devices.

Figure 9-7. Corner DQS Signal Mapping for EP2C15-EP2C70 Devices

#### *Notes to Figure 9–7:*

- (1) There are four control blocks on each side.

- (2) There are a total of 16 global clocks available.

- (3) Only one of the corner DQS pins in each corner can feed the clock control block at a time. The other DQS pins can be used as general purpose I/O pins.

- (4) PLL resource can be lost if all DQS pins from one side are used at the same time.

- (5) Top/bottom and side IOE have different timing.

# Section IV. I/O Standards

This section provides information on Cyclone® II single-ended, voltage referenced, and differential I/O standards.

This section includes the following chapters:

- Chapter 10, Selectable I/O Standards in Cyclone II Devices

- Chapter 11, High-Speed Differential Interfaces in Cyclone II Devices

# **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

Altera Corporation Section IV-1

## 1.8-V LVCMOS (EIA/JEDEC Standard EIA/JESD8-7)

The 1.8-V I/O standard is used for 1.8-V LVCMOS applications. This standard defines the DC interface parameters for high-speed, low-voltage, non-terminated digital circuits driving or being driven by other 1.8-V parts.

The 1.8-V standard does not require input reference voltages or board terminations. Cyclone II devices support input and output levels for 1.8-V LVCMOS.

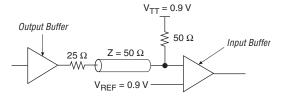

#### SSTL-18 Class I and II

The 1.8-V SSTL-18 standard is formulated under JEDEC Standard, JESD815: Stub Series Terminated Logic for 1.8V (SSTL-18).

The SSTL-18 I/O standard is a 1.8-V memory bus standard used for applications such as high-speed DDR2 SDRAM interfaces. This standard is similar to SSTL-2 and defines input and output specifications for devices that are designed to operate in the SSTL-18 logic switching range 0.0 to 1.8 V. SSTL-18 requires a 0.9-V  $\rm V_{REF}$  and a 0.9-V  $\rm V_{TT}$ , with the termination resistors connected to both. There are no class definitions for the SSTL-18 standard in the JEDEC specification. The specification of this I/O standard is based on an environment that consists of both series and parallel terminating resistors. Altera provides solutions to two derived applications in JEDEC specification and names them class I and class II to be consistent with other SSTL standards. Figures 10–5 and 10–6 show SSTL-18 class I and II termination, respectively. Cyclone II devices support both input and output levels.

Figure 10-5. 1.8-V SSTL Class I Termination

Figure 11–9 shows the mini-LVDS receiver and transmitter signal waveforms.

Positive Channel (p) = V<sub>OH</sub>

V<sub>OD</sub>

Negative Channel (n) = V<sub>OL</sub>

Ground

V<sub>OD</sub>

V<sub>OD</sub>

V<sub>OD</sub>

Figure 11–9. Transmitter Output Signal Level Waveforms for mini-LVDS Note (1)

Note to Figure 11-9:

(1) The  $V_{OD}$  specifications apply at the resistor network output.

## Designing with mini-LVDS

Similar to RSDS, Cyclone II devices support the mini-LVDS output standard using the LVDS I/O buffer types. For transmitters, the LVDS output buffer can be used with the external resistor network shown in Figure 11–10. The resistor values chosen should satisfy the equation on page 11-8.

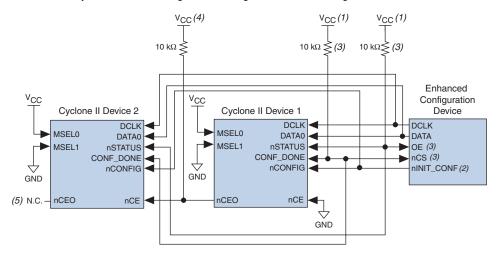

Figure 13-14. Multiple Device PS Configuration Using an Enhanced Configuration Device

#### *Notes to Figure 13–14:*

- (1) The pull-up resistor should be connected to the same supply voltage as the configuration device.

- (2) The ninit\_conf pin is available on enhanced configuration devices and has an internal pull-up resistor that is always active, meaning an external pull-up resistor should not be used on the ninit\_conf to nconfig line. The ninit\_conf pin does not need to be connected if its functionality is not used. If ninit\_conf is not used, nconfig must be pulled to V<sub>CC</sub> either directly or through a resistor (if reconfiguration is required, a resistor is necessary).

- (3) The enhanced configuration devices' OE and nCS pins have internal programmable pull-up resistors. If internal pull-up resistors are used, external pull-up resistors should not be used on these pins. The internal pull-up resistors are used by default in the Quartus II software. To turn off the internal pull-up resistors, check the **Disable nCS and OE pull-ups on configuration device** option when generating programming files.

- (4) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of I/O bank that the nCEO pin resides in.

- (5) The nCEO pin can be left unconnected or used as a user I/O pin when it does not feed other device's nCE pin.

You cannot cascade enhanced configuration devices (EPC16, EPC8, and EPC4 devices).

When configuring multiple devices, you must generate the configuration device's POF from each project's SOF. You can combine multiple SOFs using the **Convert Programming Files** window in the Quartus II software.

For more information on how to create configuration files for multiple device configuration chains, see the *Software Settings* section in Volume 2 of the *Configuration Handbook*.

When configuring multiple devices with the PS scheme, connect the first Cyclone II device's nCE pin to GND and connect its nCEO pin to the nCE pin of the Cyclone II device in the chain. Use an external 10-k $\Omega$  pull-up resistor to pull the Cyclone II device's nCEO pin to the  $V_{CCIO}$  level when

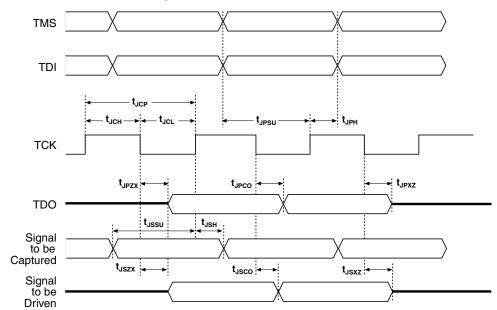

When the TAP controller is in the TEST\_LOGIC/RESET state, the BST circuitry is disabled, the device is in normal operation, and the instruction register is initialized with IDCODE as the initial instruction. At device power-up, the TAP controller starts in this TEST\_LOGIC/RESET state. In addition, forcing the TAP controller to the TEST\_LOGIC/RESET state is done by holding TMS high for five TCK clock cycles. Once in the TEST\_LOGIC/RESET state, the TAP controller remains in this state as long as TMS is held high (while TCK is clocked). Figure 14–6 shows the timing requirements for the IEEE Std. 1149.1 signals.

Figure 14-6. IEEE Std. 1149.1 Timing Waveforms

To start IEEE Std. 1149.1 operation, select an instruction mode by advancing the TAP controller to the shift instruction register (SHIFT\_IR) state and shift in the appropriate instruction code on the <code>TDI</code> pin. The waveform diagram in Figure 14–7 represents the entry of the instruction code into the instruction register. It shows the values of <code>TCK</code>, <code>TMS</code>, <code>TDI</code>, <code>TDO</code>, and the states of the TAP controller. From the <code>RESET</code> state, <code>TMS</code> is clocked with the pattern <code>01100</code> to advance the TAP controller to <code>SHIFT\_IR</code>.

# 484-Pin FineLine BGA, Option 3 - Wirebond

- All dimensions and tolerances conform to ASME Y14.5M 1994.

- Controlling dimension is in millimeters.

- Pin A1 may be indicated by an ID dot, or a special feature, in its proximity on package surface.

Tables 15–13 and 15–14 show the package information and package outline figure references, respectively, for the 484-pin FineLine BGA package.

| Table 15–13. 484-Pin FineLine BGA Package Information |                                                           |  |  |  |  |  |  |  |

|-------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|--|--|

| Description                                           | Specification                                             |  |  |  |  |  |  |  |

| Ordering code reference                               | F                                                         |  |  |  |  |  |  |  |

| Package acronym                                       | FineLine BGA                                              |  |  |  |  |  |  |  |

| Substrate material                                    | ВТ                                                        |  |  |  |  |  |  |  |

| Solder ball composition                               | Regular: 63Sn:37Pb (Typ.)<br>Pb-free: Sn:3Ag:0.5Cu (Typ.) |  |  |  |  |  |  |  |

| JEDEC Outline Reference                               | MS-034 Variation: AAJ-1                                   |  |  |  |  |  |  |  |

| Maximum lead coplanarity                              | 0.008 inches (0.20 mm)                                    |  |  |  |  |  |  |  |

| Weight                                                | 5.7 g                                                     |  |  |  |  |  |  |  |

| Moisture sensitivity level                            | Printed on moisture barrier bag                           |  |  |  |  |  |  |  |

| Table 15–14. 484-Pin FineLine BGA Package Outline Dimensions |      |            |      |  |  |  |  |  |  |

|--------------------------------------------------------------|------|------------|------|--|--|--|--|--|--|

| Cumbal                                                       |      | Millimeter |      |  |  |  |  |  |  |

| Symbol                                                       | Min. | Max.       |      |  |  |  |  |  |  |

| Α                                                            | _    | _          | 2.60 |  |  |  |  |  |  |

| A1                                                           | 0.30 | _          |      |  |  |  |  |  |  |

| A2                                                           | _    |            |      |  |  |  |  |  |  |

| A3                                                           | _    | _          | 1.80 |  |  |  |  |  |  |

| D                                                            |      | 23.00 BSC  |      |  |  |  |  |  |  |

| E                                                            |      | 23.00 BSC  |      |  |  |  |  |  |  |

| b                                                            | 0.50 | 0.60       | 0.70 |  |  |  |  |  |  |

| е                                                            |      | 1.00 BSC   |      |  |  |  |  |  |  |