Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betano                     |                                                                                            |

|----------------------------|--------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                     |

| Core Processor             | ARM® Cortex®-M4                                                                            |

| Core Size                  | 32-Bit Single-Core                                                                         |

| Speed                      | 80MHz                                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                                 |

| Number of I/O              | 51                                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                      |

| EEPROM Size                | -                                                                                          |

| RAM Size                   | 128K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                      |

| Oscillator Type            | Internal                                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                          |

| Mounting Type              | Surface Mount                                                                              |

| Package / Case             | 64-LQFP                                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l476rct6                      |

|                            |                                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Interconnect source | Interconnect<br>destination | Interconnect action         | Run | Sleep | Low-power run | Low-power sleep | Stop 0 / Stop 1 | Stop 2   |

|---------------------|-----------------------------|-----------------------------|-----|-------|---------------|-----------------|-----------------|----------|

|                     | TIMx                        | External trigger            | Y   | Y     | Y             | Υ               | -               | -        |

| GPIO                | LPTIMERx                    | External trigger            | Y   | Y     | Y             | Y               | Y               | Y<br>(1) |

|                     | ADCx<br>DACx<br>DFSDM       | Conversion external trigger | Y   | Y     | Y             | Y               | -               | -        |

## Table 6. STM32L476xx peripherals interconnect matrix (continued)

1. LPTIM1 only.

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- External triggers for conversion

- Sample and hold low-power mode, with internal or external capacitor

The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

## 3.17 Voltage reference buffer (VREFBUF)

The STM32L476xx devices embed an voltage reference buffer which can be used as voltage reference for ADCs, DACs and also as voltage reference for external components through the VREF+ pin.

The internal voltage reference buffer supports two voltages:

- 2.048 V

- 2.5 V.

An external voltage reference can be provided through the VREF+ pin when the internal voltage reference buffer is off.

The VREF+ pin is double-bonded with VDDA on some packages. In these packages the internal voltage reference buffer is not available.

## 3.18 Comparators (COMP)

The STM32L476xx devices embed two rail-to-rail comparators with programmable reference voltage (internal or external), hysteresis and speed (low speed for low-power) and with selectable output polarity.

The reference voltage can be one of the following:

- External I/O

- DAC output channels

- Internal reference voltage or submultiple (1/4, 1/2, 3/4).

All comparators can wake up from Stop mode, generate interrupts and breaks for the timers and can be also combined into a window comparator.

## 3.23 Random number generator (RNG)

All devices embed an RNG that delivers 32-bit random numbers generated by an integrated analog circuit.

## 3.24 Timers and watchdogs

The STM32L476 includes two advanced control timers, up to nine general-purpose timers, two basic timers, two low-power timers, two watchdog timers and a SysTick timer. The table below compares the features of the advanced control, general purpose and basic timers.

| Timer type          | Timer        | Counter resolution | Counter<br>type      | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>outputs |

|---------------------|--------------|--------------------|----------------------|---------------------------------------|------------------------------|---------------------------------|--------------------------|

| Advanced control    | TIM1, TIM8   | 16-bit             | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | 3                        |

| General-<br>purpose | TIM2, TIM5   | 32-bit             | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                       |

| General-<br>purpose | TIM3, TIM4   | 16-bit             | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                       |

| General-<br>purpose | TIM15        | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes                          | 2                               | 1                        |

| General-<br>purpose | TIM16, TIM17 | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes                          | 1                               | 1                        |

| Basic               | TIM6, TIM7   | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                       |

Table 10. Timer feature comparison

### 3.24.1 Advanced-control timer (TIM1, TIM8)

The advanced-control timer can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as complete general-purpose timers. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes) with full modulation capability (0-100%)

- One-pulse mode output

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switches driven by these outputs.

DocID025976 Rev 4

# 3.27 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32L476xx devices have three embedded universal synchronous receiver transmitters (USART1, USART2 and USART3) and two universal asynchronous receiver transmitters (UART4, UART5).

These interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. They provide hardware management of the CTS and RTS signals, and RS485 Driver Enable. They are able to communicate at speeds of up to 10Mbit/s.

USART1, USART2 and USART3 also provide Smart Card mode (ISO 7816 compliant) and SPI-like communication capability.

All USART have a clock domain independent from the CPU clock, allowing the USARTx (x=1,2,3,4,5) to wake up the MCU from Stop mode. The wake up events from Stop mode are programmable and can be:

- Start bit detection

- Any received data frame

- A specific programmed data frame

All USART interfaces can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>   | USART1 | USART2 | USART3     | UART4     | UART5 | LPUART1 |

|---------------------------------------|--------|--------|------------|-----------|-------|---------|

| Hardware flow control for modem       | Х      | Х      | Х          | Х         | Х     | Х       |

| Continuous communication using DMA    | Х      | Х      | Х          | Х         | Х     | Х       |

| Multiprocessor communication          | Х      | Х      | Х          | Х         | Х     | Х       |

| Synchronous mode                      | Х      | Х      | Х          | -         | -     | -       |

| Smartcard mode                        | Х      | Х      | Х          | -         | -     | -       |

| Single-wire half-duplex communication | Х      | Х      | Х          | Х         | Х     | Х       |

| IrDA SIR ENDEC block                  | Х      | Х      | Х          | Х         | х     | -       |

| LIN mode                              | Х      | Х      | Х          | Х         | Х     | -       |

| Dual clock domain                     | Х      | Х      | Х          | Х         | Х     | Х       |

| Wakeup from Stop 0 / Stop 1 modes     | Х      | Х      | Х          | Х         | х     | Х       |

| Wakeup from Stop 2 mode               | -      | -      | -          | -         | -     | Х       |

| Receiver timeout interrupt            | Х      | Х      | Х          | Х         | Х     | -       |

| Modbus communication                  | Х      | Х      | Х          | Х         | х     | -       |

| Auto baud rate detection              |        | )      | X (4 modes | )         | •     | -       |

| Driver Enable                         | Х      | Х      | Х          | Х         | Х     | Х       |

| LPUART/USART data length              |        | •      | 7, 8 ar    | nd 9 bits | •     |         |

Table 12. STM32L4x6 USART/UART/LPUART features

1. X = supported.

## 3.36 Quad SPI memory interface (QUADSPI)

The Quad SPI is a specialized communication interface targeting single, dual or quad SPI flash memories. It can operate in any of the three following modes:

- Indirect mode: all the operations are performed using the QUADSPI registers

- Status polling mode: the external flash status register is periodically read and an interrupt can be generated in case of flag setting

- Memory-mapped mode: the external flash is memory mapped and is seen by the system as if it were an internal memory

The Quad SPI interface supports:

- Three functional modes: indirect, status-polling, and memory-mapped

- SDR and DDR support

- Fully programmable opcode for both indirect and memory mapped mode

- Fully programmable frame format for both indirect and memory mapped mode

- Each of the 5 following phases can be configured independently (enable, length, single/dual/quad communication)

- Instruction phase

- Address phase

- Alternate bytes phase

- Dummy cycles phase

- Data phase

- Integrated FIFO for reception and transmission

- 8, 16, and 32-bit data accesses are allowed

- DMA channel for indirect mode operations

- Programmable masking for external flash flag management

- Timeout management

- Interrupt generation on FIFO threshold, timeout, status match, operation complete, and access error

|        |         | Pin N   | Numb    |          |         |                                       |          |               |       | Pin functions                                                                                                                 |                      |

|--------|---------|---------|---------|----------|---------|---------------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP64 | WLCSP72 | WLCSP81 | LQFP100 | UFBGA132 | LQFP144 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                           | Additional functions |

| 45     | C1      | C1      | 71      | A12      | 104     | PA12                                  | I/O      | FT_u          | -     | TIM1_ETR,<br>USART1_RTS_DE,<br>CAN1_TX, OTG_FS_DP,<br>EVENTOUT                                                                | -                    |

| 46     | C2      | C2      | 72      | A11      | 105     | PA13<br>(JTMS-SWDIO)                  | I/O      | FT            | (3)   | JTMS-SWDIO, IR_OUT,<br>OTG_FS_NOE,<br>EVENTOUT                                                                                | -                    |

| 47     | B1      | B1      | -       | -        | -       | VSS                                   | S        | -             | -     | -                                                                                                                             | -                    |

| 48     | A1      | A1      | 73      | C11      | 106     | VDDUSB                                | S        | -             | -     | -                                                                                                                             | -                    |

| -      | -       | -       | 74      | F11      | 107     | VSS                                   | S        | -             | -     | -                                                                                                                             | -                    |

| -      | -       | -       | 75      | G11      | 108     | VDD                                   | S        | -             | -     | -                                                                                                                             | -                    |

| 49     | B2      | B2      | 76      | A10      | 109     | PA14<br>(JTCK-SWCLK)                  | I/O      | FT            | (3)   | JTCK-SWCLK,<br>EVENTOUT                                                                                                       | -                    |

| 50     | A2      | A2      | 77      | A9       | 110     | PA15 (JTDI)                           | I/O      | FT_I          | (3)   | JTDI, TIM2_CH1,<br>TIM2_ETR, SPI1_NSS,<br>SPI3_NSS,<br>UART4_RTS_DE,<br>TSC_G3_IO1,<br>LCD_SEG17, SAI2_FS_B,<br>EVENTOUT      | -                    |

| 51     | D3      | D3      | 78      | B11      | 111     | PC10                                  | I/O      | FT_I          | -     | SPI3_SCK, USART3_TX,<br>UART4_TX, TSC_G3_IO2,<br>LCD_COM4/LCD_SEG28/<br>LCD_SEG40,<br>SDMMC1_D2,<br>SAI2_SCK_B, EVENTOUT      | -                    |

| 52     | C3      | C3      | 79      | C10      | 112     | PC11                                  | I/O      | FT_I          | _     | SPI3_MISO, USART3_RX,<br>UART4_RX, TSC_G3_IO3,<br>LCD_COM5/LCD_SEG29/<br>LCD_SEG41,<br>SDMMC1_D3,<br>SAI2_MCLK_B,<br>EVENTOUT | -                    |

| 53     | В3      | В3      | 80      | B10      | 113     | PC12                                  | I/O      | FT_I          | -     | SPI3_MOSI, USART3_CK,<br>UART5_TX, TSC_G3_IO4,<br>LCD_COM6/LCD_SEG30/<br>LCD_SEG42,<br>SDMMC1_CK,<br>SAI2_SD_B, EVENTOUT      | -                    |

| -      | -       | -       | 81      | C9       | 114     | PD0                                   | I/O      | FT            | -     | SPI2_NSS,<br>DFSDM_DATIN7,<br>CAN1_RX, FMC_D2,<br>EVENTOUT                                                                    | -                    |

| Table 15. STM32L476xxSTM32L476xx pin definitions | (continued)  |  |

|--------------------------------------------------|--------------|--|

|                                                  | (0011111000) |  |

| Τ        |

|----------|

| =        |

| 2        |

| 0        |

| <b>_</b> |

| ថ        |

|          |

| മ        |

|          |

| Q        |

|          |

| p        |

| _        |

| _        |

| Q        |

| Φ        |

| S        |

| o.       |

| ⊐.       |

| σ        |

| Ĕ.       |

| ō        |

| ž        |

|          |

STM32L476xx

|        |      | AF0               | AF1                                | AF2                              | AF3                 | AF4            | AF5       | AF6          | AF7                          |

|--------|------|-------------------|------------------------------------|----------------------------------|---------------------|----------------|-----------|--------------|------------------------------|

| Po     | ort  | SYS_AF            | TIM1/TIM2/<br>TIM5/TIM8/<br>LPTIM1 | TIM1/TIM2/<br>TIM3/TIM4/<br>TIM5 | TIM8                | 12C1/12C2/12C3 | SPI1/SPI2 | SPI3/DFSDM   | USART1/<br>USART2/<br>USART3 |

|        | PB0  | -                 | TIM1_CH2N                          | TIM3_CH3                         | TIM8_CH2N           | -              | -         | -            | USART3_CK                    |

|        | PB1  | -                 | TIM1_CH3N                          | TIM3_CH4                         | TIM8_CH3N           | -              | -         | DFSDM_DATIN0 | USART3_RTS<br>DE             |

|        | PB2  | RTC_OUT           | LPTIM1_OUT                         | -                                | -                   | I2C3_SMBA      | -         | DFSDM_CKIN0  | -                            |

|        | PB3  | JTDO-<br>TRACESWO | TIM2_CH2                           | -                                | -                   | -              | SPI1_SCK  | SPI3_SCK     | USART1_RTS<br>DE             |

|        | PB4  | NJTRST            | -                                  | TIM3_CH1                         | -                   | -              | SPI1_MISO | SPI3_MISO    | USART1_CTS                   |

|        | PB5  | -                 | LPTIM1_IN1                         | TIM3_CH2                         | -                   | I2C1_SMBA      | SPI1_MOSI | SPI3_MOSI    | USART1_CK                    |

|        | PB6  | -                 | LPTIM1_ETR                         | TIM4_CH1                         | TIM8_BKIN2          | I2C1_SCL       | -         | DFSDM_DATIN5 | USART1_TX                    |

| Port B | PB7  | -                 | LPTIM1_IN2                         | TIM4_CH2                         | TIM8_BKIN           | I2C1_SDA       | -         | DFSDM_CKIN5  | USART1_RX                    |

| POILE  | PB8  | -                 | -                                  | TIM4_CH3                         | -                   | I2C1_SCL       | -         | DFSDM_DATIN6 | -                            |

|        | PB9  | -                 | IR_OUT                             | TIM4_CH4                         | -                   | I2C1_SDA       | SPI2_NSS  | DFSDM_CKIN6  | -                            |

|        | PB10 | -                 | TIM2_CH3                           | -                                | -                   | I2C2_SCL       | SPI2_SCK  | DFSDM_DATIN7 | USART3_TX                    |

|        | PB11 | -                 | TIM2_CH4                           | -                                | -                   | I2C2_SDA       | -         | DFSDM_CKIN7  | USART3_RX                    |

|        | PB12 | -                 | TIM1_BKIN                          | -                                | TIM1_BKIN_<br>COMP2 | I2C2_SMBA      | SPI2_NSS  | DFSDM_DATIN1 | USART3_CK                    |

|        | PB13 | -                 | TIM1_CH1N                          | -                                | -                   | I2C2_SCL       | SPI2_SCK  | DFSDM_CKIN1  | USART3_CTS                   |

|        | PB14 | -                 | TIM1_CH2N                          | -                                | TIM8_CH2N           | I2C2_SDA       | SPI2_MISO | DFSDM_DATIN2 | USART3_RTS<br>DE             |

|        | PB15 | RTC_REFIN         | TIM1_CH3N                          | -                                | TIM8_CH3N           | -              | SPI2_MOSI | DFSDM_CKIN2  | -                            |

DocID025976 Rev 4

5

74/232

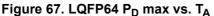

## 6.1.6 Power supply scheme

Figure 13. Power supply scheme

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

| Ē    |  |

|------|--|

| čtr  |  |

| ical |  |

| l ch |  |

| ara  |  |

| cte  |  |

| rist |  |

| ics  |  |

|                          | Т                              | able 33. Cur                                                    | rent con           | sumption          | in Lov | v-powe | er sleep | modes  | , Flash | in powe            | er-dowr | ו     |        |        |      |

|--------------------------|--------------------------------|-----------------------------------------------------------------|--------------------|-------------------|--------|--------|----------|--------|---------|--------------------|---------|-------|--------|--------|------|

| Symbol                   | Parameter                      | Conditions                                                      |                    |                   | ТҮР    |        |          |        |         | MAX <sup>(1)</sup> |         |       |        |        |      |

|                          |                                | -                                                               | Voltage<br>scaling | f <sub>HCLK</sub> | 25 °C  | 55 °C  | 85 °C    | 105 °C | 125 °C  | 25 °C              | 55 °C   | 85 °C | 105 °C | 125 °C | Unit |

|                          |                                |                                                                 |                    | 2 MHz             | 81     | 110    | 217      | 395    | 754     | 115                | 182     | 375   | 750    | 1500   |      |

| I <sub>DD</sub> (LPSleep | Supply current<br>in low-power | f <sub>HCLK</sub> = f <sub>MSI</sub><br>all peripherals disable |                    | 1 MHz             | 50     | 78     | 185      | 362    | 720     | 80                 | 149     | 342   | 717    | 1456   | uА   |

| )                        | sleep mode                     |                                                                 | 400 kHz            | 28                | 57     | 163    | 340      | 698    | 60      | 122                | 314     | 689   | 1429   | μΛ     |      |

|                          | •                              |                                                                 |                    | 100 kHz           | 18     | 47     | 155      | 332    | 686     | 50                 | 114     | 313   | 688    | 1438   |      |

- -

1. Guaranteed by characterization results, unless otherwise specified.

- -

| Symbol                   | Parameter                    | Conditions                                   |                 |       | ТҮР   |       |        |        |       | MAX <sup>(1)</sup> |       |                   |        |      |

|--------------------------|------------------------------|----------------------------------------------|-----------------|-------|-------|-------|--------|--------|-------|--------------------|-------|-------------------|--------|------|

| Symbol                   | Parameter                    | -                                            | V <sub>DD</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C              | 85 °C | 105 °C            | 125 °C | Unit |

|                          |                              |                                              | 1.8 V           | 1.14  | 3.77  | 14.7  | 34.7   | 77     | 2.7   | 9                  | 37    | 87                | 193    |      |

|                          |                              | LCD disabled                                 | 2.4 V           | 1.15  | 3.86  | 15    | 35.5   | 79.1   | 2.7   | 10                 | 38    | 89                | 198    |      |

|                          |                              |                                              | 3 V             | 1.18  | 3.97  | 15.4  | 36.4   | 81.3   | 2.8   | 10                 | 39    | 91                | 203    |      |

| (Stop 2)                 | Supply current in            |                                              | 3.6 V           | 1.26  | 4.11  | 16    | 38     | 85.1   | 3.0   | 10                 | 40    | 95 <sup>(2)</sup> | 213    |      |

| I <sub>DD</sub> (Stop 2) | Stop 2 mode,<br>RTC disabled | LCD enabled <sup>(3)</sup><br>clocked by LSI | 1.8 V           | 1.43  | 3.98  | 15    | 35     | 77.3   | 3.2   | 10                 | 38    | 88                | 193    | μA   |

|                          |                              |                                              | 2.4 V           | 1.49  | 4.07  | 15.3  | 35.8   | 79.4   | 3.2   | 10                 | 38    | 90                | 199    |      |

|                          |                              |                                              | 3 V             | 1.54  | 4.24  | 15.7  | 36.7   | 81.6   | 3.3   | 11                 | 39    | 92                | 204    |      |

|                          |                              |                                              | 3.6 V           | 1.75  | 4.47  | 16.1  | 38.3   | 85.4   | 3.5   | 11                 | 40    | 96                | 214    | 1    |

#### Table 34. Current consumption in Stop 2 mode

110/232

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 58: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously (see *Table 40: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the I/O supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DDIOx} \times f_{SW} \times C$$

where

${\rm I}_{\rm SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DDIOx</sub> is the I/O supply voltage

$f_{SW}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$  +  $C_S$

C<sub>S</sub> is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

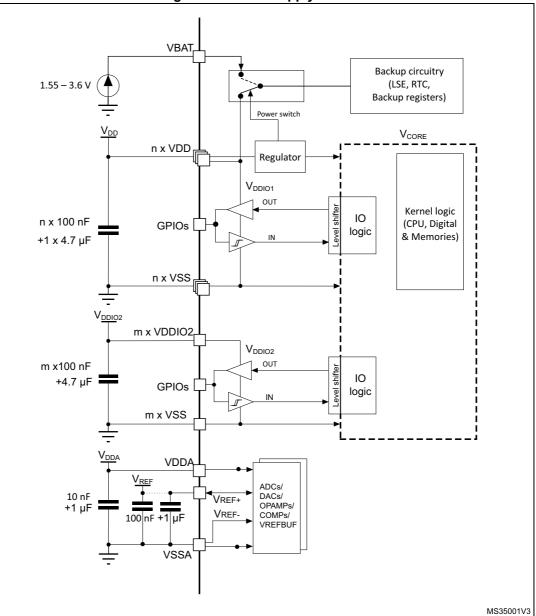

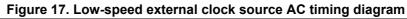

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in Figure 17.

| Symbol                                       | Parameter                             | Conditions | Min                    | Тур    | Мах                    | Unit |

|----------------------------------------------|---------------------------------------|------------|------------------------|--------|------------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | -          | -                      | 32.768 | 1000                   | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | -          | 0.7 V <sub>DDIOx</sub> | -      | V <sub>DDIOx</sub>     | V    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage  | -          | V <sub>SS</sub>        | -      | 0.3 V <sub>DDIOx</sub> |      |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | -          | 250                    | -      | -                      | ns   |

| Table 44. Low-speed external user clock characteristics <sup>(1)</sup> |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

1. Guaranteed by design.

- 1. Guaranteed by design.

- 2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

- 3. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

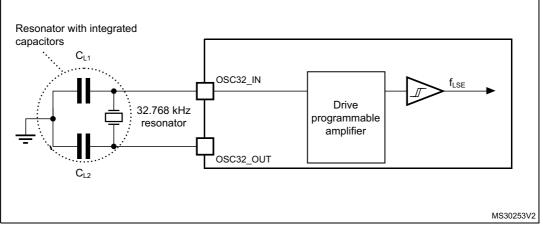

Figure 19. Typical application with a 32.768 kHz crystal

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

| Table 48. MSI oscillator characteristics <sup>(1)</sup> (continued) |                                                    |                      |                                    |                                     |                        |      |      |       |       |    |

|---------------------------------------------------------------------|----------------------------------------------------|----------------------|------------------------------------|-------------------------------------|------------------------|------|------|-------|-------|----|

| Symbol                                                              | Parameter                                          |                      | Conditions                         |                                     | Min                    | Тур  | Мах  | Unit  |       |    |

|                                                                     |                                                    |                      | Range 0 to 3                       | V <sub>DD</sub> =1.62 V<br>to 3.6 V | -1.2                   | -    | 0.5  |       |       |    |

| (100)(2)                                                            |                                                    | Molanada             | V <sub>DD</sub> =2.4 V<br>to 3.6 V | V <sub>DD</sub> =2.4 V<br>to 3.6 V  | -0.5                   | -    | 0.5  |       |       |    |

|                                                                     | MSI oscillator<br>frequency drift                  |                      | Pango 4 to 7                       | V <sub>DD</sub> =1.62 V<br>to 3.6 V | -2.5                   | -    | 0.7  | %     |       |    |

| $\Delta_{VDD}(MSI)^{(2)}$                                           | over V <sub>DD</sub><br>(reference is 3 V)         | MSI mode             | Ŭ V <sub>E</sub>                   | V <sub>DD</sub> =2.4 V<br>to 3.6 V  | -0.8                   | -    | 0.7  | 70    |       |    |

|                                                                     |                                                    |                      | Range 8 to 11                      | V <sub>DD</sub> =1.62 V<br>to 3.6 V | -5                     | -    | 1    |       |       |    |

|                                                                     |                                                    |                      | Range 6 to 11                      | V <sub>DD</sub> =2.4 V<br>to 3.6 V  | -1.6                   | -    |      |       |       |    |

| $\Delta F_{SAMPLING}$                                               | Frequency                                          |                      | $T_{A}$ = -40 to 85 °              | °C                                  | -                      | 1    | 2    |       |       |    |

| ∆F <sub>SAMPLING</sub><br>(MSI) <sup>(2)(6)</sup>                   | variation in sampling mode <sup>(3)</sup>          | MSI mode             | T <sub>A</sub> = -40 to 125        | °C                                  | -                      | 2    | 4    | %     |       |    |

| P_USB                                                               | Period jitter for<br>USB clock <sup>(4)</sup>      |                      | PLL mode                           | for next<br>transition              | -                      | -    | -    | 3.458 | 20    |    |

| Jitter(MSI) <sup>(6)</sup>                                          |                                                    |                      | USB clock <sup>(4)</sup>           | Range 11                            | for paired transition  | -    | -    | -     | 3.916 | ns |

| MT_USB                                                              | Medium term jitter<br>for USB clock <sup>(5)</sup> |                      |                                    | PLL mode                            | for next<br>transition | -    | -    | -     | 2     | ns |

| Jitter(MSI) <sup>(6)</sup>                                          |                                                    |                      | for paired<br>transition           | -                                   | -                      | -    | 1    | 115   |       |    |

| CC jitter(MSI) <sup>(6)</sup>                                       | RMS cycle-to-<br>cycle jitter                      | PLL mode R           | PLL mode Range 11                  |                                     | -                      | 60   | -    | ps    |       |    |

| P jitter(MSI) <sup>(6)</sup>                                        | RMS Period jitter                                  | PLL mode R           | ange 11                            | -                                   | -                      | 50   | -    | ps    |       |    |

|                                                                     |                                                    | Range 0              |                                    | -                                   | -                      | 10   | 20   |       |       |    |

|                                                                     |                                                    | Range 1              |                                    | -                                   | -                      | 5    | 10   |       |       |    |

| t(MSI)(6)                                                           | MSI oscillator                                     | Range 2              |                                    | -                                   | -                      | 4    | 8    | us    |       |    |

| t <sub>SU</sub> (MSI) <sup>(6)</sup>                                | start-up time                                      | Range 3              |                                    | -                                   | -                      | 3    | 7    | us    |       |    |

|                                                                     |                                                    | Range 4 to 7         |                                    | -                                   | -                      | 3    | 6    |       |       |    |

|                                                                     |                                                    | Range 8 to 11        |                                    | -                                   | -                      | 2.5  | 6    |       |       |    |

|                                                                     |                                                    |                      | 10 % of final frequency            | -                                   | -                      | 0.25 | 0.5  |       |       |    |

| t <sub>STAB</sub> (MSI) <sup>(6)</sup>                              | MSI oscillator<br>stabilization time               | PLL mode<br>Range 11 | 5 % of final<br>frequency          | -                                   | -                      | 0.5  | 1.25 | ms    |       |    |

|                                                                     |                                                    |                      | 1 % of final<br>frequency          | -                                   | -                      | -    | 2.5  |       |       |    |

|                                                                     |                                                    |                      |                                    |                                     |                        |      |      |       |       |    |

| Table 48. MSI oscillator characteristics <sup>(1)</sup> (continued | ) |

|--------------------------------------------------------------------|---|

## 6.3.10 Flash memory characteristics

| Table 51. Flash memory characteristics." |                                          |                    |               |       |      |

|------------------------------------------|------------------------------------------|--------------------|---------------|-------|------|

| Symbol                                   | Parameter                                | Conditions         | Тур           | Max   | Unit |

| t <sub>prog</sub>                        | 64-bit programming time                  | -                  | 81.69         | 90.76 | μs   |

| +                                        | one row (32 double                       | normal programming | 2.61          | 2.90  |      |

| <sup>t</sup> prog_row                    | word) programming time                   | fast programming   | 1.91          | 2.12  |      |

| +                                        | one page (2 Kbyte)                       | normal programming | 20.91         | 23.24 | ms   |

| <sup>l</sup> prog_page                   | programming time                         | fast programming   | 15.29         | 16.98 |      |

| t <sub>ERASE</sub>                       | Page (2 KB) erase time                   | -                  | 22.02         | 24.47 |      |

| t <sub>prog_bank</sub>                   | one bank (512 Kbyte)<br>programming time | normal programming | 5.35          | 5.95  | s    |

|                                          |                                          | fast programming   | 3.91          | 4.35  |      |

| t <sub>ME</sub>                          | Mass erase time<br>(one or two banks)    | -                  | 22.13         | 24.59 | ms   |

|                                          | Average consumption                      | Write mode         | 3.4           | -     |      |

|                                          | from V <sub>DD</sub>                     | Erase mode         | 3.4           | -     | mA   |

| I <sub>DD</sub>                          | Maximum aurrant (naak)                   | Write mode         | 7 (for 2 µs)  | -     | mA   |

|                                          | Maximum current (peak)                   | Erase mode         | 7 (for 41 µs) | -     |      |

#### Table 51. Flash memory characteristics<sup>(1)</sup>

1. Guaranteed by design.

| Symbol                          | Parameter      | Conditions                                           | Min <sup>(1)</sup> | Unit    |

|---------------------------------|----------------|------------------------------------------------------|--------------------|---------|

| N <sub>END</sub>                | Endurance      | T <sub>A</sub> = -40 to +105 °C                      | 10                 | kcycles |

| t <sub>RET</sub> Data retention |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C    | 30                 |         |

|                                 | Data rotantian | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C   | 15                 |         |

|                                 |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 125 °C   | 7                  | Years   |

|                                 | Data retention | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C  | 30                 | Tears   |

|                                 |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 15                 |         |

|                                 |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 |         |

#### Table 52. Flash memory endurance and data retention

1. Guaranteed by characterization results.

2. Cycling performed over the whole temperature range.

|                         | Table 00. ADC accuracy - miniced test conditions + * * * / (continued)    |                          |                          |                          |     |     |     |      |

|-------------------------|---------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|-----|-----|-----|------|

| Sym-<br>bol             | Parameter                                                                 | C                        | Conditions <sup>(4</sup> | )                        | Min | Тур | Max | Unit |

|                         |                                                                           | ADC clock frequency ≤    | Single                   | Fast channel (max speed) | -   | -71 | -69 |      |

| THD                     | Total 26 MHz,<br>harmonic 1.65 V $\leq$ V <sub>DDA</sub> = VREF+ $\leq$ - | 26  MHz,                 | ended                    | Slow channel (max speed) | -   | -71 | -69 | dB   |

|                         | distortion 3.6 V,                                                         | Differential             | Fast channel (max speed) | -                        | -73 | -72 | uр  |      |

| Voltage scaling Range 2 | Differential                                                              | Slow channel (max speed) | -                        | -73                      | -72 |     |     |      |

| Table 68. ADC accuracy - limited test conditions 4 <sup>(1)(2)(3)</sup> (cont | ntinued) |

|-------------------------------------------------------------------------------|----------|

|-------------------------------------------------------------------------------|----------|

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

- 3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4 V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V. No oversampling.

### **SAI characteristics**

Unless otherwise specified, the parameters given in *Table 86* for SAI are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in*Table 22: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels:  $0.5 \times V_{DD}$

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CK,SD,FS).

| Symbol                                             | Parameter                                                           | Conditions                                                            | Min  | Мах  | Unit    |

|----------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------|------|------|---------|

| f <sub>MCLK</sub>                                  | SAI Main clock output                                               | -                                                                     | -    | 50   | MHz     |

| f <sub>CK</sub> SAI clock frequency <sup>(2)</sup> |                                                                     | Master transmitter<br>2.7 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1  | -    | 18.5 |         |

|                                                    |                                                                     | Master transmitter<br>1.71 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1 | -    | 12.5 |         |

|                                                    |                                                                     | Master receiver<br>Voltage Range 1                                    | -    | 25   |         |

|                                                    | Slave transmitter<br>2.7 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1 | -                                                                     | 22.5 | MHz  |         |

|                                                    |                                                                     | Slave transmitter<br>1.71 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1  | -    | 14.5 |         |

|                                                    |                                                                     | Slave receiver<br>Voltage Range 1                                     | -    | 25   |         |

|                                                    |                                                                     | Voltage Range 2                                                       | -    | 12.5 |         |

| +                                                  | ES valid time                                                       | Master mode<br>2.7 $\leq$ V <sub>DD</sub> $\leq$ 3.6                  | -    | 22   | 20      |

| t <sub>v(FS)</sub>                                 | FS valid time                                                       | Master mode<br>$1.71 \le V_{DD} \le 3.6$                              | -    | 40   | ns      |

| t <sub>h(FS)</sub>                                 | FS hold time                                                        | Master mode                                                           | 10   | -    | ns      |

| t <sub>su(FS)</sub>                                | FS setup time                                                       | Slave mode                                                            | 1    | -    | ns      |

| t <sub>h(FS)</sub>                                 | FS hold time                                                        | Slave mode                                                            | 2    | -    | ns      |

| t <sub>su(SD_A_MR)</sub>                           | Data input sotup time                                               | Master receiver                                                       | 2.5  | -    | <b></b> |

| t <sub>su(SD_B_SR)</sub>                           | Data input setup time                                               | Slave receiver                                                        | 3    | -    | ns      |

| t <sub>h(SD_A_MR)</sub>                            | Data input hold time                                                | Master receiver                                                       | 8    | -    | ns      |

| t <sub>h(SD_B_SR)</sub>                            |                                                                     | Slave receiver                                                        | 4    | -    | 115     |

#### Table 86. SAI characteristics<sup>(1)</sup>

| Symbol                      | Parameter                                  | Min                    | Мах | Unit |

|-----------------------------|--------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period                             | 2T <sub>HCLK</sub> -1  | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)          | -                      | 2   |      |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)       | T <sub>HCLK</sub> +0.5 | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                | -                      | 2.5 |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high               | 1                      | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)       | -                      | 3.5 |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)    | T <sub>HCLK</sub>      | -   |      |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low                 | -                      | 2   |      |

| t <sub>d(CLKH-NWEH)</sub>   | FMC_CLK high to FMC_NWE high               | T <sub>HCLK</sub> +1   | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>    | FMC_CLK low to FMC_AD[15:0] valid          | -                      | 4   |      |

| t <sub>d(CLKL-ADIV)</sub>   | FMC_CLK low to FMC_AD[15:0] invalid        | 0                      | -   |      |

| t <sub>d(CLKL-DATA)</sub>   | FMC_A/D[15:0] valid data after FMC_CLK low | -                      | 5.5 |      |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low                 | -                      | 2.5 |      |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high               | T <sub>HCLK</sub> +1   | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high        | 0                      | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high         | 4                      | -   |      |

|                             |                | (1)(2)                         |

|-----------------------------|----------------|--------------------------------|

| Table 99. Synchronous multi | plexed PSRAM w | rite timings <sup>(1)(2)</sup> |

1. CL = 30 pF.

2. Guaranteed by characterization results.

| Symbol                      | Parameter                                | Min                     | Мах | Unit |

|-----------------------------|------------------------------------------|-------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period                           | 2T <sub>HCLK</sub> -0.5 | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)        | -                       | 2   |      |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)     | T <sub>HCLK</sub> +0.5  | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low              | -                       | 2   |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high             | 2.5                     | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)     | -                       | 5   |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)  | T <sub>HCLK</sub> -1    | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low               | -                       | 2   | 115  |

| t <sub>d(CLKH-NWEH)</sub>   | FMC_CLK high to FMC_NWE high             | T <sub>HCLK</sub> -1    | -   |      |

| t <sub>d(CLKL-Data)</sub>   | FMC_D[15:0] valid data after FMC_CLK low | -                       | 4.5 |      |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low               | 1.5                     | -   |      |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high             | T <sub>HCLK</sub> +1    | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high      | 0                       | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high       | 4                       | -   |      |

Table 101. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup>

1. CL = 30 pF.

2. Guaranteed by characterization results.

#### NAND controller waveforms and timings

*Figure 45* through *Figure 48* represent synchronous waveforms, and *Table 102* and *Table 103* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- COM.FMC\_SetupTime = 0x02

- COM.FMC\_WaitSetupTime = 0x03

- COM.FMC\_HoldSetupTime = 0x02

- COM.FMC\_HiZSetupTime = 0x03

- ATT.FMC\_SetupTime = 0x01

- ATT.FMC\_WaitSetupTime = 0x03

- ATT.FMC\_HoldSetupTime = 0x02

- ATT.FMC\_HiZSetupTime = 0x03

- Bank = FMC\_Bank\_NAND

- MemoryDataWidth = FMC\_MemoryDataWidth\_16b

- ECC = FMC\_ECC\_Enable

- ECCPageSize = FMC\_ECCPageSize\_512Bytes

- TCLRSetupTime = 0

- TARSetupTime = 0

In all timing tables, the  $T_{\mbox{HCLK}}$  is the HCLK clock period.

DocID025976 Rev 4

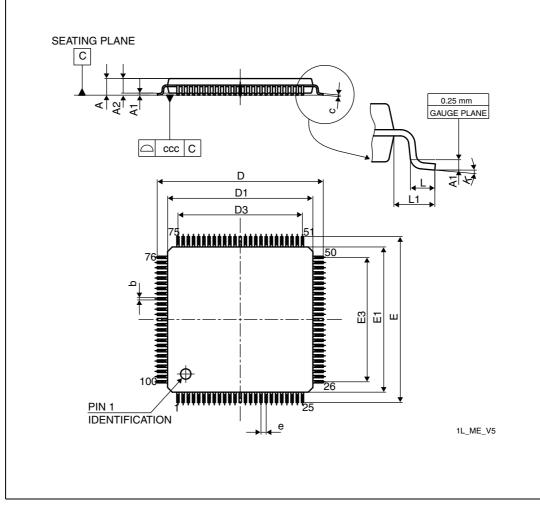

# 7.3 LQFP100 package information

Figure 55. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 107. LQPF100 - 100-pin, 14 x 14 mm<br>mechanical dat |     |

|------------------------------------------------------------|-----|

|                                                            | (1) |

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах    | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

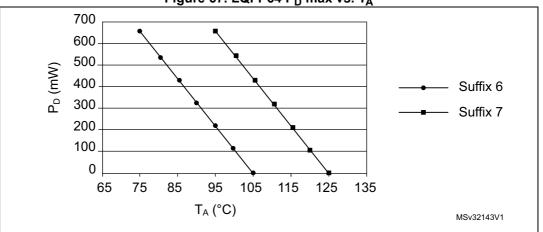

Using the values obtained in *Table 113*  $T_{Jmax}$  is calculated as follows:

- For LQFP64, 45 °C/W

- T<sub>Jmax</sub> = 100 °C + (45 °C/W × 134 mW) = 100 °C + 6.03 °C = 106.03 °C

This is above the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Section 8: Part numbering*) unless we reduce the power dissipation in order to be able to use suffix 6 parts.

Refer to *Figure 67* to select the required temperature range (suffix 6 or 7) according to your ambient temperature or power requirements.